# PBL 386 50/2 Subscriber Line Interface Circuit

# **Description**

The PBL 386 50/2 Subscriber Line Interface Circuit (SLIC) is a 90 V bipolar integrated circuit for use in Central Office Metering applications and other telecommunications equipment. The PBL 386 50/2 has been optimized for low total line interface cost and a high degree of flexibility in different applications.

The PBL 386 50/2 emulates resistive loop feed, programmable between 2x50  $\Omega$  and 2x900  $\Omega$ , with short loop current limiting adjustable to max 45 mA. In the current limited region the loop feed is nearly constant current with a slight slope corresponding to 2x30k $\Omega$ .

A second, lower battery voltage may be connected to the device to reduce short loop power dissipation. The SLIC automatically switches between the two battery supply voltages without need for external components or external control.

The SLIC incorporates loop current, ground key and ring trip detection functions. The PBL 386 50/2 is compatible with both loop and ground start signaling.

Two- to four-wire and four- to two-wire voice frequency (VF) signal conversion is accomplished by the SLIC in conjunction with either a conventional CODEC/filter or with a programmable CODEC/filter, e.g. SLAC, SiCoFi, Combo II. The programmable two-wire impedance, complex or real, is set by a simple external network.

Longitudinal voltages are suppressed by a feedback loop in the SLIC and the longitudinal balance specifications meet Bellcore TR909 requirements.

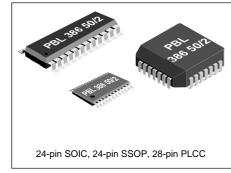

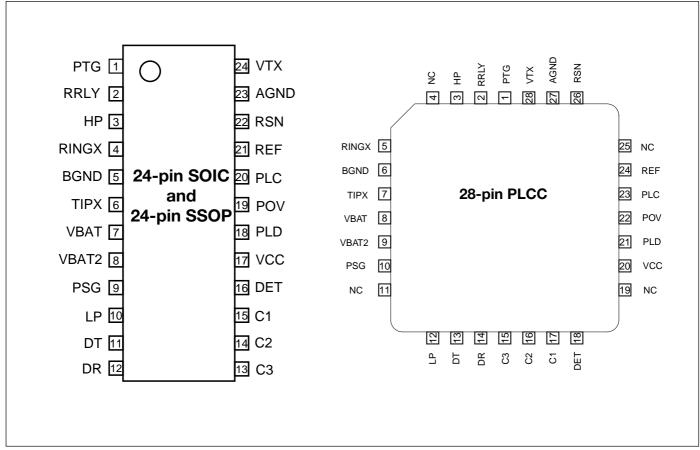

The PBL 386 50/2 package options are 24-pin SSOP, 24-pin SOIC or 28-pin PLCC.

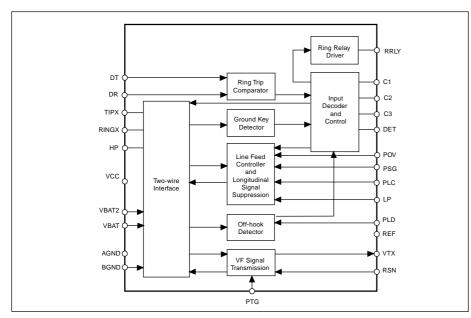

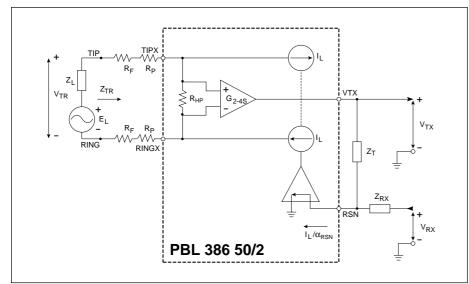

Figure 1. Block diagram.

# **Key Features**

- · 24-pin SSOP package

- Programmable two-wire signal headroom for 2.2 V<sub>ms</sub> metering

- High and low battery with automatic switching

- Only +5 V feed in addition to battery

- Selectable transmit gain (0.5x or 0.25x)

- 70 mW on-hook power dissipation in active state

- · On-hook transmission

- Long loop battery feed tracks Vbat for maximum line voltage

- · No power-up sequence

- 43V open loop voltage @

-48V battery feed

- Constant loop voltage for line leakage <5 mA (RLeak ~ >10 k $\Omega$  @ -48V)

- Full longitudinal current capability during on-hook state

- Analog over temperature protection permits transmission while the protection circuit is active

- · Line voltage measurement

- · Polarity reversal

- · Ground key detector

- Tip open state with ring ground detector

# **Maximum Ratings**

|                                                                                                                                   | Symbol                                 | Min                  | Max      | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|----------|------|

| Temperature, Humidity                                                                                                             |                                        |                      |          |      |

| Storage temperature range                                                                                                         | T <sub>Stg</sub>                       | -55                  | +150     | °C   |

| Operating temperature range                                                                                                       | $T_{Amb}$                              | -40                  | +110     | °C   |

| Operating junction temperature range, Note 1                                                                                      | $T_{J}$                                | -40                  | +140     | °C   |

| Power supply, $0^{\circ}C \le T_{Amb} \le -70^{\circ}C$                                                                           |                                        |                      |          |      |

| V <sub>cc</sub> with respect to A/BGND                                                                                            | V <sub>cc</sub>                        | -0.4                 | 6.5      | V    |

| V <sub>Bat2</sub> with respect to A/BGND                                                                                          | V <sub>Bat2</sub>                      | V <sub>Bat</sub>     | 0.4      | V    |

| V <sub>Bat</sub> with respect to A/BGND, continuous                                                                               | V <sub>Bat</sub>                       | -75                  | 0.4      | V    |

| V <sub>Bat</sub> with respect to A/BGND, 10 ms                                                                                    | $V_{\text{Bat}}$                       | -80                  | 0.4      | V    |

| Power dissipation                                                                                                                 |                                        |                      |          |      |

| Continuous power dissipation at T <sub>Amb</sub> ≤ +70 °C                                                                         | P <sub>D</sub>                         |                      | 1.5      | W    |

| Ground                                                                                                                            |                                        |                      |          |      |

| Voltage between AGND and BGND                                                                                                     | V <sub>G</sub>                         | -0,3                 | 0,3      | V    |

| Relay Driver                                                                                                                      |                                        |                      |          |      |

| Ring relay supply voltage                                                                                                         |                                        |                      | BGND+14  | l V  |

| Ring trip comparator                                                                                                              |                                        |                      |          |      |

| Input voltage                                                                                                                     | $V_{\rm DT}, V_{\rm DR}$               | V <sub>Bat</sub>     | AGND     | V    |

| Input current                                                                                                                     | $I_{DT}, I_{DR}$                       | -5                   | 5        | mA   |

| Digital inputs, outputs (C1, C2, C3, DET)                                                                                         |                                        |                      |          |      |

| Input voltage                                                                                                                     | $V_{ID}$                               | -0.4                 | $V_{cc}$ | V    |

| Output voltage                                                                                                                    | $V_{od}$                               | -0.4                 | $V_{cc}$ | V    |

| TIPX and RINGX terminals, $0^{\circ}\text{C} < \text{T}_{\text{Amb}} < +70^{\circ}\text{C}, \text{ V}_{\text{Bat}} = -50\text{V}$ |                                        |                      |          |      |

| Maximum supplied TIPX or RINGX current                                                                                            | I <sub>TIPX</sub> , I <sub>RINGX</sub> | -100                 | +100     | mA   |

| TIPX or RINGX voltage, continuous (referenced to AGND), Note 2                                                                    | V <sub>TA</sub> , V <sub>RA</sub>      | -80                  | 2        | V    |

| TIPX or RINGX, pulse < 10 ms, t <sub>Rep</sub> > 10 s, Note 2                                                                     | $V_{TA}, V_{RA}$                       | V <sub>Bat</sub> -10 | 5        | V    |

| TIPX or RINGX, pulse < 1 $\mu$ s, $t_{Rep}$ > 10 s, Note 2                                                                        | $V_{TA}, V_{RA}$                       | V <sub>Bat</sub> -25 | 10       | V    |

| TIPX or RINGX, pulse < 250 ns, t <sub>Rep</sub> > 10 s, Notes 2 & 3                                                               | $V_{TA}, V_{RA}$                       | V <sub>Bat</sub> -35 | 15       | V    |

# **Recommended Operating Condition**

| Parameter                             | Symbol           | Min  | Max  | Unit |

|---------------------------------------|------------------|------|------|------|

| Ambient temperature                   | $T_{Amb}$        | 0    | +70  | °C   |

| V <sub>cc</sub> with respect to AGND  | V <sub>cc</sub>  | 4.75 | 5.25 | V    |

| V <sub>Bat</sub> with respect to AGND | V <sub>Bat</sub> | -65  | -8   | V    |

| AGND with respect to BGND             | $V_{g}$          | -100 | 100  | mV   |

# **Notes**

- 1. The circuit includes thermal protection. Operation at or above 140°C junction temperature may degrade device reliability.

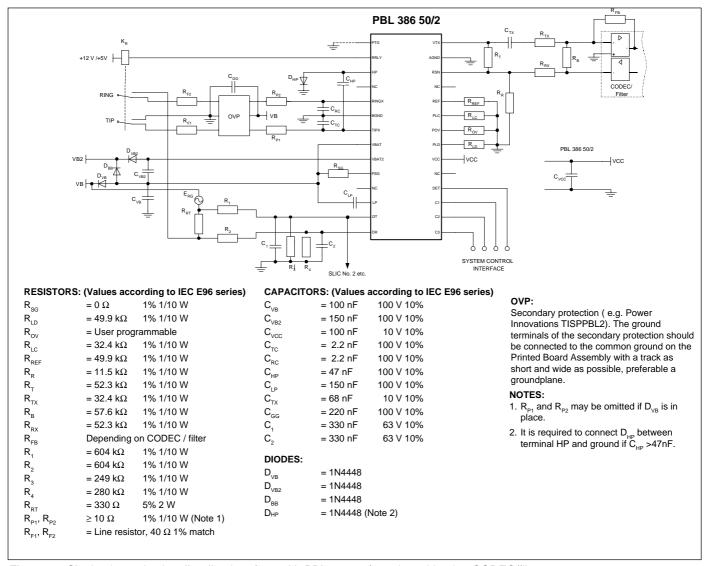

- 2. With the diodes  $\rm D_{\rm VB}$  and  $\rm D_{\rm VB2}$  included, see figure 12.

- 3.  $R_{F1}$  and  $R_{F2} \ge 20~\Omega$  is also required. Pulse is applied to TIP and RING outside  $R_{F1}$  and  $R_{F2}$ .

# **Electrical Characteristics**

0 °C ≤  $T_{Amb}$  ≤ +70 °C, PTG = Open (see pin description),  $R_{OV}$  = ∞,  $V_{CC}$  = +5V ±5 %,  $V_{Bat}$  = -58V to -40V,  $V_{Bat2}$  = -32V,  $R_{LC}$ =32.4 kΩ,  $I_{L}$  = 27 mA.  $R_{L}$  = 600  $\Omega$ ,  $R_{F1}$  =  $R_{F2}$  =  $R_{P1}$  =  $R_{P2}$  =0,  $R_{Ref}$  = 49.9 k $\Omega$ ,  $C_{HP}$  = 47 nF,  $C_{LP}$ =0.15  $\mu$ F,  $R_{T}$  = 60 k $\Omega$ ,  $R_{SG}$  = 0 k $\Omega$ ,  $R_{RX}$  = 60 k $\Omega$ ,  $R_{RX}$  = 11 k $\Omega$  unless otherwise specified. Current definition: current is positive if flowing into a pin.

|                                                                            | Ref |                                                          |     |                     |     |                        |

|----------------------------------------------------------------------------|-----|----------------------------------------------------------|-----|---------------------|-----|------------------------|

| Parameter                                                                  | fig | Conditions                                               | Min | Тур                 | Max | Unit                   |

| Two-wire port                                                              |     |                                                          |     |                     |     |                        |

| Overhead voltage, V <sub>TRO</sub> , I <sub>Ldc</sub> ≥ 18mA               | 2   | Active state, R <sub>ov</sub> = ∞                        | 2.7 |                     |     | $V_{Peak}$             |

|                                                                            |     | 0.2 kHz < f < 3.4 kHz                                    |     |                     |     |                        |

| On-Hook, I <sub>Ldc</sub> ≤5mA                                             |     | 1% THD, Note 1                                           | 1.1 |                     |     | $V_{Peak}$             |

| Over load level, metering                                                  |     | f≤16kHz, Z <sub>LAC</sub> =200Ω, Adj. by R <sub>OV</sub> |     |                     | 5.0 | V <sub>Peak</sub>      |

| Input impedance, Z <sub>TR</sub>                                           |     | Note 2                                                   |     | Z <sub>T</sub> /200 |     |                        |

| Longitudinal impedance, Z <sub>LOT</sub> , Z <sub>LOR</sub>                |     | 0 < f < 100 Hz                                           |     | 20                  | 35  | Ω/wire                 |

| Longitudinal current limit, I <sub>LOT</sub> , I <sub>LOR</sub>            |     | active state                                             | 18  |                     |     | mA <sub>ms</sub> /wire |

| Longitudinal to metallic balance, B <sub>LM</sub>                          |     | Normal polarity:                                         |     |                     |     |                        |

| (IEEE standard 455-1985, $Z_{TRX} = 736\Omega$ )                           |     | 0.2 kHz < f < 1.0 kHz                                    | 55  |                     |     | dB                     |

| Longitudinal to metallic balance, B <sub>LME</sub>                         | 3   | 1.0 kHz < f < 3.4 kHz                                    | 55  |                     |     | dB                     |

| E <sub>Lo</sub>                                                            |     | Reverse polarity:                                        |     |                     |     |                        |

| $B_{LME} = 20 \cdot Log \left  \frac{E_{Lo}}{V_{TR}} \right $              |     | 0.2 kHz < f < 3.4 kHz                                    | 55  |                     |     | dB                     |

| Longitudinal to four-wire balance, B <sub>LEE</sub>                        | 3   | Normal polarity:                                         |     |                     |     |                        |

| _                                                                          |     | 0.2 kHz < f < 1.0 kHz                                    | 61  | 75                  |     | dB                     |

| $B_{LFE} = 20 \cdot Log \left  \frac{E_{Lo}}{V_{Tot}} \right $             |     | 1.0 kHz < f < 3.4 kHz                                    | 61  | 70                  |     | dB                     |

| TX                                                                         |     | Reverse polarity:                                        |     |                     |     |                        |

|                                                                            |     | 0.2 kHz < f < 3.4 kHz                                    | 61  | 68                  |     | dB                     |

| Metallic to longitudinal balance, B <sub>MLE</sub>                         | 4   | 0.2 kHz < f < 3.4 kHz                                    | 40  | 50                  |     | dB                     |

| $B_{MLE} = 20 \cdot Log \left  \frac{V_{TR}}{V_{Lo}} \right  ; E_{RX} = 0$ |     |                                                          |     |                     |     |                        |

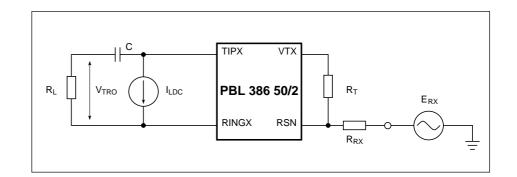

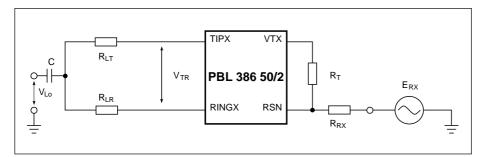

Figure 2. Overhead voltage,  $V_{TRO}$ , two-wire port

$$\frac{1}{\omega C} \ll R_L$$

,  $R_L = 600 \Omega$

$$R_{T} = 60 \text{ k}\Omega, R_{RX} = 60 \text{ k}\Omega$$

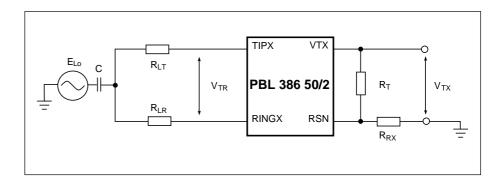

Figure 3. Longitudinal to metallic ( $B_{\rm LME}$ ) and Longitudinal to four-wire ( $B_{\rm LFE}$ ) balance

$$\frac{1}{\omega C}$$

<< 150  $\Omega$ ,  $R_{LR} = R_{LT} = R_L/2 = 300 \Omega$

$$R_{_T} = 60 \text{ k}\Omega, R_{_{RX}} = 60 \text{ k}\Omega$$

# PBL 386 50/2

| Parameter                                                              | Ref<br>fig | Conditions                                                      | Min   | Тур                   | Max  | Unit              |

|------------------------------------------------------------------------|------------|-----------------------------------------------------------------|-------|-----------------------|------|-------------------|

| Four-wire to longitudinal balance, B <sub>FI F</sub>                   | 4          | 0.2 kHz < f < 3.4 kHz                                           | 40    | 50                    |      | dB                |

| 7                                                                      |            | $B_{FLE} = 20 \cdot Log \bigg  \frac{E_{RX}}{V_{Lo}} \bigg $    |       |                       |      |                   |

| Two-wire return loss, r                                                |            | $r = 20 \cdot \text{Log} \frac{ Z_{TR} + Z_L }{ Z_{TR} - Z_L }$ |       |                       |      |                   |

|                                                                        |            | 0.2 kHz < f < 1.0 kHz                                           | 27    | 35                    |      | dB                |

|                                                                        |            | 1.0 kHz < f < 3.4 kHz, Note 3                                   | 20    | 22                    |      | dB                |

| TIPX idle voltage, V <sub>Ti</sub>                                     |            | active, I <sub>1</sub> <5 mA                                    |       | - 1.3                 |      | V                 |

| RINGX idle voltage, V <sub>Ri</sub>                                    |            | active, I <5 mA                                                 |       | V <sub>Bat</sub> +3.0 | )    | V                 |

|                                                                        |            | tip open, I <sub>L</sub> <5 mA                                  |       | V <sub>Bat</sub> +3.0 |      | V                 |

| $V_{TR}$                                                               |            | active, I <sub>L</sub> <5 mA                                    |       | V <sub>Bat</sub> +4.3 | 3    | V                 |

| Four-wire transmit port (VTX)                                          |            |                                                                 |       |                       |      |                   |

| Overhead voltage, V <sub>TXO</sub> , I <sub>L</sub> ≥ 18mA             | 5          | Load impedance > 20 k $\Omega$ ,<br>1% THD, Note 4              | 1.35  |                       |      | V <sub>Peak</sub> |

| On-hook, $I_1 \leq 5mA$                                                |            | ·                                                               | 0.55  |                       |      | V <sub>Peak</sub> |

| Output offset voltage, $\Delta V_{TX}$                                 |            |                                                                 | -100  | 0                     | 100  | mV                |

| Output impedance, z <sub>TX</sub>                                      |            | 0.2 kHz < f < 3.4 kHz                                           |       | 15                    | 50   | Ω                 |

| Four-wire receive port (RSN)                                           |            |                                                                 |       |                       |      |                   |

| Receive summing node (RSN) DC voltage                                  |            | I <sub>RSN</sub> = -155 μA                                      | 1.15  | 1.25                  | 1.35 | V                 |

| Receive summing node (RSN) impedance                                   |            | 0.2 kHz < f < 3.4 kHz                                           |       | 8                     | 20   | Ω                 |

| Receive summing node (RSN)                                             |            | 0.3 kHz < f < 3.4 kHz                                           |       |                       |      |                   |

| current (I <sub>RSN</sub> ) to metallic loop current (I <sub>L</sub> ) |            |                                                                 |       | 200                   |      | ratio             |

| $gain, \alpha_{RSN}$                                                   |            |                                                                 |       |                       |      |                   |

| Frequency response                                                     |            |                                                                 |       |                       |      |                   |

| Two-wire to four-wire, g <sub>2-4</sub>                                | 6          | relative to 0 dBm, 1.0 kHz. $E_{RX} = 0 \text{ V}$              |       |                       |      |                   |

| <del>-</del> ·                                                         |            | 0.3 kHz < f < 3.4 kHz                                           | -0.20 |                       | 0.10 | dB                |

|                                                                        |            | f = 8.0 kHz, 12 kHz, 16 kHz                                     | -1.0  |                       | 0.1  | dB                |

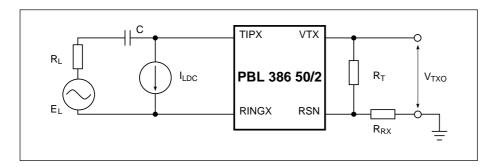

Figure 4. Metallic to longitudinal and fourwire to longitudinal balance

$$\frac{1}{\omega C} << 150~\Omega,~R_{LT}~=R_{LR} = R_{L}~/2 = 300\Omega$$

$$R_{T} = 60 \text{ k}\Omega, R_{RX} = 60 \text{ k}\Omega$$

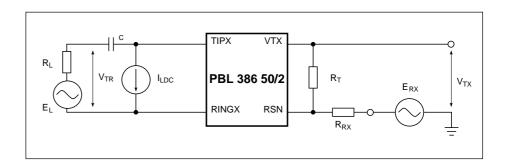

Figure 5. Overhead voltage,  $V_{\rm TXO}$ , fourwire transmit port

$$\frac{1}{\omega C}$$

<< R<sub>L</sub>, R<sub>L</sub> = 600  $\Omega$

$$R_{T} = 60 \text{ k}\Omega, R_{RX} = 60 \text{ k}\Omega$$

| Parameter                                                                         | Ref<br>fig | Conditions                                                                       | Min                 | Тур                 | Max                 | Unit   |

|-----------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------|---------------------|---------------------|---------------------|--------|

| Four-wire to two-wire, g <sub>4-2</sub>                                           | 6          | relative to 0 dBm, 1.0 kHz. E,=0 V                                               |                     |                     |                     |        |

| -72                                                                               |            | 0.3 kHz < f < 3.4 kHz                                                            | -0.2                |                     | 0.1                 | dB     |

|                                                                                   |            | f = 8 kHz, 12 kHz,                                                               | -1.0                |                     | 0                   | dB     |

|                                                                                   |            | 16 kHz                                                                           | -2.0                |                     | 0                   | dB     |

| Four-wire to four-wire, g <sub>4-4</sub>                                          | 6          | relative to 0 dBm, 1.0 kHz, $E_L$ =0 V                                           |                     |                     |                     |        |

|                                                                                   |            | 0.3 kHz < f < 3.4 kHz                                                            | -0.2                |                     | 0.1                 | dB     |

| Insertion loss                                                                    |            |                                                                                  |                     |                     |                     |        |

| Two-wire to four-wire, G <sub>2-4</sub>                                           | 6          | 0 dBm, 1.0 kHz, Note 5                                                           |                     |                     |                     |        |

|                                                                                   |            | $G_{2-4} = 20 \cdot \text{Log} \left  \frac{V_{TX}}{V_{TR}} \right ; E_{RX} = 0$ | -6.22               | -6.02               | -5.82               | dB     |

|                                                                                   |            | PTG = AGND                                                                       | -12.24              | -12.04              | -11.84              | dB     |

| Four-wire to two-wire, G <sub>4-2</sub>                                           | 6          | 0 dBm, 1.0 kHz, Note 6                                                           |                     |                     |                     |        |

|                                                                                   |            | $G_{4-2} = 20 \cdot \text{Log} \left  \frac{V_{TR}}{E_{RX}} \right ; E_{L} = 0$  | -0.2                |                     | 0.2                 | dB     |

| Gain tracking                                                                     |            |                                                                                  |                     |                     |                     |        |

| Two-wire to four-wire                                                             | 6          | Ref10 dBm, 1.0 kHz, Note 7                                                       |                     |                     |                     |        |

|                                                                                   |            | -40 dBm to +3 dBm                                                                | -0.1                |                     | 0.1                 | dB     |

|                                                                                   |            | -55 dBm to -40 dBm                                                               | -0.2                |                     | 0.2                 | dB     |

| Four-wire to two-wire                                                             | 6          | Ref10 dBm, 1.0 kHz,                                                              |                     |                     |                     |        |

|                                                                                   |            | -40 dBm to +3 dBm                                                                | -0.1                |                     | 0.1                 | dB     |

|                                                                                   |            | -55 dBm to -40 dBm                                                               | -0.2                |                     | 0.2                 | dB     |

| Noise                                                                             |            |                                                                                  |                     |                     |                     |        |

| Idle channel noise at two-wire                                                    |            | C-message weighting, 2 wire                                                      |                     |                     | 12                  | dBrnC  |

| (TIPX-RINGX) or four-wire (VTX) output                                            |            | Psophometrical weighting, 2 wire                                                 |                     |                     | -78                 | dBmp   |

|                                                                                   |            | C-message weighting, 4 wire                                                      |                     |                     | 6                   | dBrnC  |

|                                                                                   |            | Psophometrical weighting, 4 wire                                                 |                     |                     | -84                 | dBmp   |

|                                                                                   |            | Note 8                                                                           |                     |                     |                     |        |

| Harmonic distortion                                                               |            | 0.40                                                                             |                     | 0.7                 | <b>50</b>           | -ID    |

| Two-wire to four-wire                                                             | 6          | 0 dBm                                                                            |                     | -67                 | -50                 | dB     |

| Four-wire to two-wire                                                             |            | 0.3 kHz < f < 3.4 kHz                                                            |                     | -67                 | -50                 | dB<br> |

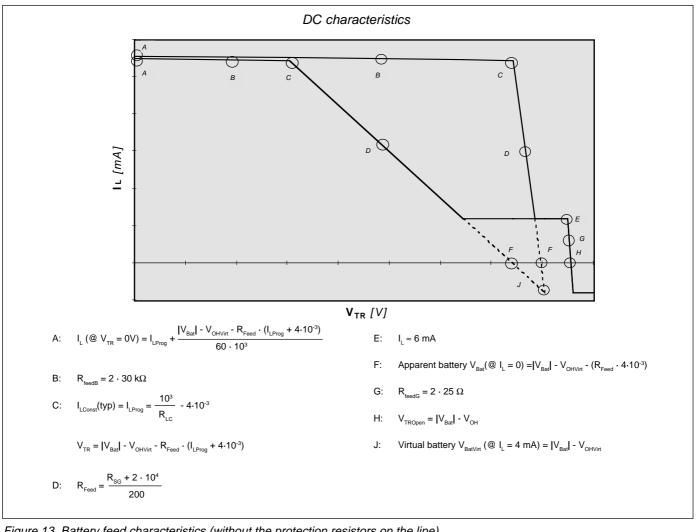

| Battery feed characteristics                                                      |            |                                                                                  |                     |                     |                     |        |

| Loop current, $\rm I_{\rm L}$ , in the current limited region, reference A, B & C | 13         | $18\text{mA} \le I_L \le 45 \text{ mA}$                                          | 0.92 I <sub>L</sub> | I <sub>L</sub>      | 1.08 I <sub>L</sub> | mA     |

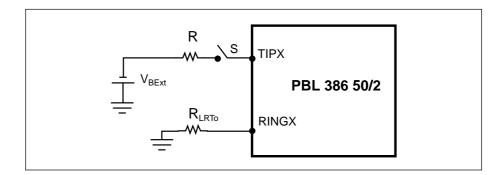

| Tip open state TIPX current, I <sub>Leak</sub>                                    | 7          | S = closed; R = 7 k $\Omega$ , Note 10                                           |                     |                     | -150                | μΑ     |

| Tip open state RINGX current, I <sub>LRTo</sub>                                   |            | $R_{LRTo} = 0\Omega$ , $V_{Bat} = -48V$                                          |                     | IL                  |                     | mA     |

|                                                                                   |            | $R_{LRTo} = 2.5 \text{ k}\Omega, V_{Bat} = -48V$                                 |                     | 17                  |                     | mA     |

| Tip open state RINGX voltage, V <sub>RTo</sub>                                    |            | I <sub>LRTo</sub> < 23 mA                                                        |                     | V <sub>Bat</sub> +6 |                     | V      |

Figure 6.

Frequency response, insertion loss, gain tracking.

$$\frac{1}{\omega C}$$

<< R<sub>L</sub>, R<sub>L</sub> = 600  $\Omega$

$$R_{_{\mathrm{T}}} = 60 \text{ k}\Omega, R_{_{\mathrm{RX}}} = 60 \text{ k}\Omega$$

|                                                            | Ref<br>fig | Conditions                                       | Min                   | Тур       | Max                   | Unit |

|------------------------------------------------------------|------------|--------------------------------------------------|-----------------------|-----------|-----------------------|------|

| Tip voltage (ground start)                                 | 7          | Active state, Tip lead open (S open),            | -4                    | -2.2      |                       | V    |

|                                                            |            | Ring lead to ground through 150 $\Omega$         |                       |           |                       |      |

| Tip voltage (ground start)                                 |            | Active state, tip lead to -48 V                  | -6                    | -2.4      |                       | V    |

|                                                            |            | through 7 k $\Omega$ (S closed), Ring            |                       |           |                       |      |

|                                                            |            | lead to ground through 150 $\Omega$              |                       |           |                       |      |

| Open circuit state loop current, I <sub>LOC</sub>          |            | $R_L = 0\Omega$                                  | -100                  | 0         | 100                   | μΑ   |

| Loop current detector                                      |            |                                                  |                       |           |                       |      |

| Programmable threshold, I <sub>LTh</sub> ,                 |            | $I_{LTh} = \frac{500}{R_{LD}}$                   | $0.85 \cdot I_{LTh}$  | $I_{LTh}$ | 1.15⋅I <sub>LTh</sub> | mA   |

| active, active reverse                                     |            | $R_{LD}$                                         |                       |           |                       |      |

|                                                            |            | $R_{LD}$ in $k\Omega$ , $I_{LTh} \ge 7$ mA       |                       |           |                       |      |

| Tip open state                                             |            | $I_{LTh} = \frac{500}{R_{LD}}$                   | 0.85·I <sub>LTh</sub> | $I_{LTh}$ | 1.15⋅I <sub>LTh</sub> | mA   |

|                                                            |            | K <sub>LD</sub>                                  |                       |           |                       |      |

| Ground key detector                                        |            |                                                  |                       |           |                       |      |

| Ground key detector threshold                              |            |                                                  |                       |           |                       |      |

| $(I_{LTIPX}$ and $I_{LRINGX}$ difference to trigger ground | key        | det.)                                            | 10                    | 16        | 22                    | mA   |

| Line voltage measurement                                   |            |                                                  |                       |           |                       |      |

| Pulse width, t <sub>LVM</sub>                              |            | Note 9                                           |                       | 5.5       |                       | μs/V |

| Ring trip comparator                                       |            |                                                  |                       |           |                       |      |

| Offset voltage, $\Delta V_{\text{DTDR}}$                   |            | Source resistance, $R_s = 0 \Omega$              | -20                   | 0         | 20                    | mV   |

| Input bias current, I <sub>B</sub>                         |            | $I_{B} = (I_{DT} + I_{DR})/2$                    | -200                  | -20       | 200                   | nA   |

| Input common mode range, $V_{DT}$ , $V_{DR}$               |            |                                                  | $V_{\text{Bat}}$ +1   |           | -1                    | V    |

| Ring relay driver                                          |            |                                                  |                       |           |                       |      |

| Saturation voltage, V <sub>OL</sub>                        |            | $I_{OL} = 50 \text{ mA}$ $V_{OH} = 12 \text{ V}$ |                       | 0.2       | 0.5                   | V    |

| Off state leakage current, I <sub>Lk</sub>                 |            | $V_{OH} = 12 \text{ V}$                          |                       |           | 10                    | μΑ   |

| Digital inputs (C1, C2, C3)                                |            |                                                  |                       |           |                       |      |

| Input low voltage, V <sub>IL</sub>                         |            |                                                  | 0                     |           | 0.5                   | V    |

| Input high voltage, V <sub>IH</sub>                        |            |                                                  | 2.5                   |           | V <sub>cc</sub>       | V    |

| Input low current, I <sub>IL</sub>                         |            | $V_{IL} = 0.5$                                   |                       |           | -50                   | μΑ   |

| Input high current, I <sub>IH</sub>                        |            | V <sub>IH</sub> = 2.5 V                          |                       |           | 50                    | μΑ   |

| Detector output (DET)                                      |            |                                                  |                       |           |                       |      |

| Output low voltage                                         |            | $I_{OL} = 0.5 \text{ mA}$                        |                       |           | 0.7                   | V    |

| Internal pull-up resistor                                  |            |                                                  |                       | 15        |                       | kΩ   |

| Power dissipation ( $V_{Bat} = -48V$ , $V_{Bat2} = -32V$   | <b>V</b> ) |                                                  |                       |           |                       |      |

| $P_1$                                                      |            | Open circuit state, C1, C2, C3 = 0, 0,           | 0                     | 10        | 15                    | mW   |

|                                                            |            | Active state, C1, C2, C3 = 0, 1, 0               |                       |           |                       |      |

| $P_{2}$                                                    |            | Longitudinal current = 0 mA, I = 0 mA            | (on-hook)             | 70        | 85                    | mW   |

| $P_3^-$                                                    |            | $R_1 = 300 \Omega \text{ (off-hook)}$            |                       | 730       |                       | mW   |

| $P_4$                                                      |            | $R_{\perp} = 800 \Omega \text{ (off-hook)}$      |                       | 360       |                       | mW   |

| Power supply currents (V <sub>Bat</sub> = -48V)            |            |                                                  |                       |           |                       |      |

| V <sub>cc</sub> current, I <sub>cc</sub>                   |            | Open circuit state                               | <u> </u>              | 1.2       | 2.0                   | mA   |

| V <sub>Bat</sub> current, I <sub>Bat</sub>                 |            |                                                  | -0.1                  | -0.05     |                       | mA   |

| V <sub>cc</sub> current, I <sub>cc</sub>                   |            | Active state                                     |                       | 2.8       | 4.0                   | mA   |

| $V_{Bat}$ current, $I_{Bat}$                               |            | On-hook, Long Current = 0 mA                     | -1.5                  | -1.1      |                       | mA   |

| Power supply rejection ratios                              |            |                                                  |                       |           |                       |      |

| V <sub>cc</sub> to 2- or 4-wire port                       |            | Active State                                     | 30                    | 42        |                       | dB   |

| V <sub>Bat</sub> to 2- or 4-wire port                      |            | $f = 1 \text{ kHz V}_n = 100 \text{mV}$          | 36                    | 45        |                       | dB   |

| V <sub>Bat2</sub> to 2- or 4-wire port                     |            |                                                  | 40                    | 60        |                       | dB   |

| Temperature guard                                          |            |                                                  |                       |           |                       |      |

| Junction threshold temperature, $T_{JG}$                   |            |                                                  |                       | 145       |                       | °C   |

| Thermal resistance                                         |            |                                                  |                       |           |                       |      |

| 28-pin PLCC, θ <sub>JP28plcc</sub>                         |            |                                                  |                       | 39        |                       | °C/W |

| 24-pin SOIC, $\theta_{JP24soic}$                           |            |                                                  |                       | 43        |                       | °C/W |

| 24-pin SSOP, $\theta_{JP24ssop}$                           |            |                                                  |                       | 55        |                       | °C/W |

|                                                            |            |                                                  |                       |           |                       |      |

Figure 7. Tipx voltage.

#### **Notes**

- 1. The overhead voltage can be adjusted with the  $R_{\text{OV}}$  resistor for higher levels e.g. min 3.1  $V_{\text{Peak}}$  and is specified at the two-wire port with the signal source at the four-wire receive port.

- The two-wire impedance is programmable by selection of external component values according to:

- $Z_{TRX} = Z_T / |G_{2-4S} \alpha_{RSN}|$  where:

- $Z_{TRX}$  = impedance between the TIPX and RINGX terminals

- Z<sub>T</sub> = programming network between the VTX and RSN terminals

- $G_{2-4S}$  = transmit gain, nominally = 0.5 (or 0.25 see pin PTG)

- $\alpha_{RSN}$  = receive current gain, nominally = 200 (current defined as positive flowing into the receivesumming node, RSN, and when flowing from ring to tip).

- Higher return loss values can be achieved by adding a reactive component to R<sub>T</sub>, the two-wire terminating impedance programming resistance, e.g. by dividing R<sub>T</sub> into two equal halves and connecting a capacitor from the common point to ground.

- 4. The overhead voltage can be adjusted with the ROV resistor for higher levels e.g. min 1.6 V<sub>Peak</sub> and is specified at the four-wire transmit port, VTX, with the signal source at the two-wire port. Note that the gain from the two-wire port to the four-wire transmit port is G<sub>2-4S</sub> = 0.5 (or 0.25 see pin PTG). The overhead voltage is dependent on G<sub>2-4S</sub> and POV setting.

- 5. Pin PTG = Open sets transmit gain to nom. -6.02dB Pin PTG = AGND sets transmit gain to nom. -12.04 dB Secondary protection resistors  $R_{\scriptscriptstyle F}$  and resistors  $R_{\scriptscriptstyle P}$  impact the insertion loss as explained in the text, section Transmission. The specified insertion loss is for  $R_{\scriptscriptstyle F} = R_{\scriptscriptstyle P} = 0$ .

- The specified insertion loss tolerance does not include errors caused by external components.

- 7. The level is specified at the two-wire port.

- 8. The two-wire idle noise is specified with the port terminated in 600  $\Omega$  (R $_{\!\!\! L}$ ) and with the four-wire receive port grounded (E $_{\!\!\! RX}$  = 0; see figure 6). The four-wire idle noise at VTX is specified with the two-wire port terminated in 600  $\Omega$  (R $_{\!\!\! L}$ ). The noise specification is referenced to a 600  $\Omega$  programmed two-wire impedance level at VTX. The four-wire receive port is grounded (E $_{\!\!\! RX}$  = 0).

- Previous state must be active loop or ground key detector.

- 10. If  $|V_{BExt}| \ge |V_{Bat} + 2 V|$ , where  $V_{Bat}$  is the voltage at  $V_{BAT}$  pin, the current  $I_{Leak}$  is limited to  $\approx 5 mA$ .

Figure 8. Pin configuration, 24-pin SSOP, 24-pin SOIC and 28 pin PLCC package, top view.

# **Pin Description**

Refer to figure 8.

| PLCC | Symbol Description |                                                                                                                                                                                                         |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PTG                | <b>P</b> rogr. Transmit <b>G</b> ain. Left open transmit gain = -6.02 dB, connected to AGND transmit gain = -12.04 dB.                                                                                  |

| 2    | RRLY               | Ring Relay driver output. The relay coil may be connected to maximum +14V.                                                                                                                              |

| 3    | HP                 | Connection for <b>H</b> igh <b>P</b> ass filter capacitor, $C_{HP}$ . Other end of $C_{HP}$ connects to TIPX.                                                                                           |

| 4    | NC                 | No internal Connection                                                                                                                                                                                  |

| 5    | RINGX              | The TIPX and RINGX pins connect to the tip and ring leads of the two-wire interface via overvoltage                                                                                                     |

|      |                    | protection components and ring relay (and optional test relay).                                                                                                                                         |

| 6    | BGND               | Battery Ground, should be tied together with AGND.                                                                                                                                                      |

| 7    | TIPX               | The TIPX and RINGX pins connect to the tip and ring leads of the two-wire interface via overvoltage                                                                                                     |

|      |                    | protection components and ring relay (and optional test relay).                                                                                                                                         |

| 8    | VBAT               | Battery supply Voltage. Negative with respect to AGND.                                                                                                                                                  |

| 9    | VBAT2              | An optional second (2) <b>Bat</b> tery <b>V</b> oltage connects to this pin.                                                                                                                            |

| 10   | PSG                | <b>P</b> rogrammable <b>S</b> aturation <b>G</b> uard. The resistive part of the DC feed characteristic is programmed by a resistor connected from this pin to VBAT.                                    |

| 11   | NC                 | No internal Connection                                                                                                                                                                                  |

| 12   | LP                 | Connection for Low Pass filter capacitor, $C_{LP}$ . Other end of $C_{LP}$ connects to VBAT.                                                                                                            |

| 13   | DT                 | Input to the ring trip comparator. With DR more positive than DT the detector output, DET, is at logic level low, indicating off-hook condition. The external ring trip network connects to this input. |

| 14   | DR                 | Input to the ring trip comparator. With DR more positive than DT the detector output, DET, is at logic level low, indicating off-hook condition. The external ring trip network connects to this input. |

| 15<br>16<br>17 | C3<br>C2<br>C1 | C1, C2 and C3 are digital inputs (internal pull-up) controlling the SLIC operating states. Refer to section "Operating states" for details.                                                                                                                                                                           |

|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18             | DET            | <b>Det</b> ector output. Active low when indicating loop detection and ring trip, active high when indicating ground key detection.                                                                                                                                                                                   |

| 19             | NC             | No internal Connection                                                                                                                                                                                                                                                                                                |

| 20             | VCC            | +5 V power supply.                                                                                                                                                                                                                                                                                                    |

| 21             | PLD            | <b>P</b> rogrammable Loop <b>D</b> etector threshold. The loop detection threshold is programmed by a resistor connected from this pin to AGND.                                                                                                                                                                       |

| 22             | POV            | <b>P</b> rogrammable <b>O</b> verhead <b>V</b> oltage. If pin is left open: The overhead voltage is internally set to min 2.7 V in off-hook and min 1.1 V in On-hook. If a resistor is connected between this pin and AGND: the overhead voltage can be set to higher values.                                         |

| 23             | PLC            | <b>P</b> rog. <b>L</b> ine <b>C</b> urrent, the current limit,reference C in figure 13, is programmed by a resistor connected from this pin to AGND.                                                                                                                                                                  |

| 24             | REF            | A <b>Ref</b> erence, 49.9 k $\Omega$ , resistor should be connected from this pin to AGND.                                                                                                                                                                                                                            |

| 25             | NC             | No internal Connection                                                                                                                                                                                                                                                                                                |

| 26             | RSN            | Receive <b>S</b> umming <b>N</b> ode. 200 times the AC-current flowing into this pin equals the metallic (transversal) AC-current flowing from RINGX to TIPX. Programming networks for two-wire impedance and receive gain connect to the receive summing node. A resistor should be connected from this pin to AGND. |

| 27             | AGND           | Analog Ground, should be tied together with BGND.                                                                                                                                                                                                                                                                     |

| 28             | VTX            | Transmit vf output. The AC voltage difference between TIPX and RINGX, the AC metallic voltage, is reproduced as an unbalanced GND referenced signal at VTX with a gain of 0.5 (or 0.25, see pin PTG). The two-wire impedance programming network connects between VTX and RSN.                                        |

# **SLIC Operating States**

| State | C3 | C2 | C1 | SLIC operating state | Active detector                   |

|-------|----|----|----|----------------------|-----------------------------------|

| 0     | 0  | 0  | 0  | Open circuit         | -                                 |

| 1     | 0  | 0  | 1  | Ringing state        | Ring trip detector (active low)   |

| 2     | 0  | 1  | 0  | Active state         | Loop detector (active low)        |

| 3     | 0  | 1  | 1  | Active state         | Line voltage measurement (note 9) |

| 4     | 1  | 0  | 0  | Tip open state       | Loop detector (active low)        |

| 5     | 1  | 0  | 1  | Active state         | Ground key detector (active high) |

| 6     | 1  | 1  | 0  | Active reverse       | Loop detector (active low)        |

| 7     | 1  | 1  | 1  | Active reverse       | Ground key detector (active high) |

Table 1. SLIC operating states.

Figure 9. Simplified ac transmission circuit.

# **Functional Description** and Applications Information

# **Transmission**

#### General

A simplified ac model of the transmission circuits is shown in figure 9. Circuit analysis yields:

$$V_{TR} = \frac{V_{TX}}{G_{2-4}s} + I_{L} \cdot (2R_F + 2R_P)$$

(1)

$$\frac{V_{TX}}{Z_{T}} + \frac{V_{RX}}{Z_{RX}} = \frac{I_{L}}{\alpha_{RSN}}$$

(2)

$$V_{TR} = E_L - I_L \cdot Z_L \tag{3}$$

$V_{Tx}$  is a ground referenced version of the ac metallic voltage between the TIPX and RINGX terminals.

$G_{2-4S}$  is the programmable SLIC two-wire to four-wire gain (transmit direction). See note below.

$V_{TR}$  is the ac metallic voltage between tip and ring.

is the line open circuit ac metallic voltage.

I, is the ac metallic current.

is a fuse resistor.

is part of the SLIC protection

is the line impedance.

determines the SLIC TIPX to RINGX impedance at voice frequencies.

Z<sub>RX</sub> controls four- to two-wire gain. V<sub>RX</sub> is the analog ground referenced receive signal.

$\alpha_{\text{RSN}}$  is the receive summing node current to metallic loop current gain = 200.

Note that the SLICs two-wire to fourwire gain, G<sub>2-4S</sub>, is user programmable between two fix values. Refer to the datasheets for values on G<sub>2-4S</sub>.

#### **Two-Wire Impedance**

To calculate  $Z_{TR}$ , the impedance presented to the two-wire line by the SLIC including the fuse and protection resistors  $R_F$  and  $R_P$ , let  $V_{RX} = 0$ .

From (1) and (2):

$$Z_{TR} = \frac{Z_T}{\alpha_{RSN} \cdot G_{2-4S}} + 2R_F + 2R_P$$

Thus with  $Z_{TR},\,\alpha_{RSN},\,G_{\text{2-4S}},\,R_{\text{P}}$  and  $R_{\text{F}}$ known:

$$Z_T = \alpha_{RSN} \cdot G_{2-4S} \cdot (Z_{TR} - 2R_F - 2R_P)$$

#### Two-Wire to Four-Wire Gain

From (1) and (2) with  $V_{PY} = 0$ :

$$G_{2-4} = \frac{V_{TX}}{V_{TR}} = \frac{Z_T \ / \ \alpha_{RSN}}{\frac{Z_T}{\alpha_{RSN} \cdot G_{2-4S}} + 2R_F + 2R_P} \qquad \text{When choosing $R_{TX}$, make sure the output load of the VTX terminal is $>$20k\Omega$.}$$

#### Four-Wire to Two-Wire Gain

From (1), (2) and (3) with

$$E_L = 0$$

:

$$G_{4-2} = \frac{V_{TR}}{V_{RX}} =$$

$$-\frac{Z_T}{Z_{RX}} \cdot \frac{Z_L}{\frac{Z_T}{\alpha_{RSN}} + G_{2-4S} \cdot (Z_L + 2R_F + 2R_P)}$$

For applications where

$\rm Z_T/(\alpha_{RSN}\cdot G_{2.4S}) + 2R_F + 2R_P$  is chosen to be equal to  $\rm Z_L$  the expression for  $\rm G_{4.2}$

$$G_{4-2} = -\frac{Z_T}{Z_{RX}} \cdot \frac{1}{2G_{2-4S}}$$

#### Four-Wire to Four-Wire Gain

From (1), (2) and (3) with  $E_1 = 0$ :

$$G_{4-4} = \frac{V_{TX}}{V_{RX}} = -\frac{Z_T}{Z_{RX}} \cdot \frac{G_{2-4S} \cdot (Z_L + 2R_F + 2R_P)}{\frac{Z_T}{\alpha_{RSN}} + G_{2-4S} \cdot (Z_L + 2R_F + 2R_P)}$$

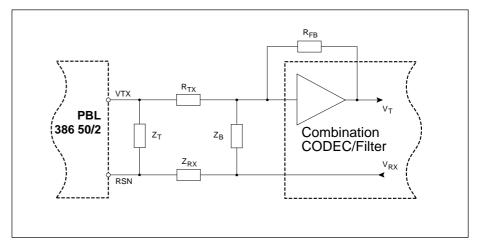

# **Hybrid Function**

The hybrid function can easily be implemented utilizing the uncommitted amplifier in conventional CODEC/filter combinations. Please, refer to figure 10. Via impedance Z<sub>B</sub> a current proportional to  $V_{\mbox{\scriptsize RX}}$  is injected into the summing node of the combination CODEC/filter amplifier. As can be seen from the expression for the four-wire to four-wire gain a voltage proportional to  $V_{RX}$  is returned to  $V_{Tx}$ . This voltage is converted by  $R_{Tx}$  to a current flowing into the same summing node. These currents can be made to

$$\frac{V_{TX}}{R_{TX}} + \frac{V_{RX}}{Z_B} = 0(E_L = 0)$$

The four-wire to four-wire gain,  $G_{4-4}$ , includes the required phase shift and thus the balance network Z<sub>R</sub> can be

$$\begin{split} Z_{B} &= -R_{TX} \cdot \frac{V_{RX}}{V_{TX}} = \\ R_{TX} \cdot \frac{Z_{RX}}{Z_{T}} \cdot \frac{\frac{Z_{T}}{\alpha_{RSN}} + G_{2-4S} \cdot (Z_{L} + 2R_{F} + 2R_{P})}{G_{2-4S} \cdot (Z_{L} + 2R_{F} + 2R_{P})} \end{split}$$

If calculation of the  $Z_{\scriptscriptstyle B}$  formula above yields a balance network containing an inductor, an alternate method is recommended. Contact Ericsson Microelectronics for assistance.

The PBL 386 50/2 SLIC may also be used together with programmable CODEC/filters. The programmable CODEC/filter allows for system controller adjustment of hybrid balance to accommodate different line impedances without change of hardware. In addition, the transmit and receive gain may be adjusted. Please, refer to the programmable CODEC/filter data sheets for design information.

#### **Longitudinal Impedance**

A feed back loop counteracts longitudinal voltages at the two-wire port by injecting longitudinal currents in opposing phase.

Thus longitudinal disturbances will appear as longitudinal currents and the TIPX and RINGX terminals will experience very small longitudinal voltage excursions, leaving metallic voltages well within the SLIC common mode range.

The SLIC longitudinal impedance per wire,  $Z_{\text{LoT}}$  and  $Z_{\text{LoR}}$ , appears as typically  $20\Omega$  to longitudinal disturbances. It should be noted that longitudinal currents may exceed the dc loop current without disturbing the vf transmission.

# Capacitors $C_{TC}$ and $C_{RC}$

The capacitors designated  $C_{\text{TC}}$  and  $C_{\text{RC}}$  in figure 12, connected between TIPX and ground as well as between RINGX and ground, can be used for RFI filtering.

The recommended value for  $C_{TC}$  and  $C_{RC}$  is 2200 pF. Higher capacitance values may be used, but care must be taken to prevent degradation of either longitudinal balance or return loss.  $C_{TC}$  and  $C_{RC}$  contribute to a metallic impedance of  $1/(\pi \cdot f \cdot C_{TC}) = 1/(\pi \cdot f \cdot C_{RC})$ , a TIPX to ground impedance of  $1/(2 \cdot \pi \cdot f \cdot C_{TC})$  and a RINGX to ground impedance of  $1/(2 \cdot \pi \cdot f \cdot C_{RC})$ .

Figure 10. Hybrid function.

#### AC - DC Separation Capacitor, C<sub>HP</sub>

The high pass filter capacitor connected between terminals HP and TIPX provides the separation of the ac signal from the dc part.  $C_{\rm HP}$  positions the low end frequency response break point of the ac loop in the SLIC. Refer to table 1 for recommended values of  $C_{\rm HP}$ .

Example: A  $C_{HP}$  value of 150 nF will position the low end frequency response 3dB break point of the ac loop at 1.8 Hz ( $f_{3dB}$ ) according to  $f_{3dB} = 1/(2 \cdot \pi \cdot R_{HP} \cdot C_{HP})$  where  $R_{HP} = 600 \text{ k}\Omega$ .

# **High-Pass Transmit Filter**

The capacitor  $C_{TX}$  in figure 12 connected between the VTX output and the CODEC/filter forms, together with  $R_{TX}$  and/or the input impedance of a programmable CODEC/filter, a high-pass RC filter. It is recommended to position the 3 dB break point of this filter between 30 and 80 Hz to get a faster response for the dc steps that may occur at DTMF signalling.

#### Capacitor CLP

The capacitor  $C_{LP}$ , which connects between the terminals CLP and VBAT, positions together with the resistive loop feed resistor  $R_{SG}$  (see section Battery Feed), the high end frequency break point of the low pass filter in the dc loop in the SLIC.  $C_{LP}$  together with  $R_{SG}$ ,  $C_{HP}$  and  $Z_{T}$  (see section Two-Wire Imped-

ance) forms the total two wire output impedance of the SLIC. The choise of these programmable components have an influence on the power supply rejection ratio (PSRR) from VBAT to the two wire side at sub-audio frequencies. At these frequencies capacitor  $C_{\rm LP}$  also influences the transversal to longitudinal balance in the SLIC. Table 1 suggests suitable values on  $C_{\rm LP}$  for different feeding characteristics. Typical values of the transversal to longitudinal balance (T-L bal.) at 200Hz is given in table 1 for the chosen values on  $C_{\rm LP}$ .

| R <sub>Feed</sub> | R <sub>ss</sub> | $C_{LP}$ | T-L bal.<br>@200Hz | C <sub>HP</sub> |

|-------------------|-----------------|----------|--------------------|-----------------|

| $[\Omega]$        | [k $\Omega$ ]   | [nF]     | [dB]               | [nF]            |

| 2.50              | 0               | 150      | -46                | 47              |

| 2.200             | 60.4            | 100      | -46                | 150             |

| 2.400             | 147             | 47       | -43                | 150             |

| 2.800             | 301             | 22       | -36                | 150             |

Table 1.  $R_{SG}$ ,  $C_{LP}$  and  $C_{HP}$  values for different feeding characteristics.

# **Battery Feed**

The PBL 386 50/2 SLIC emulate resistive loop feed, programmable between  $2.50\Omega$  and  $2.900~\Omega$ , with adjustable current limitation. In the current limited region the loop current has a slight slope corresponding to  $2.30~k\Omega$ , see figure 13 reference B.

The open loop voltage measured between the TIPX and RINGX terminals is tracking the battery voltage  $V_{Bat}$ . The signalling headroom, or overhead voltage  $V_{TRO}$ , is programmable with a resistor  $R_{\rm OV}$  connected between terminal POV on the SLIC and ground. Please refer to section "Programmable overhead voltage(POV)".

The battery voltage overhead,  $V_{OH}$ , depends on the programmed signal overhead voltage  $V_{TRO}$ .  $V_{OH}$  defines the TIP to RING voltage at open loop conditions according to  $V_{TR}$ (at  $I_L = 0$  mA) =  $|V_{Bat}|$  -  $V_{OH}$ .

Refer to table 2 for typical values on  $V_{\text{OH}}$  and  $V_{\text{OHVirt}}$ . The overhead voltage is changed when the line current is approaching open loop conditions. To ensure maximum open loop voltage, even with a leaking telephone line, this occurs at a line current of approximately 6 mA. When the overhead voltage has changed, the line voltage is kept nearly constant with a steep slope corresponding to  $2.25~\Omega(\text{reference G in figure 13})$ .

The virtual battery overhead, V<sub>OHVirt</sub>, is defined as the difference between the battery voltage and the crossing point of all possible resistive feeding slopes, see figure 13 reference J. The virtual battery overhead is a theoretical constant needed to be able to calculate the feeding characteristics.

| SLIC         | V <sub>OH(typ)</sub><br>[V] | V <sub>OHVirt(typ)</sub><br>[V] |

|--------------|-----------------------------|---------------------------------|

| PBL 386 50/2 | 3.0 +V <sub>TRO</sub>       | 4.9 +V <sub>TRO</sub>           |

Table 2. Battery overhead.

The resistive loop feed (reference D in figure 13) is programmed by connecting a resistor, R<sub>SG</sub>, between terminals PSG and VBAT according to the equation:

$$R_{\text{Feed}} = \frac{R_{\text{SG}} + 2.10^4}{200} + 2R_{\text{F}}$$

where  $R_{\text{Feed}}$  is in  $\Omega$  for  $R_{\text{SG}}$  and  $R_{\text{F}}$  in  $\Omega$ .

The current limit (reference C in figure 13) is adjusted by connecting a resistor,  $R_{\rm LC}$ , between terminal PLC and ground according to the equation:

$$R_{LC} = \frac{1000}{I_{LProg} + 4}$$

where  $R_{LC}$  is in  $k\Omega$  for  $I_{LProg}$  in mA. A second, lower battery voltage may be connected to the device at terminal VBAT2 to reduce short loop power dissipation. The SLIC automatically switches between the two battery supply voltages without need for external control. The silent battery switching occurs when the line voltage passes the value |VB2| -  $40 \cdot I_L$  -  $(V_{OHVirt}$  -1.3), if  $I_{\rm l} > 6$  mA.

For correct functionality it is important to connect the terminal VBAT2 to the second power supply via the diode  $D_{\text{VB2}}$  in figure 12.

An optional diode  $D_{BB}$  connected between terminal VB and the VB2 power supply, see figure 12, will make sure that the SLIC continues to work on the second battery even if the first battery voltage disappears.

If a second battery voltage is not used, VBAT2 is connected to VBAT on the SLIC and  $\rm C_{VB2},\, \rm D_{BB}$  and  $\rm D_{VB2}$  are removed.

# Metering applications

For designs with metering applications please contact Ericsson Microelectronics for assistance.

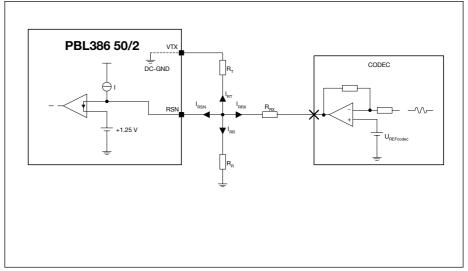

#### **CODEC Receive Interface**

The PBL 386 50/2 SLIC have got a completely new receive interface at the four wire side which makes it possible to reduce the number of capacitors in the applications and to fit both single and dual battery feed CODECs. The RSN terminal, connecting to the CODEC

receive output via the resistor  $R_{\rm RX}$ , is dc biased with +1.25V. This makes it possible to compensate for currents floating due to dc voltage differences between RSN and the CODEC output without using any capacitors. This is done by connecting a resistor  $R_{\rm R}$  between the RSN terminal and ground. With current directions defined as in figure 14, current summation gives:

$$-I_{RSN} = I_{RT} + I_{RRX} + I_{RR} =$$

$$\frac{1,25}{R_T} + \frac{1,25 - V_{CODEC}}{R_{RX}} + \frac{1,25}{R_{R}}$$

where  $V_{\text{CODEC}}$  is the reference voltage of the CODEC at the receive output. From this equation the resistor  $R_{\text{R}}$  can be calculated as

$$R_{R} = \frac{1,25}{-I_{RSN} - \frac{1,25}{R_{T}} - \frac{1,25 - V_{CODEC}}{R_{RY}}}$$

For values on  $I_{\text{RSN}}$ , see table 3. The resistor  $R_{\text{R}}$  has no influence on the ac transmission.

| SLIC         | I <sub>RSN</sub> [μΑ] |

|--------------|-----------------------|

| PBL 386 50/2 | -155                  |

Table 3. The SLIC internal bias current with the direction of the current defined as positive when floating into the terminal RSN.

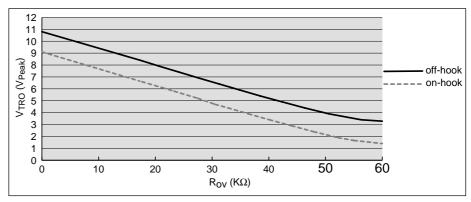

#### Programmable overhead voltage(POV)

With the POV function the overhead voltage can be increased.

If the POV pin is left open the overhead voltage is internally set to 3.2  $V_{\text{Peak}}$  in off-

Figure 11. Programmable overhead voltage (POV).  $R_1 = 600 \Omega$  or  $\infty$ .

hook and 1.3  $V_{Peak}$  on-hook. If a resistor  $R_{OV}$  is connected between the POV pin and AGND, the overhead voltage can be set to higher values, typical values can be seen in figure 11. The  $R_{OV}$  and corresponding  $V_{TRO}$  (signal headroom) are typical values for THD <1% and the signal frequency 1000Hz.

Observe that the 4-wire output terminal  $V_{TX}$  can not handle more than  $3.2 \, V_{Peak}$ . So if the gain 2-wire to 4-wire is -6.02dB, 6.4  $V_{Peak}$  is maximum also for the 2-wire side. Signal levels between 6.4 and 12.8  $V_{Peak}$  on the 2-wire side can be handled with the PTG shorted so that the gain  $G_{2-4S}$  become -12.04dB. Please note that the 2-wire impedance,  $R_R$  and the 4-wire to 4-wire gain has to be recalculated if the PTG is shorted.

Please note that the maximum signal current at the 2-wire side can not be greater than 29 mA.

#### How to use POV:

- Decide what overhead voltage(V<sub>TRO</sub>) is needed. The POV function is only needed if the overhead voltage exceeds 3.2 V<sub>Rook</sub>

- 2. In figure 11 the corresponding  $R_{\rm OV}$  for the decided  $V_{\rm TRO}$  can be found.

- If the overhead voltage exceeds 6.4 V<sub>Peak</sub>, the G<sub>2-4S</sub> gain has to be changed to -12.04dB by connecting the PTG pin to AGND. Please note that the two-wire impedance, R<sub>R</sub> and the 4-wire to 4-wire gain has to be recalculated.

#### **Analog Temperature Guard**

The widely varying environmental conditions in which SLICs operate may lead to the chip temperature limitations being exceeded. The PBL 386 50/2 SLIC reduce the dc line current when the chip temperature reaches approximately 145°C and increases it again automatically when the temperature drops. Accordingly transmission is not lost under high ambient temperature conditions.

The detector output, DET, is forced to a logic low level when the temperature guard is active.

Figure 12. Single-channel subscriber line interface with PBL 386 50/2 and combination CODEC/filter.

Figure 13. Battery feed characteristics (without the protection resistors on the line).

# **Loop Monitoring Functions**

The loop current, ground key and ring trip detectors report their status through a common output. DET. The detector to be connected to DET is selected via the three bit wide control interface C1, C2 and C3. Please refer to section Control Inputs for a description of the control interface.

# **Loop Current Detector**

The loop current detector is indicating that the telephone is off hook and that current is flowing in the loop by putting the output DET to a logical low level when selected. The loop current threshold value, I, Th, at which the loop current detector changes state is programmable by selecting the value of resistor R<sub>LD</sub>. R<sub>LD</sub> connects between pin PLD and ground

and is calculated according to

$$R_{LD} = \frac{500}{I_{I,Th}}$$

The current detector is internally filtered and is not influenced by the ac signal at the two wire side.

#### **Ground Key Detector**

The ground key detector is indicating when the ground key is pressed (active) by putting the output pin DET to a logical high level when selected. The ground key detector circuit senses the difference in TIPX and RINGX currents. When the current at the RINGX side exceeds the current at the TIPX side with the threshold value the detector is triggered. For threshold current values, please refer to the datasheet.

# **Ring Trip Detector**

Ring trip detection is accomplished by connecting an external network to a comparator in the SLIC with inputs DT and DR. The ringing source can be balanced or unbalanced superimposed on V<sub>B</sub> or GND. The unbalanced ringing source may be applied to either the ring lead or the tip lead with return via the other wire. A ring relay driven by the SLIC ring relay driver connects the ringing source to tip and ring.

The ring trip function is based on a polarity change at the comparator input when the line goes off-hook. In the onhook state no dc current flows through the loop and the voltage at comparator input DT is more positive than the voltage at input DR. When the line goes off-hook, while the ring relay is ener-

gized, dc current flows and the comparator input voltage reverses polarity.

Figure 12 gives an example of a ring trip detection network. This network is applicable, when the ring voltage is superimposed on V<sub>B</sub> and is injected on the ring lead of the two-wire port. The dc voltage across sense resistor R<sub>RT</sub> is monitored by the ring trip comparator input DT and DR via the network R<sub>1</sub>, R<sub>2</sub>,  $R_3$ ,  $R_4$ ,  $C_1$  and  $C_2$ . With the line on-hook (no dc current) DT is more positive than DR and the DET output will report logic level high, i.e. the detector is not tripped. When the line goes off-hook, while ringing, a dc current will flow through the loop including sense resistor R<sub>RT</sub> and will cause input DT to become more negative than input DR. This changes output DET to logic level low, i.e. tripped detector condition. The system controller (or line card processor) responds by de-energizing the ring relay, i.e. ring trip.

Complete filtering of the 20 Hz ac component at terminal DT and DR is not necessary. A toggling DET output can be examined by a software routine to determine the duty cycle. When the DET output is at logic level low for more than half the time, off-hook condition is indicated.

# Relay driver

The PBL 386 50/2 SLIC incorporates a ring relay driver designed as open collector (npn) with a current sinking capability of 50mA. The drive transistor emitter is connected to BGND. The relay driver has an internal zener diode clamp for inductive kickback voltages. Care must be taken when using the relay driver together with relays that have high impedance.

# **Control Inputs**

The PBL 386 50/2 SLIC have three digital control inputs, C1, C2 and C3.

A decoder in the SLIC interprets the control input condition and sets up the commanded operating state.

C1 to C3 are internal pull-up inputs.

#### **Open Circuit State**

In the Open Circuit State the TIPX and RINGX line drive amplifiers as well as other circuit blocks are powered down. This causes the SLIC to present a high impedance to the line. Power dissipation is at a minimum and no detectors are active.

Figure 14. CODEC receive interface.

# **Ringing State**

The ring relay driver and the ring trip detector are activated and the ring trip detector is indicating off hook with a logic low level at the detector output.

The SLIC is in the active normal state.

#### **Active States**

TIPX is the terminal closest to ground and sources loop current while RINGX is the more negative terminal and sinks loop current. Vf signal transmission is normal. The loop current or the ground key detector is activated. The loop current detector is indicating off hook with a logic low level and the ground key detector is indicating active ground key with a logic high level present at the detector output.

In PBL 386 50/2 a line voltage measurement feature is available in the active state, which may be used for line length estimations or for line test purposes. The line voltage is presented on the detector output as a pulse at logic high level with a pulsewidth of 5.5  $\mu s/V$ . To start the line voltage measurement this mode has to be entered from the Active State with the loop or ground key detector active. The pulse presented at the DET output proportional to the line voltage measuring mode.

#### **Tip Open State**

Tip Open State is used for ground start signalling.

In this state the SLICs present a high impedance to the line on the TIPX pin

and the programmed dc characteristic, with the longitudinal current compensation (see section Longitudinal Impedance) not active, to the line on the RINGX pin.

The loop current detector is active.

#### **Active Polarity Reversal State**

TIPX and RINGX polarity is reversed from the Active State: RINGX is the terminal closest to ground and sources loop current while TIPX is the more negative terminal and sinks current. Vf signal transmission is normal. The loop current or the ground key detector is activated. The loop current detector is indicating off hook with a logic low level and the ground key detector is indicating active ground key with a logic high level present at the detector output.

# **Overvoltage Protection**

The PBL 386 50/2 SLIC must be protected against overvoltages on the telephone line caused by lightning, ac power contact and induction. Refer to Maximum Ratings, TIPX and RINGX terminals, for maximum allowable continuous and transient currents that may be applied to the SLIC.

# **Secondary Protection**

The circuit shown in figure 12 utilizes series resistors together with a programmable overvoltage protector (e.g. PowerInnovations TISPPBL2),

(e.g. PowerInnovations TISPPBL2) serving as a secondary protection.

The TISPPBL2 is a dual forward-conducting buffered p-gate overvoltage protector. The protector gate references the protection (clamping) voltage to negative supply voltage (i e the battery voltage,  $V_B$ ). As the protection voltage will track the negative supply voltage the overvoltage stress on the SLIC is minimized.

Positive overvoltages are clamped to ground by a diode. Negative overvoltages are initially clamped close to the SLIC negative supply rail voltage and the protector will crowbar into a low voltage on-state condition, by firing an internal thyristor.

A gate decoupling capacitor, C<sub>GG</sub>, is