## HIGH-SPEED 64K x 16 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM

IDT709289L

### **Features**

- True Dual-Ported memory cells which allow simultaneous access of the same memory location

- High-speed clock to data access

- Commercial: 7.5/9/12ns (max.)

- Low-power operation

- IDT709289L Active: 1.2W (typ.) Standby: 2.5mW (typ.)

- ◆ Flow-Through or Pipelined output mode on either Port via the FT/PIPE pins

- Counter enable and reset features

- Dual chip enables allow for depth expansion without additional logic

- Full synchronous operation on both ports

- 4ns setup to clock and 0ns hold on all control, data, and address inputs

- Data input, address, and control registers

- Fast 7.5ns clock to data out in the Pipelined output mode

- Self-timed write allows fast cycle time

- 12ns cycle time, 83MHz operation in Pipelined output mode

- Separate upper-byte and lower-byte controls for multiplexed bus and bus matching compatibility

- \* TTL- compatible, single 5V (±10%) power supply

- Industrial temperature range (-40°C to +85°C) is available for selected speeds

- Available in a 100-pin Thin Quad Flatpack (TQFP) package

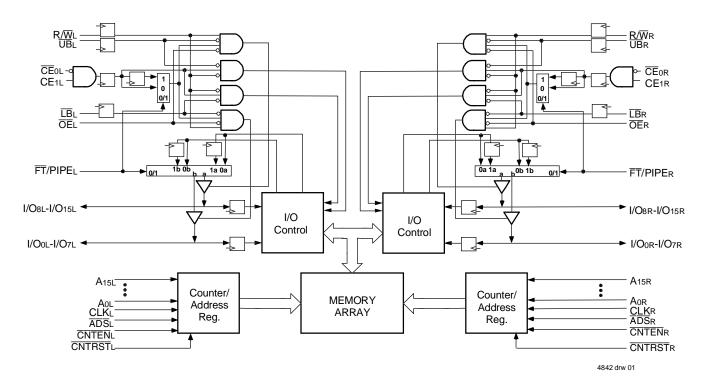

## **Functional Block Diagram**

**JANUARY 2001**

## **Description**

The IDT709289 is a high-speed 64K x 16 bit synchronous Dual-Port RAM. The memory array utilizes Dual-Port memory cells to allow simultaneous access of any address from both ports. Registers on control, data, and address inputs provide minimal setup and hold times. The timing latitude provided by this approach allows systems to be designed with very short cycle times.

With an input data register, the IDT709289 has been optimized for applications having unidirectional or bidirectional data flow in bursts. An automatic power down feature, controlled by  $\overline{\text{CE}}$ 0 and CE1, permits the on-chip circuitry of each port to enter a very low standby power mode. Fabricated using IDT's CMOS high-performance technology, these devices typically operate on only 1.2W of power.

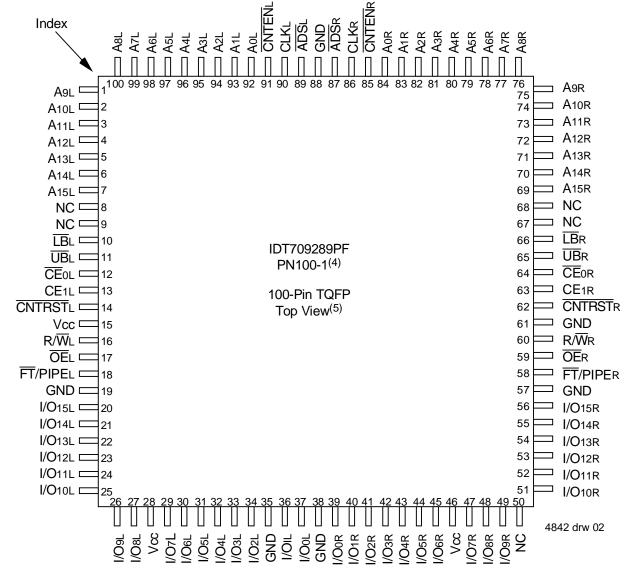

- 1. All Vcc pins must be connected to power supply.

- 2. All GND pins must be connected to ground.

- 3. Package body is approximately 14mm x 14mm x 1.4mm

- 4. This package code is used to reference the package diagram.

- 5. This text does not indicate orientation of the actual part-marking.

## **Pin Names**

| Left Port          | Right Port             | Names                 |

|--------------------|------------------------|-----------------------|

| Œ0L, CE1L          | CEOR, CE1R             | Chip Enables          |

| $R/\overline{W}_L$ | R/W̄R                  | Read/Write Enable     |

| ŌĒL                | <del>OE</del> R        | Output Enable         |

| A0L - A15L         | A0R - A15R             | Address               |

| I/O0L - I/O15L     | I/O0R - I/O15R         | Data Input/Output     |

| CLKL               | CLKR                   | Clock                 |

| <del>UB</del> L    | <del>UB</del> R        | Upper Byte Select     |

| ŪB∟                | <u>IB</u> <sub>R</sub> | Lower Byte Select     |

| ĀDS <sub>L</sub>   | <del>ADS</del> R       | Address Strobe        |

| CNTENL             | <u>CNTEN</u> R         | Counter Enable        |

| CNTRSTL            | CNTRST <sub>R</sub>    | Counter Reset         |

| FT/PIPEL           | FT/PIPER               | Flow-Through/Pipeline |

| V                  | 'cc                    | Power                 |

| G                  | ND                     | Ground                |

4842 tbl 01

# Truth Table I—Read/Write and Enable Control(1,2,3)

| ŌĒ | CLK      | Œ | CE <sub>1</sub> | ŪB | ĪВ | R/W | Upper Byte<br>I/O <sub>8-15</sub> | Lower Byte<br>I/O <sub>0-7</sub> | Mode                     |

|----|----------|---|-----------------|----|----|-----|-----------------------------------|----------------------------------|--------------------------|

| Х  | 1        | Н | Х               | Х  | Х  | Х   | High-Z                            | High-Z                           | Deselected—Power Down    |

| Х  | 1        | Х | L               | Χ  | Χ  | Χ   | High-Z                            | High-Z                           | Deselected—Power Down    |

| Х  | 1        | L | Н               | Н  | Н  | Х   | High-Z                            | High-Z                           | Both Bytes Deselected    |

| Х  | 1        | L | Н               | L  | Н  | L   | DATAIN                            | High-Z                           | Write to Upper Byte Only |

| Х  | 1        | L | Н               | Н  | L  | L   | High-Z                            | DATAIN                           | Write to Lower Byte Only |

| Х  | 1        | L | Н               | L  | L  | L   | DATAIN                            | DATAIN                           | Write to Both Bytes      |

| L  | 1        | L | Н               | L  | Н  | Н   | <b>DATA</b> out                   | High-Z                           | Read Upper Byte Only     |

| L  | <b>↑</b> | L | Н               | Н  | L  | Н   | High-Z                            | DATAout                          | Read Lower Byte Only     |

| L  | <b>↑</b> | L | Н               | L  | L  | Н   | DATAout                           | DATAout                          | Read Both Bytes          |

| Н  | Χ        | L | Н               | L  | L  | Χ   | High-Z                            | High-Z                           | Outputs Disabled         |

NOTES:

1. "H" = VIH, "L" = VIL, "X" = Don't Care.

2. ADS, CNTEN, CNTRST = X.

3.  $\overline{\text{OE}}$  is an asynchronous input signal.

4842 tbl 02

## Truth Table II—Address Counter Control<sup>(1,2,6)</sup>

| Address | Previous<br>Address | Addr<br>Used | CLK | ĀDS              | CNTEN            | CNTRST | I/O <sup>(3)</sup> | Mode                                                  |

|---------|---------------------|--------------|-----|------------------|------------------|--------|--------------------|-------------------------------------------------------|

| Х       | Х                   | 0            | 1   | Х                | Χ                | L      | Dvo(0)             | Counter Reset to Address 0                            |

| An      | Х                   | An           | 1   | L <sup>(4)</sup> | Χ                | Н      | DVO(n)             | External Address Loaded into Counter                  |

| An      | Ар                  | Ар           | 1   | Н                | Н                | Н      | Dvo(p)             | External Address Blocked—Counter Disabled (Ap reused) |

| Х       | Ар                  | Ap + 1       | 1   | Н                | L <sup>(5)</sup> | Н      | Dvo(p+1)           | Counter Enable—Internal Address Generation            |

#### NOTES:

4842 tbl 03

- 1. "H" = VIH, "L" = VIL, "X" = Don't Care.

- 2.  $\overline{CE}_0$ ,  $\overline{LB}$ ,  $\overline{UB}$ , and  $\overline{OE}$  = VIL; CE1 and R/ $\overline{W}$  = VIH.

- 3. Outputs configured in Flow-Through Output mode: if outputs are in Pipelined mode the data out will be delayed by one cycle.

- 4.  $\overline{ADS}$  is independent of all other signals including  $\overline{CE}_0$ ,  $\overline{CE}_1$ ,  $\overline{UB}$  and  $\overline{LB}$ .

- 5. The address counter advances if ONTEN = VIL on the rising edge of CLK, regardless of all other signals including OEO, CEI, UB and LB.

- 6. While an external address is being loaded (ADS = VIL),  $RI\overline{W} = VIH$  is recommended to ensure data is not written arbitrarily.

# Recommended Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature <sup>(2)</sup> | GND | Vcc               |

|------------|---------------------------------------|-----|-------------------|

| Commercial | 0°C to +70°C                          | 0V  | 5.0V <u>+</u> 10% |

| Industrial | -40°C to +85°C                        | 0V  | 5.0V <u>+</u> 10% |

NOTES:

842 tbl 04

- Industrial temperature: for other speeds, packages and powers contact your sales

- 2. This is the parameter Ta. This is the "instant on" case temperature.

# Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |

|--------|--------------------|---------------------|------|--------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | V    |

| GND    | Ground             | 0                   | 0    | 0      | V    |

| VIH    | Input High Voltage | 2.2                 | _    | 6.0(1) | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(2)</sup> |      | 0.8    | V    |

4842 tbl 05

### NOTES:

- 1. VTERM must not exceed Vcc + 10%.

- 2.  $VIL \ge -1.5V$  for pulse width less than 10ns.

# Absolute Maximum Ratings(1)

| Symbol               | Rating                                     | Commercial<br>& Industrial | Unit |

|----------------------|--------------------------------------------|----------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0               | >    |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                | °C   |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | °C   |

| Іоит                 | DC Output<br>Current                       | 50                         | mA   |

NOTES:

2.

4842 tbl 06

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may

cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect reliability.

- 2. VTERM must not exceed Vcc + 10% for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period of VTERM  $\geq$  Vcc + 10%.

## **Capacitance**<sup>(1)</sup> (TA = +25°C, f = 1.0MHz)

| Symbol              | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|---------------------|--------------------|---------------------------|------|------|

| CIN                 | Input Capacitance  | $V_{IN} = 3dV$            | 9    | pF   |

| Соит <sup>(3)</sup> | Output Capacitance | Vout = 3dV                | 10   | pF   |

**NOTES:**1. These parameters are determined by device characterization, but are not

- production tested.3dV references the interpolated capacitance when the input and output switch from

- OV to 3V or from 3V to OV.

3. Cout also references CI/O.

4842 tbl 08

# DC Electrical Characteristics Over the Operating Temperature Supply Voltage Range (Vcc = 5.0V ± 10%)

|        |                                      |                                                        | 7092 |      |      |

|--------|--------------------------------------|--------------------------------------------------------|------|------|------|

| Symbol | Parameter                            | Test Conditions                                        | Min. | Max. | Unit |

| Iu     | Input Leakage Current <sup>(1)</sup> | Vcc = 5.5V, Vin = 0V to Vcc                            | _    | 5    | μA   |

| ILO    | Output Leakage Current               | $\overline{CE}_0$ = ViH or CE1 = ViL, Vout = 0V to Vcc | _    | 5    | μA   |

| Vol    | Output Low Voltage                   | IoL = +4mA                                             | _    | 0.4  | V    |

| Voh    | Output High Voltage                  | Iон = -4mA                                             | 2.4  | _    | V    |

#### NOTE

1. At  $Vcc \le 2.0V$  input leakages are undefined.

DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range $^{(3,6)}$  (Vcc = 5V ± 10%)

| Tomporatare and earphy Tomage Italige |                                                                                        |                                                                                                                                                                                                                                                          |       |    | (100 - 01 - 1070) |              |                     |              |                     |      |      |

|---------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|-------------------|--------------|---------------------|--------------|---------------------|------|------|

|                                       |                                                                                        |                                                                                                                                                                                                                                                          |       |    |                   | 89L7<br>Only | 7092<br>Com'l       | 89L9<br>Only | 70928<br>Com'l      |      |      |

| Symbol                                | Parameter                                                                              | Test Condition                                                                                                                                                                                                                                           | Versi | on | Тур.(4)           | Max.         | Typ. <sup>(4)</sup> | Max.         | Тур. <sup>(4)</sup> | Max. | Unit |

| Icc                                   | Dynamic Operating<br>Current                                                           | CEL and CER= VIL                                                                                                                                                                                                                                         | COM'L | L  | 275               | 465          | 250                 | 400          | 230                 | 355  | mA   |

|                                       | (Both Ports Active)                                                                    | Outputs Disabled<br>f = fMAX <sup>(1)</sup>                                                                                                                                                                                                              | IND   | L  | _                 | _            | _                   |              |                     | _    |      |

| ISB1                                  | Standby Current                                                                        | CEL = CER = VIH                                                                                                                                                                                                                                          | COM'L | L  | 95                | 150          | 80                  | 135          | 70                  | 110  | mA   |

|                                       | (Both Ports - TTL $f = fMAX$<br>Level Inputs)                                          | $f = fMAX^{(1)}$                                                                                                                                                                                                                                         | IND   | L  |                   | _            |                     |              |                     | _    |      |

| ISB2                                  | Standby Current                                                                        | <u>CE</u> "A" = V <sub>IL</sub> and                                                                                                                                                                                                                      | COM'L | L  | 200               | 295          | 175                 | 275          | 150                 | 240  | mA   |

| (One Port - TTL<br>Level Inputs)      | CE"B" = VIH <sup>(3)</sup> Active Port Outputs         Disabled, f=fMAX <sup>(1)</sup> | IND                                                                                                                                                                                                                                                      | L     | 1  |                   | 1            | _                   | 1            | -                   |      |      |

| ISB3                                  | Full Standby Current                                                                   | Both Ports CER and                                                                                                                                                                                                                                       | COM'L | L  | 0.5               | 3            | 0.5                 | 3            | 0.5                 | 3    | mA   |

| (Both Ports -<br>CMOS Level Inputs)   |                                                                                        | $ \begin{array}{l} \text{CEL} \geq \text{VCC} - 0.2\text{V} \\ \text{VIN} \geq \text{VCC} - 0.2\text{V} \text{ or} \\ \text{VIN} \leq 0.2\text{V},  f = 0^{(2)} \\ \end{array} $                                                                         | IND   | L  | _                 | _            |                     |              | _                   | _    |      |

| ISB4                                  | Full Standby Current                                                                   | CE"A" ≤ 0.2V and                                                                                                                                                                                                                                         | COM'L | L  | 190               | 290          | 170                 | 270          | 140                 | 225  | mA   |

| (One Port -<br>CMOS Level Inputs)     |                                                                                        | $\begin{array}{l} \overline{\text{CE}}\text{'B"} \geq \text{VCC} - 0.2\text{V}^{(5)} \\ \text{VN} \geq \text{VCC} - 0.2\text{V or} \\ \text{VN} \leq 0.2\text{V}, \text{ Active Port} \\ \text{Outputs Disabled, } f = f_{\text{MAX}}^{(1)} \end{array}$ | IND   | L  | _                 |              | —                   |              | _                   |      |      |

- 1. At f = fMAX, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tcvc, using "AC TEST CONDITIONS" at input levels of GND to 3V.

- 2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

- 3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 4. Vcc = 5V, TA = 25°C for Typ, and are not production tested. lcc pc(f=0) = 150mA (Typ).

- 5.  $\overline{CE}x = V_{IL} \text{ means } \overline{CE}_{0x} = V_{IL} \text{ and } CE_{1x} = V_{IH}$

- $\overline{CE}x = VIH \text{ means } \overline{CE}0x = VIH \text{ or } CE1x = VIL$

- $\overline{\text{CE}} x \le 0.2 \text{V}$  means  $\overline{\text{CE}} \text{ox} \le 0.2 \text{V}$  and  $\text{CE} 1x \ge \text{Vcc} 0.2 \text{V}$

- $\overline{CE}x \ge Vcc 0.2V$  means  $\overline{\overline{CE}}0x \ge Vcc 0.2V$  or  $CE1x \le 0.2V$

- "X" represents "L" for left port or "R" for right port.

- 6. Industrial temperature: for other speeds, packages and powers contact your sales office.

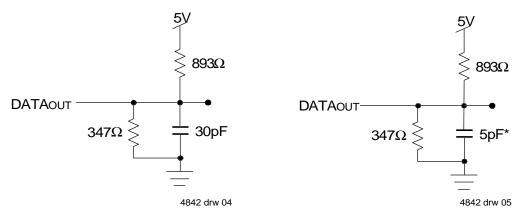

### **AC Test Conditions**

| <u> </u>                      |                   |

|-------------------------------|-------------------|

| Input Pulse Levels            | GND to 3.0V       |

| Input Rise/Fall Times         | 3ns Max.          |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

| Output Load                   | Figures 1,2 and 3 |

4842 tbl 10

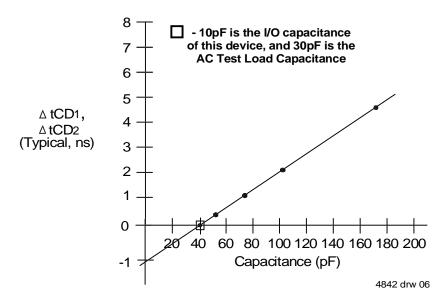

Figure 1. AC Output Test load.

Figure 2. Output Test Load (For tcklz, tckHz, tolz, and toHz). \*Including scope and jig.

Figure 3. Typical Output Derating (Lumped Capacitive Load).

AC Electrical Characteristics Over the Operating Temperature Range (Read and Write Cycle Timing) $^{(3,4)}$  (Vcc = 5V ± 10%, TA = 0°C to +70°C)

|                | and write Cycle Timing) (Vcc                      | 709  | 289L7<br>'I Only | 7092 | 89L9<br>I Only | 7092<br>Com' |      |      |

|----------------|---------------------------------------------------|------|------------------|------|----------------|--------------|------|------|

| Symbol         | Parameter                                         | Min. | Max.             | Min. | Max.           | Min.         | Max. | Unit |

| tcyc1          | Clock Cycle Time (Flow-Through) <sup>(2)</sup>    | 22   | _                | 25   | _              | 30           | _    | ns   |

| tcyc2          | Clock Cycle Time (Pipelined) <sup>(2)</sup>       | 12   | _                | 15   | _              | 20           | _    | ns   |

| tcн1           | Clock High Time (Flow-Through) <sup>(2)</sup>     | 7.5  | _                | 12   | _              | 12           | _    | ns   |

| tCL1           | Clock Low Time (Flow-Through) <sup>(2)</sup>      | 7.5  | _                | 12   | _              | 12           | _    | ns   |

| tCH2           | Clock High Time (Pipelined) <sup>(2)</sup>        | 5    | _                | 6    | _              | 8            | _    | ns   |

| tCL2           | Clock Low Time (Pipelined) <sup>(2)</sup>         | 5    | _                | 6    | _              | 8            | _    | ns   |

| tr             | Clock Rise Time                                   | _    | 3                | _    | 3              | _            | 3    | ns   |

| tr             | Clock Fall Time                                   | _    | 3                | _    | 3              | _            | 3    | ns   |

| tsa            | Address Setup Time                                | 4    | _                | 4    | _              | 4            | _    | ns   |

| tha            | Address Hold Time                                 | 0    | _                | 1    | _              | 1            | _    | ns   |

| tsc            | Chip Enable Setup Time                            | 4    | _                | 4    | _              | 4            | _    | ns   |

| tнc            | Chip Enable Hold Time                             | 0    | _                | 1    | _              | 1            | _    | ns   |

| tsв            | Byte Enable Setup Time                            | 4    | _                | 4    | _              | 4            | _    | ns   |

| tнв            | Byte Enable Hold Time                             | 0    | _                | 1    | _              | 1            | _    | ns   |

| tsw            | R/W Setup Time                                    | 4    | _                | 4    | _              | 4            | _    | ns   |

| thw            | R/W Hold Time                                     | 0    |                  | 1    |                | 1            | _    | ns   |

| tsp            | Input Data Setup Time                             | 4    | _                | 4    | _              | 4            | _    | ns   |

| tho            | Input Data Hold Time                              | 0    | _                | 1    | _              | 1            | _    | ns   |

| tsad           | ADS Setup Time                                    | 4    | _                | 4    | _              | 4            | _    | ns   |

| thad           | ADS Hold Time                                     | 0    | _                | 1    | _              | 1            | _    | ns   |

| tscn           | CNTEN Setup Time                                  | 4    | _                | 4    | _              | 4            | _    | ns   |

| then           | CNTEN Hold Time                                   | 0    | _                | 1    | _              | 1            | _    | ns   |

| tsrst          | CNTRST Setup Time                                 | 4    | _                | 4    | _              | 4            | _    | ns   |

| thrst          | CNTRST Hold Time                                  | 0    | _                | 1    | _              | 1            | _    | ns   |

| toe            | Output Enable to Data Valid                       | _    | 9                | _    | 12             | _            | 12   | ns   |

| tolz           | Output Enable to Output Low-Z <sup>(1)</sup>      | 2    | _                | 2    | _              | 2            | _    | ns   |

| tонz           | Output Enable to Output High-Z <sup>(1)</sup>     | 1    | 7                | 1    | 7              | 1            | 7    | ns   |

| tcD1           | Clock to Data Valid (Flow-Through) <sup>(2)</sup> | _    | 18               | _    | 20             | _            | 25   | ns   |

| tcD2           | Clock to Data Valid (Pipelined) <sup>(2)</sup>    |      | 7.5              | _    | 9              | _            | 12   | ns   |

| toc            | Data Output Hold After Clock High                 | 2    |                  | 2    | _              | 2            | _    | ns   |

| tскнz          | Clock High to Output High-Z <sup>(1)</sup>        | 2    | 9                | 2    | 9              | 2            | 9    | ns   |

| tcklz          | Clock High to Output Low-Z <sup>(1)</sup>         | 2    |                  | 2    | _              | 2            | _    | ns   |

| Port-to-Port [ | Delay                                             |      |                  | •    |                |              | •    |      |

| tcwdd          | Write Port Clock High to Read Data Delay          | _    | 28               | _    | 35             | _            | 40   | ns   |

| tccs           | Clock-to-Clock Setup Time                         | _    | 10               | _    | 15             | _            | 15   | ns   |

NOTES:

1842 tbl 11

<sup>1.</sup> Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2). This parameter is guaranteed by device characterization, but is not production tested.

<sup>2.</sup> The Pipelined output parameters (tcyc2, tcp2) to either the Left or Right ports when FT/PIPE = VIH. Flow-Through parameters (tcyc1, tcp1) apply when FT/PIPE = VIL for that port.

<sup>3.</sup> All input signals are synchronous with respect to the clock except for the asynchronous Output Enable (OE), FT/PIPER and FT/PIPEL.

<sup>4.</sup> Industrial temperature: for other speeds, packages and powers contact your sales office.

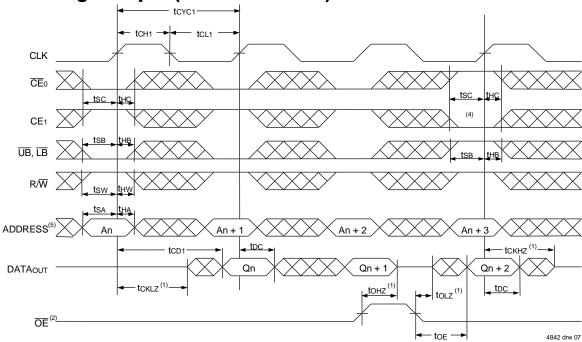

# Timing Waveform of Read Cycle for Flow-Through Output (FT/PIPE"x" = VIL)(3,7)

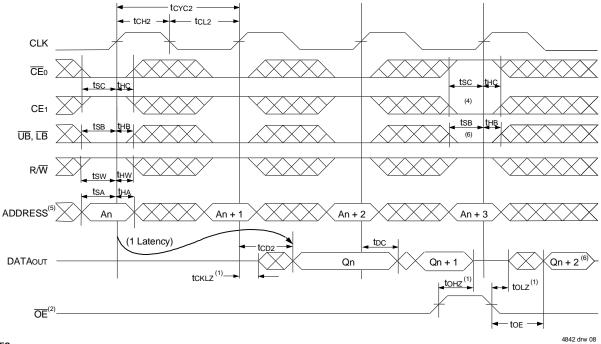

# Timing Waveform of Read Cycle for Pipelined Operation $(\overline{FT}/PIPE"x" = VIH)^{(3,7)}$

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 2.  $\overline{\text{OE}}$  is asynchronously controlled; all other inputs are synchronous to the rising clock edge.

- 3. ADS = VIL, CNTEN and CNTRST = VIH.

- 4. The output is disabled (High-Impedance state) by  $\overline{\text{CE}}_0$  = Vін,  $\overline{\text{CE}}_1$  = Vін,  $\overline{\text{UB}}_2$  = Vін, or  $\overline{\text{LB}}_3$  = Vін following the next rising edge of the clock. Refer to Truth Table 1.

- Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers

are for reference use only.

- 6. If  $\overline{\sf UB}$  or  $\overline{\sf LB}$  was HIGH, then the Upper Byte and/or Lower Byte of DATAout for Qn + 2 would be disabled (High-Impedance state).

- 7. "X" here denotes Left or Right port. The diagram is with respect to that port.

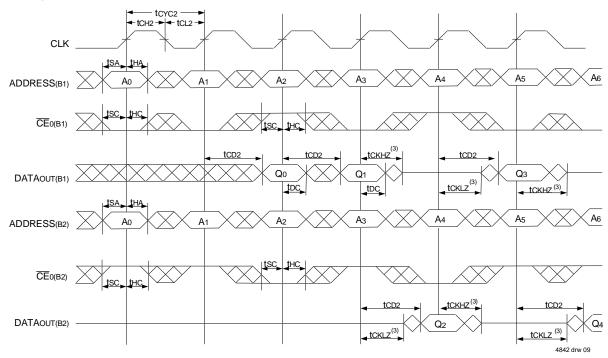

# Timing Waveform of a Bank Select Pipelined Read<sup>(1,2)</sup>

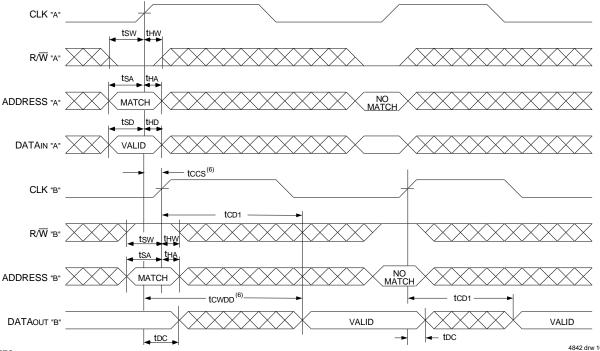

# Timing Waveform of Write with Port-to-Port Flow-Through Read<sup>(4,5,7)</sup>

- B1 Represents Bank #1; B2 Represents Bank #2. Each Bank consists of one IDT709289 for this waveform, and are setup for depth expansion in this example. ADDRESS(B1) = ADDRESS(B2) in this situation.

- 2.  $\overline{\text{UB}}$ ,  $\overline{\text{LB}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{ADS}}$  = VIL; CE1(B1), CE1(B2), R/ $\overline{\text{W}}$ ,  $\overline{\text{CNTEN}}$ , and  $\overline{\text{CNTRST}}$  = VIH.

- 3. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 4.  $\overline{CE}_0$ ,  $\overline{UB}$ ,  $\overline{LB}$ , and  $\overline{ADS}$  = VIL; CE1,  $\overline{CNTEN}$ , and  $\overline{CNTRST}$  = VIH.

- 5.  $\overline{OE}$  = V<sub>IL</sub> for the Right Port, which is being read from.  $\overline{OE}$  = V<sub>IH</sub> for the Left Port, which is being written to.

- If tccs ≤ maximum specified, then data from right port READ is not valid until the maximum specified for tcwbb.

If tccs > maximum specified, then data from right port READ is not valid until tccs + tcb1. tcwbb does not apply in this case.

- 7. All timing is the same for both Left and Right ports. Port "A" may be either Left or Right port. Port "B" is the opposite from Port "A".

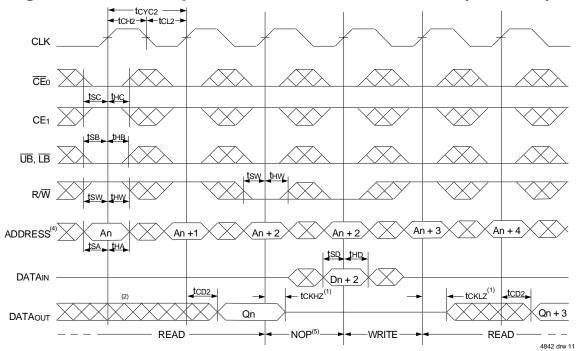

# Timing Waveform of Pipelined Read-to-Write-to-Read ( $\overline{OE} = V_{IL}$ )<sup>(3)</sup>

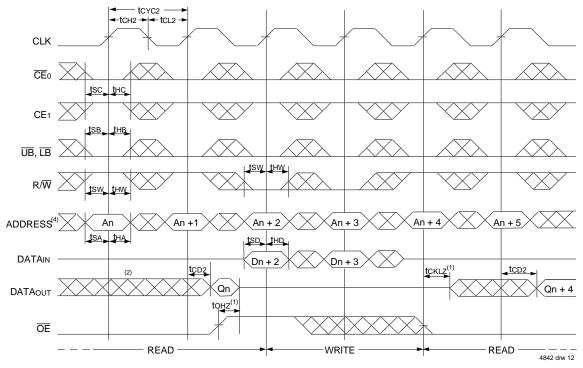

# Timing Waveforn of Pipelined Read-to-Write-to-Read (OE Controlled)(3)

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 2. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

- 3.  $\overline{\text{CE}}_0$ ,  $\overline{\text{UB}}$ ,  $\overline{\text{LB}}$ , and  $\overline{\text{ADS}}$  = VIL; CE1,  $\overline{\text{CNTEN}}$ , and  $\overline{\text{CNTRST}}$  = VIH. "NOP" is "No Operation".

- 4. Addresses do not have to be accessed sequentially since  $\overline{ADS} = VIL$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

- 5. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

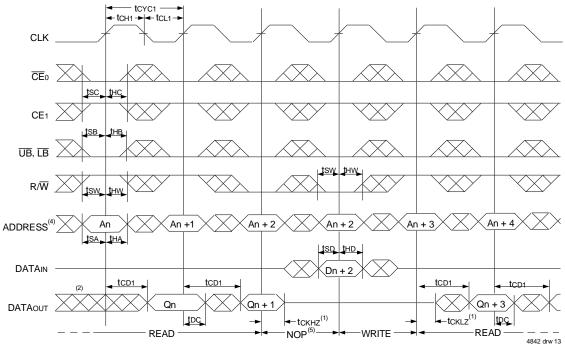

# Timing Waveform of Flow-Through Read-to-Write-to-Read ( $\overline{OE} = V_{IL}$ )<sup>(3)</sup>

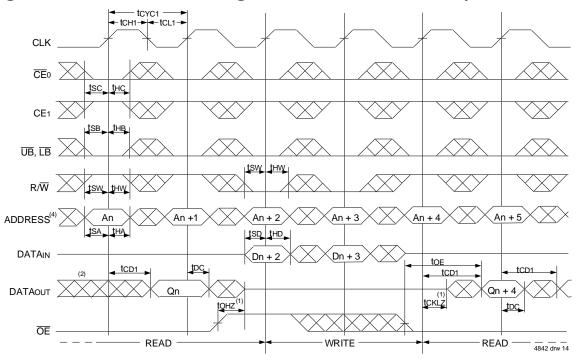

# Timing Waveform of Flow-Through Read-to-Write-to-Read ( $\overline{\text{OE}}$ Controlled) $^{(3)}$

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 2. <u>Output state</u> (High, Low, or High-impedance is determined by the previous cycle control signals.

- 3.  $\overline{\text{CE}}_0$ ,  $\overline{\text{UB}}$ ,  $\overline{\text{LB}}$ , and  $\overline{\text{ADS}}$  = VIL;  $\overline{\text{CE}}_1$ ,  $\overline{\text{CNTEN}}$ , and  $\overline{\text{CNTRST}}$  =  $\overline{\text{VIH}}$ . "NOP" is "No Operation".

- 4. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

- 5. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

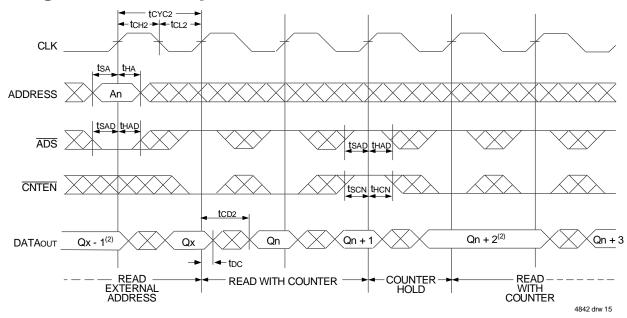

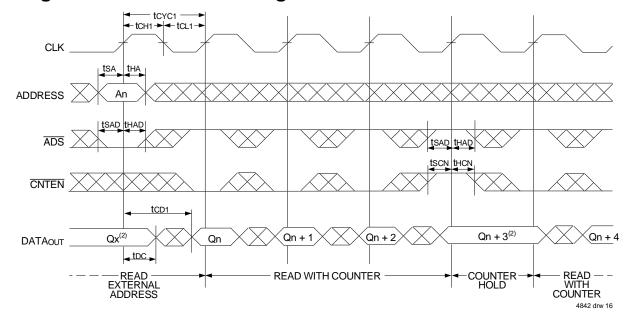

# Timing Waveform of Pipelined Read with Address Counter Advance<sup>(1)</sup>

## Timing Waveform of Flow-Through Read with Address Counter Advance<sup>(1)</sup>

- 1.  $\overline{CE}_0$ ,  $\overline{OE}$ ,  $\overline{UB}$ , and  $\overline{LB}$  = VIL; CE1, R/ $\overline{W}$ , and  $\overline{CNTRST}$  = VIH.

- 2. If there is no address change via  $\overline{ADS} = VIL$  (loading a new address) or  $\overline{CNTEN} = VIL$  (advancing the address), i.e.  $\overline{ADS} = VIH$  and  $\overline{CNTEN} = VIH$ , then the data output remains constant for subsequent clocks.

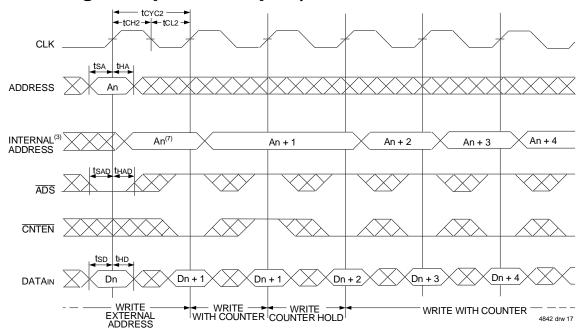

# Timing Waveform of Write with Address Counter Advance (Flow-Through or Pipelined Outputs)<sup>(1)</sup>

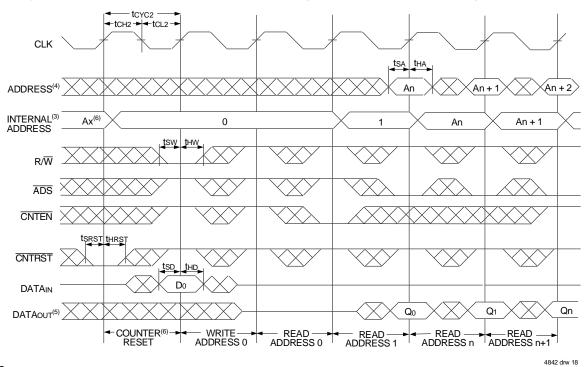

# Timing Waveform of Counter Reset (Pipelined Outputs)(2)

- 1.  $\overline{CE}_0$ ,  $\overline{UB}$ ,  $\overline{LB}$ , and  $R/\overline{W} = V_{IL}$ ;  $CE_1$  and  $\overline{CNTRST} = V_{IH}$ .

- 2.  $\overline{CE}_0$ ,  $\overline{UB}$ ,  $\overline{LB}$  = VIL; CE1 = VIH.

- 3. The "Internal Address" is equal to the "External Address" when  $\overline{ADS} = VIL$  and equals the counter output when  $\overline{ADS} = VIH$ .

- 4. Addresses do not have to be accessed sequentially since  $\overline{ADS} = ViL$  constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

- 5. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

- 6. No dead cycle exists during counter reset. A READ or WRITE cycle may be coincidental with the counter reset cycle.

- 7. CNTEN = VIL advances Internal Address from 'An' to 'An +1'. The transition shown indicates the time required for the counter to advance. The 'An +1' Address is written to during this cycle.

## **A Functional Description**

The IDT709289 provides a true synchronous Dual-Port Static RAM interface. Registered inputs provide minimal set-up and hold times on address, data, and all critical control inputs. All internal registers are clocked on the rising edge of the clock signal, however, the self-timed internal write pulse is independent of the LOW to HIGH transition of the clock signal.

An asynchronous output enable is provided to ease asynchronous bus interfacing. Counter enable inputs are also provided to stall the operation of the address counters for fast interleaved memory applications.

$\overline{\text{CE}}\text{O} = \text{VIH}$  or CE1 = VIL for one clock cycle will power down the internal circuitry to reduce static power consumption. Multiple chip enables allow easier banking of multiple IDT709289's for depth expansion configurations. When the Pipelined output mode is enabled, two cycles are required with  $\overline{\text{CE}}\text{O} = \text{VIL}$  and CE1 = VIH to reactivate the outputs.

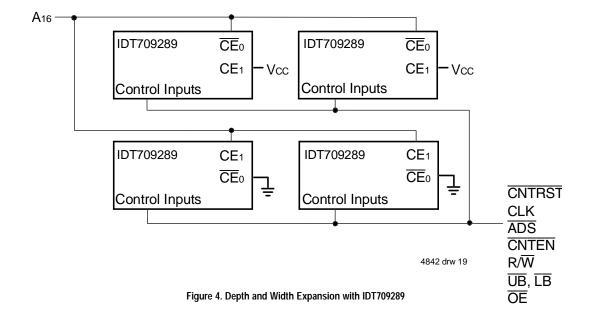

## **Depth and Width Expansion**

The IDT709289 features dual chip enables (refer to Truth Table I) in order to facilitate rapid and simple depth expansion with no requirements for external logic. Figure 4 illustrates how to control the various chip enables in order to expand two devices in depth.

The 709289 can also be used in applications requiring expanded width, as indicated in Figure 4. Since the banks are allocated at the discretion of the user, the external controller can be set up to drive the input signals for the various devices as required to allow for 32-bit or wider applications.

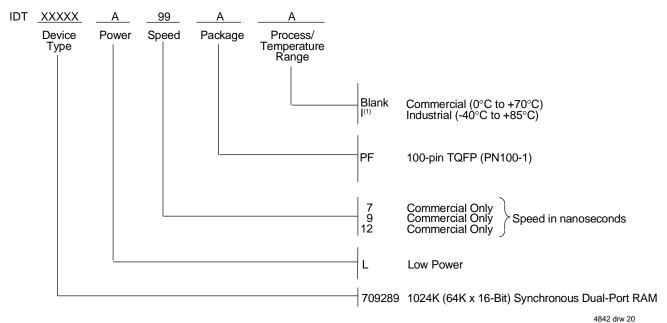

## **Ordering Information**

NOTE:

Industrial temperature range is available.

For specific speeds, packages and powers contact your sales office.

# **Datasheet Document History**

9/30/99: Initial Public Release 11/10/99: Replaced IDT logo

12/22/99: Page 1 Added missing diamond

1/5/01: Page 4 Changed information in Truth Table II

Increased storage temperature parameter

Clarified TA parameter

Page 5 DC Electrical parameters-changed wording from "open" to "disabled"

Changed ±200mV to 0mV in notes Removed Preliminary specification

CORPORATE HEADQUARTERS

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-611 6 fax: 408-492-8674

www.idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

*for Tech Support:* 831-754-4613

DualPortHelp@idt.com