# MOS INTEGRATED CIRCUIT $\mu$ PD17068

# 4-BIT SINGLE-CHIP MICROCONTROLLER CONTAINING IMAGE DISPLAY CONTROLLER AND PLL FREQUENCY SYNTHESIZER FOR DIGITAL TUNING SYSTEMS

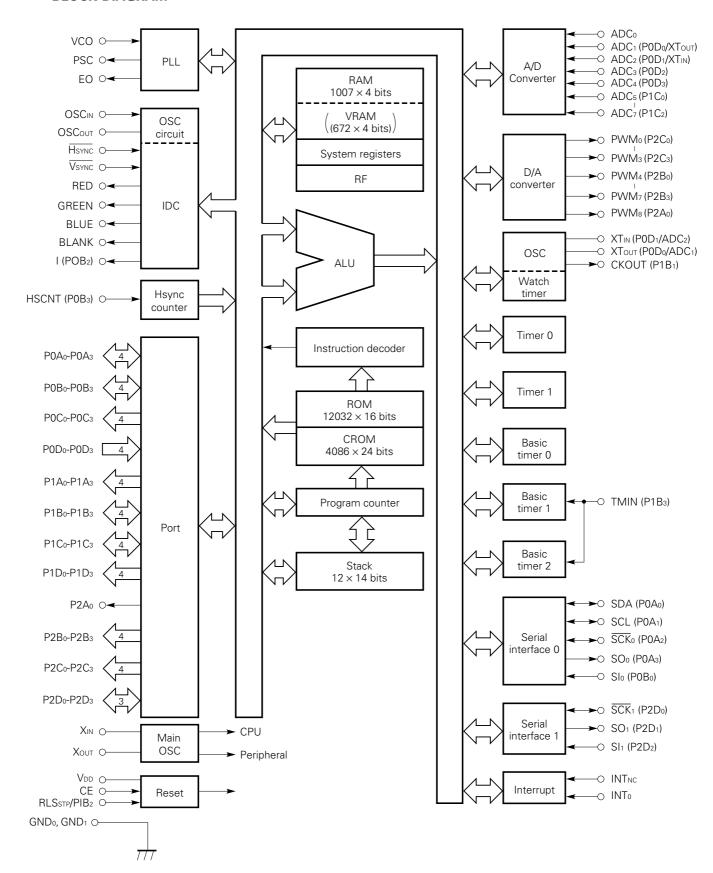

The  $\mu$ PD17068 is a 4-bit single-chip microcontroller for digital tuning systems. It contains an image display controller (IDC) that supports many types of display, and a PLL synthesizer.

The CPU of the  $\mu$ PD17068 is capable of 4-bit parallel addition, logical operations, bit tests, setting/resetting of a carry flag, and supports a powerful interrupt function and timer function.

The image display controller for on-screen display is user-programmable, allowing a range of displays to be programmed.

The peripheral hardware includes a full complement of I/O ports, controlled with powerful I/O instructions, as well as a serial interface, a 6-bit A/D converter, and an 8-bit D/A converter (PWM output).

#### **FEATURES**

• Program memory (ROM) : 24K bytes (12032  $\times$  16 bits) • Character ROM (CROM) :  $4086 \times 24$  bits (255 characters)

Data memory (RAM) : 1007 × 4 bits

• Video RAM (VRAM) :  $672 \times 4$  bits (can be used for data memory)

Address stackInterrupt stack2 levels

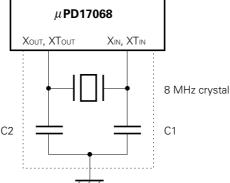

• Instruction execution time : 2  $\mu$ s (when an 8 MHz crystal is used)

· PLL frequency synthesizer

· 8-bit serial interface

(2 channels: One for two-wire or three-wire mode, compatible with I<sup>2</sup>C bus, and one for three-wire mode only)

- D/A converter: 8 bits × 9 lines (PWM output)

- A/D converter: 6 bits × 8 lines

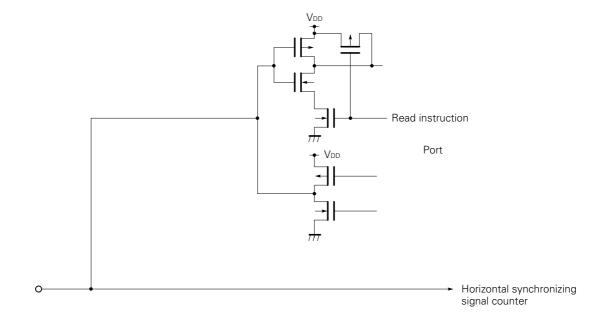

- · Horizontal synchronizing signal counter

- Commercial power supply frequency counter

- · Power-failure detection circuit and power-on reset circuit

- Interrupt input for remote-controller signal (with noise canceler)

- User-programmable image display controller (IDC)

Displayed characters: Up to 192 per screen (more characters can be displayed when the use of the entire

screen is specified with a program)

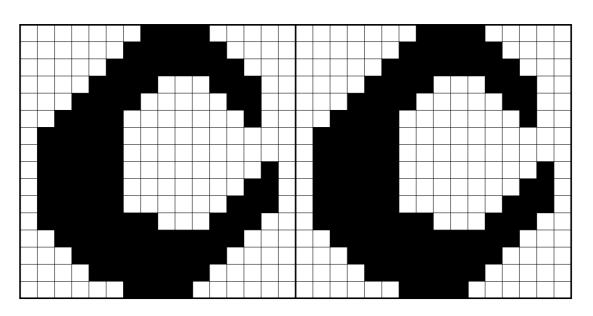

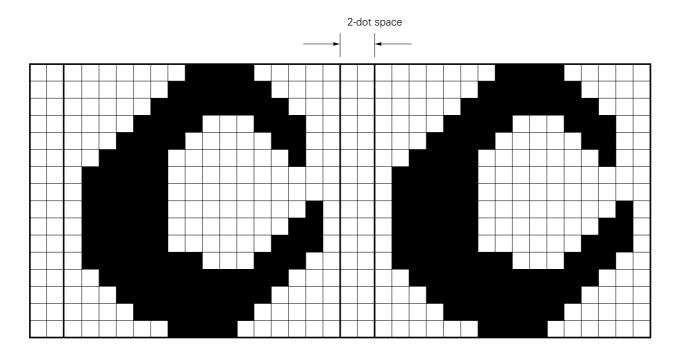

Display mode :  $16 \times 16$  dots in 15 lines  $\times$  24 columns

14 × 16 dots in 17 lines × 24 columns

Character patterns : 255

Character format :  $16 \times 16$  dots or  $14 \times 16$  dots

Colors : 15

Character sizes : 16 sizes for height (can be specified per line)

24 sizes for width (can be specified per character)

Many I/O ports

I/O : 19 ports

Input only : 4 ports

Output only : 21 ports

Operating supply voltage:  $5 \text{ V} \pm 10 \text{ \%}$

· Low power dissipation by use of CMOS technology

The information in this document is subject to change without notice.

# **ORDERING INFORMATION**

| Part number                                      | Package                                 | Quality grade |

|--------------------------------------------------|-----------------------------------------|---------------|

| μPD17068GF-×××-3BA                               | 100-pin plastic QFP (14 × 20 mm)        | Standard      |

| $\mu$ PD17068GF-E $	imes$ -3BA $^{	extbf{Note}}$ | 100-pin plastic QFP (14 $\times$ 20 mm) | Standard      |

**Note** Product supporting an I<sup>2</sup>C bus interface. When using the I<sup>2</sup>C bus interface (including implementation with a program that does not use peripheral hardware), make this point clear to your NEC sales representative when ordering mask options.

Remark xxx is a ROM code.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# **FUNCTION OVERVIEW**

| ltem                       |           | Function                                                                                                                                    |

|----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Program memory (R          | ROM)      | • 24K bytes (12032 × 16 bits)                                                                                                               |

|                            |           | Table reference area: $12032 \times 16$ bits                                                                                                |

| Character ROM (CRO         | OM)       | • $4086 \times 24$ bits (255 characters)                                                                                                    |

| Data memory                | RAM       | • 1007 $\times$ 4 bits (including area also used for VRAM)                                                                                  |

|                            |           | Data buffers: $4 \times 4$ bits, general-purpose registers: $16 \times 4$ bits                                                              |

| Video RAM (VRAM)           |           | • 672 $\times$ 4 bits (can be used for data memory (RAM))                                                                                   |

| System registers           |           | • 12 × 4 bits                                                                                                                               |

| Register files             |           | • 12 × 4 bits                                                                                                                               |

| General-purpose port       | registers | • 12 × 4 bits                                                                                                                               |

| Instruction execution      | n time    | • 2 $\mu$ s (when 8 MHz crystal is used)                                                                                                    |

| Stack levels               |           | 12 levels (stack manipulation possible)                                                                                                     |

| General-purpose po         | rts       | • I/O : 19 ports                                                                                                                            |

|                            |           | Input only : 4 ports                                                                                                                        |

|                            |           | Output only : 21 ports                                                                                                                      |

| IDC<br>(Image Display Cont | troller)  | Displayed characters: Up to 192 per screen (more characters can be displayed when the use of the entire screen is specified with a program) |

|                            |           | • Display mode : $16 \times 16$ dots in 15 lines $\times$ 24 columns                                                                        |

|                            |           | 14 × 16 dots in 17 lines × 24 columns                                                                                                       |

|                            |           | Character patterns : 255 (user-programmable)                                                                                                |

|                            |           | Character format : 16 × 16 dots or 14 × 16 dots     (2-dot interval can be specified between characters.)                                   |

|                            |           | • Colors : 15                                                                                                                               |

|                            |           | Character sizes : 16 different heights (can be specified per line)                                                                          |

|                            |           | 24 different widths (can be specified per character)                                                                                        |

| PLL frequency synth        | nesizer   | Frequency division method: Pulse swallow                                                                                                    |

|                            |           | Reference frequency : 5, 6.25, 10, 12.5, and 25 kHz                                                                                         |

|                            |           | Contains a charge pump for an external low-pass filter                                                                                      |

|                            |           | Phase comparator : Unlock can be detected with a program.                                                                                   |

|                            |           | The delay for the unlock flip-flop is selectable.                                                                                           |

| Serial interface           |           | • 2 channels                                                                                                                                |

|                            |           | Serial interface 0 (two-wire or three-wire mode, compatible with I <sup>2</sup> C bus)                                                      |

|                            |           | Serial interface 1 (three-wire mode only)                                                                                                   |

| D/A converter              |           | 8 bits × 9 lines (PWM output with withstand voltage of 12.5 V max.)                                                                         |

| A/D converter              |           | + 6 bits $\times$ 8 lines (successive approximation system with software)                                                                   |

| Interrupts                 |           | 10 channels (maskable interrupts)                                                                                                           |

|                            |           | External interrupts: 3 channels (INTo, INToc, and Vsync/Hsync)                                                                              |

|                            |           | Internal interrupts : 7 channels (timers 0 and 1, serial interfaces 0 and 1, basic timer 2, VRAM pointer, and timer 0 overflow)             |

| Item           | Function                                                                  |

|----------------|---------------------------------------------------------------------------|

| Timers         | Timer 0 : 10 $\mu$ s to 204.75 ms (interrupt)                             |

|                | Timer 1 : 1 $\mu$ s to 256 ms (interrupt)                                 |

|                | Basic timer 0: 1, 5, and 100 ms (carry)                                   |

|                | Basic timer 1 : 125 $\mu$ s, 1 ms, 5 ms, 100 ms, and external (carry)     |

|                | Basic timer 2 : 125 $\mu$ s, 1 ms, 5 ms, 100 ms, and external (interrupt) |

|                | Watch timer : Day, hour, minute, and second (count value)                 |

| Reset          | Power-on reset                                                            |

|                | Reset with the CE pin (by switching the CE pin from low to high)          |

|                | Power-failure detection function                                          |

| Supply voltage | 5 V±10%                                                                   |

| Package        | 100-pin plastic QFP (14 × 20 mm)                                          |

Remark Parentheses for timers indicate how to obtain the elapsed time for each timer.

Interrupt : Receiving an interrupt

Carry : Detecting the state of the carry flip-flop

Count value : Reading the count value

#### **BLOCK DIAGRAM**

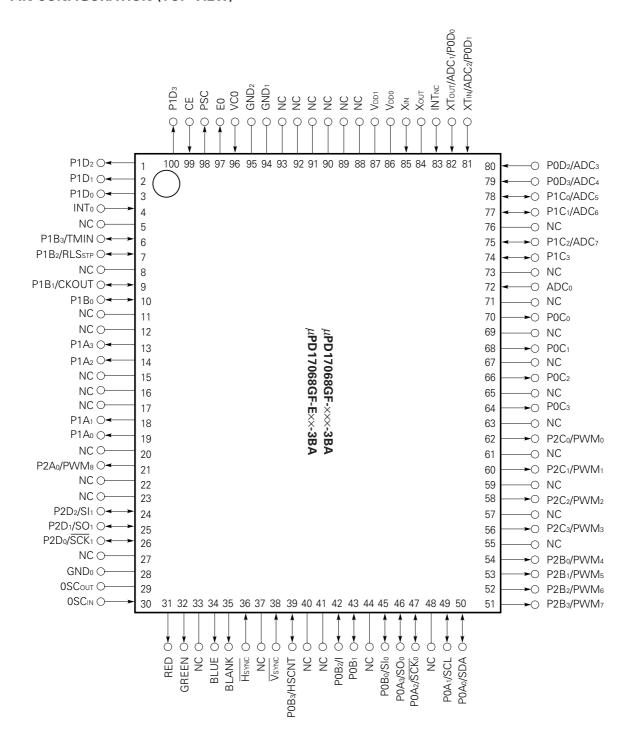

#### **PIN CONFIGURATION (TOP VIEW)**

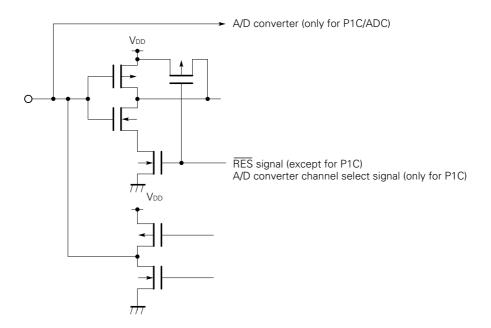

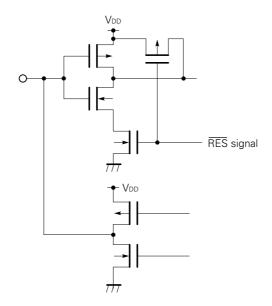

#### **PINS**

HSYNC

ADC<sub>0</sub> - ADC<sub>7</sub> P1C<sub>0</sub> - P1C<sub>3</sub> : Port 1C : A/D converter input P1D<sub>0</sub> - P1D<sub>3</sub> **BLANK** : Blanking signal output : Port 1D **BLUE** : Character signal output P2A<sub>0</sub> : Port 2A CE : Chip enable P2B<sub>0</sub> - P2B<sub>3</sub> : Port 2B CKOUT P2C<sub>0</sub> - P2C<sub>3</sub> : Port 2C : Watch timer adjustment P2D<sub>0</sub> - P2D<sub>2</sub> : Port 2D output **PSC** EO : Error output : Pulse swallow control output GND<sub>0</sub>, GND<sub>1</sub>, GND<sub>2</sub> : Ground PWMo - PWM8 : Pulse width modulation output RED **GREEN** : Character signal output : Character signal output **HSCNT** : Input for horizontal RLSSTP : Input for clock stop release signal synchronizing signal SCL : Shift clock I/O

SCK<sub>0</sub>, SCK<sub>1</sub> counter : Shift clock I/O : Serial data I/O : Horizontal synchronizing SDA : Serial data input signal input Slo, Sl1

SO<sub>0</sub>, SO<sub>1</sub> : Serial data output : Character signal output

INTo, INTNC : Input for external **TMIN** : Event input for basic timer 1 or 2

interrupt request signal

OSCIN, OSCOUT : LC oscillation I/O for IDC VCO : Local oscillation input P0A<sub>0</sub> - P0A<sub>3</sub> : Port 0A V<sub>DD0</sub>, V<sub>DD1</sub> : Main power supply

P0B<sub>0</sub> - P0B<sub>3</sub> : Port 0B VSYNC : Vertical synchronizing signal

P0C<sub>0</sub> - P0C<sub>3</sub> : Port 0C input P0D<sub>0</sub> - P0D<sub>3</sub> : Port 0D XIN, XOUT : Main clock oscillation I/O

P1A<sub>0</sub> - P1A<sub>3</sub> : Port 1A XTIN, XTOUT : Watch timer oscillation I/O P1B<sub>0</sub> - P1B<sub>3</sub> : Port 1B

# **CONTENTS**

| 1. | PIN F               | FUNCTIO | ONS                                                             | 17 |  |  |  |

|----|---------------------|---------|-----------------------------------------------------------------|----|--|--|--|

|    | 1.1                 | LIST O  | F PIN FUNCTIONS                                                 | 17 |  |  |  |

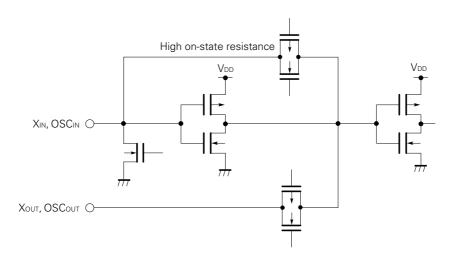

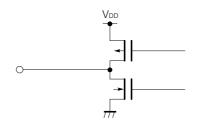

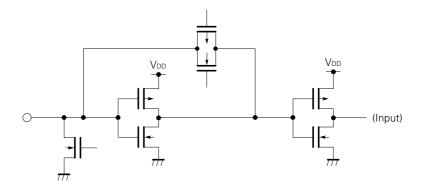

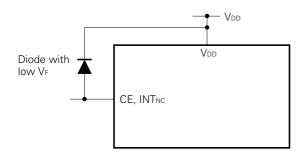

|    | 1.2                 | EQUIV   | ALENT CIRCUIT OF EACH PIN                                       | 2  |  |  |  |

|    | 1.3                 | HANDI   | LING UNUSED PINS                                                | 26 |  |  |  |

|    | 1.4                 | NOTES   | ON USE OF THE CE AND INTNC PINS                                 | 28 |  |  |  |

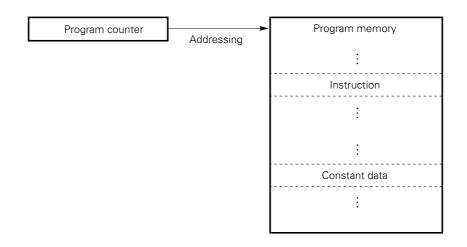

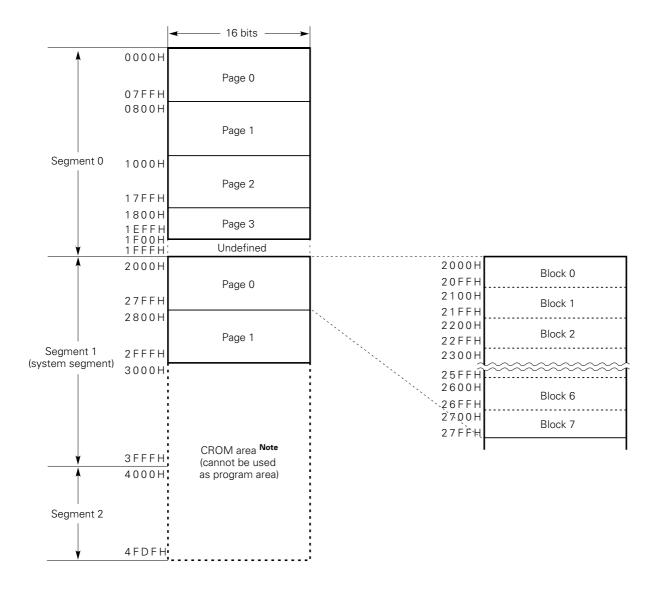

| 2. | PRO                 | GRAM N  | ЛЕМОRY (ROM)                                                    | 29 |  |  |  |

|    | 2.1                 | OUTLI   | NE OF PROGRAM MEMORY                                            | 29 |  |  |  |

|    | 2.2                 | PROGE   | RAM MEMORY CONFIGURATION                                        | 30 |  |  |  |

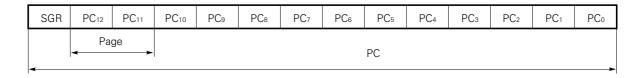

|    | 2.3                 | PROGE   | RAM COUNTER                                                     | 31 |  |  |  |

|    |                     | 2.3.1   | Program Counter Configuration                                   | 3′ |  |  |  |

|    |                     | 2.3.2   | Segment Register (SGR)                                          | 31 |  |  |  |

|    | 2.4                 | PROGE   | RAM FLOW                                                        | 31 |  |  |  |

|    |                     | 2.4.1   | Branch Instructions                                             | 31 |  |  |  |

|    |                     | 2.4.2   | Subroutines                                                     | 32 |  |  |  |

|    |                     | 2.4.3   | Table Reference                                                 | 32 |  |  |  |

|    |                     | 2.4.4   | System Call                                                     | 32 |  |  |  |

|    | 2.5                 | NOTES   | ON USE OF PROGRAM MEMORY                                        | 33 |  |  |  |

|    |                     | 2.5.1   | Program Counter and Program Memory Size                         | 33 |  |  |  |

|    |                     | 2.5.2   | Last Address of Each Segment                                    | 33 |  |  |  |

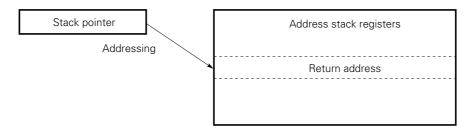

| 3. | ADDRESS STACK (ASK) |         |                                                                 |    |  |  |  |

| ٠. | 3.1                 |         | NE OF ADDRESS STACK                                             |    |  |  |  |

|    | 3.2                 |         | SS STACK REGISTERS (ASR)                                        | 34 |  |  |  |

|    | 3.2                 |         | POINTER (SP)                                                    | 36 |  |  |  |

|    | 3.3                 | 3.3.1   | Configuration and Function of Stack Pointer                     | 36 |  |  |  |

|    | 3.4                 |         | ESS STACK OPERATION                                             | 37 |  |  |  |

|    | 3.4                 | 3.4.1   | Subroutine Call Instruction ("CALL addr" or "CALL @AR") and     | 37 |  |  |  |

|    |                     | 3.4.1   | Return Instruction ("RET" or "RETSK")                           | 37 |  |  |  |

|    |                     | 3.4.2   | Table Reference Instruction ("MOVT DBF, @AR")                   |    |  |  |  |

|    |                     | 3.4.2   | Interrupt Reception and Return Instruction ("RETI")             | 37 |  |  |  |

|    |                     | 3.4.4   | Address Stack Manipulation Instructions ("PUSH AR", "POP AR")   |    |  |  |  |

|    |                     | 3.4.5   | System Call Instruction ("SYSCAL entry") and Return Instruction | 31 |  |  |  |

|    |                     | 3.4.5   | ("RET" or "RETSK")                                              | 37 |  |  |  |

|    | 3.5                 | NOTES   | ON USE OF ADDRESS STACK                                         | 37 |  |  |  |

|    | 3.5                 | 3.5.1   | Nesting Level                                                   | 37 |  |  |  |

|    |                     |         |                                                                 |    |  |  |  |

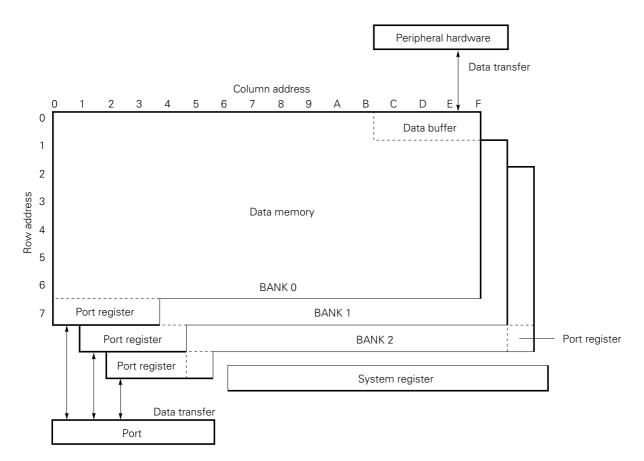

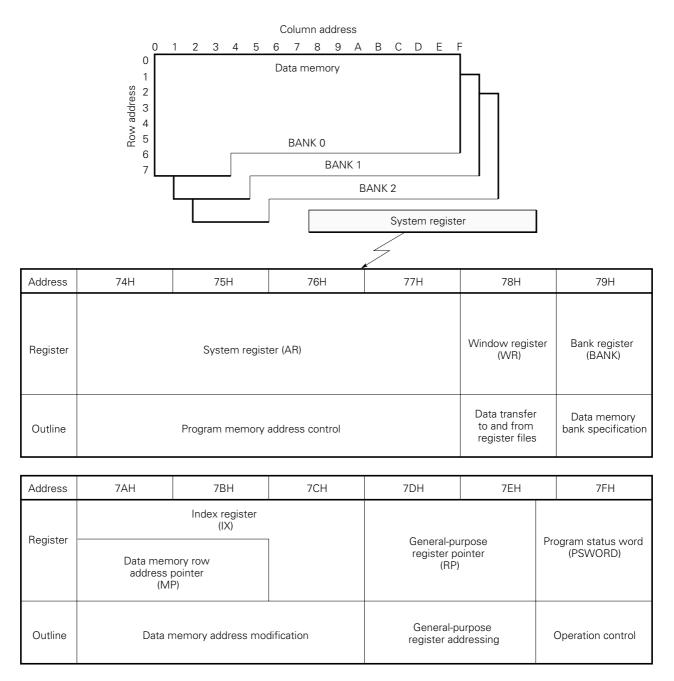

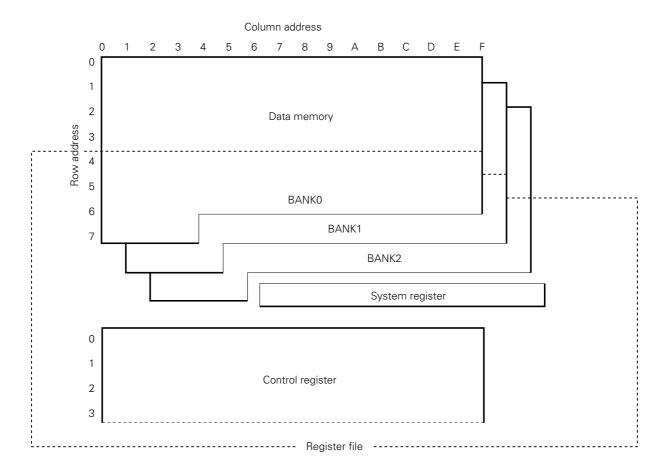

| 4. |                     |         | DRY (RAM)                                                       | 38 |  |  |  |

|    | 4.1                 |         | NE OF DATA MEMORY                                               | 38 |  |  |  |

|    | 4.2                 |         | GURATION AND FUNCTIONS OF DATA MEMORY                           | 39 |  |  |  |

|    |                     | 4.2.1   | System Register (SYSREG)                                        | 39 |  |  |  |

|    |                     | 4.2.2   | Data Buffer (DBF)                                               | 38 |  |  |  |

|    |                     | 4.2.3   | VRAM (Video RAM) for the IDC                                    | 38 |  |  |  |

|    |                     | 4.2.4   | Port Register                                                   | 39 |  |  |  |

|    |                     | 4.2.5   | General-Purpose Data memory                                     | 39 |  |  |  |

|    |                     | 4.2.6   | Unmounted Data Memory                                           | 39 |  |  |  |

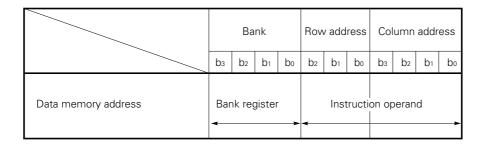

|    | 4.3                      | DATA MEMORY ADDRESSING 42 |                                                               |    |  |  |  |

|----|--------------------------|---------------------------|---------------------------------------------------------------|----|--|--|--|

|    | 4.4                      | NOTES                     | ON USING DATA MEMORY                                          | 42 |  |  |  |

|    |                          | 4.4.1                     | Power-On Reset                                                | 42 |  |  |  |

|    |                          | 4.4.2                     | Notes on Unmounted Data Memory                                | 42 |  |  |  |

| 5. | SYSTEM REGISTER (SYSREG) |                           |                                                               |    |  |  |  |

|    | 5.1                      | OUTLIN                    | NE OF SYSTEM REGISTER                                         | 43 |  |  |  |

|    | 5.2                      | FORM <i>A</i>             | AT OF SYSTEM REGISTER                                         | 44 |  |  |  |

|    | 5.3                      | ADDRE                     | SS REGISTER (AR)                                              | 45 |  |  |  |

|    |                          | 5.3.1                     | Format of Address Register                                    | 45 |  |  |  |

|    |                          | 5.3.2                     | Address Register Functions                                    | 46 |  |  |  |

|    |                          | 5.3.3                     | Address Register and Data Buffer                              | 46 |  |  |  |

|    |                          | 5.3.4                     | Notes on Using Address Register                               | 46 |  |  |  |

|    | 5.4                      | WINDO                     | W REGISTER (WR)                                               | 47 |  |  |  |

|    |                          | 5.4.1                     | Format of Window Register                                     | 47 |  |  |  |

|    |                          | 5.4.2                     | Window Register Functions                                     | 47 |  |  |  |

|    | 5.5                      | BANK I                    | REGISTER (BANK)                                               | 48 |  |  |  |

|    |                          | 5.5.1                     | Format of Bank Register                                       | 48 |  |  |  |

|    |                          | 5.5.2                     | Bank Register Functions                                       | 48 |  |  |  |

|    | 5.6                      | INDEX                     | REGISTER (IX) AND DATA MEMORY ROW ADDRESS POINTER             |    |  |  |  |

|    |                          | (MP: M                    | EMORY POINTER)                                                | 49 |  |  |  |

|    |                          | 5.6.1                     | Index Register (IX)                                           | 49 |  |  |  |

|    |                          | 5.6.2                     | Data Memory Row Address Pointer (MP)                          | 50 |  |  |  |

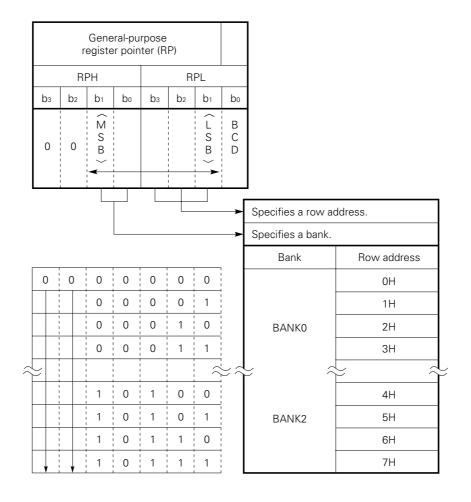

|    | 5.7                      | GENER                     | AL-PURPOSE REGISTER POINTER (RP)                              | 52 |  |  |  |

|    |                          | 5.7.1                     | Format of General-Purpose Register Pointer                    | 52 |  |  |  |

|    |                          | 5.7.2                     | General-Purpose Register Pointer Functions                    | 53 |  |  |  |

|    |                          | 5.7.3                     | Notes on Using General-Purpose Register Pointer               | 53 |  |  |  |

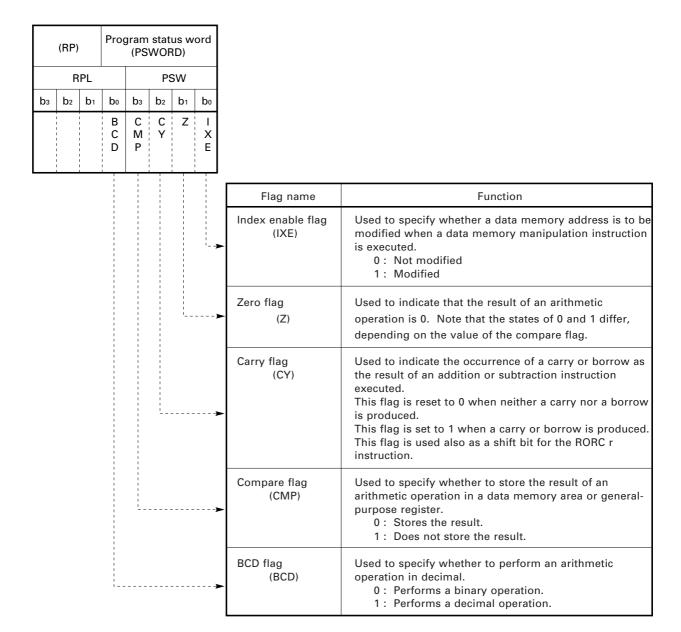

|    | 5.8                      | PROGR                     | AM STATUS WORD (PSWORD)                                       | 54 |  |  |  |

|    |                          | 5.8.1                     | Format of Program Status Word                                 | 54 |  |  |  |

|    |                          | 5.8.2                     | Program Status Word Functions                                 | 55 |  |  |  |

|    |                          | 5.8.3                     | Notes on Using Program Status Word                            | 56 |  |  |  |

|    | 5.9                      | NOTES                     | ON USING SYSTEM REGISTER                                      | 56 |  |  |  |

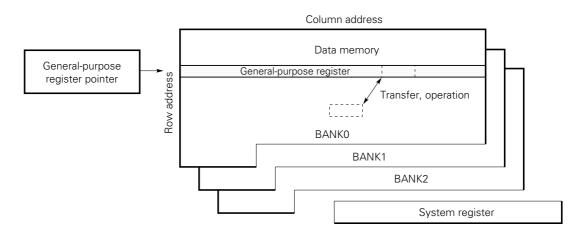

| 6. | GENE                     | RAL-PU                    | JRPOSE REGISTER (GR)                                          | 57 |  |  |  |

|    | 6.1                      | OUTLIN                    | NE OF GENERAL-PURPOSE REGISTER                                | 57 |  |  |  |

|    | 6.2                      | GENER                     | AL-PURPOSE REGISTER BODY                                      | 57 |  |  |  |

|    | 6.3                      | GENER                     | AL-PURPOSE REGISTER ADDRESS GENERATION WITH INSTRUCTIONS      | 58 |  |  |  |

|    |                          | 6.3.1                     | Addition Instructions (ADD r,m, ADDC r,m)                     |    |  |  |  |

|    |                          |                           | Subtraction Instructions (SUB r,m, SUBC r,m)                  |    |  |  |  |

|    |                          |                           | Logical Operation Instructions (AND r,m, OR r,m, XOR r,m)     |    |  |  |  |

|    |                          |                           | Direct Transfer Instructions (LD r,m, ST m,r), and            |    |  |  |  |

|    |                          |                           | Rotate Instruction (RORC r)                                   | 58 |  |  |  |

|    |                          | 6.3.2                     | Indirect Transfer Instructions (MOV @r,m, MOV m,@r)           | 58 |  |  |  |

|    | 6.4                      | NOTES                     | ON USING GENERAL-PURPOSE REGISTER                             | 59 |  |  |  |

|    |                          | 6.4.1                     | Row Address of General-Purpose Register                       | 59 |  |  |  |

|    |                          | 6.4.2                     | Operation between General-Purpose Register and Immediate Data | 59 |  |  |  |

| 7.  | ARITH | <b>IMETIC</b>                       | LOGIC UNIT (ALU) BLOCK                                                | 60       |  |  |

|-----|-------|-------------------------------------|-----------------------------------------------------------------------|----------|--|--|

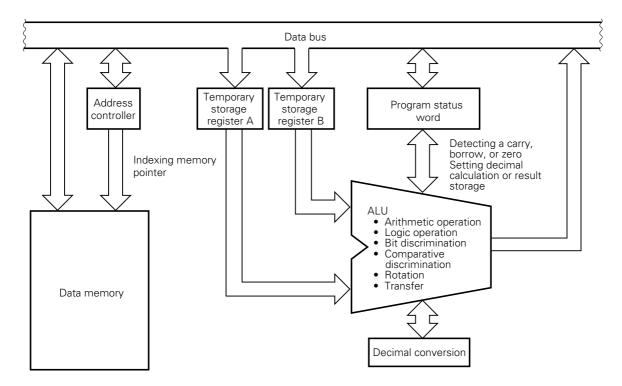

|     | 7.1   | OVERV                               | IEW                                                                   | 60       |  |  |

|     | 7.2   | CONFIG                              | GURATION AND FUNCTIONS OF THE COMPONENTS OF THE ALU BLOCK             | 61       |  |  |

|     |       | 7.2.1                               | ALU                                                                   | 61       |  |  |

|     |       | 7.2.2                               | Temporary Storage Registers A and B                                   | 61       |  |  |

|     |       | 7.2.3                               | Program Status Word                                                   | 61       |  |  |

|     |       | 7.2.4                               | Decimal Conversion Circuit                                            | 61       |  |  |

|     |       | 7.2.5                               | Address Controller                                                    | 61       |  |  |

|     | 7.3   | ALU OP                              | PERATIONS                                                             | 61       |  |  |

|     | 7.4   | NOTES                               | ON USING THE ALU                                                      | 65       |  |  |

|     |       | 7.4.1                               | Notes on Using the Program Status Word for Operations                 | 65       |  |  |

|     |       | 7.4.2                               | Notes on Performing Decimal Operations                                | 65       |  |  |

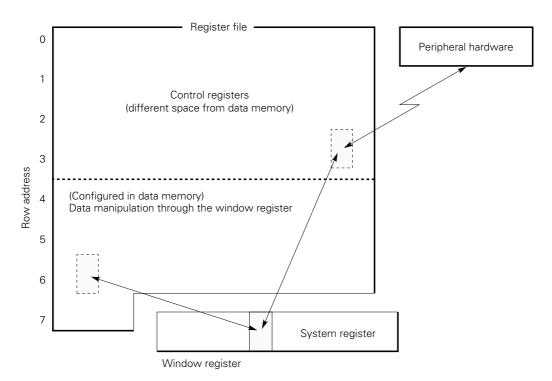

| 8.  | REGIS | TER FILI                            | E (RF)                                                                | 66       |  |  |

|     | 8.1   |                                     | IEW                                                                   | 66       |  |  |

|     | 8.2   | CONFIG                              | GURATION AND FUNCTIONS OF THE REGISTER FILE                           | 67       |  |  |

|     |       | 8.2.1                               | Register File Manipulation Instructions (PEEK WR, rf and POKE rf, WR) | 68       |  |  |

|     | 8.3   | CONTR                               | OL REGISTERS                                                          | 68       |  |  |

|     | 8.4   |                                     | ON USING THE REGISTER FILE                                            | 79       |  |  |

|     | • • • |                                     |                                                                       |          |  |  |

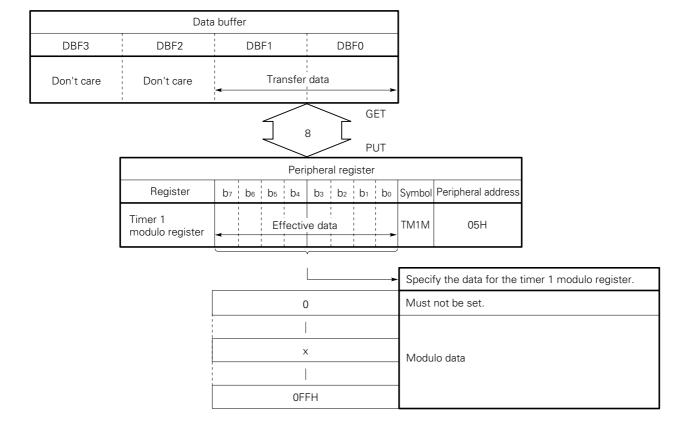

| 9.  |       |                                     | R (DBF)                                                               | 80       |  |  |

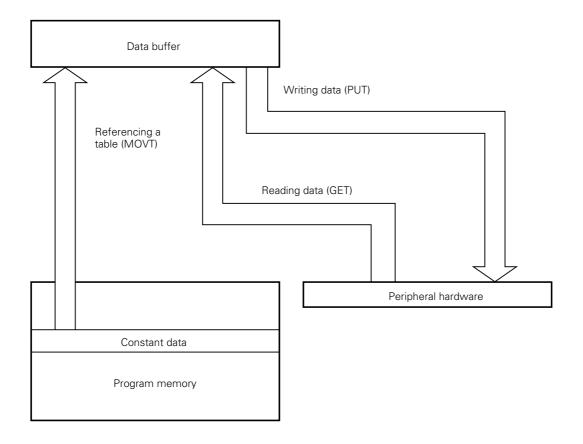

|     | 9.1   |                                     | IEW                                                                   | 80       |  |  |

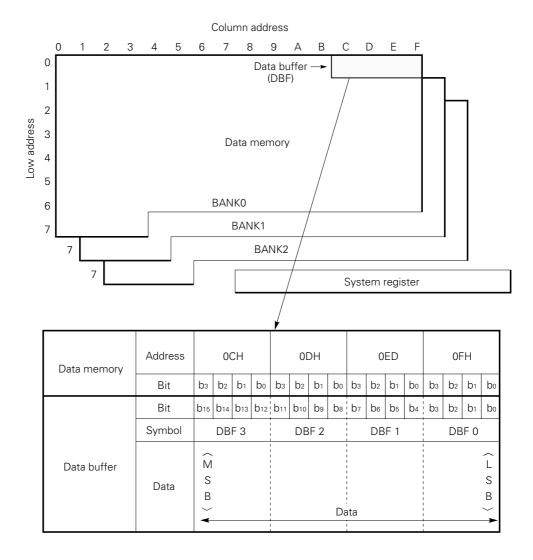

|     | 9.2   | DATA B                              | BUFFER MAIN BODY                                                      | 81       |  |  |

|     |       | 9.2.1                               | Configuration of the Data Buffer Main Body                            | 81       |  |  |

|     |       | 9.2.2                               | Instruction to Reference a Table (MOVT DBF, @AR)                      | 82       |  |  |

|     |       | 9.2.3                               | Instructions for Controlling the Peripheral Hardware (PUT, GET)       | 82<br>82 |  |  |

|     | 9.3   | PERIPHERAL HARDWARE AND DATA BUFFER |                                                                       |          |  |  |

|     | 9.4   | NOTES                               | ON USING THE DATA BUFFER                                              | 86       |  |  |

| 10. | GENE  | RAL-PU                              | JRPOSE PORTS                                                          | 87       |  |  |

|     | 10.1  | OVERV                               | IEW                                                                   | 87       |  |  |

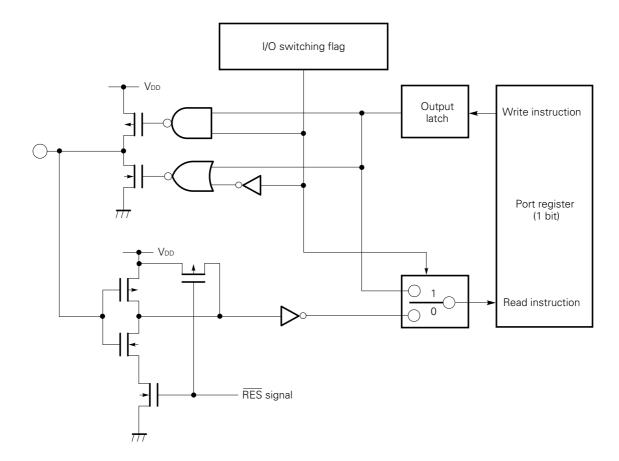

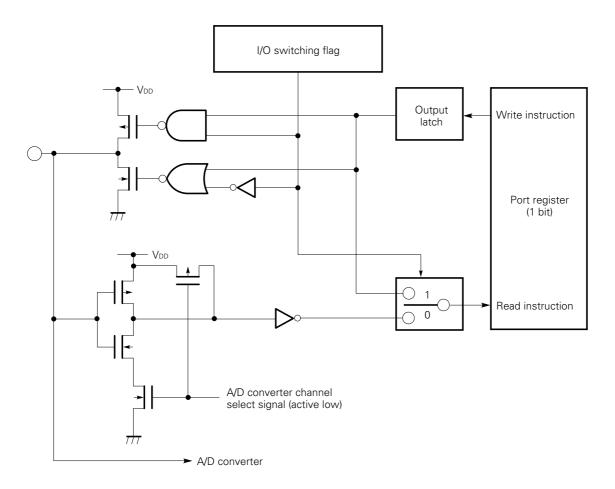

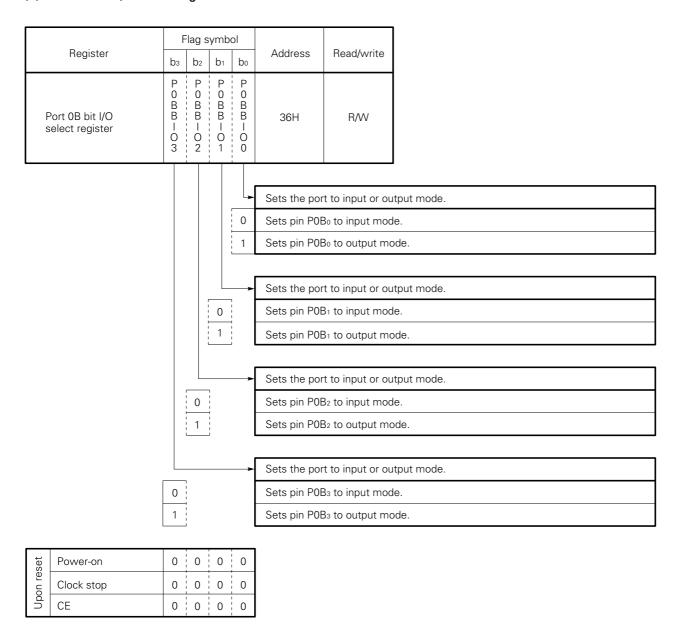

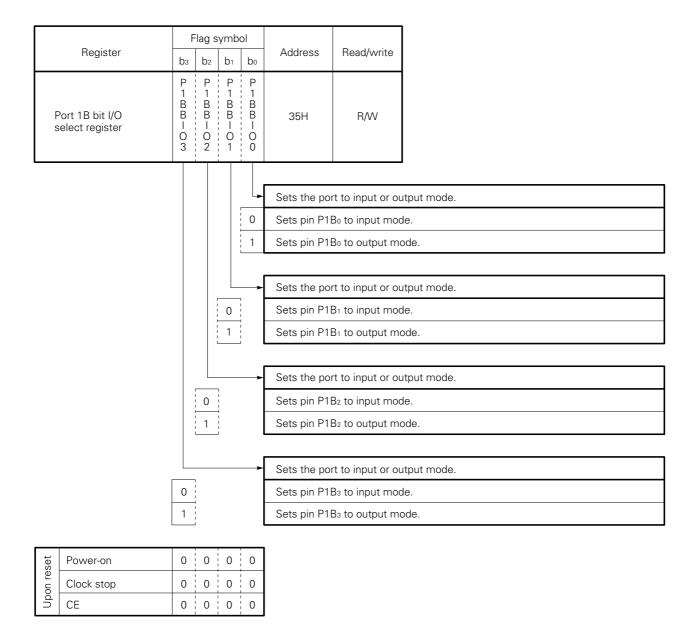

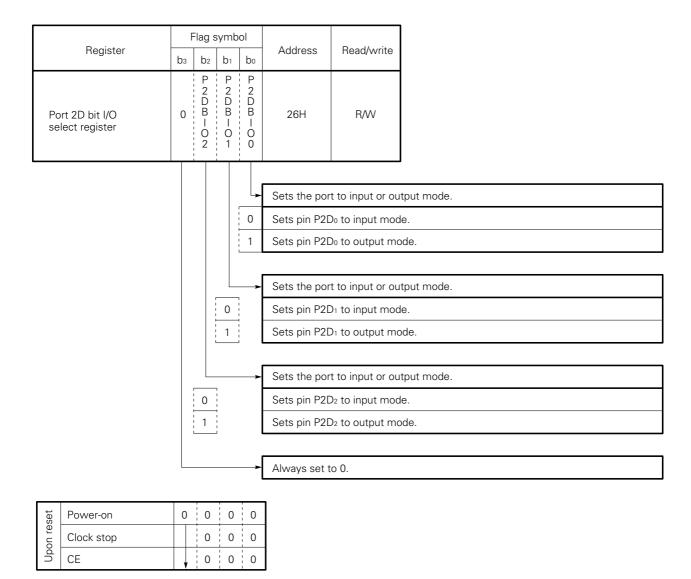

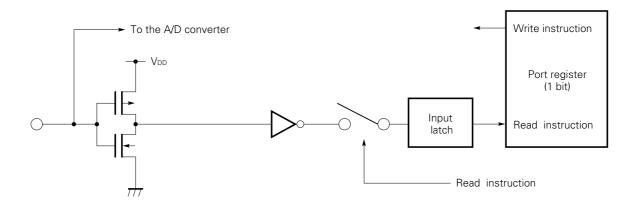

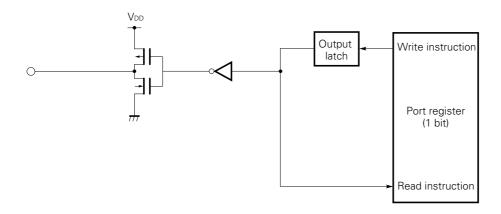

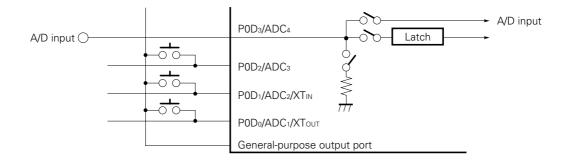

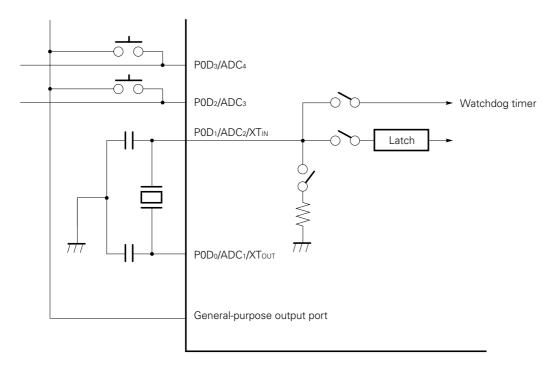

|     | 10.2  | GENER                               | AL-PURPOSE I/O PORTS (P0A, P0B, P1B, P1C, P2D)                        | 89       |  |  |

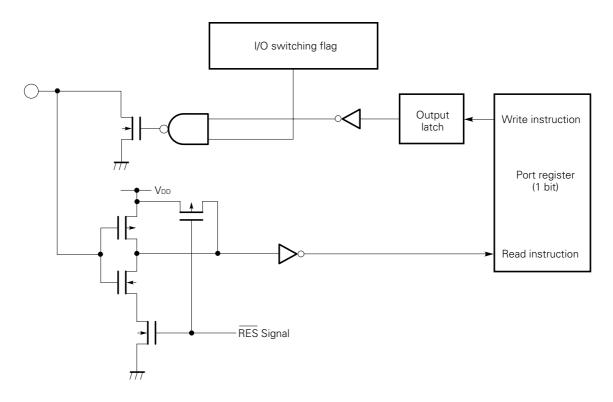

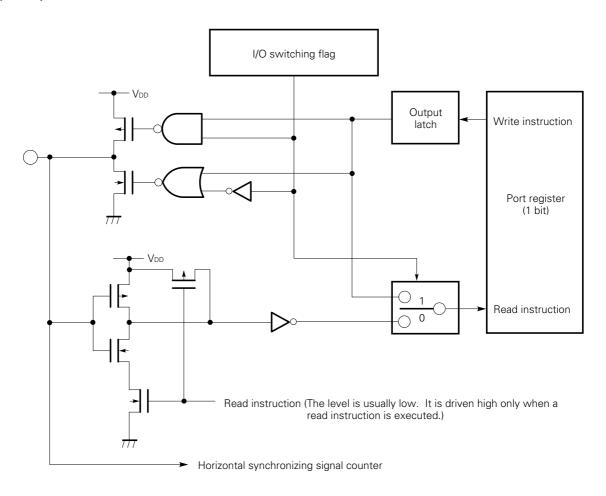

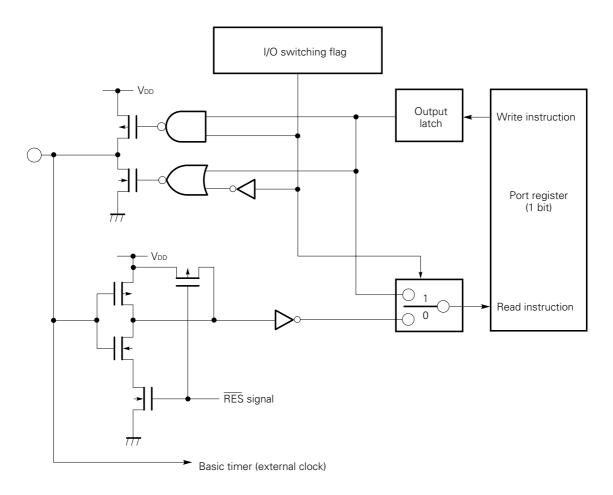

|     |       | 10.2.1                              | Configurations of the I/O ports                                       | 89       |  |  |

|     |       | 10.2.2                              | Using the I/O Port                                                    | 92       |  |  |

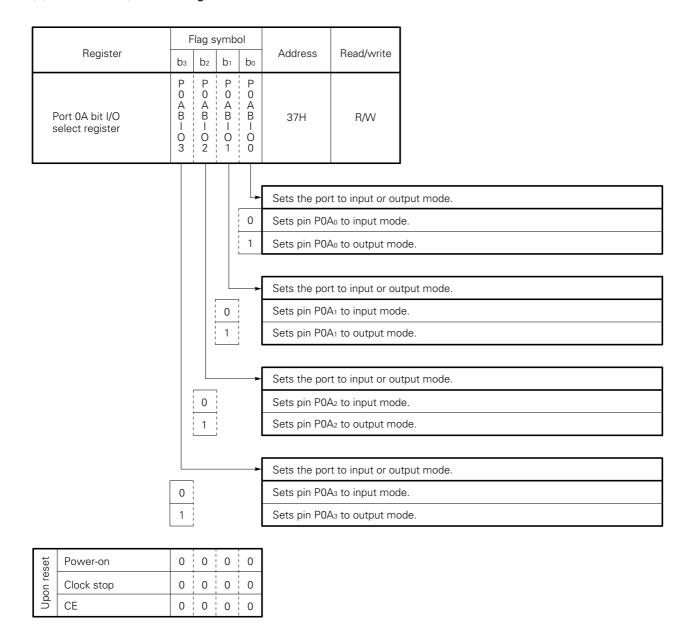

|     |       | 10.2.3                              | Control Registers of the I/O Ports                                    | 93       |  |  |

|     |       | 10.2.4                              | Using an I/O Port as an Input Port                                    | 98       |  |  |

|     |       | 10.2.5                              | Using an I/O Port as an Output Port                                   | 98       |  |  |

|     |       | 10.2.6                              | Notes on Using the I/O Port                                           | 98       |  |  |

|     |       | 10.2.7                              | Statuses of the I/O Ports upon Reset                                  | 99       |  |  |

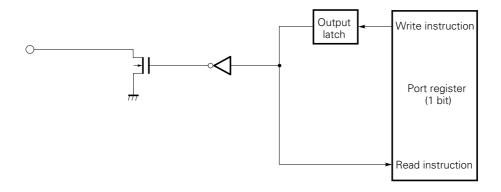

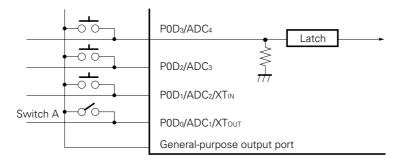

|     | 10.3  | GENER                               | AL-PURPOSE INPUT PORT (P0D)                                           | 99       |  |  |

|     |       | 10.3.1                              | Configuration of the Input Port                                       | 99       |  |  |

|     |       | 10.3.2                              | Using the Input Port                                                  | 99       |  |  |

|     |       | 10.3.3                              | Notes on Using the Input Port                                         | 100      |  |  |

|     |       | 10.3.4                              | Statuses of the Input Port upon Reset                                 | 100      |  |  |

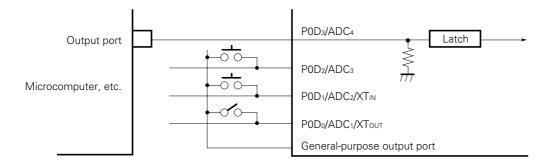

|     | 10.4  | GENER                               | AL-PURPOSE OUTPUT PORTS (P0C, P1A, P1D, P2A, P2B, P2C)                | 100      |  |  |

|     |       | 10.4.1                              | Configurations of the Output Ports                                    | 100      |  |  |

|     |       | 10.4.2                              | Using the Output Port                                                 | 101      |  |  |

|     |       | 10.4.3                              | Statuses of the Output Port upon Reset                                | 101      |  |  |

| 11. | INTER | RRUPT   |                                                                        | 102 |

|-----|-------|---------|------------------------------------------------------------------------|-----|

|     | 11.1  | OUTLIN  | IE OF THE INTERRUPT BLOCK                                              | 102 |

|     | 11.2  | INTERR  | UPT CONTROL BLOCKS                                                     | 104 |

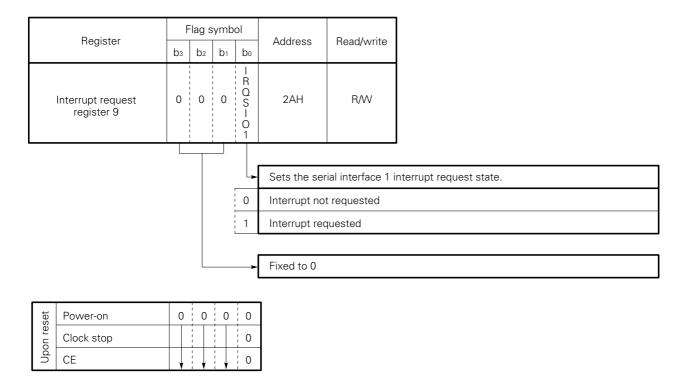

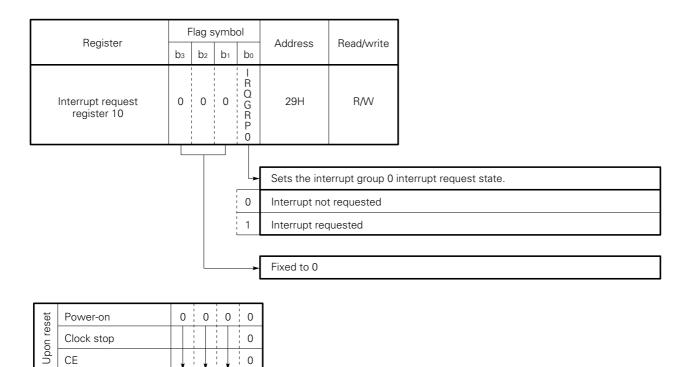

|     |       | 11.2.1  | Formats and Functions of Interrupt Request Flags (IRQxxx)              | 104 |

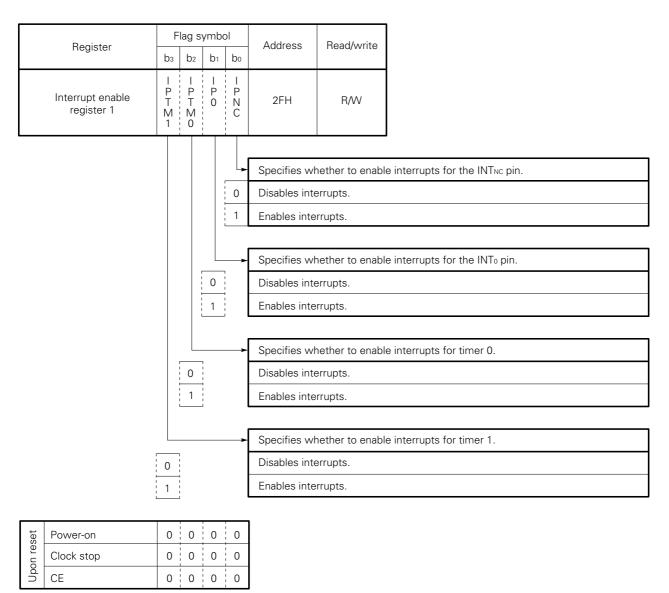

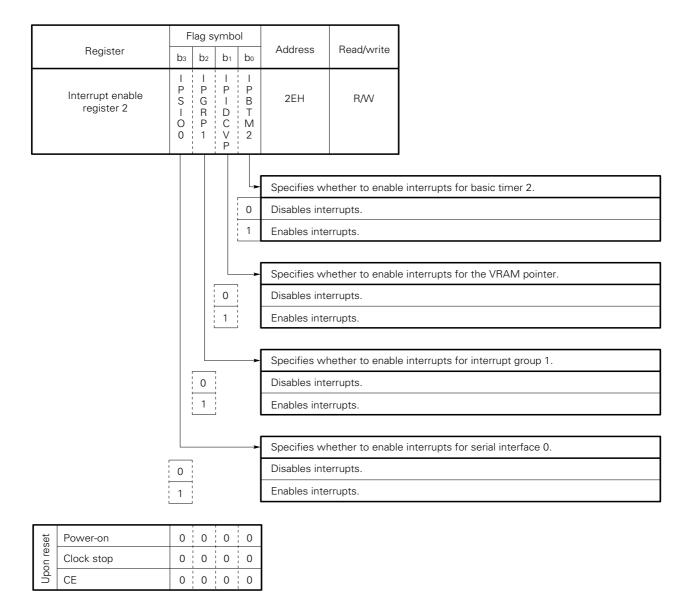

|     |       | 11.2.2  | Interrupt Enable Flags (IPxxx)                                         | 110 |

|     |       | 11.2.3  | Vector Address Generator (VAG)                                         | 112 |

|     | 11.3  | INTERR  | UPT STACK REGISTER                                                     | 113 |

|     |       | 11.3.1  | Format and Functions of the Interrupt Stack Register                   | 113 |

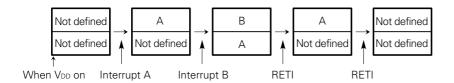

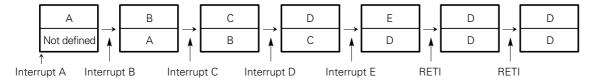

|     |       | 11.3.2  | Interrupt Stack Operation                                              | 113 |

|     | 11.4  | STACK   | POINTER, ADDRESS STACK REGISTER, AND PROGRAM COUNTER                   | 114 |

|     | 11.5  | INTERR  | UPT ENABLE FLIP-FLOP (INTE)                                            | 114 |

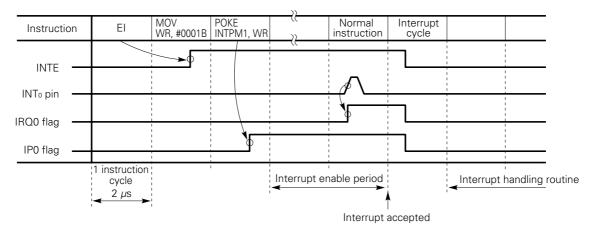

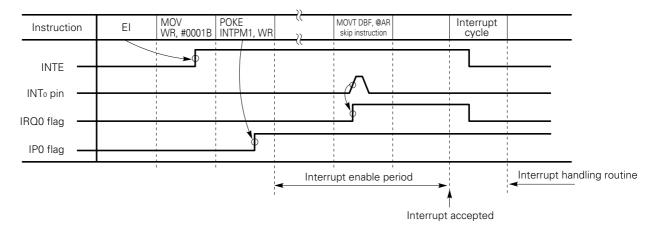

|     | 11.6  | ACCEPT  | TING INTERRUPTS                                                        | 115 |

|     |       | 11.6.1  | Operation for Accepting Interrupts and Priorities                      | 115 |

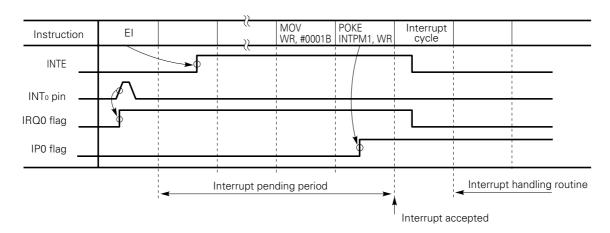

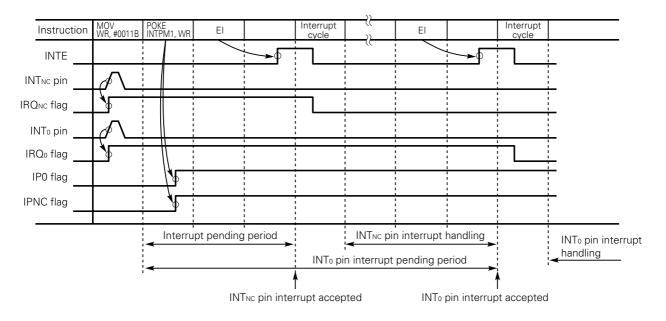

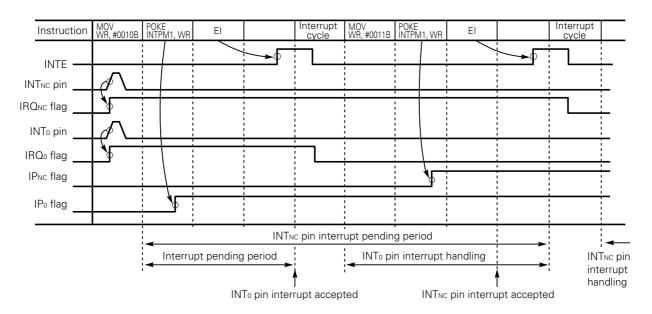

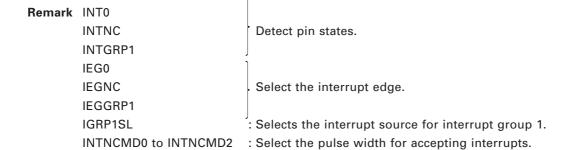

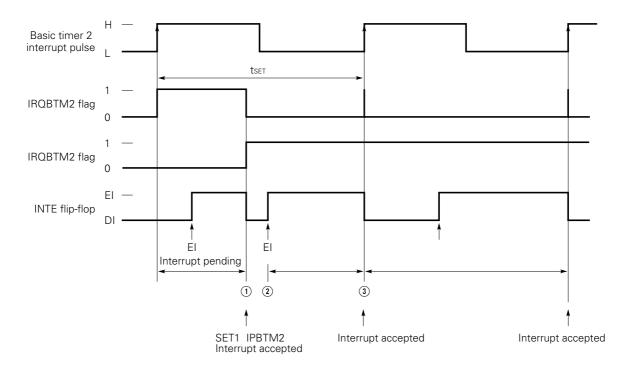

|     |       | 11.6.2  | Timing Charts for Accepting Interrupts                                 | 116 |

|     | 11.7  | OPERAT  | FION AFTER AN INTERRUPT IS ACCEPTED                                    | 119 |

|     | 11.8  | RETURN  | N FROM THE INTERRUPT HANDLING ROUTINE                                  | 119 |

|     | 11.9  | EXTERN  | NAL INTERRUPTS (INTO PIN, INTOC PIN, VSYNC PIN, HSYNC PIN)             | 120 |

|     |       | 11.9.1  | Outline of External Interrupts                                         | 120 |

|     |       | 11.9.2  | Edge Detection Blocks                                                  | 121 |

|     |       | 11.9.3  | Interrupt Control Block                                                | 122 |

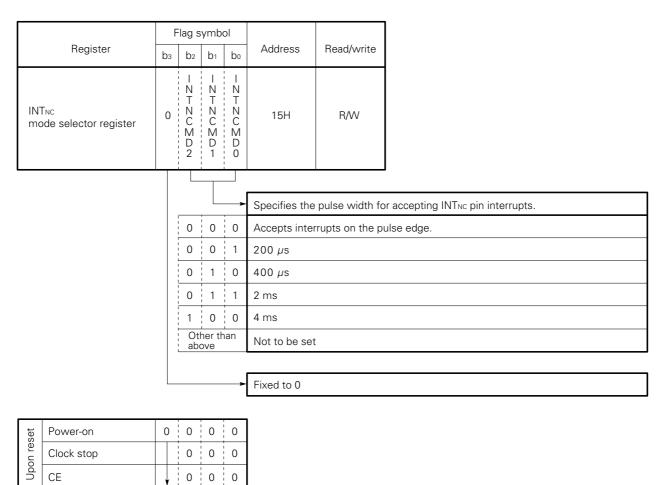

|     |       | 11.9.4  | Input Pin for Remote Control (INTNc)                                   | 123 |

|     | 11.10 | INTERN  | AL INTERRUPTS                                                          | 123 |

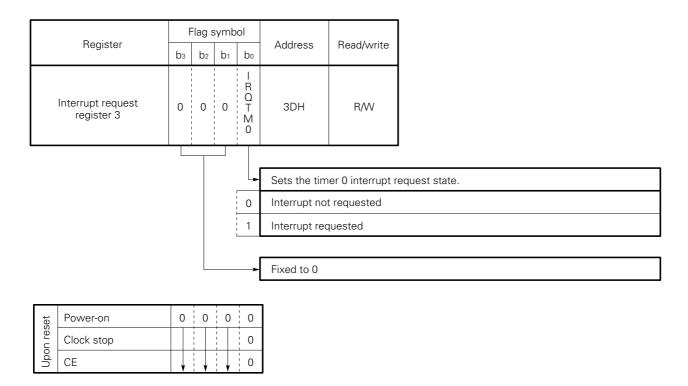

|     |       | 11.10.1 | Timer 0 Interrupt                                                      | 124 |

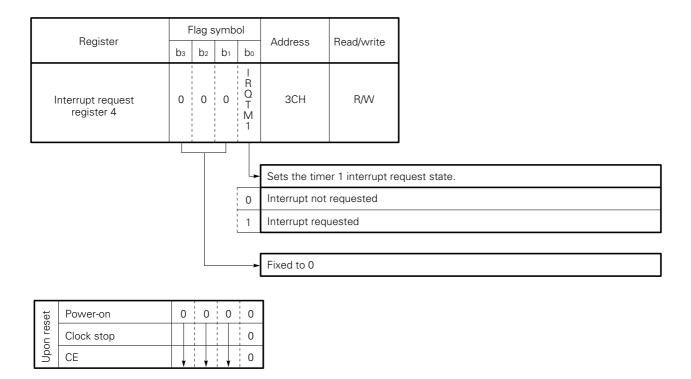

|     |       | 11.10.2 | Timer 1 Interrupt                                                      | 124 |

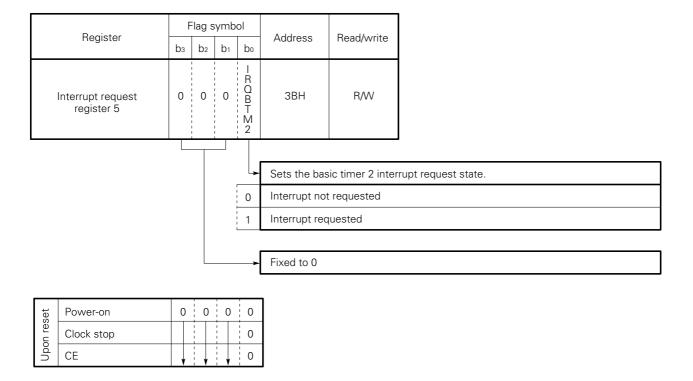

|     |       | 11.10.3 | Basic Timer 2 Interrupt                                                | 124 |

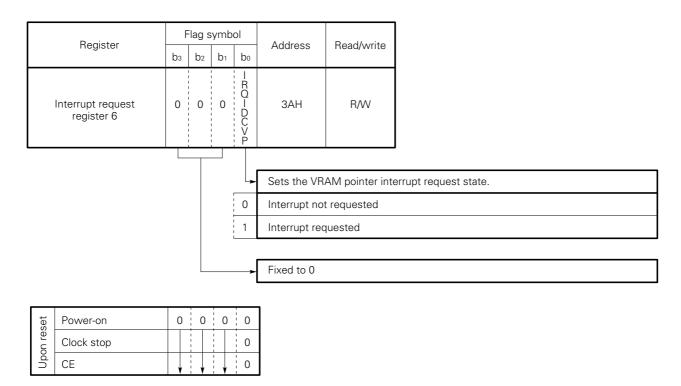

|     |       | 11.10.4 | VRAM Pointer Interrupt                                                 | 124 |

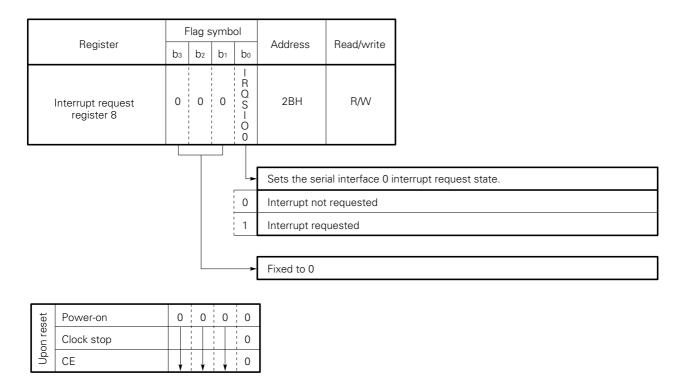

|     |       | 11.10.5 | Serial Interface 0 Interrupt                                           | 124 |

|     |       | 11.10.6 | Serial Interface 1 Interrupt                                           | 124 |

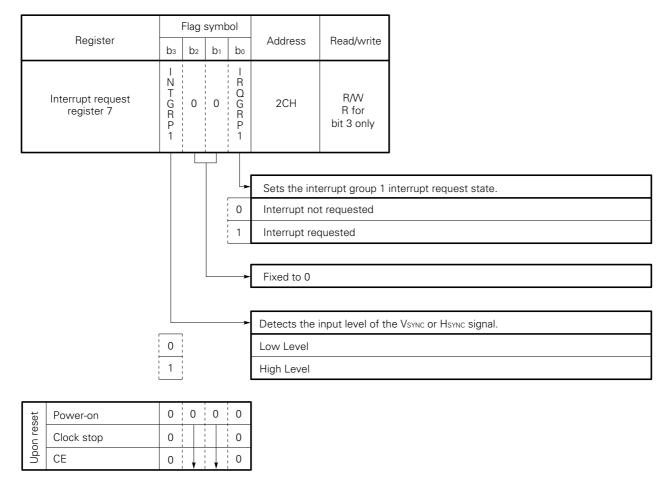

|     |       | 11.10.7 | Interrupts by Interrupt Group 0 and Interrupt Group Selection Register | 125 |

|     |       |         |                                                                        |     |

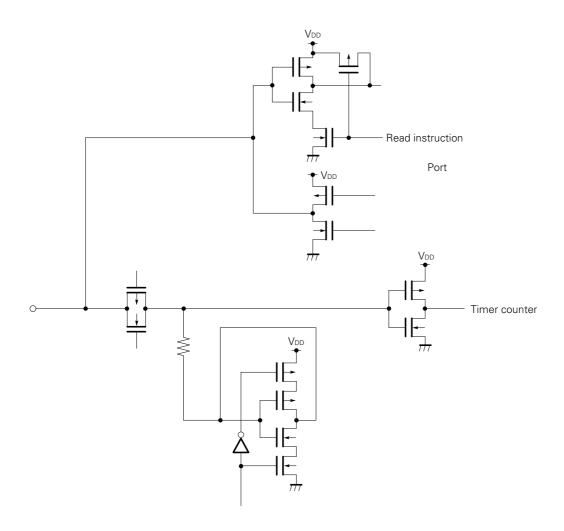

| 12. | TIME  | _       |                                                                        |     |

|     | 12.1  |         | IEW                                                                    |     |

|     | 12.2  |         | TIMER 0                                                                |     |

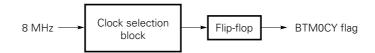

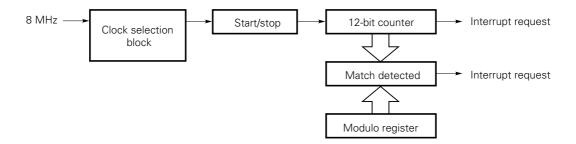

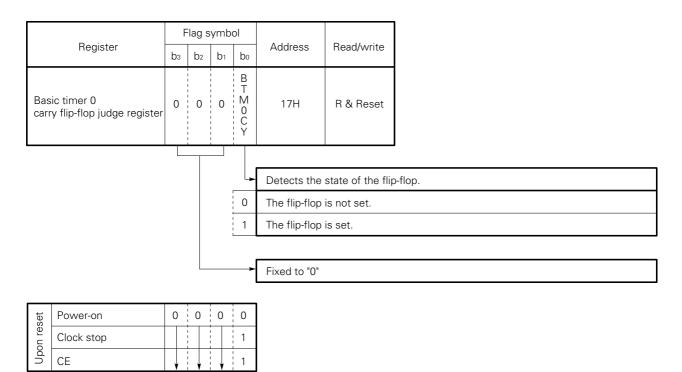

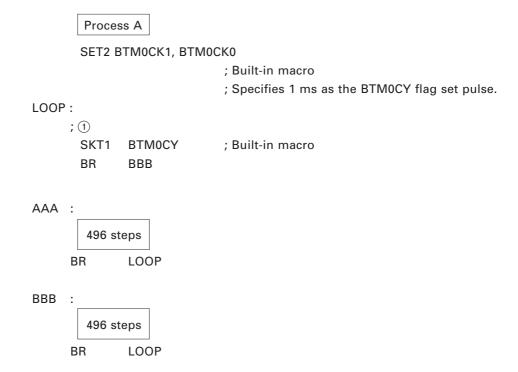

|     |       | 12.2.1  | Overview of Basic Timer 0                                              |     |

|     |       | 12.2.2  | Clock Selection Block                                                  |     |

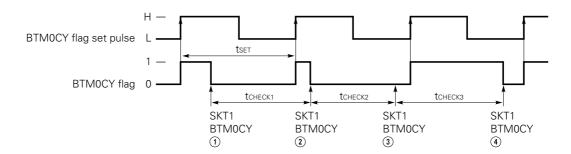

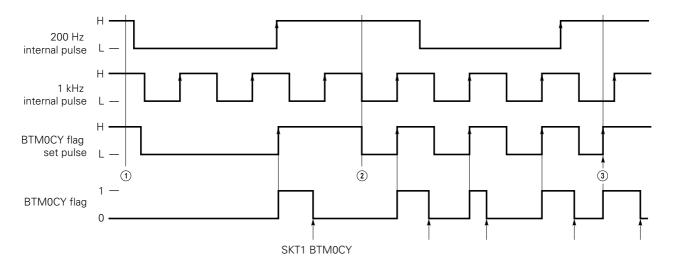

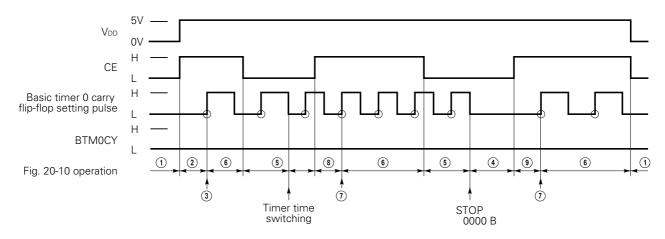

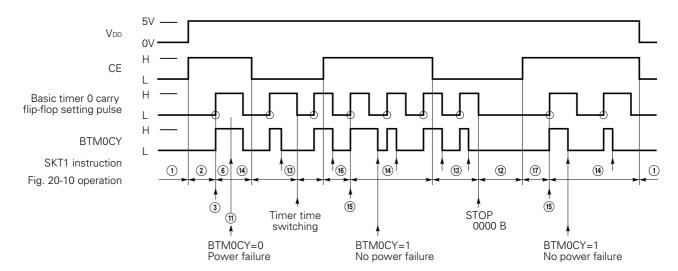

|     |       | 12.2.3  | Flip-Flop and BTM0CY Flag                                              |     |

|     |       | 12.2.4  | Example of Using Basic Timer 0                                         |     |

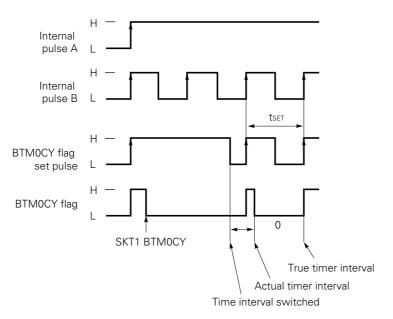

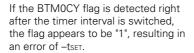

|     |       | 12.2.5  | Time Interval Error in Basic Timer 0                                   |     |

|     |       | 12.2.6  | Cautions for Using Basic Timer 0                                       |     |

|     | 12.3  | BASIC T | 「IMER 1                                                                |     |

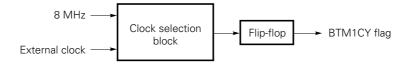

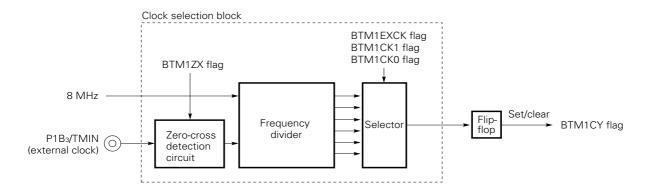

|     |       | 12.3.1  | Overview of Basic Timer 1                                              |     |

|     |       | 12.3.2  | Clock Selection Block                                                  |     |

|     |       | 12.3.3  | Flip-Flop and BTM1CY Flag                                              |     |

|     |       | 12.3.4  | Time Interval Error in Basic Timer 1                                   |     |

|     | 12.4  | BASIC T | TIMER 2                                                                |     |

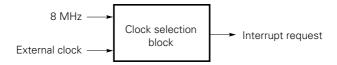

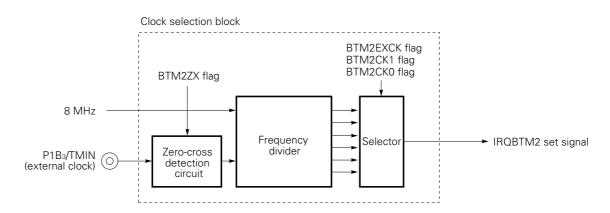

|     |       | 12.4.1  | Overview of Basic Timer 2                                              |     |

|     |       | 12.4.2  | Clock Selection Block                                                  |     |

|     |       | 12.4.3  | Example of Using Basic Timer 2                                         | 145 |

|     |       | 12.4.4                   | Time Interval Error in Basic Timer 2                       | 145 |  |  |  |

|-----|-------|--------------------------|------------------------------------------------------------|-----|--|--|--|

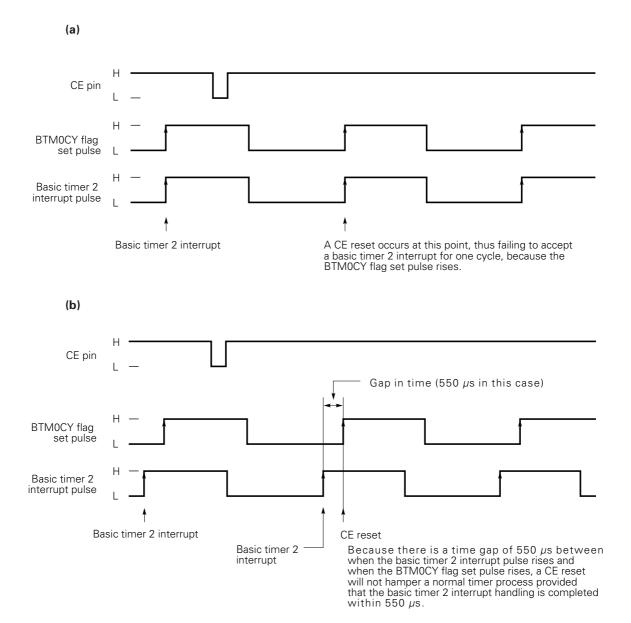

|     |       | 12.4.5                   | Cautions for Using Basic Timer 2                           | 148 |  |  |  |

|     | 12.5  | TIMER (                  | )                                                          | 150 |  |  |  |

|     |       | 12.5.1                   | Overview of Timer 0                                        | 150 |  |  |  |

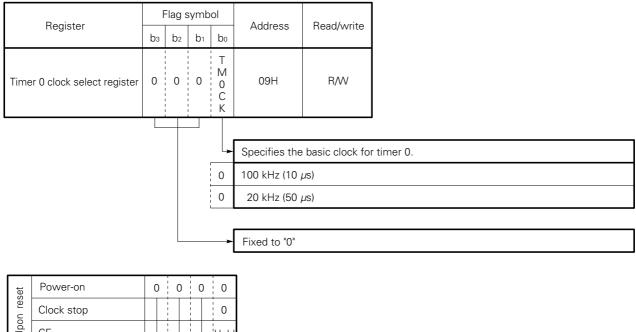

|     |       | 12.5.2                   | Clock Selection Block                                      | 151 |  |  |  |

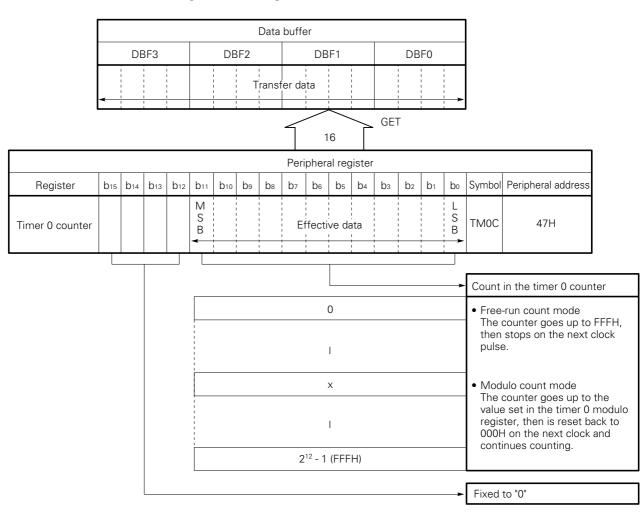

|     |       | 12.5.3                   | Count Block                                                | 152 |  |  |  |

|     |       | 12.5.4                   | Example of Using Timer 0                                   | 155 |  |  |  |

|     |       | 12.5.5                   | Time Interval Error in Timer 0                             |     |  |  |  |

|     |       | 12.5.6                   | Cautions for Using Timer 0                                 | 156 |  |  |  |

|     | 12.6  | TIMER 1                  | 1                                                          |     |  |  |  |

|     |       | 12.6.1                   | Overview of Timer 1                                        | 157 |  |  |  |

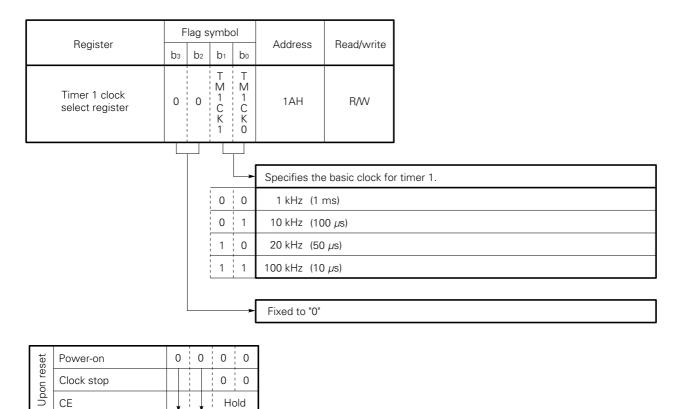

|     |       | 12.6.2                   | Clock Selection Block                                      |     |  |  |  |

|     |       | 12.6.3                   | Count Block                                                | 159 |  |  |  |

|     |       | 12.6.4                   | Time Interval Error in Timer 1                             |     |  |  |  |

|     |       | 12.6.5                   | Cautions for Using Timer 1                                 |     |  |  |  |

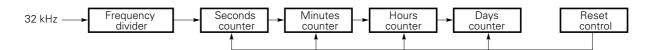

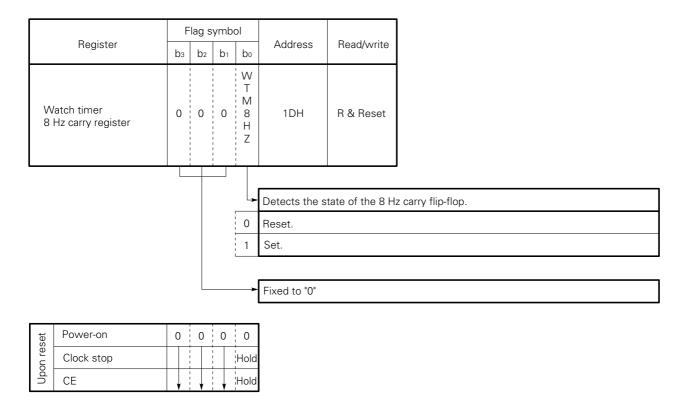

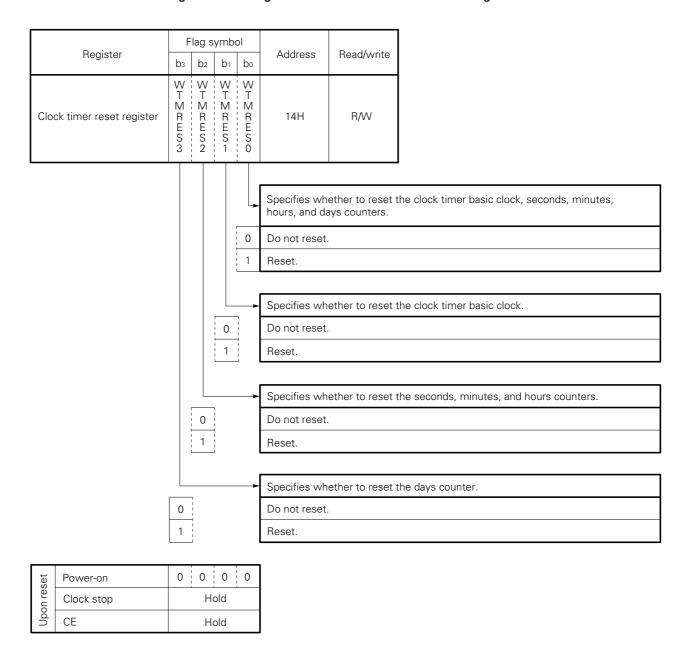

|     | 12.7  |                          | TIMER                                                      |     |  |  |  |

|     |       | 12.7.1                   | Overview of the Clock Timer                                |     |  |  |  |

|     |       | 12.7.2                   | Clock Frequency Divider Block                              |     |  |  |  |

|     |       | 12.7.3                   | Count Block                                                |     |  |  |  |

|     |       | 12.7.4                   | Reset Control Block                                        |     |  |  |  |

|     |       | 12.7.5                   | 32 kHz Oscillator and Oscillation Frequency Adjustment     |     |  |  |  |

|     |       | 12.7.6                   | Cautions for Using the Clock Timer                         |     |  |  |  |

|     |       |                          |                                                            |     |  |  |  |

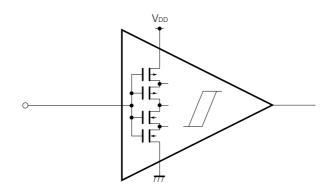

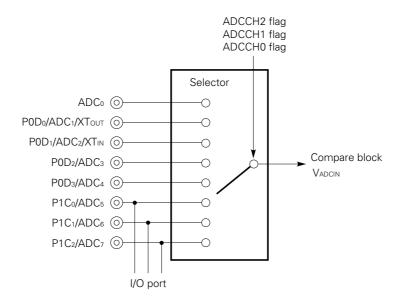

| 13. | A/D C | ONVER                    | TER                                                        | 171 |  |  |  |

|     | 13.1  | OUTLINE OF A/D CONVERTER |                                                            |     |  |  |  |

|     | 13.2  | INPUT SWITCHING BLOCK    |                                                            |     |  |  |  |

|     | 13.3  |                          | RE VOLTAGE GENERATION BLOCK AND COMPARE BLOCK              |     |  |  |  |

|     | 13.4  |                          | RE TIMING CHART                                            |     |  |  |  |

|     | 13.5  |                          | NVERTER PERFORMANCE                                        |     |  |  |  |

|     | 13.6  | •                        | A/D CONVERTER                                              |     |  |  |  |

|     | 10.0  | 13.6.1                   | Comparison with One Reference Voltage                      |     |  |  |  |

|     |       | 13.6.2                   | Successive Approximation Based on the Binary Search Method |     |  |  |  |

|     | 13.7  |                          | ON USING A/D CONVERTER                                     |     |  |  |  |

|     | 13.8  |                          | S UPON RESET                                               |     |  |  |  |

|     | 13.0  | 13.8.1                   | Power-On Reset                                             |     |  |  |  |

|     |       | 13.8.2                   | Clock Stop                                                 |     |  |  |  |

|     |       | 13.8.3                   | CE Reset                                                   |     |  |  |  |

|     |       | 13.0.3                   | GE Neset                                                   | 104 |  |  |  |

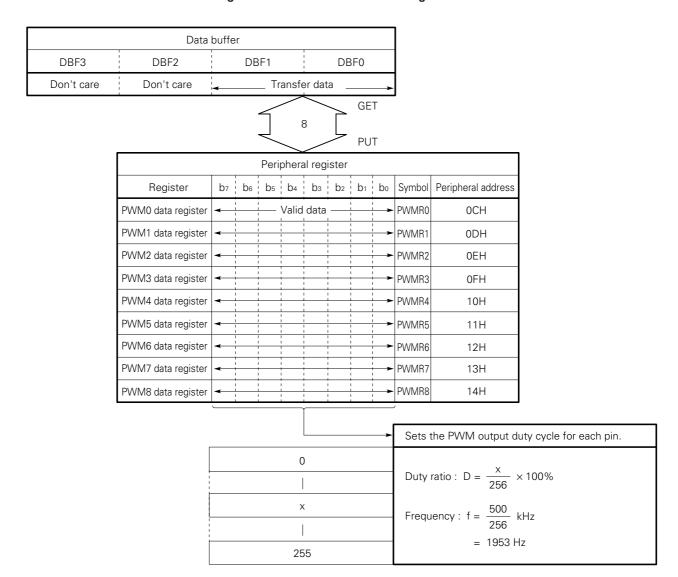

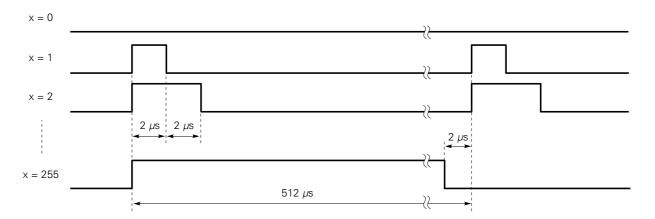

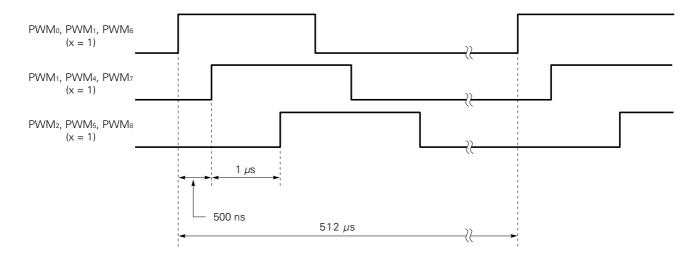

| 14  | D/A C | ONVER                    | TER (PWM METHOD)                                           | 185 |  |  |  |

| 17. | 14.1  |                          | IE OF D/A CONVERTER                                        |     |  |  |  |

|     | 14.2  |                          | T SWITCHING BLOCK                                          |     |  |  |  |

|     | 14.3  |                          | YCLE SETTING BLOCK                                         |     |  |  |  |

|     | 14.3  |                          | GENERATION BLOCK                                           |     |  |  |  |

|     | 14.4  |                          | T WAVEFORMS OF D/A CONVERTER                               |     |  |  |  |

|     | 14.5  |                          | ON USING D/A CONVERTER                                     |     |  |  |  |

|     |       |                          |                                                            |     |  |  |  |

|     | 14.7  |                          | Buyon On Booot                                             |     |  |  |  |

|     |       | 14.7.1                   | Power-On Reset                                             |     |  |  |  |

|     |       | 14.7.2                   | Clock Stop                                                 | 191 |  |  |  |

|     |       | 14.7.3    | CE Reset                                             | 191 |

|-----|-------|-----------|------------------------------------------------------|-----|

|     |       | 14.7.4    | Halt State                                           | 191 |

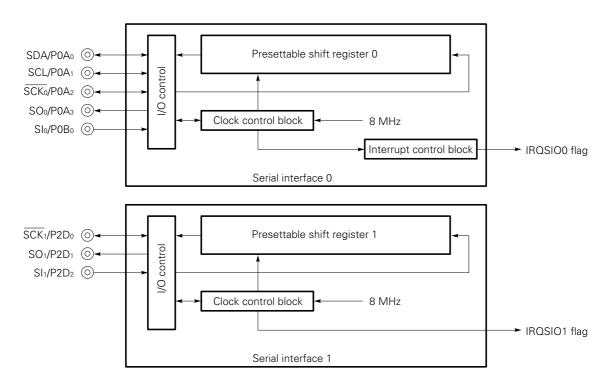

| 15  | CEDI/ | VI INITEE | RFACE                                                | 102 |

| 15. | 15.1  |           | AL                                                   |     |

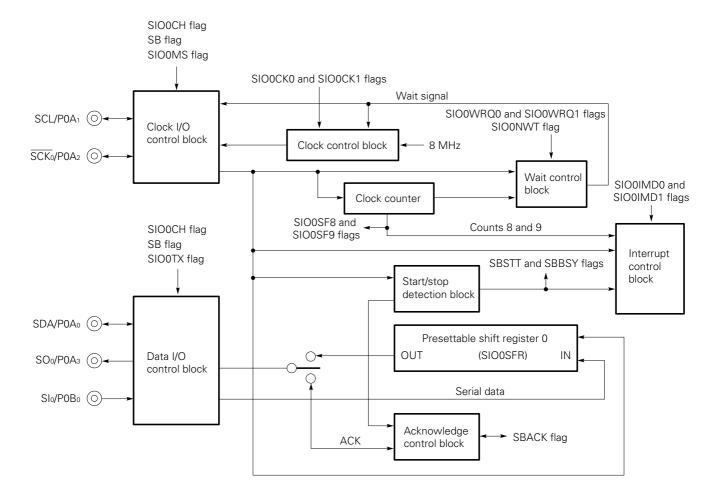

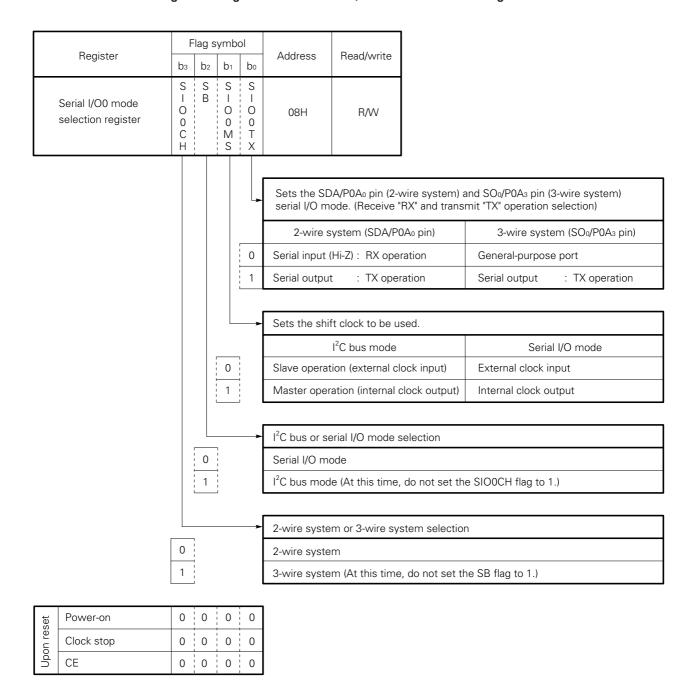

|     | 15.1  |           | INTERFACE 0                                          |     |

|     | 13.2  | 15.2.1    | General                                              |     |

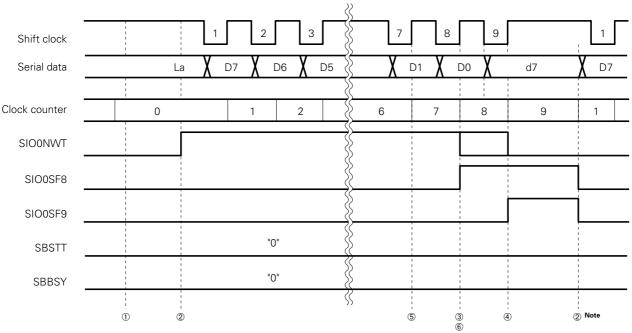

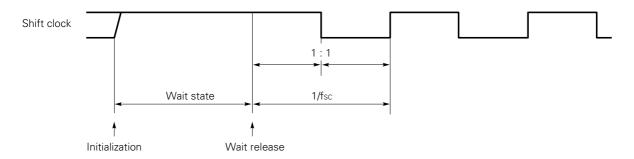

|     |       | 15.2.1    | Clock I/O Control Block and Data I/O Control Block   |     |

|     |       | 15.2.2    | Clock Control Block                                  |     |

|     |       | 15.2.4    | Clock Counter and Start/Stop Detection Block         |     |

|     |       | 15.2.4    | ·                                                    |     |

|     |       |           | Presettable Shift Register 0                         |     |

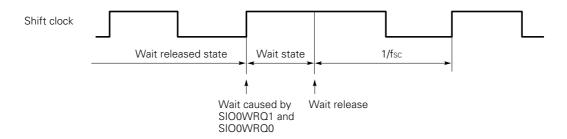

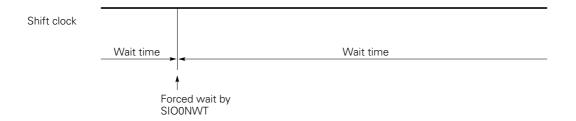

|     |       | 15.2.6    | Wait Control Block and Acknowledge Control Block     |     |

|     |       | 15.2.7    | Interrupt Control Block                              |     |

|     |       | 15.2.8    | I'C Bus Mode                                         |     |

|     |       | 15.2.9    | Serial I/O Mode                                      |     |

|     |       | 15.2.10   | Data Write and Read Cautions                         |     |

|     |       | 15.2.11   | Serial Interface 0 Operation                         |     |

|     |       | 15.2.12   | State When Serial Interface 0 Is Reset               |     |

|     | 15.3  |           | INTERFACE 1                                          |     |

|     |       | 15.3.1    | General                                              |     |

|     |       | 15.3.2    | Clock I/O Control Block and Data I/O Control Block   |     |

|     |       | 15.3.3    | Clock Counter                                        |     |

|     |       | 15.3.4    | Presettable Shift Register 1                         | 222 |

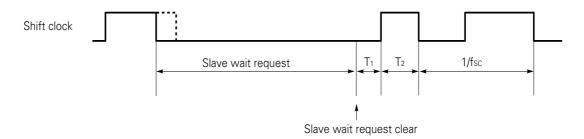

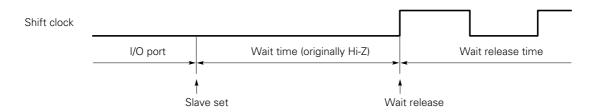

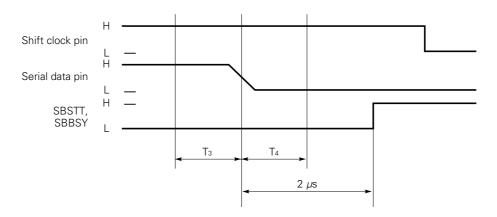

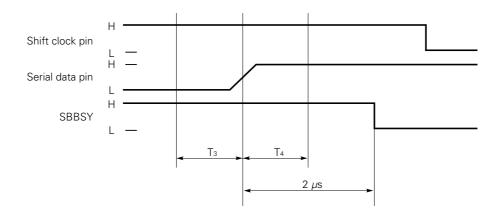

|     |       | 15.3.5    | Wait Control Block                                   |     |

|     |       | 15.3.6    | Serial Interface 1 Operation                         | 223 |

|     |       | 15.3.7    | Data Write and Data Read Cautions                    | 226 |

|     |       | 15.3.8    | Serial Interface 1 Operation                         |     |

|     |       | 15.3.9    | State When Serial Interface 1 Is Reset               | 228 |

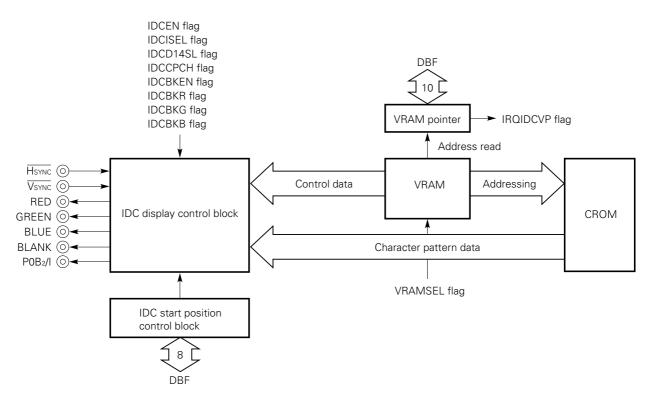

| 16. | IMAG  | E DISPL   | AY CONTROLLER (IDC)                                  | 229 |

|     | 16.1  |           | AL                                                   |     |

|     |       | 16.1.1    | Configuration                                        |     |

|     |       | 16.1.2    | IDC Functions                                        |     |

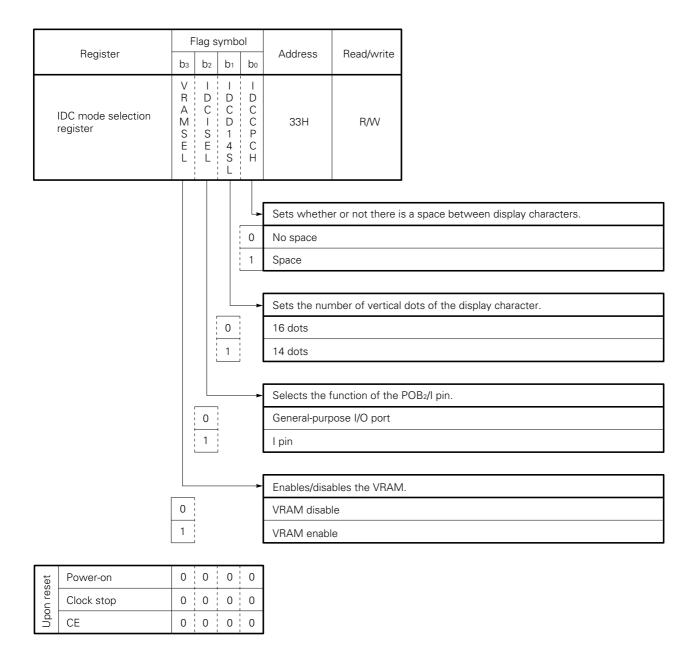

|     | 16.2  |           | PLAY CONTROL BLOCK                                   |     |

|     |       | 16.2.1    | IDC Display Control Block Control Registers          |     |

|     |       | 16.2.2    | Display Format                                       |     |

|     |       | 16.2.3    | Space between Characters                             |     |

|     |       | 16.2.4    | Screen Background Color                              |     |

|     | 16.3  |           | ART POSITION CONTROL BLOCK                           |     |

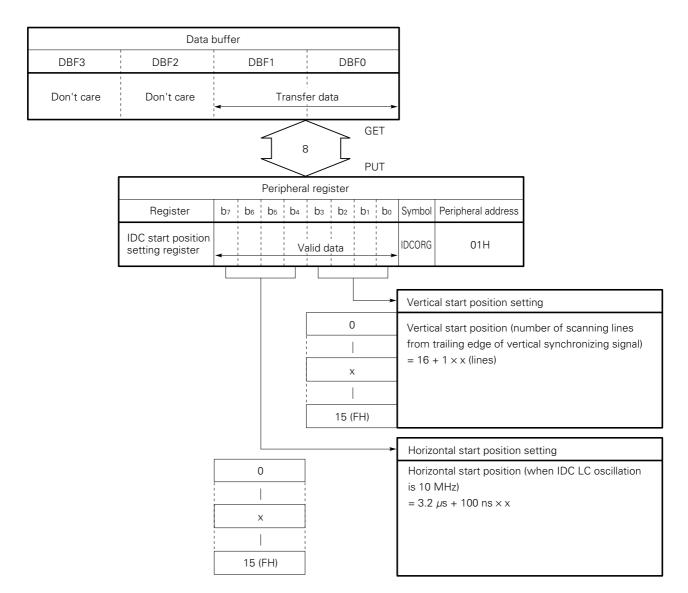

|     | 10.0  | 16.3.1    | Configuration of IDC Start Position Setting Register |     |

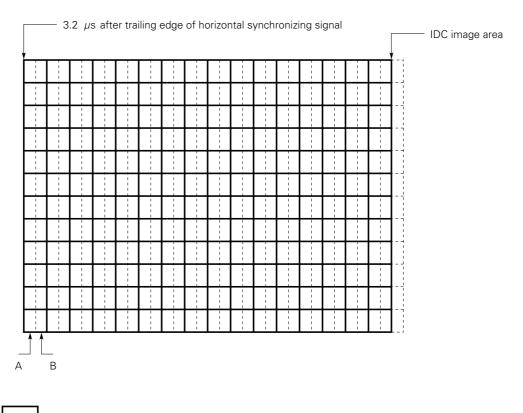

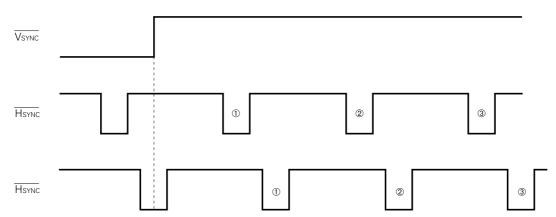

|     |       | 16.3.2    | Horizontal Start Position Setting                    | 236 |

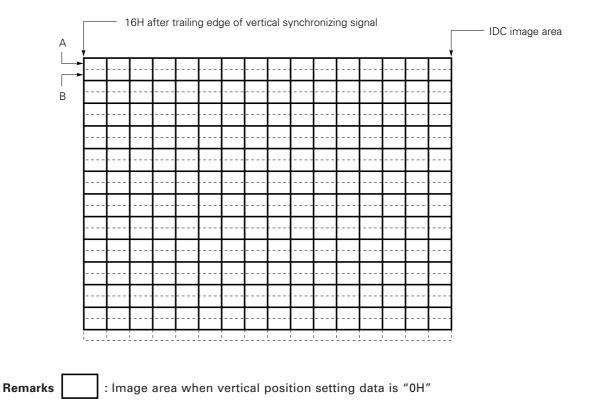

|     |       | 16.3.3    | Vertical Start Position Setting                      |     |

|     | 16.4  |           | CHARACTER ROM)                                       | 239 |

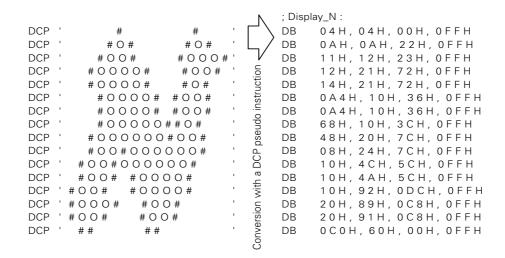

|     | 10.4  | 16.4.1    | Character Pattern Data Configuration                 | 240 |

|     |       | 16.4.1    | Definition of Character Pattern Data with Assembler  |     |

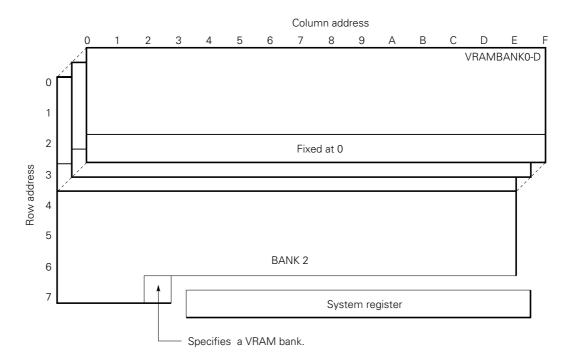

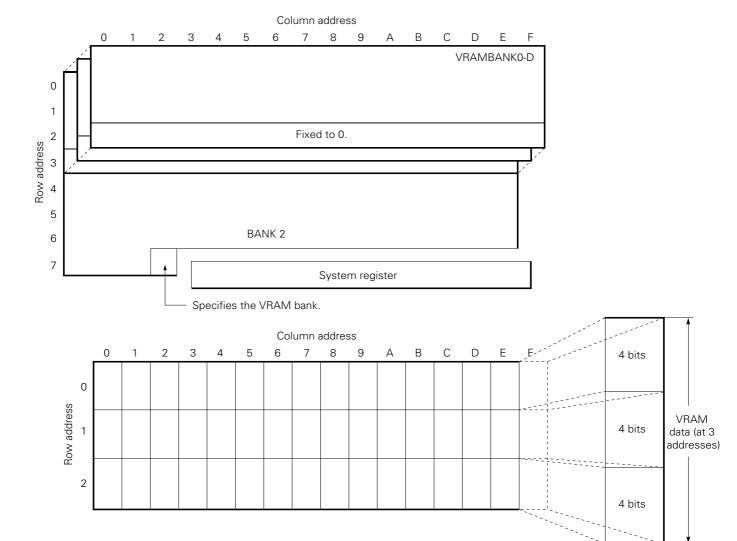

|     | 16.5  |           | VIDEO RAM)                                           |     |

|     | 10.0  |           |                                                      | 243 |

|     |       | 16.5.1    | General                                              | 243 |

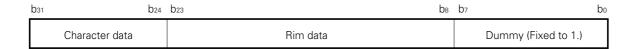

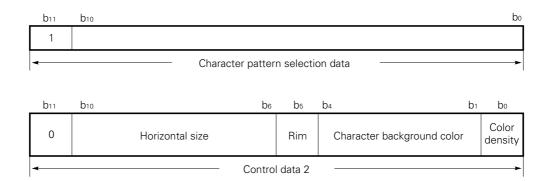

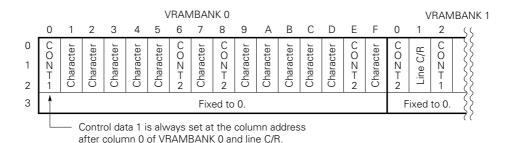

|     |       | 16.5.2    | Configuration of VRAM Data                           | 244 |

|     |       | 16.5.3                        | Character Pattern Selection Data                                  | 245 |  |

|-----|-------|-------------------------------|-------------------------------------------------------------------|-----|--|

|     |       | 16.5.4                        | Carriage Return Data (C/R)                                        | 248 |  |

|     |       | 16.5.5                        | Control Data                                                      | 248 |  |

|     |       | 16.5.6                        | VRAM Data Setting Example                                         | 253 |  |

|     |       | 16.5.7                        | VRAM Data Setting Cautions                                        | 253 |  |

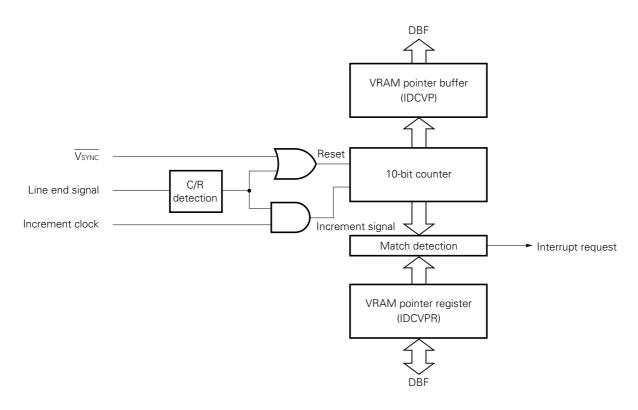

|     | 16.6  | VRAM                          | POINTER                                                           | 255 |  |

|     |       | 16.6.1                        | Configuration of VRAM Pointer                                     | 255 |  |

|     |       | 16.6.2                        | VRAM Pointer Buffer (IDCVP)                                       | 256 |  |

|     |       | 16.6.3                        | VRAM Pointer Register (IDCVPR)                                    | 257 |  |

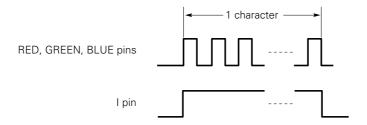

|     | 16.7  | IDC OU                        | TPUT PINS (BLANK, RED, GREEN, BLUE, I PINS)                       | 258 |  |

|     |       | 16.7.1                        | Functions of IDC Output Pins                                      | 258 |  |

|     |       | 16.7.2                        | IDC Output Waveforms                                              | 258 |  |

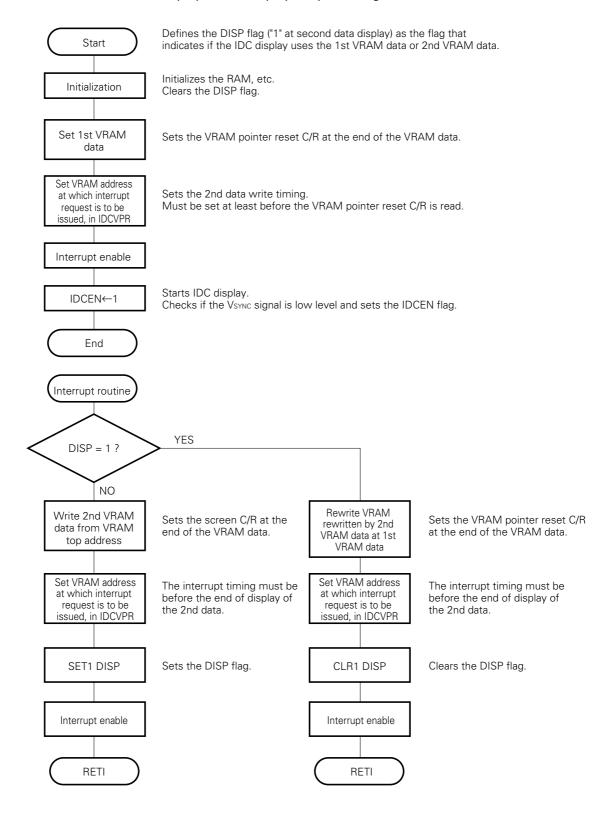

|     | 16.8  | SAMPL                         | E PROGRAM                                                         | 259 |  |

|     |       | 16.8.1                        | Displaying Data Exceeding VRAM Capacity (Extended Display Mode)   | 259 |  |

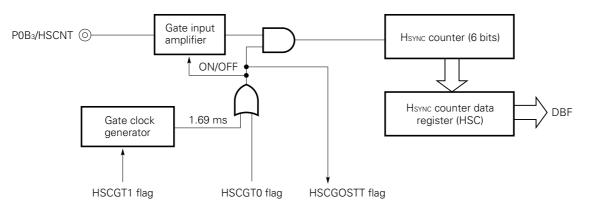

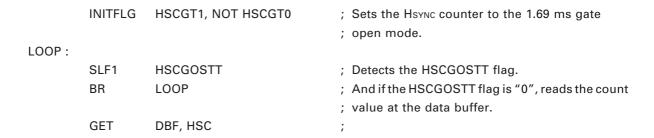

| 17. | HORI  | ZONTAI                        | L SYNCHRONIZING SIGNAL COUNTER                                    | 262 |  |

|     | 17.1  | GENER                         | AL                                                                | 262 |  |

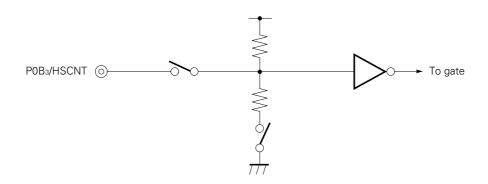

|     | 17.2  | GATE II                       | NPUT AMPLIFIER                                                    | 262 |  |

|     | 17.3  | GATE (                        | CONTROL                                                           | 263 |  |

|     |       | 17.3.1                        | HSYNC Counter Gate Mode Selection Flag (HSCGT×)                   | 264 |  |

|     |       | 17.3.2                        | HSYNC Counter Gate Open Status Flag (HSCGOSTT)                    | 264 |  |

|     | 17.4  | Hsync C                       | OUNTER DATA REGISTER (HSC)                                        | 265 |  |

|     | 17.5  | SAMPL                         | E PROGRAM                                                         | 265 |  |

|     | 17.6  | STATE                         | AT RESET                                                          | 265 |  |

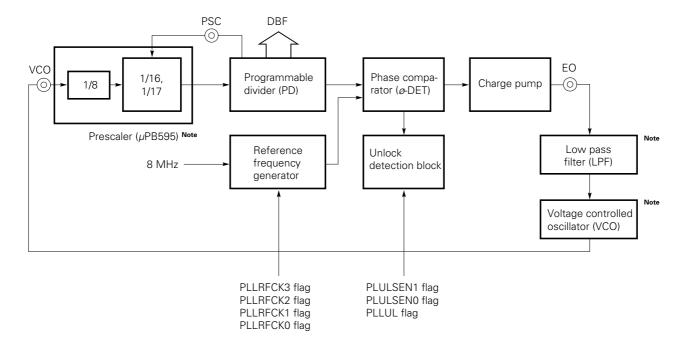

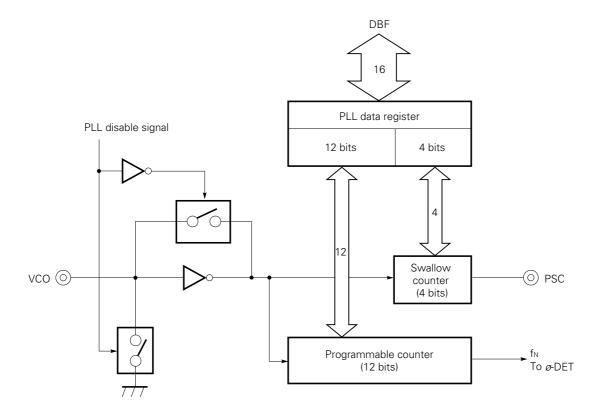

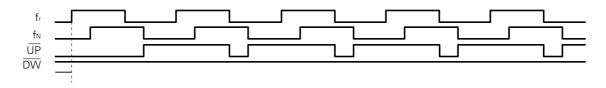

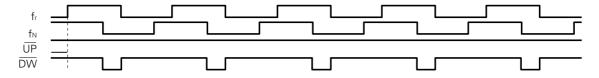

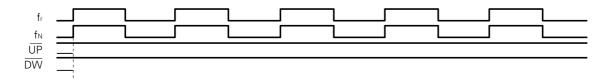

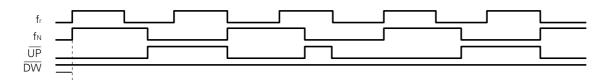

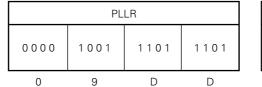

| 18. | PLL F | REQUE                         | NCY SYNTHESIZER                                                   | 266 |  |

|     | 18.1  | GENER                         | AL                                                                | 266 |  |

|     | 18.2  | PROGR                         | AMMABLE DIVIDER                                                   | 267 |  |

|     |       | 18.2.1                        | Configuration                                                     | 267 |  |

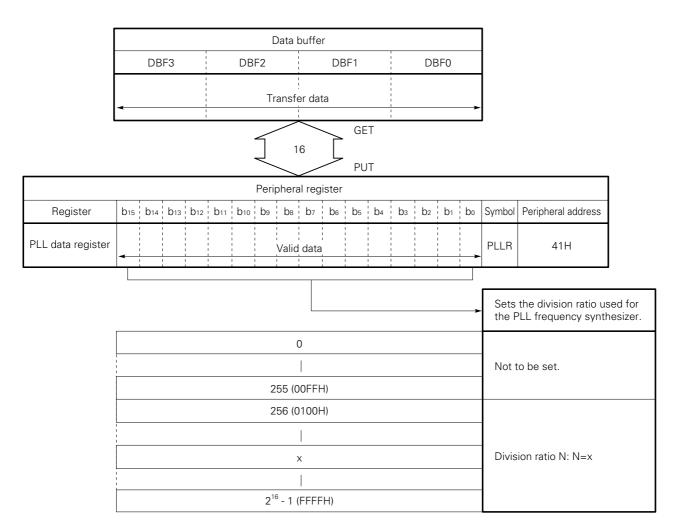

|     |       | 18.2.2                        | Programmable Divider and PLL Data Register                        | 268 |  |

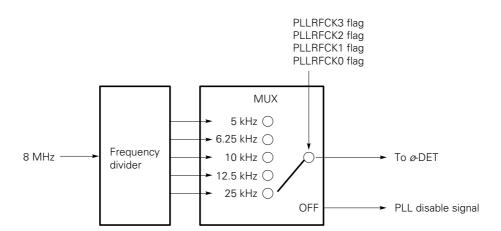

|     | 18.3  | REFERE                        | ENCE FREQUENCY GENERATOR                                          | 269 |  |

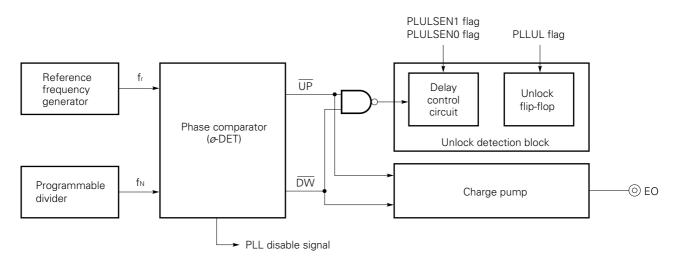

|     | 18.4  | PHASE                         | COMPARATOR ( $\phi$ -DET), CHARGE PUMP AND UNLOCK DETECTION BLOCK | 271 |  |

|     |       | 18.4.1                        | Configuration of Phase Comparator, Charge Pump and                |     |  |

|     |       |                               | Unlock Detection Block                                            | 271 |  |

|     |       | 18.4.2                        | Phase Comparator Functions                                        | 271 |  |

|     |       | 18.4.3                        | Charge Pump                                                       |     |  |

|     |       | 18.4.4                        | Configuration and Functions of Unlock Detection Block             | 273 |  |

|     |       | 18.4.5                        | Organization and Functions of PLL Unlock Flip-Flop Judge Register | 273 |  |

|     |       | 18.4.6                        | Organization and Functions of PLL Unlock Flip-Flop Sensibility    |     |  |

|     |       |                               | Selection Register                                                |     |  |

|     | 18.5  | 5 PLL DISABLED STATE          |                                                                   |     |  |

|     | 18.6  | PLL FREQUENCY SYNTHESIZER USE |                                                                   |     |  |

|     | 18.7  | SAMPLE PROGRAM                |                                                                   |     |  |

|     | 18.8  | STATE                         | AT RESET                                                          |     |  |

|     |       | 18.8.1                        | At Power-On Reset                                                 | 277 |  |

|     |       | 18.8.2                        | At Clock-Stop                                                     |     |  |

|     |       | 18.8.3                        | At CE Reset                                                       |     |  |

|     |       | 18.8.4                        | During the Halt State                                             | 277 |  |

| 19. | STAN  | DBY           |                                                                  | 278 |

|-----|-------|---------------|------------------------------------------------------------------|-----|

|     | 19.1  | STANDE        | BY FUNCTIONS                                                     | 278 |

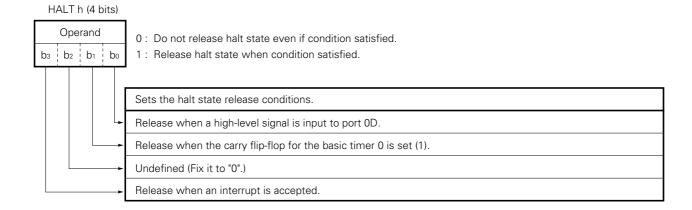

|     | 19.2  | HALT FU       | UNCTION                                                          | 280 |

|     |       | 19.2.1        | General                                                          | 280 |

|     |       | 19.2.2        | Halt State                                                       | 280 |

|     |       | 19.2.3        | Halt Release Conditions                                          | 280 |

|     |       | 19.2.4        | Halt Release by Key Input                                        | 281 |

|     |       | 19.2.5        | Halt Release by Basic Timer 0                                    | 283 |

|     |       | 19.2.6        | Halt Release by Interrupt                                        | 283 |

|     |       | 19.2.7        | When Multiple Release Conditions Set Simultaneously              | 286 |

|     | 19.3  | CLOCK-        | STOP FUNCTION                                                    | 287 |

|     |       | 19.3.1        | Clock-Stop State                                                 | 287 |

|     |       | 19.3.2        | Clock-Stop State Release                                         | 287 |

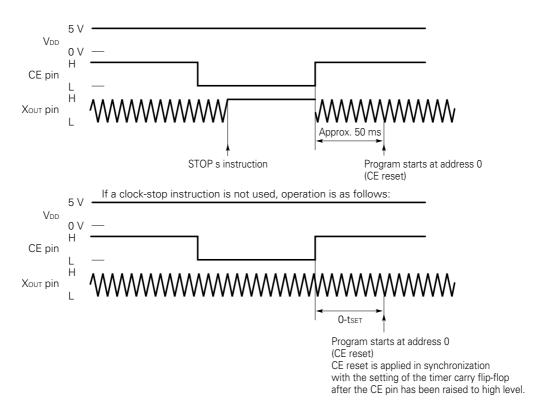

|     |       | 19.3.3        | Clock-Stop Release by CE Reset                                   | 287 |

|     |       | 19.3.4        | Clock-Stop Release by Power-On Reset                             | 288 |

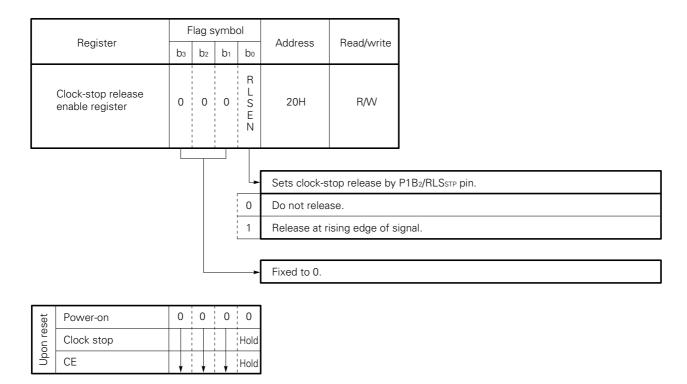

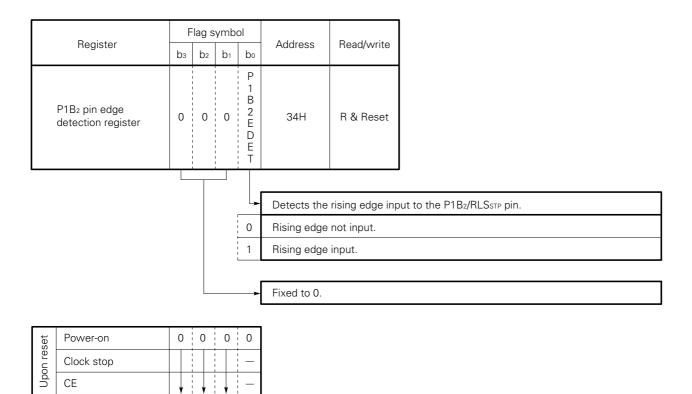

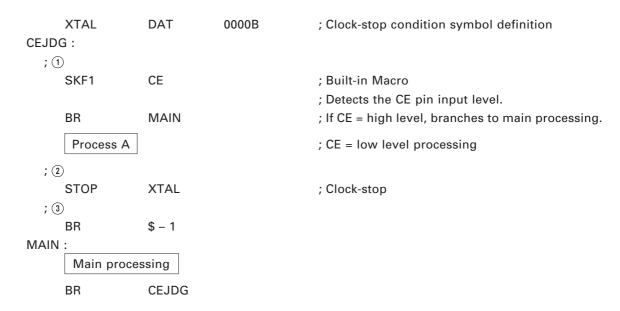

|     |       | 19.3.5        | Clock-Stop Release by R1B2/RLSsTP Pin                            | 289 |

|     |       | 19.3.6        | Cautions When Using Clock-Stop Instruction                       | 291 |

|     | 19.4  | <b>DEVICE</b> | OPERATION AT HALT AND CLOCK-STOP                                 | 292 |

|     | 19.5  | PIN PRO       | OCESSING CAUTIONS IN HALT STATE AND CLOCK-STOP STATE             | 293 |

|     | 19.6  | <b>DEVICE</b> | OPERATION CONTROL BY CE PIN                                      | 296 |

|     |       | 19.6.1        | Image Display Controller (IDC) Operation Control                 | 296 |

|     |       | 19.6.2        | PLL Frequency Synthesizer Operation Control                      | 296 |

|     |       | 19.6.3        | Clock-Stop Instruction Disable/Enable Control                    | 296 |

|     |       | 19.6.4        | Device Reset                                                     | 296 |

|     |       | 19.6.5        | Signal Input to CE Pin                                           | 297 |

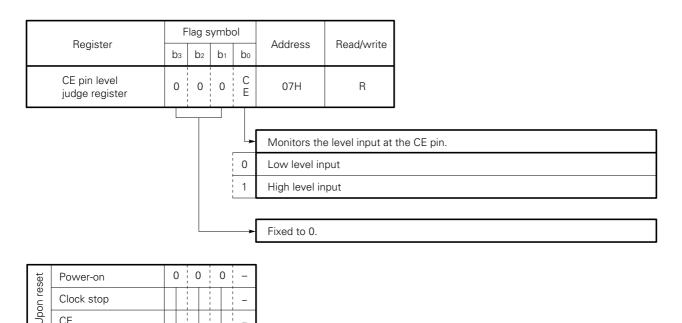

|     |       | 19.6.6        | Organization and Functions of CE Pin Level Judge Register        | 297 |

|     |       | 19.6.7        | Organization and Functions of CE Pin Edge Detection Register     | 298 |

| 20  | Reset |               |                                                                  | 299 |

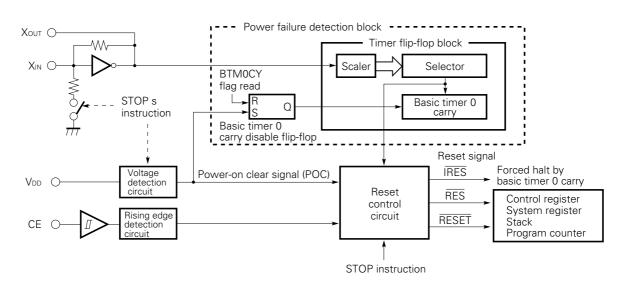

| 20. | 20.1  |               | BLOCK CONFIGURATION                                              |     |

|     | 20.2  |               | FUNCTION                                                         |     |

|     | 20.3  |               | ET                                                               |     |

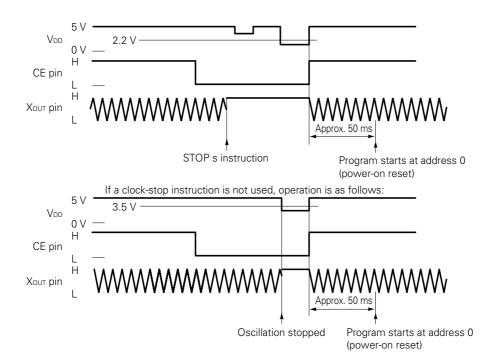

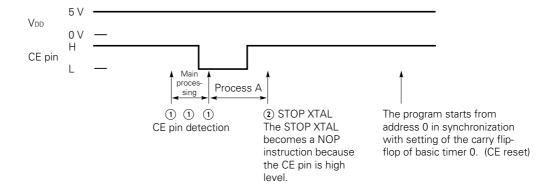

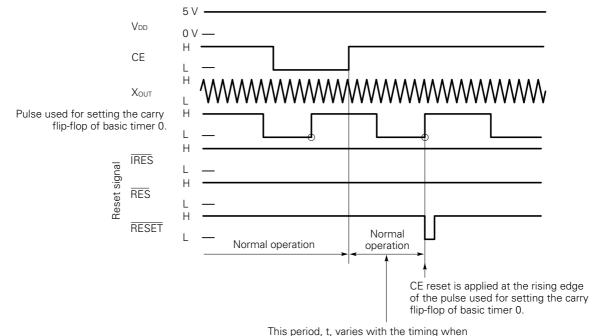

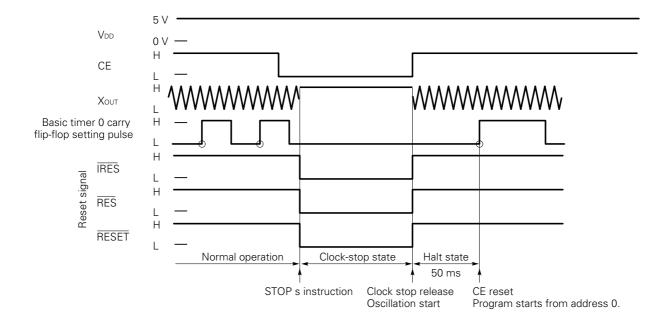

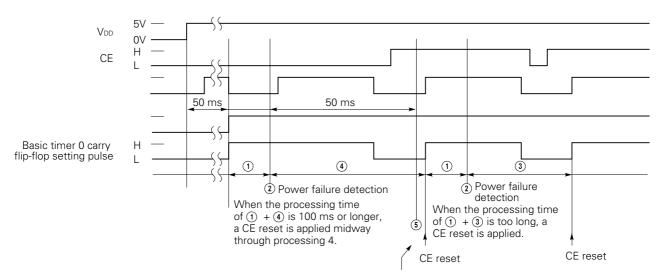

|     |       |               | CE Reset When Clock-Stop (STOP's Instruction) Not Used           |     |

|     |       | 20.3.2        | CE Reset When Clock-Stop (STOP's Instruction) Used               |     |

|     |       | 20.3.3        | Cautions at CE Reset                                             |     |

|     | 20.4  |               | -ON RESET                                                        |     |

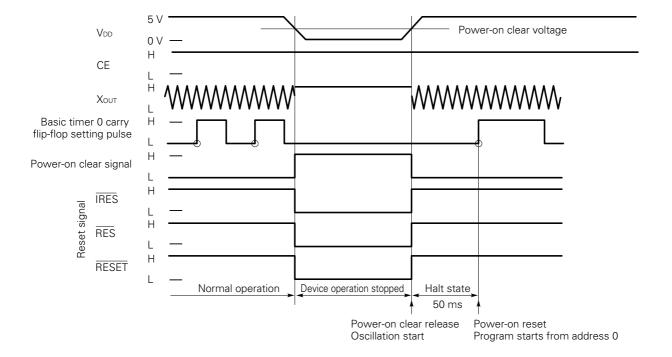

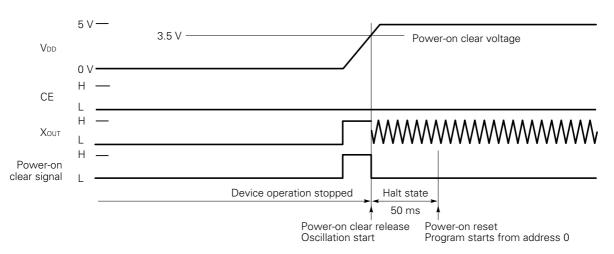

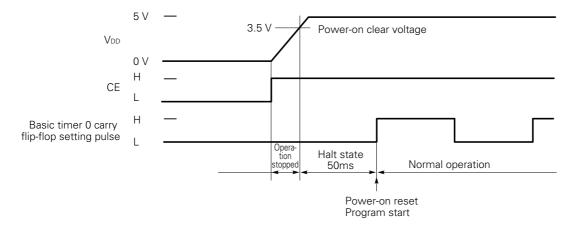

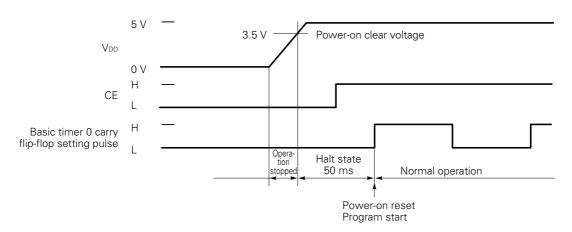

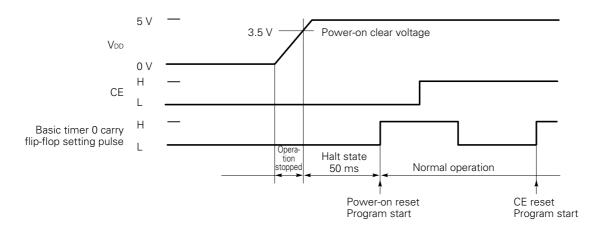

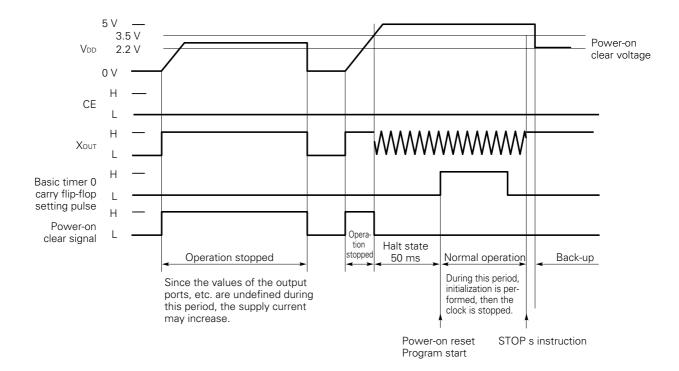

|     |       | 20.4.1        | Power-On Reset at Normal Operation                               |     |

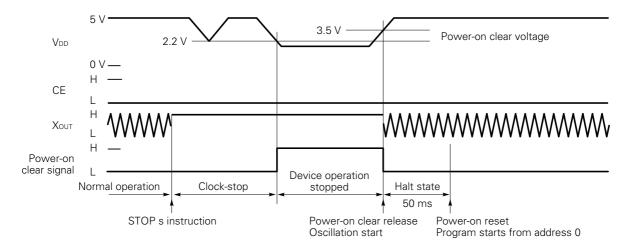

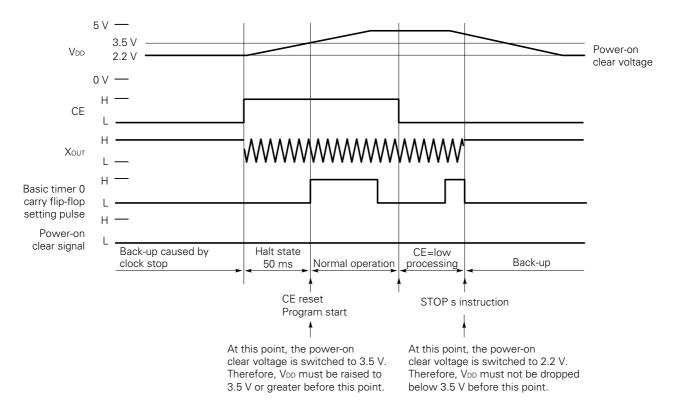

|     |       | 20.4.2        | Power-On Reset in Clock-Stop State                               |     |

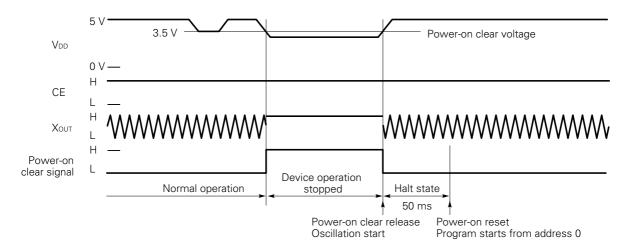

|     |       | 20.4.3        | Power-On Reset When Vpp Rises From 0 V                           |     |

|     | 20.5  |               | ONSHIP BETWEEN CE RESET AND POWER-ON RESET                       |     |

|     | 20.0  | 20.5.1        | When VDD Pin and CE Pin Rise Simultaneously                      |     |

|     |       | 20.5.2        | When CE Pin Raised in Forced Halt State Caused by Power-On Reset |     |

|     |       | 20.5.2        | When CE Pin Raised After Power-On Reset                          |     |

|     |       | 20.5.4        | Cautions When VDD Raised                                         |     |

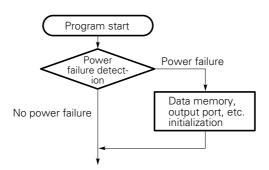

|     | 20.6  |               | FAILURE DETECTION                                                |     |

|     | _5.5  | 20.6.1        | Power Failure Detection Circuit                                  |     |

|     |       | 20.6.2        | Cautions at Power Failure Detection with BTM0CY Flag             |     |

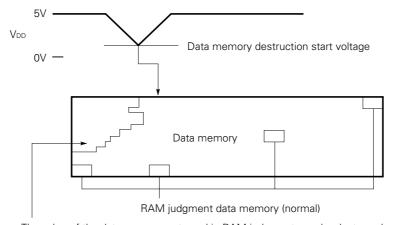

|     |       | 20.6.2        | Power Failure Detection by RAM Judgment                          |     |

|     |       | 20.6.4        | Cautions at Power Failure Detection by RAM Judgment              |     |

|     |       |               |                                                                  |     |

| 21. | INSTF  | RUCTION SET                                   |     |

|-----|--------|-----------------------------------------------|-----|

|     | 21.1   | LIST OF INSTRUCTION SET                       |     |

|     | 21.2   | INSTRUCTIONS                                  | 320 |

|     | 21.3   | ASSEMBLER (AS17K) BUILT-IN MACRO INSTRUCTIONS | 323 |

| 22. | RESEI  | RVED SYMBOLS                                  |     |

|     | 22.1   | DATA BUFFER (DBF)                             |     |

|     |        | SYSTEM REGISTER (SYSREG)                      |     |

|     | 22.3   | VRAM BANK REGISTER                            |     |

|     | 22.4   | PORT REGISTER                                 | 325 |

|     | 22.5   | REGISTER FILES                                |     |

|     | 22.6   | PERIPHERAL HARDWARE REGISTER                  |     |

|     | 22.7   | OTHERS                                        | 331 |

| 23. | ELECT  | TRICAL CHARACTERISTICS                        | 332 |

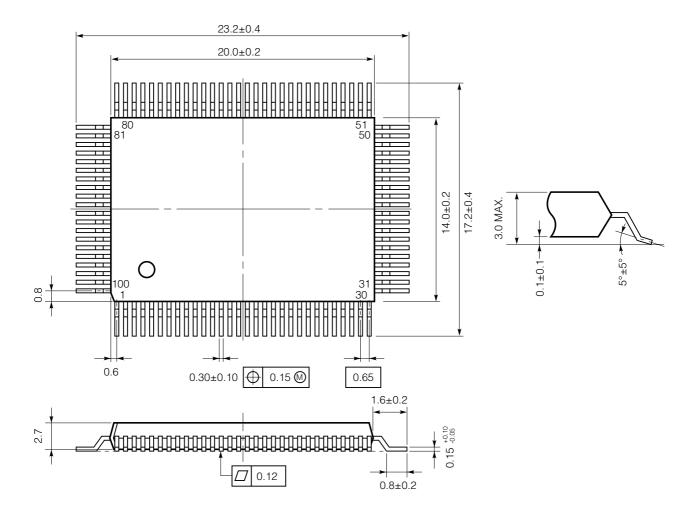

| 24. | PACK   | AGE DRAWINGS                                  | 335 |

| 25. | RECO   | MMENDED SOLDERING CONDITIONS                  | 336 |

| APF | PENDIX | ( A. NOTES ON CONNECTING A CRYSTAL            | 337 |

| APF | PENDIX | ( B. DEVELOPMENT TOOLS                        | 338 |

# 1. PIN FUNCTIONS

# 1.1 LIST OF PIN FUNCTIONS

# (1) Port pins

| Pin                                       | Function                                                                                         | I/O    | Output type                                             | At reset                   | Also used as:                       |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------|----------------------------|-------------------------------------|

| P0A <sub>0</sub>                          | 4-bit I/O port. Input or output mode can be specified in                                         | I/O    | N-ch open drain                                         | Input                      | SDA                                 |

| P0A <sub>1</sub>                          | bit units.                                                                                       |        |                                                         |                            | SCL                                 |

| P0A <sub>2</sub>                          | The pins are automatically set to input mode when the power ( $V_{DD}$ ) is turned on,           |        | CMOS push-pull                                          |                            | SCK₀                                |

| Р0А3                                      | the clock is stopped, or the device is reset with the CE pin.                                    |        |                                                         |                            | SO <sub>0</sub>                     |

| P0B <sub>0</sub>                          | 4-bit I/O port. Input or output mode can be specified in                                         | I/O    | CMOS push-pull                                          | Input                      | Slo                                 |

| P0B <sub>1</sub>                          | bit units.                                                                                       |        |                                                         |                            | _                                   |

| P0B <sub>2</sub>                          | The pins are automatically set to input mode when the power (VDD) is turned on,                  |        |                                                         |                            | 1                                   |

| Р0В3                                      | the clock is stopped, or the device is reset with the CE pin.                                    |        |                                                         |                            | HSCNT                               |

| P0C <sub>0</sub><br>l<br>P0C <sub>3</sub> | 4-bit output port. Undefined data is output when the power (VDD) is turned on.                   | Output | CMOS push-pull                                          | Outputs<br>undefined data. | _                                   |

| P0D <sub>0</sub>                          | 4-bit input port                                                                                 | Input  | _                                                       | Input with a pull-         | ADC <sub>1</sub> /XT <sub>OUT</sub> |

| P0D <sub>1</sub>                          | 4-bit iliput port                                                                                | iliput | _                                                       | down registor              | ADC <sub>2</sub> /XT <sub>IN</sub>  |

| P0D <sub>2</sub>                          |                                                                                                  |        |                                                         |                            | ADC <sub>3</sub>                    |

| P0D <sub>3</sub>                          |                                                                                                  |        |                                                         |                            | ADC <sub>4</sub>                    |

| P1A <sub>0</sub>                          | 4-bit output port                                                                                | Output | N-ch open drain with                                    | Outputs                    | _                                   |

| <br> <br> P1A3                            | 4 bit output port                                                                                | Output | intermediate with-<br>stand voltage and<br>high current | undefined data.            |                                     |

| P1B <sub>0</sub>                          | 4-bit I/O port.                                                                                  | I/O    | CMOS push-pull                                          | Input                      | _                                   |

| P1B <sub>1</sub>                          | Input or output mode can be specified in bit units.                                              |        |                                                         |                            | СКОИТ                               |

| P1B <sub>2</sub>                          |                                                                                                  |        |                                                         |                            | RLSstp                              |

| P1B <sub>3</sub>                          |                                                                                                  |        |                                                         |                            | TMIN                                |

| P1C <sub>0</sub>                          | 4-bit I/O port.                                                                                  | I/O    | CMOS push-pull                                          | Input                      | ADC <sub>5</sub>                    |

| P1C <sub>2</sub>                          | Input or output mode can be specified in 4-bit units.                                            |        |                                                         |                            | ADC <sub>7</sub>                    |

| P1C <sub>3</sub>                          |                                                                                                  |        |                                                         |                            | _                                   |

| P1D₀<br>I                                 | 4-bit output port                                                                                | Output | CMOS push-pull                                          | Outputs undefined data.    | -                                   |

| P1D₃                                      |                                                                                                  |        | N-ch open drain with                                    |                            |                                     |

| P2A <sub>0</sub>                          | 1-bit output port                                                                                | Output | intermediate with-<br>stand voltage                     | Outputs undefined data.    | PWM <sub>3</sub>                    |

| P2B <sub>0</sub>                          | 4-bit output port                                                                                | Output | N-ch open drain                                         | Outputs                    | PWM <sub>4</sub>                    |

| l<br>P2B₃                                 |                                                                                                  |        | with intermediate withstand voltage                     | undefined data.            | l<br>PWM <sub>7</sub>               |

| P2C <sub>0</sub>                          | 4-bit output port                                                                                | Output | N-ch open drain                                         | Outputs                    | PWM <sub>0</sub>                    |

| l<br>P2C₃                                 |                                                                                                  |        | with intermediate withstand voltage                     | undefined data.            | l<br>PWM₃                           |

| P2D <sub>0</sub>                          | 3-bit I/O port. Input or output mode can be specified in bit                                     | I/O    | CMOS push-pull                                          | Input                      | SCK <sub>1</sub>                    |

| P2D <sub>1</sub>                          | units.  The pins are automatically set to input mode                                             |        | _                                                       |                            | SO <sub>1</sub>                     |

| P2D <sub>2</sub>                          | when the power (VDD) is turned on, the clock is stopped, or the device is reset with the CE pin. |        |                                                         |                            | SI <sub>1</sub>                     |

# (2) Non-port pins

| Pin                   | Function                                                                                                                                                                                                                                                                                                                   | I/O                                           | Output type                         | At reset         | Also used as:                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------|------------------|------------------------------------|

| INT₀                  | Input pin for an external interrupt request signal. An interrupt request is triggered by the rising or falling edge of the signal input to this pin.                                                                                                                                                                       | Input                                         | -                                   | Input            | _                                  |

| INTnc                 | Input pin for an interrupt request signal with a noise canceler. When inputting a signal subject to much noise, such as a remotecontroller signal, use this pin to facilitate programming. Whether the rising or falling edge of the input signal is used to trigger an interrupt request can be specified with a program. | Input                                         | -                                   | Input            | -                                  |

| TMIN                  | Event input pin for basic timer 1 or 2                                                                                                                                                                                                                                                                                     | Input                                         | _                                   | Input            | PIB₃                               |

| XTIN                  | Pins for connecting the crystal (32.768                                                                                                                                                                                                                                                                                    | -                                             | _                                   | _                | P0D <sub>1</sub> /ADC <sub>2</sub> |

| ХТоит                 | kHz) for the watch timer                                                                                                                                                                                                                                                                                                   |                                               |                                     |                  | P0D <sub>0</sub> /ADC <sub>1</sub> |

| CKOUT                 | Output pin for adjusting the watch timer                                                                                                                                                                                                                                                                                   | Output                                        | CMOS push-pull                      | Input            | P1B <sub>1</sub>                   |

| SCK₀                  | Shift clock I/O pins                                                                                                                                                                                                                                                                                                       | I/O                                           | CMOS push-pull                      | Input            | P0A <sub>2</sub>                   |

| SCK <sub>1</sub>      |                                                                                                                                                                                                                                                                                                                            |                                               |                                     |                  | P2D <sub>0</sub>                   |

| SIo                   | Serial data input pins                                                                                                                                                                                                                                                                                                     | Input                                         | _                                   | Input            | P0B <sub>0</sub>                   |

| SI <sub>1</sub>       |                                                                                                                                                                                                                                                                                                                            |                                               |                                     |                  | P2D <sub>2</sub>                   |

| SO <sub>0</sub>       | Serial data output pins                                                                                                                                                                                                                                                                                                    | Output                                        | CMOS push-pull                      | Input            | P0A <sub>3</sub>                   |

| SO <sub>1</sub>       |                                                                                                                                                                                                                                                                                                                            |                                               |                                     |                  | P2D <sub>1</sub>                   |

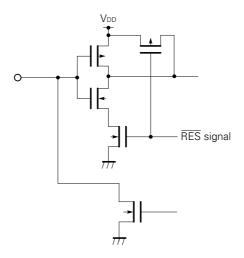

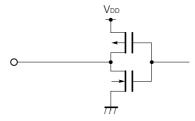

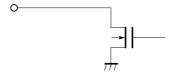

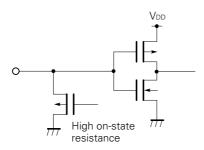

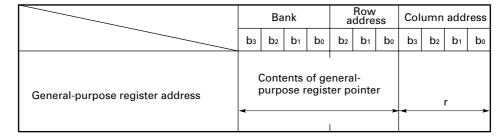

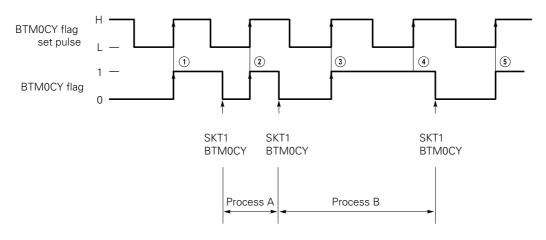

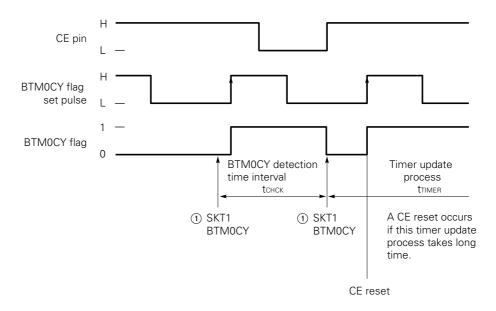

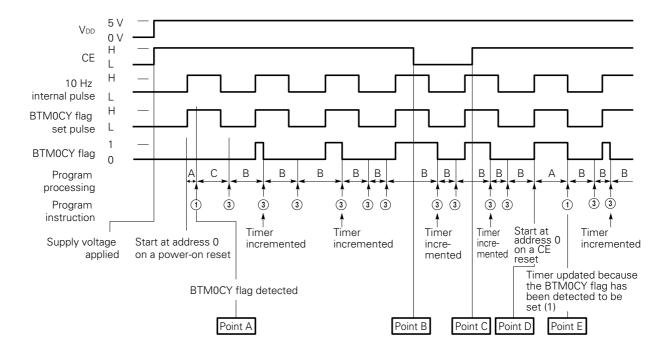

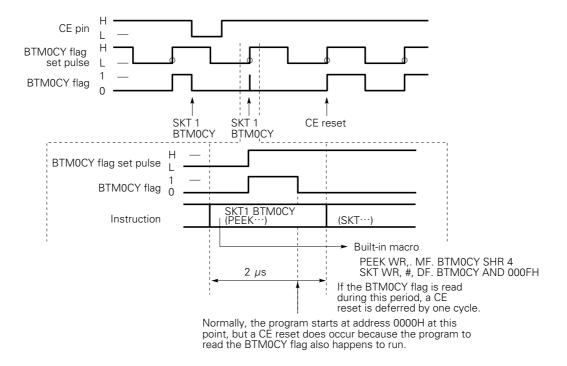

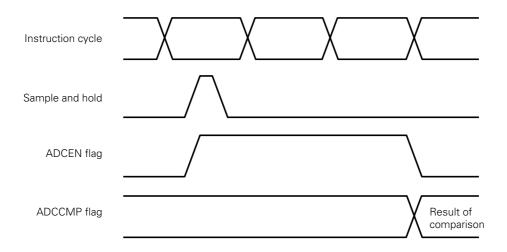

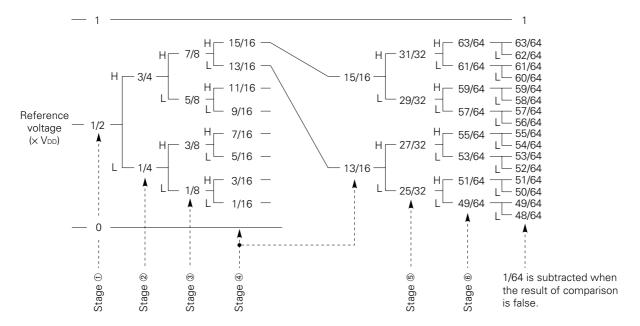

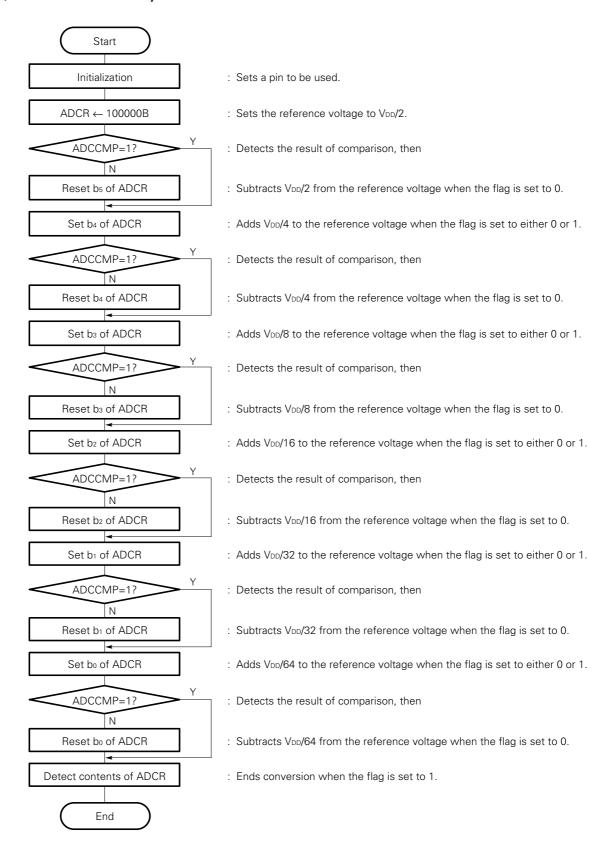

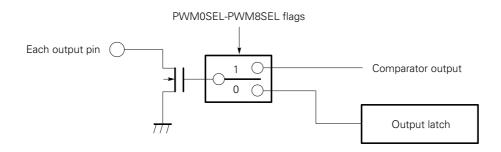

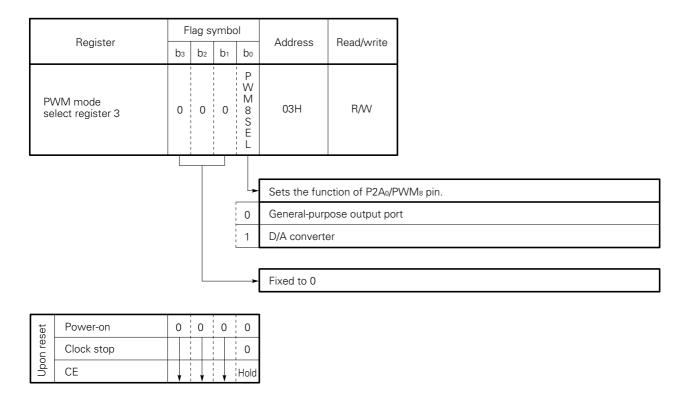

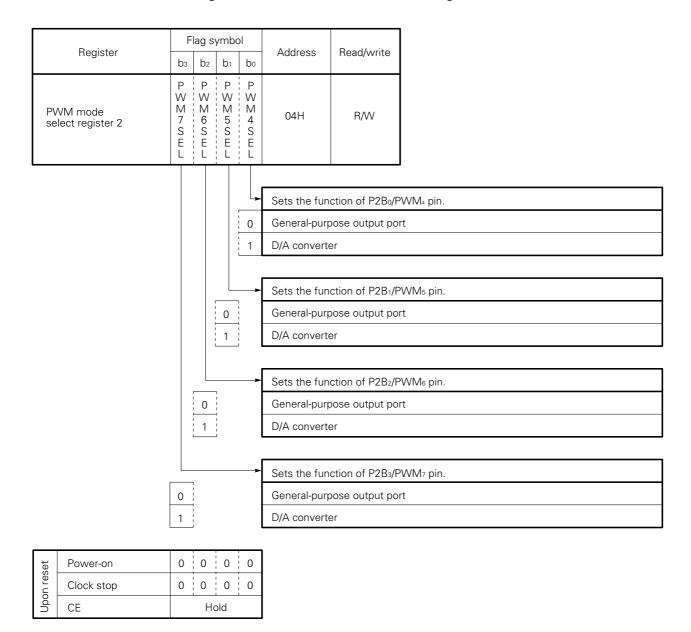

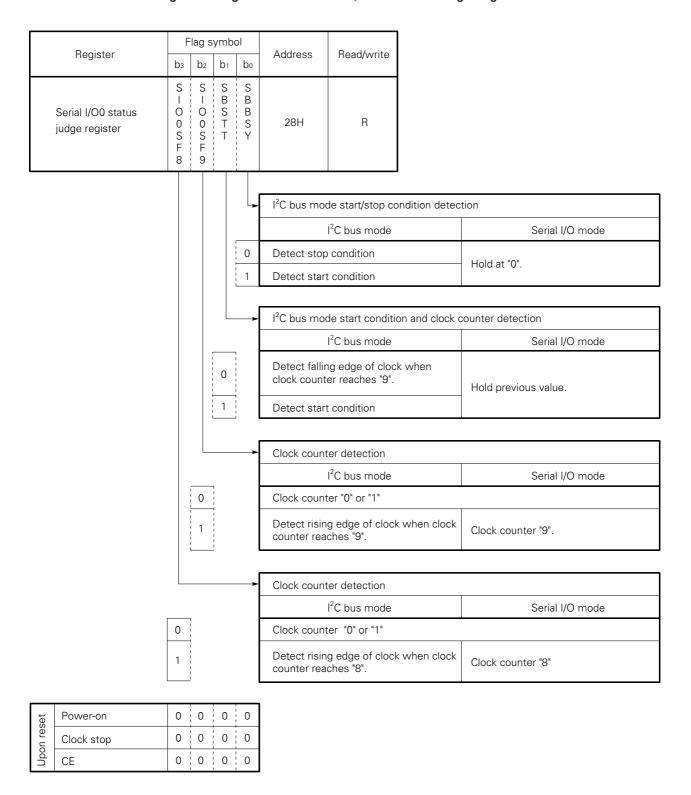

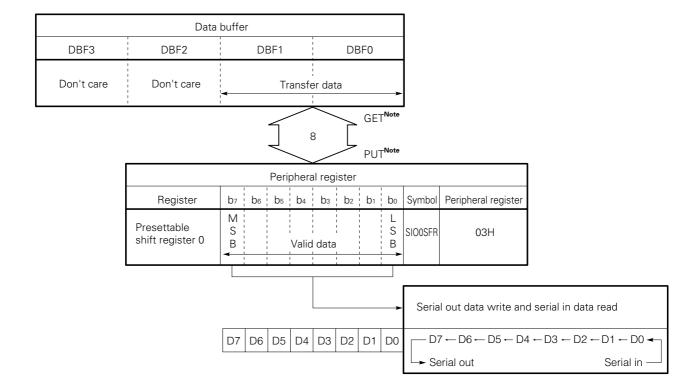

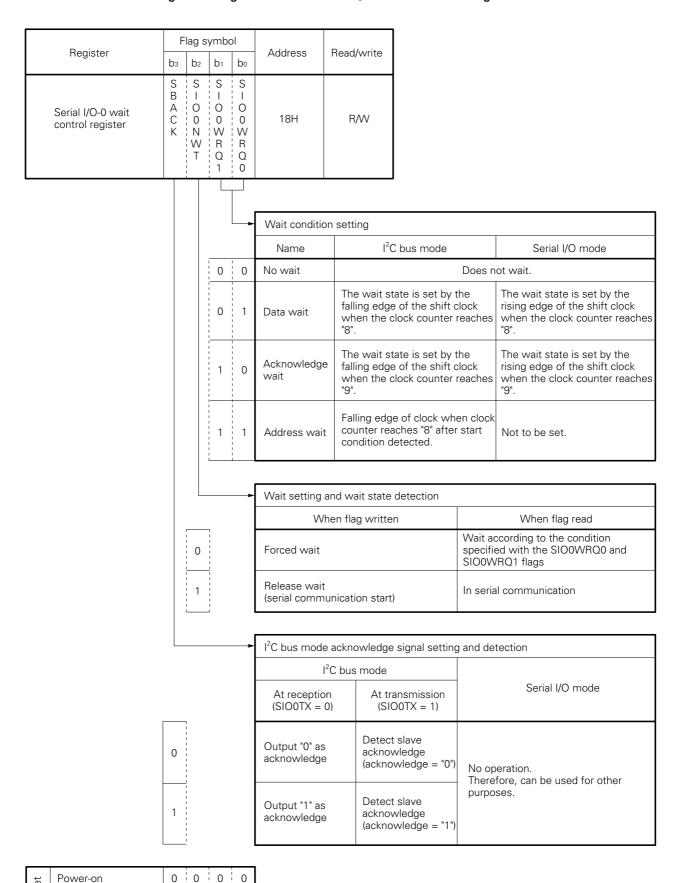

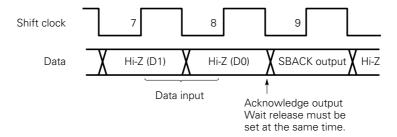

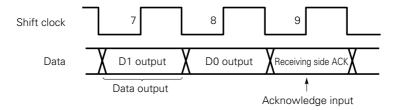

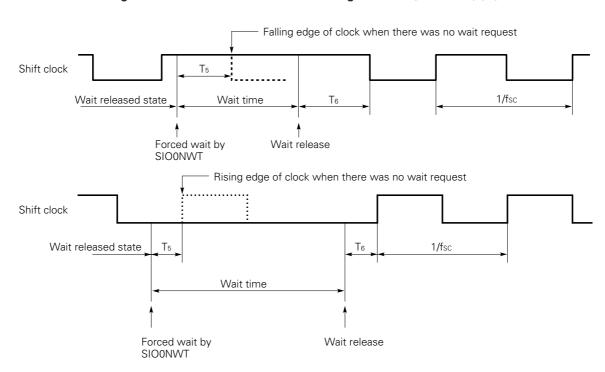

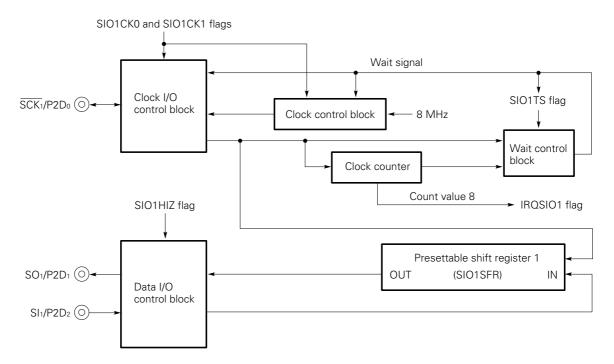

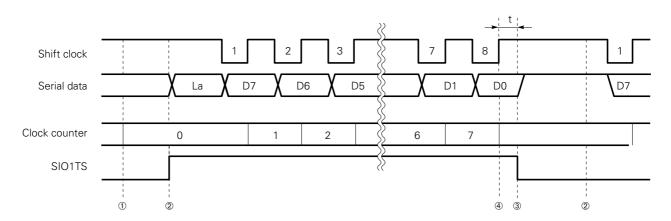

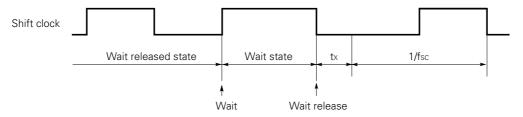

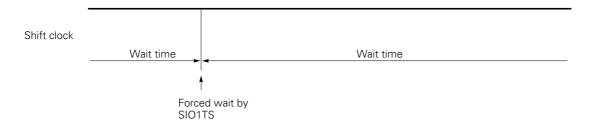

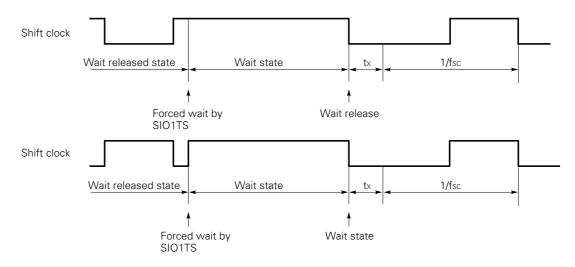

| SCL                   | Shift clock I/O pin                                                                                                                                                                                                                                                                                                        | I/O                                           | N-ch open drain                     | Input            | P0A <sub>1</sub>                   |