February 1998

# **Digital QPSK Demodulator**

#### **Features**

- 25.6MHz or 26.97MHz Clock Rates

- Single Chip QPSK Demodulator with 10kHz Tracking Loop

- Square Root of Raised Cosine ( $\alpha$  = 0.4) Matched Filtering

- 2.048 MBPS Reconstructed Output Data Stream

- · Bit Synchronization with 3kHz Loop Bandwidth

- · Internal Equalization for Multipath Distortion

- 6-Bit Real Input: Digitized 10.7MHz or 2.1MHz IF

- Level Detection for External IF AGC Loop

- 0.1s Acquisition Time

- 10<sup>-9</sup> BER

- <116mA on +5.0V Supply

## **Applications**

- · Cable Data Link Receivers

- Cable Control Channel Receivers

## Ordering Information

| PART NUMBER     | TEMP.<br>RANGE (°C) | PACKAGE       | PKG.<br>NO. |

|-----------------|---------------------|---------------|-------------|

| HSP50306SC-27   | 0 to 70             | 16 Ld SOIC    | M16.3       |

| HSP50306SC-2796 | 0 to 70             | Tape and Reel |             |

| HSP50306SC-25   | 0 to 70             | 16 Ld SOIC    | M16.3       |

| HSP50306SC-2596 | 0 to 70             | Tape and Reel |             |

## Description

The HSP50306 is a 6-bit QPSK demodulator chip designed for use in high signal to noise environments which have some multipath distortion. The part recovers 2.048 MBPS data from samples of a QPSK modulated 10.7MHz or 2.1MHz carrier. The chip coherently demodulates the waveform, recovers symbol timing, adaptively equalizes the signal to remove multipath distortion, differentially decodes and multiplexes the data decisions. 8-A lock signal is provided to indicate when the tracking loops are locked and the data decisions are valid. To optimize performance, a gain error feedback signal is provided which can be filtered and used to close an I.F. AGC loop around the A/D converter.

The QPSK demodulator derives all timing from CLKIN. The chip divides this clock by 2 to provide the sample clock for the external A/D converter. The -27 version operates at a clock input of 26.97MHz and demodulates a 10.7MHz QPSK signal to recover the 2048 KSPS data. The -25 version operates at a clock input of 25.6MHz and demodulates a 2.1MHz QPSK signal to recover the 2048 KSPS data. Variation from these CLKIN frequencies will progressively degrade the receive data rate, the receive IF, acquisition sweep rate, acquisition sweep range and loop bandwidths as the deviation increases from normal CLKIN. Details on the maximum allowable deviation are found in the Input Characteristics section. The HSP50306 processes 6-bit offset binary data. 4-bit data provides adequate performance for many applications.

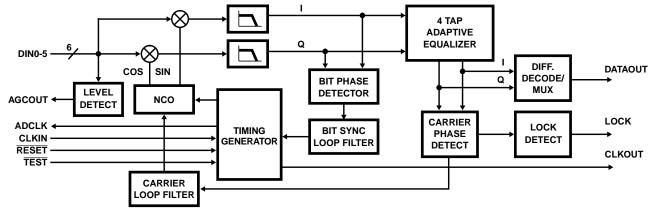

# Block Diagram

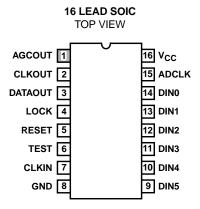

# Pinout

# Pin Description

| NAME            | SOIC PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|-----------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | 16       | -    | +5V Power Supply                                                                                                                                                                                                                                                                        |

| GND             | 8        | -    | Ground                                                                                                                                                                                                                                                                                  |

| CLKIN           | 7        | I    | Clock input. This is the processing clock for the part. All timing is derived from this clock.                                                                                                                                                                                          |

| DIN (5:0)       | 9-14     | I    | I.F. input samples from the A/D converter. These bits interpreted as offset binary format. DIN5 is the MSB. If fewer than 6 bits are used, the bits from the A/D should be connected to the MSBs of the input and the unused LSBs grounded.                                             |

| ADCLK           | 15       | 0    | This output clock is the clock for the A/D converter.                                                                                                                                                                                                                                   |

| AGCOUT          | 1        | 0    | This output indicates whether the magnitude of the input samples are above or below the expected level. This output is provided as an error detector for an external AGC loop. The output is low when the input is greater than nominal, and high when the input is lower than nominal. |

| DATAOUT         | 3        | 0    | This is the recovered data.                                                                                                                                                                                                                                                             |

| CLKOUT          | 2        | 0    | This is the recovered clock.                                                                                                                                                                                                                                                            |

| LOCK            | 4        | 0    | This signal indicates that the carrier tracking loop is locked and data on the DOUT pin should be valid.                                                                                                                                                                                |

| RESET           | 5        | I    | This input is provided to for initialization and test. Active low.                                                                                                                                                                                                                      |

| TEST            | 6        | I    | This input is provided for test. Pull high for normal operation.                                                                                                                                                                                                                        |

The Block Diagram of the QPSK Demodulator is shown on page 1. To demodulate the data, the I.F. samples are multiplied by sine and cosine samples from a numerically controlled oscillator. The digital mixer outputs are then low pass filtered to remove mixer products. The filtered data is then equalized by a 4 tap equalizer (1 precursor, one reference tap, and a 2 tap Decision Feedback Equalizer (DFE) to remove distortion caused by multipath. The output of the equalizer is differentially decoded and multiplexed into the output data stream. The carrier tracking loop providing the L.O. for the digital mixer is a second order digital Costas loop with a tracking bandwidth of ~10kHz. A sweep circuit searches the carrier uncertainty using a triangle sweep algorithm during acquisition. A lock detector controls the sweep and indicates when valid data is available. The recovered data rate clock is generated by another numerically controlled oscillator. The timing recovery loop is a first order decision directed digital phase locked with a loop bandwidth of ~3kHz. The Level Detect circuitry generates the AGC error signal by rectifying the I.F. input samples and comparing them against a threshold. The error signal is low if the signal magnitude is above the upper threshold, high if the magnitude is below the lower limit.

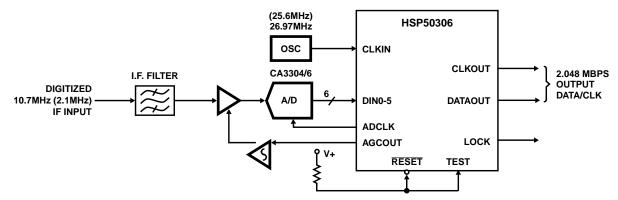

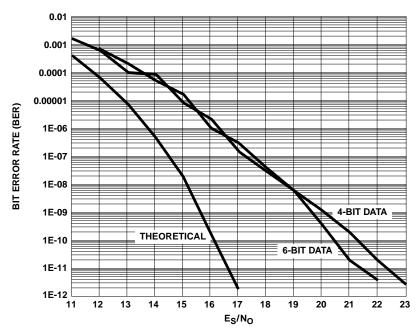

Figure 1 shows the circuit of a typical demodulator application. The typical Bit Error Rate (BER) performance is shown in Figure 2 for both 4-bit and 6-bit quantized inputs. The theoretical QPSK BER Performance Curve is provided for reference. Note that the BER performance shown in Figure 2 includes a multipath distortion element at the input, in addition to the desired signal. This multipath distortion is representative of receive signal distortions found in cable data links.

Table 1 details the BER, Acquisition and Delay Performance Specifications of the HSP50306 QPSK demodulator chip, based on an input that complies with the specifications detailed in Table 2.

## Application Example

FIGURE 1. APPLICATIONS CIRCUIT EXAMPLE

NOTE: Simulation performed using alpha = 0.4 Root Raised Cosine Transmit Filtering, Multipath -10dBc at  $72^{0}$  at  $1.6\mu s$ .

FIGURE 2. TYPICAL BIT ERROR RATE PERFORMANCE

#### **TABLE 1. PERFORMANCE SPECIFICATIONS**

| SPECIFICATION           | PERFORMANCE                                                                                   |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------|--|--|

| BER                     | Better than 1.0 x 10 <sup>-9</sup> with specified input signal characteristics. See Figure 1. |  |  |

| Acquisition Time        | Acquisition within 0.1s from applying an input signal with the specified characteristics.     |  |  |

| Carrier Loop Bandwidth  | 10kHz                                                                                         |  |  |

| Bit Sync Loop Bandwidth | 3kHz                                                                                          |  |  |

| Throughput Delay        | Less than 6 output bit times.                                                                 |  |  |

#### TABLE 2. INPUT SIGNAL CHARACTERISTICS (NOTE 1)

| PARAMETER              | SPECIFICATION                                                                                                                                                                                                               |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Carrier Frequency      | 10.7 x 10 <sup>6</sup> ±40kHz.                                                                                                                                                                                              |  |  |

| Bit Rate               | $2.048 \times 10^6 \pm 0.01\%$ .                                                                                                                                                                                            |  |  |

| Modulation Format      | QPSK w/differential encoding specified as:  00: 0° phase change 10: +90° phase change 01: -90° phase change 11: 180° phase change (Note 2)                                                                                  |  |  |

| Filtering              | Square root of raised cosine matched filtering ( $\alpha = 0.4$ ).                                                                                                                                                          |  |  |

| Input RMS Signal Level | Set input p-p signal to full scale on the A/D converter.                                                                                                                                                                    |  |  |

| Input Data Format      | 6 bits, offset binary.                                                                                                                                                                                                      |  |  |

| Input Clock Frequency  | 26.97MHz ±0.015% (Note 3) for -27; 25.6MHz ±0.015% for -25.                                                                                                                                                                 |  |  |

| SINAD                  | >25.5dB SNR (thermal (AWGN)), >28dB (adjacent channel interference).                                                                                                                                                        |  |  |

| Multipath Distortion   | Total energy in multipath distortion -10dBc >95% of multipath energy within 2µs from main path. If the multipath changes rapidly, the bit error rate may exceed the above specification until the equalizer has readjusted. |  |  |

#### NOTES:

- 1. All frequencies are relative to the input clock frequency. For example, the bit rate is actually ~0.075936 \* f<sub>CLK</sub>. The frequencies provided in this document are only valid for a 26.97MHz or 25.6MHz clock.

- 2. Each pair of input bits is encoded into a phase change relative to the previous symbol. In the HSP50306, the symbol to symbol phase change is decoded into the transmitted bit pair which is multiplexed into the output data stream.

- 3. While the device is static CMOS and can be clocked down to close to DC, the specified range indicates the accuracy needed to maintain the data rate inside the bit sync tracking loop bandwidth assuming 50ppm tx and 100ppm rx crystal accuracies.

## Two Versions: Different Applications

The -27 and -25 versions of the HSP50306 Digital QPSK Demodulator are not simply different speed grades of the same device, but are designs which have proportionally scaled clocks and bandwidths for different applications. NOTE: While these parts are pin for pin compatible, in most applications they cannot be used as functional equivalent substitutes for each other. Key differences are:

- The -27 version of the HSP50306 has an input IF of 10.7MHz with an input clock of 26. 97MHz.

- The -25 version of the HSP50306 has an input IF of 2.1MHz with an input clock of 25. 6MHz.

In both the -27 and -25 designs, the sample rate clock for the input IF signal is half of the CLK frequency. **NOTE: Sample rate clock is designated by**  $f_S = f_{CLK}/2$ . Aside from input IF and input clock, all other performance parameters of the two parts are identical for their respective IF inputs.

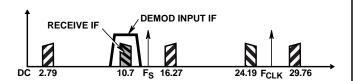

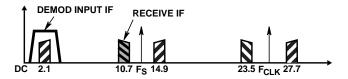

## 10.7MHz Input IF Applications

Both the -27 and -25 parts can be used in 10.7MHz IF Applications. Figures 3 and 4 show the frequency spectrum for the sampled 10.7MHz IF input signals for both the -27 and -25 versions, respectively. In the 10.7MHz IF Application, the -25 version offers tighter filtering capability than the -27 version because the lower IF allows use of low pass filtering. Also, the lower IF of the -25 version has inherently lower internal processing spectral spurs than the -27 version. Note that the receive IF for the HSP50306SC-27 is the input IF to the demodulator. For the HSP50306SC-25, the receive IF is 10.7MHz, but the processing is done on the spectral image at 2.1MHz. Examine the spectral inversion between the 10.7MHz Receive IF and the 2.1MHz demodulator input in Figure 4. The transmit differential encoder must take into account this spectral reversal. The required encoding is shown in Table 3. This part was designed to be paired with the HSP50307 Burst Modulator, and can be operated from the same 25.6MHz reference clock.

FIGURE 3. SAMPLED SPECTRUM FOR THE -27 VERSIONS (f<sub>CLK</sub> = 26.97MHz)

FIGURE 4. SAMPLED SPECTRUM FOR THE -25 VERSIONS (f<sub>CLK</sub> = 25.6MHz)

TABLE 3. DIFFERENTIAL ENCODING REQUIRED FOR THE -27 AND -25 DEMODULATORS RECEIVING 10.7MHz IF

| INPUT<br>BITS | PHASE CHANGE<br>REQUIRED FOR -27<br>DEMODULATION | PHASE CHANGE<br>REQUIRED FOR -25<br>DEMODULATION |  |  |

|---------------|--------------------------------------------------|--------------------------------------------------|--|--|

| 00            | 0o                                               | 0o                                               |  |  |

| 01            | -90°                                             | 90°                                              |  |  |

| 10            | 90°                                              | -90°                                             |  |  |

| 11            | 180 <sup>0</sup>                                 | 180 <sup>0</sup>                                 |  |  |

## **Absolute Maximum Ratings** $T_A = 25^{\circ}C$

####

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4)     | $\theta_{JA}$ (°C/W) |

|------------------------------------------|----------------------|

| SOIC Package                             | . 100                |

| Maximum Junction Temperature             | 150°C                |

| Maximum Storage Temperature Range        | -65°C to 150°C       |

| Maximum Lead Temperature (Soldering 10s) | 300°C                |

| (SOIC - Lead Tips Only)                  |                      |

#### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

4.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## **DC Electrical Specifications** $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}$ to $70^{\circ}C$

| PARAMETER                        | SYMBOL            | TEST CONDITIONS                                                        | MIN | MAX | UNITS |

|----------------------------------|-------------------|------------------------------------------------------------------------|-----|-----|-------|

| Power Supply Current             | I <sub>CCOP</sub> | V <sub>CC</sub> = Max, CLK = 28.6MHz<br>(Notes 5, 6)                   | -   | 114 | mA    |

| Standby Power Supply Current     | ICCSB             | V <sub>CC</sub> = Max, Outputs Not Loaded                              | -   | 500 | μΑ    |

| Input Leakage Current            | I <sub>I</sub>    | $V_{CC} = Max$ , Input = 0V or $V_{CC}$                                | -10 | 10  | μΑ    |

| CMOS Output High (ADCLK, AGCOUT) | V <sub>OHC</sub>  | V <sub>CC</sub> = Min, I <sub>OH</sub> = -400μA                        | 3.7 | -   | V     |

| CMOS Output Low (ADCLK, AGCOUT)  | V <sub>OLC</sub>  | V <sub>CC</sub> = Min, I <sub>OL</sub> = 2mA                           | -   | 0.4 | V     |

| Logical One Input Voltage        | V <sub>IH</sub>   | V <sub>CC</sub> = Max                                                  | 2.0 | -   | V     |

| Logical Zero Input Voltage       | V <sub>IL</sub>   | V <sub>CC</sub> = Min                                                  | -   | 0.8 | V     |

| Logical One Output Voltage       | V <sub>OH</sub>   | $I_{OH} = -400\mu A$ , $V_{CC} = Min$                                  | 2.4 | -   | V     |

| Logical Zero Output Voltage      | V <sub>OL</sub>   | I <sub>OL</sub> = 2mA, V <sub>CC</sub> = Min                           | -   | 0.4 | V     |

| Input Capacitance                | C <sub>IN</sub>   | CLK = 1MHz                                                             | -   | 10  | pF    |

| Output Capacitance               | C <sub>OUT</sub>  | All measurements referenced to GND.<br>T <sub>A</sub> = 25°C, (Note 7) | -   | 10  | pF    |

#### NOTES:

- 5. Power supply current is proportional to frequency. Typical rating is 4mA/MHz.

- 6. Output load per test circuit and  $C_1 = 40pF$ .

- 7. Not tested, but characterized at initial design and at major process/design changes.

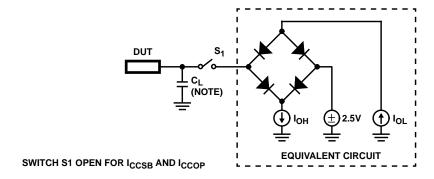

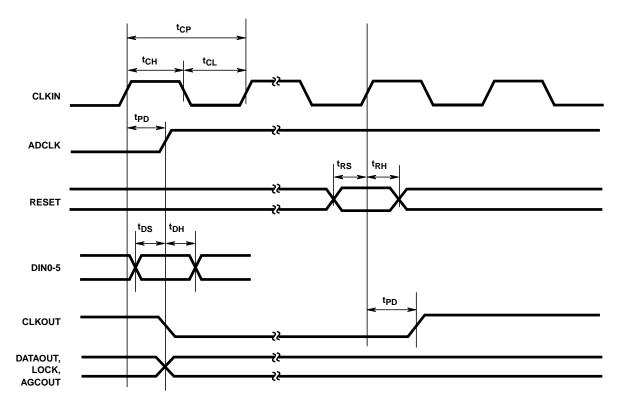

**AC Electrical Specifications** 27MHz Clock Rate,  $V_{CC} = 5.0V \pm 5\%$ ,  $T_A = 0^{\circ}$  to  $70^{\circ}$ C (Note 8)

| PARAMETER                             | SYMBOL          | NOTES | MIN | MAX | UNITS |

|---------------------------------------|-----------------|-------|-----|-----|-------|

| CLK Period                            | t <sub>CP</sub> |       | 36  | -   | ns    |

| CLK High                              | <sup>t</sup> CH |       | 12  | -   | ns    |

| CLK Low                               | t <sub>CL</sub> |       | 12  | -   | ns    |

| Setup RESET to CLK                    | t <sub>RS</sub> |       | 15  | -   | ns    |

| Hold Time RESET to CLK                | <sup>t</sup> RH |       | 1   | -   | ns    |

| Setup Time DIN0-5 to ADCLK            | t <sub>DS</sub> | 9     | 15  | -   | ns    |

| Hold Time DIN0-5 to ADCLK             | <sup>t</sup> DH | 9     | 2   | -   | ns    |

| CLK to DATAOUT, LOCK, AGCOUT          | t <sub>PD</sub> |       | -   | 25  | ns    |

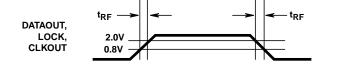

| Output Rise, Fall Time                | t <sub>RF</sub> | 10    | -   | 8   | ns    |

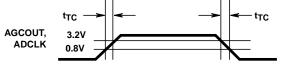

| Output Rise, Fall Time (CMOS Outputs) | tTC             | 10    | -   | 12  | ns    |

#### NOTES:

- 8. AC Testing is performed as follows: Input levels 0.0V to 3.0V. Timing reference levels = 1.5V. Output load circuit with  $C_L$  = 40pF. Output transition measured at  $V_{OH}$ \_1.5V and  $V_{OL}$ \_1.5V.

- 9. The set up and hold times for DIN (5:0) are with respect to the rising edge of ADCLKOUT. These parameters are guaranteed by design and characterization but not tested. An A/D converter with a clock to data out specification of 55ns and a data hold from clock specification of 2ns will meet these requirements at an oscillator clock frequency of 26.97MHz. Intersil recommends the CA3304 or CA3306 A/D converters for use with the HSP50306.

- 10. Controlled via design or process parameters and not directly tested. Characterized upon initial design and at major process or design changes.

## AC Test Load Circuit

NOTE: Test head capacitance

## Waveforms

FIGURE 5.

FIGURE 6. OUTPUT RISE AND FALL TIMES

FIGURE 7. OUTPUT RISE AND FALL TIMES

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com