# **SIEMENS**

# ISDN Terminal Adapter Circuit (ITAC®)

**PSB 2110**

**CMOSIC**

#### 1 Features

#### **DTE Interface**

- Support of async and sync interfaces (X.21, X.21 bis, V.24, RS232C, V.35)

- Modem control lines

- Programmable baud rates

#### **Protocol Support**

- Bit rate adaptation according to X.30, V.110, ECMA.102

- USART and HDLC controller to support V.120 and DMI applications

- Support of V.120 protocol sensetive and bit transparent mode

- Hayes modem protocol support

- In-band parameter exchange and signaling support

# Synchronous Network Interface

- Supports SSI- and IOM<sup>®</sup>-2-interface for Basic Rate applications

- Supports time-slot oriented interface (up to64-time slots)

- Supports PCM30- and PCM24-interface for Primary Rate applications

- IOM-2 MONITOR channel controller

# Microprocessor Interface

- Siemens/Intel multiplexed microprocessor interface

- DMA support for USART or HDLC controller

# **Power Supply**

- Single +5 V supply

- Low power CMOS technology

- Power down (standby) mode

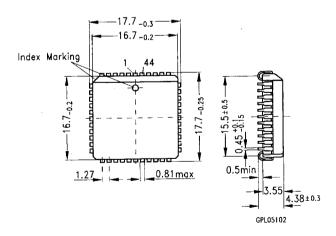

| Туре       | Version | Ordering Code | Package        |

|------------|---------|---------------|----------------|

| PSB 2110-N | V2.2    | Q67100-H6293  | P-LCC-44 (SMD) |

| PSB 2110-P | V2.2    | Q67100-H6294  | P-DIP-40       |

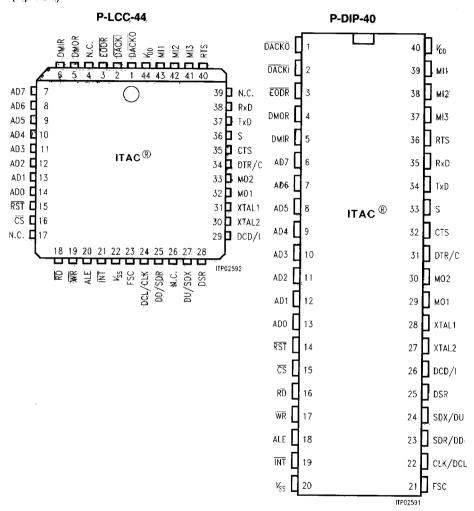

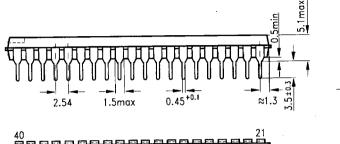

# Pin Configurations

(top view)

# 1.1 Pin Definitions and Functions

| Pin No.<br>P-LCC                          | Pin No.<br>P-DIP                         | Symbol                                               | Input (I)<br>Output (O)<br>Open Drain (OD)    | Function                                                                                                                                                                                     |

|-------------------------------------------|------------------------------------------|------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14<br>13<br>12<br>11<br>10<br>9<br>8<br>7 | 13<br>12<br>11<br>10<br>9<br>8<br>7<br>6 | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | 1/O<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O | Multiplexed Address/Data Bus. Transfers addresses and data between the microprocessor and the ITAC.                                                                                          |

| 16                                        | 15                                       | CS                                                   | I                                             | Chip Select. A low level on this line selects the ITAC for a read/ write operation.                                                                                                          |

| 19                                        | 17                                       | WR                                                   | I                                             | Write. A low level on this line indicates a write operation to the ITAC.                                                                                                                     |

| 18                                        | 16                                       | RD                                                   | I                                             | <b>Read.</b> A low level on this line indicates a read operation from the ITAC.                                                                                                              |

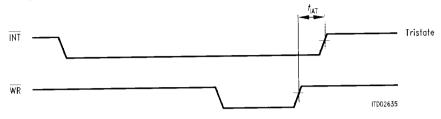

| 21                                        | 19                                       | ĪNT                                                  | OD                                            | Interrupt Request. This signal is active (low) while the ITAC indicates an interrupt to the microprocessor. It is an open drain output and level active.                                     |

| 20                                        | 18                                       | ALE                                                  | I                                             | Address Latch Enable. A transition from high to low latches the contents of the AD1-AD6 lines and use them as the address.                                                                   |

| 6                                         | 5                                        | DMIR                                                 | 0                                             | DMA Input Request. A high leve on this line indicates a request for a DMA transfer from memory to the ITAC. It is released by a write operation to one of the corresponding FIFO-addresses.  |

| 5                                         | 4                                        | DMOR                                                 | 0                                             | DMA Output Request. A high level on this line indicates a request for a DMA transfer from the ITAC to memory. It is released by a read operation to one of the corresponding FIFO-addresses. |

# **Features**

# Pin Definitions and Functions (cont'd)

| Pin No.<br>P-LCC | Pin No.<br>P-DIP | Symbol                                                         | Input (I) Output (O) Open Drain (OD) | Function                                                                                                                                                                                                        |

|------------------|------------------|----------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                | 2 DACKI I        |                                                                | I                                    | DMA Input Acknowledge. A low level on this line indicates an acknowledgement to a DMA Input Request. It will select the corresponding FIFO address-space. It will also return the DMIR output to a low level.   |

| 1                | 1                | 1 DACKO I DMA Ou level on knowledg Request. sponding will also |                                      | DMA Output Acknowledge. A low level on this line indicates an acknowledgement to a DMA Output Request. It will select the corresponding FIFO address-space. It will also return the DMOR output to a low level. |

| 3                | 3                | EODR                                                           | 0                                    | End of DMA Request. A low level on this line indicates the end of a DMA transfer. It will go active only for HDLC reception after the last byte of a frame has been read.                                       |

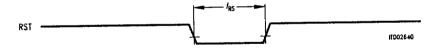

| 15               | 14               | RST                                                            | I                                    | Reset. A low level of at least 2 $\mu$ s will reset the ITAC.                                                                                                                                                   |

| 27               | 24               | SDX/DU                                                         | O/OD                                 | Synchronous Data Transmit/<br>Data Upstream. Transmit data out-<br>put to the network interface.                                                                                                                |

| 25               | 23               | SDR/DD                                                         | I                                    | Synchronous Data Receive/Data Downstream. Receive data input from the network interface.                                                                                                                        |

| 24               | 22               | CLK/DCL                                                        | I                                    | Clock/Data Clock. Clock signal on the network interface.                                                                                                                                                        |

| 23               | 21               | FSC                                                            | I                                    | <b>Frame Sync.</b> 8-kHz signal which indicates the start of a new frame on the network interface.                                                                                                              |

| 37               | 34               | TxD                                                            | I                                    | Transmit Data from the Terminal. This line is the data input to the ITAC.                                                                                                                                       |

| 38               | 35               | RxD                                                            | 0                                    | Receive Data to the Terminal. This line is the data output from the ITAC.                                                                                                                                       |

# Pin Definitions and Functions (cont'd)

| Pin No.<br>P-LCC | Pin No.<br>P-DIP | Symbol            | Input (I)<br>Output (O)<br>Open Drain (OD) | Function                                                                                                                                                                                                                              |

|------------------|------------------|-------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36               | 33 S             |                   | O/OD                                       | S Clock. Bit element timing for the synchronous DCE interface. Data is clocked off on the RxD pin on the falling edge of S. Data on the TxD pin is latched on the rising edge of S. It is tristate for async DCE interface selection. |

| 34               | 31               | DTR/C             | I                                          | Data Terminal Ready/Control.  Data Terminal Ready (108) interchange circuit if V.24 interface is selected. Control interchange circuit if X.21 interface is selected.                                                                 |

| 29               | 29 26 DCD/I      |                   | O/OD                                       | Data Channel Received Line Signal Detector Carrier Detect/Indicate. DCD (109) interchange circuit if V.24 interface is selected. Indicate interchange line if X.21 interface is selected.                                             |

| 40               | 36 RTS           |                   | I                                          | Request to Send. RTS (105) interchange circuit if V.24 interface is selected.                                                                                                                                                         |

| 35               | 32               | CTS               | O/OD                                       | Clear to Send. CTS (106) interchange circuit if V.24 interface is selected.                                                                                                                                                           |

| 28               | 25               | DSR               | O/OD                                       | <b>Data Set Ready.</b> DSR (107) interchange circuit if V.24 interface is selected.                                                                                                                                                   |

| 43<br>42<br>41   | 39<br>38<br>37   | MI1<br>MI2<br>MI3 | I<br>I<br>I                                | <b>Multifunctional Input 1-3.</b> General purpose inputs if V.24 interface is selected.                                                                                                                                               |

| 32<br>33         | 29<br>30         | MO1<br>MO2        | O/OD<br>O/OD                               | Multifunctional Output 1-2. General purpose outputs if V.24 interface is selected.                                                                                                                                                    |

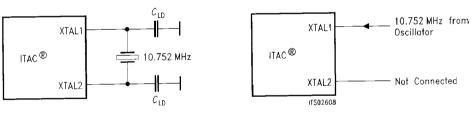

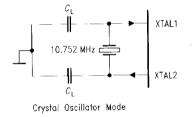

| 31               | 28 XTAL1 I       |                   | I                                          | <b>Crystal 1.</b> Connection for the external crystal or input for external clock generator.                                                                                                                                          |

# **Features**

# Pin Definitions and Functions (cont'd)

| Pin No.<br>P-LCC | Pin No.<br>P-DIP | Symbol   | Input (I)<br>Output (O)<br>Open Drain (OD) | Function                         |                                                                                                      |

|------------------|------------------|----------|--------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------|

| 30               | 27               | 27 X     | XTAL2                                      | 0                                | Crystal 2. Connection for the external crystal. Not connected when external clock generator is used. |

| 44               | 40               | $V_{DD}$ | I                                          | Power supply (+5 V <u>+</u> 5 %) |                                                                                                      |

| 22               | 20               | Vss      | I                                          | Power supply ground (GND)        |                                                                                                      |

# 1.2 Functional Description

# 1.2.1 General Functions and Device Architecture

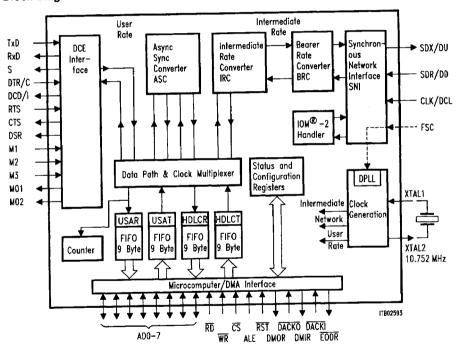

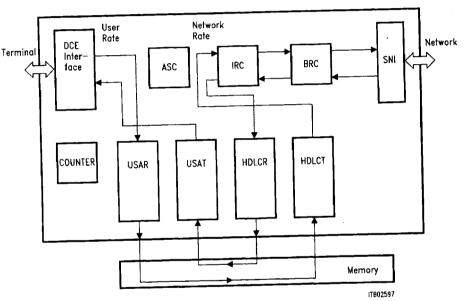

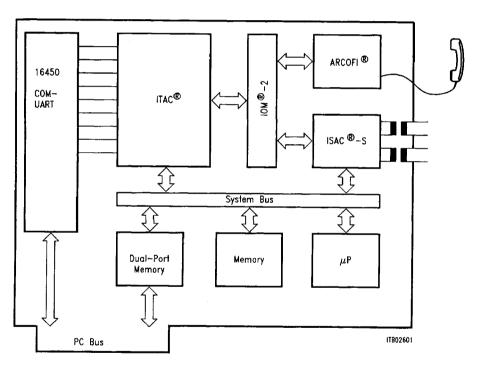

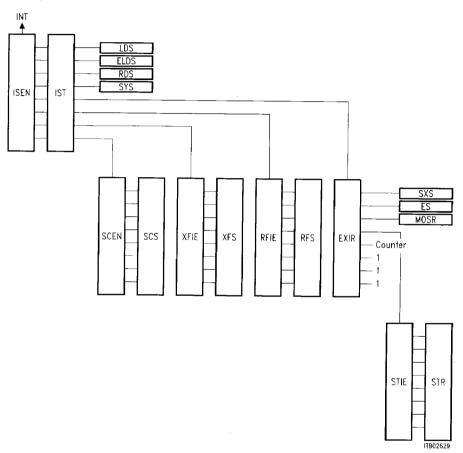

Figure 1 shows the block diagram of the ITAC.

Figure 1 Block Diagram

#### **Features**

#### Interfaces

The ITAC has three interfaces. The DCE interface provides all necessary data, interchange and clock signals to form a V.- or X.-series interface. The Synchronous Network Interface is a PCM compatible interface which consists of four lines. It can be configured as IOM-2 compatible and offers additionally communication paths via the MONITOR channel. The microprocessor interface is compatible to multiplexed bus systems like Siemens/Intel CPUs. Control lines may be used to synchronize the data transfer between the serial controllers and the memory via DMA.

#### **Bit Rate Adaptation**

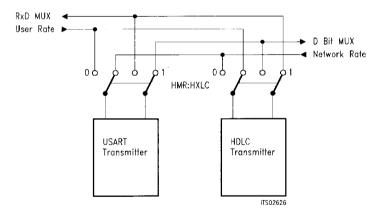

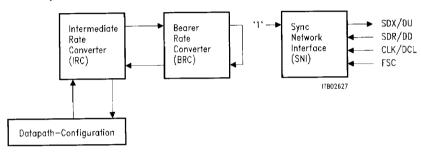

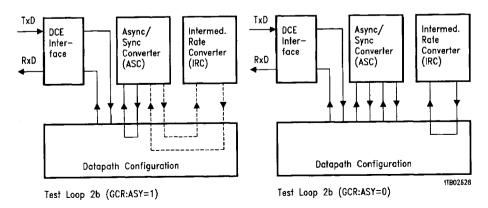

Three blocks of the ITAC perform the bit rate adaptation according to the V.110, X.30 or ECMA.102 specification. The first block is the Async/Sync Converter (ASC). It corresponds to the RA0 block and converts an asynchronous data stream received at the user rate into a synchronous data stream at the network rate. It handles overspeed and underspeed conditions and provides support for flow control. The Intermediate Rate Converter (IRC) corresponds to the RA1 block and converts the synchronous data stream into the V.110 frame. The IRC outputs the V.110 frame at the intermediate rate. The Bearer Rate Converter (BRC) corresponds to the RA2 block and converts the data between the IRC and the Synchronous Network Interface (SNI).

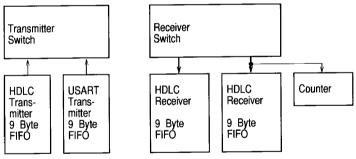

#### **Serial Communications Logic**

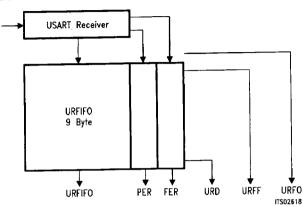

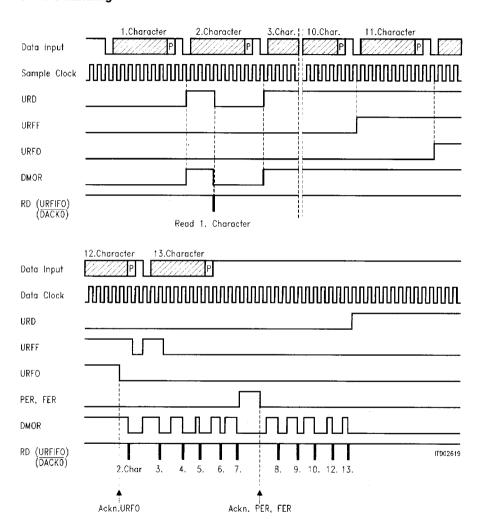

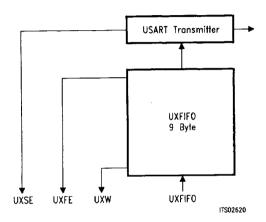

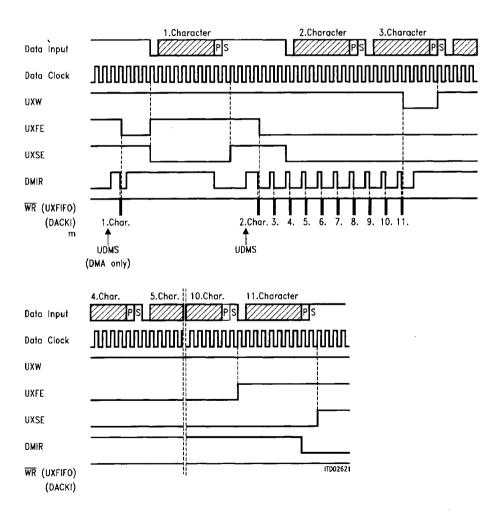

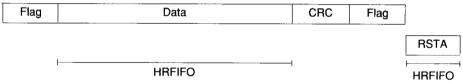

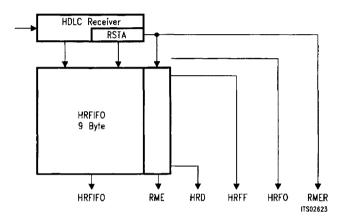

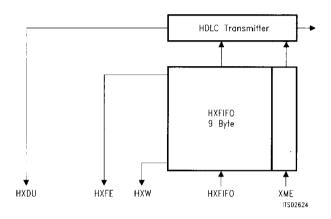

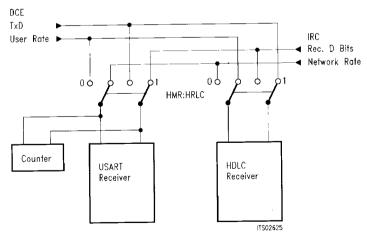

The serial communications logic consists of an USART transmitter, receiver and an HDLC transmitter and receiver plus a programmable counter. The data path for the receivers and transmitters are selected independently. They connect to the DCE interface or the IRC. Each receiver/transmitter has a 9 byte FIFO which reduces the response time of the microcontroller. The data transfer between the FIFOs and memory is performed by the microprocessor or by a DMA controller. The USART is used for in-band signaling (X.21, V.25, Hayes), speed conversion and flag-stuffing adaptation protocols (V.120, DMI). The HDLC controller is also used for flag-stuffing protocols and for general HDLC transfer over the B channels.

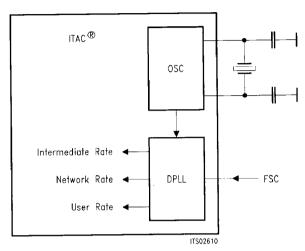

#### **Clock Generation**

All internal clock signals are derived from a DPLL inside the ITAC. The clock source for the DPLL is the internal oscillator which requires a 10.752-MHz crystal. The DPLL generates the intermediate rate, the network rate and the user rate. The network rate specifies the speed at which the IRC operates while the user rate determines the speed at the DCE interface.

#### IOM®-2 Handler

The IOM-2 mode, the ITAC supports access to both B channels or the intercommunication channels (IC) for transfering user data. Additionally it can control the MONITOR channel and two C/l bits of the second IOM channel.

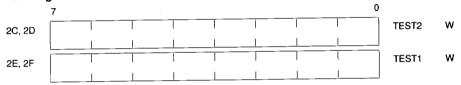

#### **Test Loops**

The ITAC provides three test loops. Two loop back the data of the IRC at the network side. The third test loop loops the data of the IRC or ASC at the terminal (DCE) side.

# 1.3 Operating Modes

The ITAC distinguishes between two basic operating modes. In transparent mode the V.110 framing is done autonomously. Therefore the user rate and the network rate have to be the same. In non-transparent modes the elements of the Serial Communications Logic (USART, HDLC controller) are switched into the data path. The user rate and the network rate may be different.

# 1.3.1 Transparent Mode

In the transparent mode, the ASC (in case of an asynchronous DCE interface), the IRC and the BRC operate autonomously. The microprocessor supervises the status of the IRC and will react only in case of synchronization loss or a disconnect request. To support inband signaling like the Hayes modem protocol, the USART receiver may be used to monitor the terminal data while the counter is used to supervise the guard time.

The transparent mode is selected by setting the network rate equal to the user rate.

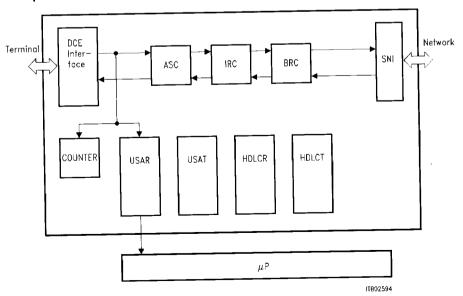

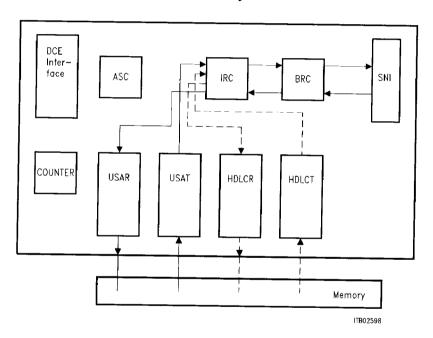

Figure 2 shows the data path for the transparent mode.

Figure 2

Transparent Mode. User Rate = Network Rate

### 1.3.2 Non - Transparent Modes

All non-transparent modes are characterized by the fact that the user rate and the network rate are not the same or the data source or destination is in memory and not the DCE interface.

Applications for non-transparent modes are:

- V.110 Adaptation of terminals with unequal speeds

- In-band signaling

- V.120 or DMI Terminal adapters

- Data transfer from or to the local memory

#### 1.3.2.1 Terminal Adapter for Unequal Speeds

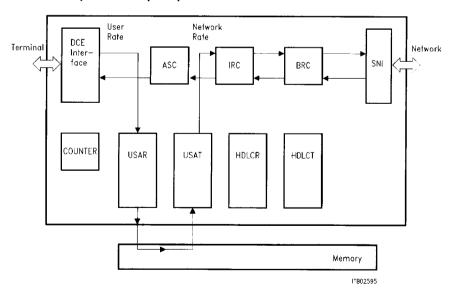

Figure 3 shows the data path for a terminal adapter which can handle unequal data rates.

Figure 3

Terminal Adapter for Unequal Speeds

#### **Features**

In this figure the user rate is higher than the network rate. In the data path from the lower to the higher data rate, the ASC will add stop bits between the characters to fill the gaps. In the opposite data path, the USART receiver and transmitter are used to convert the data rates. Data from the DCE interface is received by the USART receiver and transferred to memory. The data from memory is than written to the USART transmitter and sent to the IRC at the lower data rate.

Flow control between both ends is performed by interchange circuits or by using flow control characters. To detect these flow control characters (e.g. XON/XOFF) the ASC can compare each received character with two register values. If a match occurs, an interrupt is generated and the character may be deleted from the data stream.

#### 1.3.2.2 In-Band Signaling

Another non-transparent mode is the handling of in-band signaling information (e.g. X.21, Hayes modem protocol). The USART receiver and transmitter are used during local mode to transfer signaling information between the terminal and the terminal adapter.

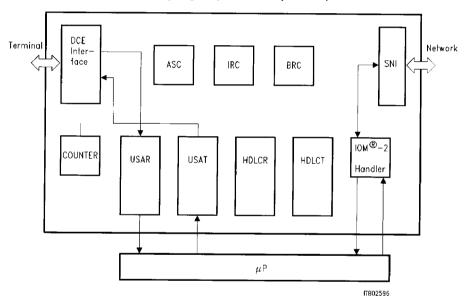

Figure 4 shows the data path for in-band signaling.

Figure 4

Data Path for In-Band Signaling (e.g. Hayes modem protocol)

All data from the terminal is received by the USART receiver and transfered to the microprocessor. The microprocessor interprets the data and transmits responses to the terminal using the USART transmitter. If the microprocessor which operates with the ITAC is different from the one which performs the LAPD signaling protocol, the MONITOR channel 1 of the IOM-2 interface can be used for intercommunication.

# 1.3.2.3 Terminal Adapter for V.120 or DMI

A terminal adapter for V.120 or DMI will also use the non-transparent mode. Figure 5 shows the data path.

Figure 5 Terminal Adapter for V.120 or DMI

All data from the terminal is received by the USART receiver and transfered to memory. The microprocessor adds the V.120 control elements and writes the data to the HDLC transmitter. The HDLC transmitter formats the HDLC frame and sends it to the IRC. In receive direction, the HDLC receiver receives a frame and transfers the data to memory. The microprocessor extracts the user data and writes it to the USART transmitter FIFO. The USART transmitter sends the characters to the terminal. Depending on the selected network rate, 7 bits (restricted 56 kbit/s) or 8 bits (64 kbit/s) of the B channel are used to transfer the HDLC information.

# 1.3.2.4 Data Transfer from or to the Local Memory

If the data which has to be transferred over the network doesn't originate from the DCE interface but from local memory, another non-transparent mode is used. **Figure 6** shows the data path.

Figure 6

Data Transfer from or to the Local Memory

The data from memory is written to the USART transmitter which sends it to the IRC. The IRC adapts the data and outputs it to the SNI. The data from the network is received by the IRC. The user data is forwarded to the USART receiver and transfered to memory. The same data path may be selected for the HDLC blocks to transfer HDLC frames formatted in V.110 frames or transparent over the B channel.

### 1.4 System Integration

The ITAC may be used in a number of applications, where terminals with V- or X-series interfaces are connected to an ISDN.

These applications are:

- V- or X- series terminal adapters for basic access

- V- or X- series terminal adapter add-on modules to feature phones

- PC add-on cards as terminal adapters or basis for ISDN terminals

- V- or X- series terminal adapters in exchanges

- Modem pools

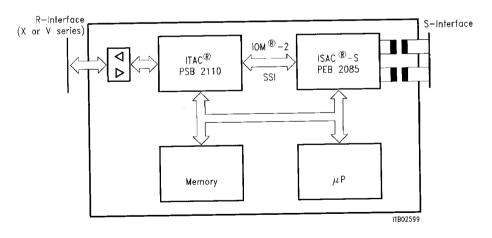

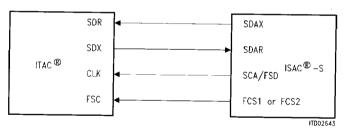

## 1.4.1 Terminal Adapter for ISDN Basic Access

A typical implementation of an ISDN basic access for a conventional X- or V- series terminal using the ITAC is shown in **figure 7**.

Figure 7

Terminal Adapter for ISDN Basic Access

#### **Features**

The ITAC can be connected via a serial synchronous interface (e.g. IOM-2, SSI) to an ISDN basic access transceiver/LAPD controller (in this case, the ISDN Subscriber Access Controller for the S interface, ISAC® -S). These two devices, together with a microcontroller, convert V- and X-series interface characteristics to the functional and procedural interface characteristics required by an ISDN at reference point S.

In this configuration, the ITAC will do the rate adaptation according to V.110, X.30 or ECMA.102 autonomously. The ITAC together with the microcontroller is used to receive and transmit signaling information between the terminal and the terminal adapter. The microcontroller together with the ISAC-S will convert the signaling data and transfer them using LAPD on S-interface. In V.120 and DMI terminal adapters the ITAC together with the microprocessor will perform the rate adaptation.

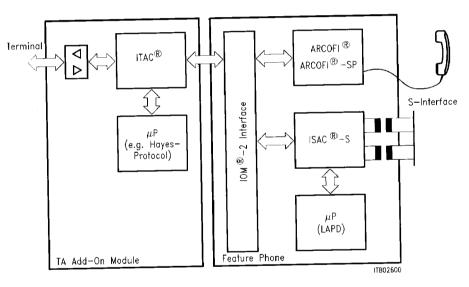

# 1.4.2 Terminal Adapter Add-On Modules for Feature Phones

A modular design of a feature phone may contain of a basic voice board with a microcontroller and an S-interface circuitry. Via the IOM-2 interface additional modules like encryption modules, card readers or terminal adapter modules may be added. Such a configuration is shown in **figure 8**.

Figure 8

Feature Phone Plus Terminal Adapter Add-On Module Based on IOM<sup>®</sup>-2

The microcontroller on the feature phone performs the telephone functions plus the processing of signaling information according to the LAPD protocol. The microcontroller on the TA add-on module performs the DTE signaling protocol (V.25 bis, Hayes) and controls the ITAC. Data between both microcontrollers is exchanged via the MONITOR channel 1. This data includes telephone numbers, call status information as well as B-channel assignment.

#### 1.4.3 PC Add-On Cards

Add-on cards for IBM PCs or compatibles based on the ITAC are not just simple terminal adapters but turn the PC into an ISDN terminal. A standard design is shown in **figure 9**.

Figure 9

Add-On Cards for PCs

Universal programs use the COM-Port to transfer data. The ITAC operates just like a terminal adapter. For card-specific application programs the Dual-Port Memory is used to transfer data between the PC Bus and the ISDN card. The ISDN card will transfer this data using the build-in communications controllers of the ITAC. A card like this is able to adapt the COM-Port according to the standards V.110, V.120 or DMI mode II. Additionally it can be used to access X.25 packet data services and it can transfer group IV facsimile data.

#### 1.4.4 Modem Pools

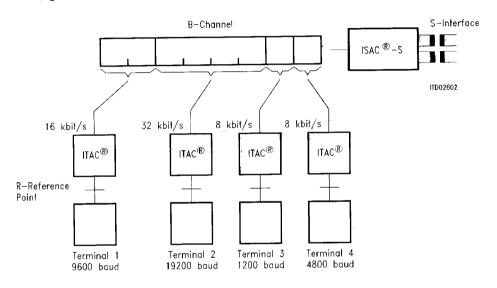

The ITAC supports V.110 subchannel multiplexing. This means that the 64 kbit/s bearer channel is shared by up to eight independent terminals. This is illustrated in **figure 10**.

Figure 10

Sharing of Bearer Channel Among Serveral Independent DTEs

# 1.4.5 Other Applications

The synchronous network interface of the ITAC is compatible to most PCM systems using programmable time slots. Consequently, the circuit in association with all IOM-2 compatible circuits, is ideally suited for applications on PABX line cards and concentrators/multiplexers.

Other applications of the ITAC include: host computer multiple line communication couplers, primary access/DMI peripheral boards, and Interworking Units (IWUs) between ISDN and analog PSTN.

#### 2 Operational Description

#### 2.1 Microprocessor/DMA Interface

#### Microprocessor Interface

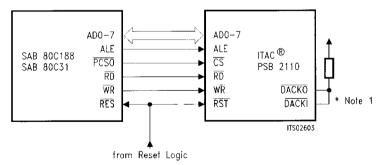

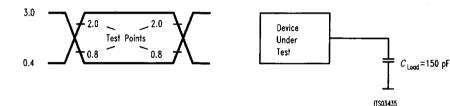

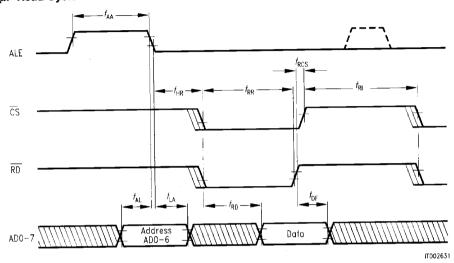

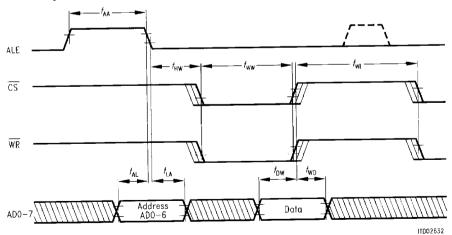

The microprocessor interface of the ITAC is designed for multiplexed address/data bus systems. The contents of the address/data lines is latched on the falling edge of ALE to form the register address. After chip select (CS) becomes active, the read or write control line specifies the register access. If read becomes active, the contents of the selected register is output on the address/data lines. If write becomes active, the contents of the address/data lines is latched into the selected register.

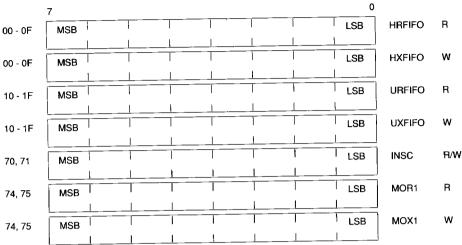

The address decoder uses address lines AD1 to AD6. Address line AD0 is not evaluated to allow a direct interface to 16-bit microprocessors like the SAB 80C186. The SAB 80C186 accesses the ITAC registers via even addresses. Address line AD7 is also not evaluated so that the occupied address space ranges from 00H to 7FH and another device may use the address space from 80H to FFH.

The DMA acknowledge inputs have to be connected to  $V_{DD}$  if they are not used.

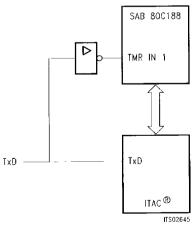

**Figure 11** shows the connection of an ITAC to a SAB 80C188/80C31 microprocessor without DMA support.

Figure 11

Connecting the ITAC® to SAB 80C188/80C31

\* Note 1: if DMA acknowledge inputs not used

#### **DMA** Interface

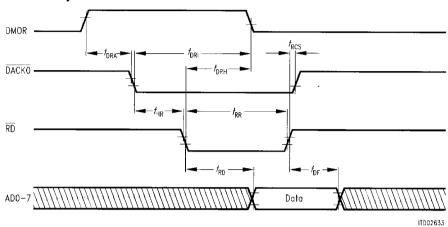

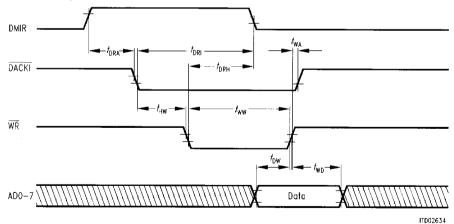

The ITAC supports data transfer between the FIFOs and memory via DMA (Direct Memory Access). If the ITAC requires a data transfer, it will indicate this to the DMA controller via a DMA request signal (DMIR, DMOR). The DMA controller will than signal to the CPU that it requires the control over the address and data bus. After the CPU responded by issuing an acknowledge signal, the DMA controller starts to transfer data.

DMA requests generated by the ITAC are acknowledged by the proper read or write operation to the FIFO. The read or write operation can be performed in two ways.

The first way is to perform a standard CPU cycle on one of the FIFO addresses. In this case, both DMA acknowledge inputs have to be connected to  $V_{\rm DD}$ .

The second way uses the DMA acknowledge inputs to select the FIFO address instead of a CS-signal. The RD or WR control signal together with the proper DMA acknowledge input selects the data bus operation. This allows single cycle I/O to memory transfers.

Both possible acknowledgements are shown in table 1.

Table 1 DMA Acknowledgements

| Request | Acknowledgement                    | Operation                             |

|---------|------------------------------------|---------------------------------------|

| DMIR    | DACKI ● WR                         | DMA transfer from memory to ITAC FIFO |

|         | or<br>CS (FIFO) ● WR               |                                       |

| DMOR    | DACKO ● RD<br>or<br>CS (FIFO) ● RD | DMA transfer from ITAC FIFO to memory |

The EODR output indicates that the last byte of a frame has been transferred by the DMA controller. It reflects the inverted status of the RME bit if the DMA interface is connected to the HDLC controller.

The generation of DMOR requests is blocked until the RME status bit has been acknowledged regardless whether the RME interrupt enable bit is set or cleared.

### **Operational Description**

#### 2.2 DCE Interface

The DCE interface consists of 13 lines in total. The number of available signals and their meaning depends on the selected clock mode (synchron or asynchron) and on the selected interchange configuration. The DCE interface may either operate synchron or asynchron. The selection is done by the 'ASY' bit in the General Configuration Register (GCR).

#### 2.2.1 Operating Modes

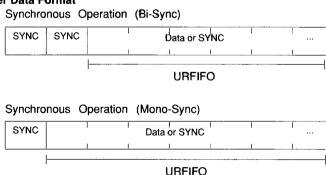

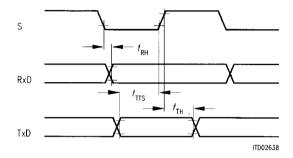

#### Synchronous Operation (GCR:ASY = 0)

During the synchronous operation, the clock signal which synchronizes the data transfer is outputed on the S-line. The data rate is equal to the selected user rate (BRS:UR0-3). The data on RxD is clocked off on the falling edges of the S-clock while data on TxD is latched on the rising edge of S. The ASC is inactive.

#### Asynchronous Operation (GCR:ASY = 1)

No clock signal is available on the S-line during asynchronous operation. In receive direction, the internal clock (16 \* user rate) is synchronized on every falling edge of a start bit or every falling edge of the received data stream (bit transparent mode). The TxD is sampled in the middle of each bit (after 8 internal clocks). Data on RxD is transmitted with no synchronization to the received data stream. The ASC is active.

#### 2.2.2 Interchange Circuits

The meaning of the interchange circuits and the corresponding status detection logic depends on the selected interface type. If the X.21 interface is selected, only C (Control) and I (Indicate) interchange lines are available. The status detection logic reports the recognized combination of local (TxD,C). If a non-X.21 interface (V-series interface) is selected, 10 interchange circuits are available. Their current status can be read from or written into registers, or controlled by the S-bits of the V.110 frame.

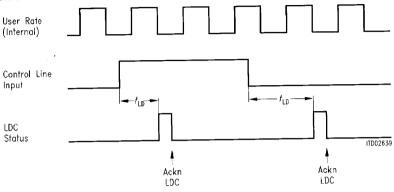

#### X.21 Interchange Circuits (GCR:V24 = 0)

The status detect logic samples the received data on TxD and the status of the control line (C). It reports the current status combination via the LDS (Local DTE Status) and the ELDS (Extended Local DTE Status) registers. A change in the LDS register is indicated by the LDC bit in the IST (Interrupt Status) register. A change in the ELDS register is indicated by the ELDC bit in the IST register. Both bits may generate an interrupt if their corresponding bit in the ISEN (Interrupt Status Enable) register is set to one.

The status detection logic is in no-state after reset. 'No state' is indicated by a value of zero in both status registers (LDS, ELDS). The status detection logic starts to sample the TxD and C line on every rising edge of the S-clock signal. The sampled values are compared against the different possibilities after 16 samples were taken. If a match is detected, the LDS and ELDS register change to the new value and set the corresponding LDC or ELDC bit to '1'. This may generate an interrupt. If a status is detected, which is different from LONX or LOFX, the status detection logic will sample four bits before the pattern is varified. If the status is no longer true, the LDS and ELDS registers change to 'no-state' (00) and the corresponding LDC or ELDC bit will be set. The next status will be indicated after another 16 bits have been sampled.

If LONX or LOFX or no valid status is detected after 16 samples, the status detection logic will check its last 16 samples after every clock cycle.

The valid status are shown in table 2.

# **Operational Description**

Table 2

DTE Status Logic Indications

| Status | Status Name       | Sampled Data                                 | Register Bit |

|--------|-------------------|----------------------------------------------|--------------|

| LON0   | Local (0, ON)     | TxD 00000000 00000000 C 00000000 000000000   | LDS : Bit 7  |

| LOF01  | Local (0101, OFF) | TxD 01010101 01010101<br>C 11111111 11111111 | LDS : Bit 6  |

| LL3    | Local Loop 3      | TxD 00001111 00001111 C 000000000            | LDS : Bit 5  |

| LONX   | Local (X, ON)     | TxD xxxxxxxx xxxxxxxx C 000000000 000000000  | ELDS : Bit 7 |

| LOFX   | Local (X, OFF)    | TxD xxxxxxxx xxxxxxx C 111111111             | ELDS : Bit 6 |

| LON1   | Local (1, ON)     | TxD 11111111 11111111 C 000000000            | ELDS : Bit 5 |

| LOF1   | Local (1, OFF)    | TxD 11111111 11111111 C 111111111            | ELDS : Bit 4 |

| LOF0   | Local (0, OFF)    | TxD 00000000 00000000 C 111111111111111111   | ELDS : Bit 3 |

| LL2    | Local Loop2       | TxD 00110011 00110011<br>C 11111111 1111111  | ELDS : Bit 2 |

Note: X = 0 or 1

The value of the I interchange circuit depends on the setting of the RCS bit in the DPCR register. If the RCS bit is '0', the value of the I interchange circuit is controlled by the DCD/ I-bit in the LDR register. If the RCS bit is '1', the value of the interchange circuit is controlled by the received S(SA)-bits.

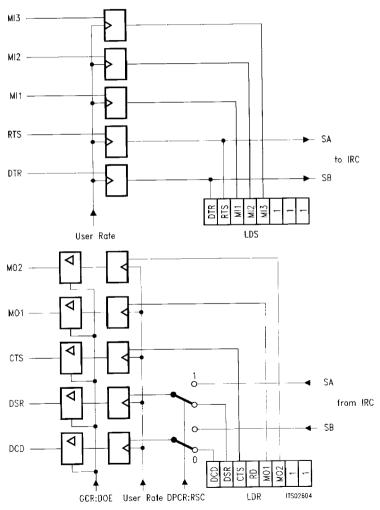

# V-Series Interchange Circuits (GCR:V24 = 1)

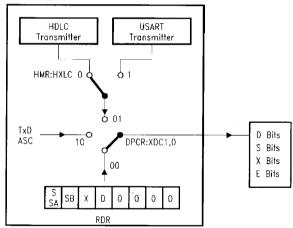

The configuration of the DCE interchange circuit in V.24 mode are shown in figure 12.

Figure 12 DCE Interchange Circuits (GCR:V24 = 1)

### **Operational Description**

The level of the CTS, MO1 and MO2 output is always controlled by the corresponding bits in the LDR register. The level of the DCD and DSR output may be controlled by the corresponding bits of the LDR register. This is selected if the RCS bit in the DPCR register is set to 0. The level of the DCD output is controlled by the received SA bits and the level of the DSR output is controlled by the received SB bit if the RCS bit is set to 1.

The input levels are sampled with the user rate period. The sampled value can always be read from the LDS register and may be forwarded to the S-bits. A change on at least one of the control lines will generate an LDC interrupt. This interrupt is delayed by half a user rate period.

### 2.2.3 DCE Output and Input Characteristics

## **Output Drivers**

All output drivers of the DCE interface are tri-state drivers. The enable function of the drivers is controlled by the DOE bit in the GCR register. If GCR:DOE (DCE Output Enable) = 0, all output lines are tri-state. If GCR:DOE = 1 all output drivers are active. If it is required to set all output lines to a defined state while DOE = 0, external pull-up resistors must be connected to all output pins.

#### **Connection of Open Inputs**

All available input pins of the DCE interface must be set to a defined state in order to avoid interrupts. Unused inputs may be connected to an external pull-up resistor or to GND.

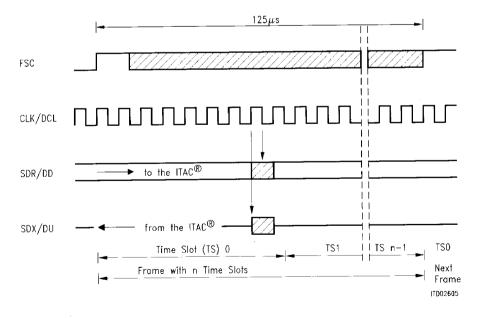

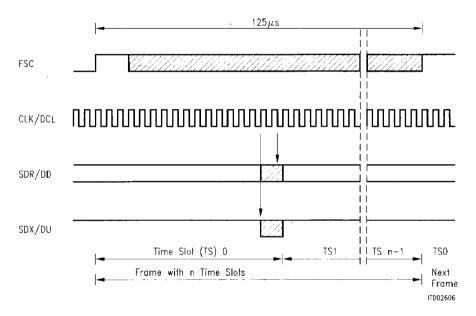

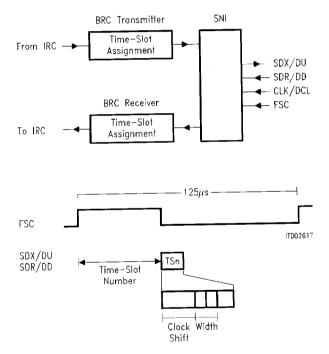

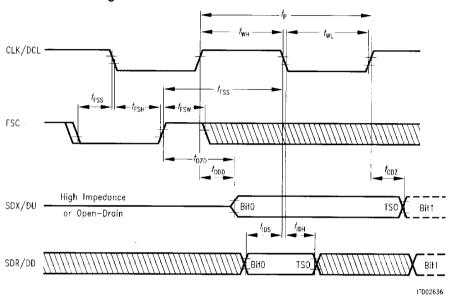

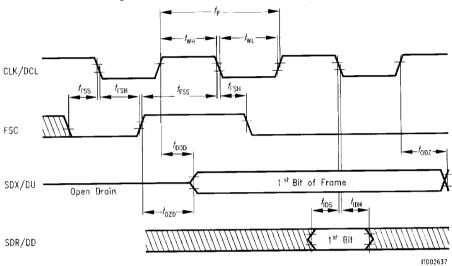

### 2.3 Synchronous Network Interface

The Synchronous Network Interface (SNI) consists of four lines. Two lines transfer the data signals, one line receives the bit clock signal while the last line receives the frame start signal. The SDX/DU line is used to transmit data to the network side, while SDR/DD line is used to receive data from the network. The bit clock signal (one clock cycle per bit) or the data clock signal (two clock cycles per bit) is connected to the CLK/DCL input. The frame start signal (8 kHz) is connected to the FSC input.

#### 2.3.1 Operating Modes

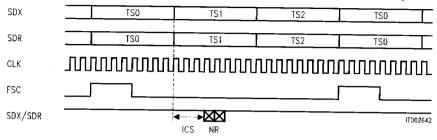

#### PCM Interface (single bit clock)

Single bit clock operation is selected, if SCR:DCL = 0. This means that there is one clock cycle per data bit. The transmitted data is clocked off the SDX/DU line by the rising edge of the CLK signal while the received data on the SDR/DD line is latched with the falling edge of the CLK signal.

Figure 13 PCM Interface (single bit clock)

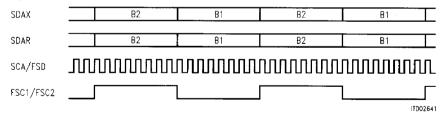

### IOM®-2 Interface

Double bit clock operation is selected, if SCR:DCL = 1. This means that there are two clock cycles per data bit. The transmitted data is clocked off the SDX/DU line by the first rising edge of the CLK/DCL signal while the received data on the SDR/DD line is latched at the falling edge of the second cycle of the CLK/DCL signal.

Figure 14

IOM®-2 Interface (double bit clock)

#### **SNI Clock Characteristics**

In both cases the FSC signal has to fulfill a short setup and hold time. The signal on CLK/DCL may not be symetrical. The data rate on the SNI has to be more or equal to twice the maximum intermediate rate. To transfer 64, 56, 48 or 38.4 kbit/s the minimum data rate on the SNI is 128 kbit/s.

#### **SNI Output Driver Characteristics**

The output driver of the SDX/DU line can be programmed to a push-pull output (SCR:OD = 0) or to an open-drain output (SCR:OD = 1). The output driver is only active during the transmission of the selected bits on the time-slot and tri-state during the other bits of the frame.

If the output driver is set to open-drain output, an external pull-up resistor is required. The value of the resistor depends on the length of the line and the number of connected devices. The minimum value for the resistor is 720  $\Omega$ .

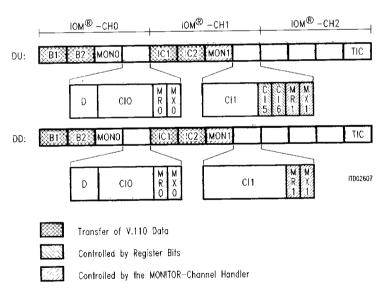

# 2.3.2 IOM®-2 Interface Support

The ITAC offers additional support for the IOM-2 interface mode. This include the protocol support for the MONITOR channel 1 and the control of the CI5 and CI6 bits in the upstream CI1-channel. It is enabled by setting the MOCR:IOM2 bit to '1'.

Figure 15

IOM®-2 Interface Support

### **Operational Description**

#### Selection of the V.110/X.30 Data Stream

The V.110/X.30 formated data can be transferred over all time slots of the IOM-2 interface by programming the TSR register. But only four settings are recommended. They are listed in **table 3** and show the programming for B1, B2 and IC1, IC2.

Table 3

Selection of Time -Slots in IOM®-2 Mode

| IOM Channel | TSR Value |  |

|-------------|-----------|--|

| B1          | 00000XXX  |  |

| B2          | 00001XXX  |  |

| IC1         | 00100XXX  |  |

| IC2         | 00101XXX  |  |

### **MONITOR Channel Support**

The IOM-2 handler of the ITAC includes a MONITOR channel handler for the MONITOR channel 1. The access is hardwired to time slot 7 for the MONITOR data byte and time slot 8 for evaluation of the MR, MX bits.

The MONITOR channel handler performs the MONITOR channel protocol. It provides a receive and transmit register for the MONITOR channel data byte plus control and status bits. Since the ITAC requires a microprocessor interface for operation, there is no automatic comparison of the MONITOR channel address byte. The begin of all MONITOR channel messages is received and the microcontroller accepts a message by setting the MRC control bit to '1'.

More information about the MONITOR channel protocol is available in the IOM-2 reference guide. (Order-No: B115-H6397-X-X-7600)

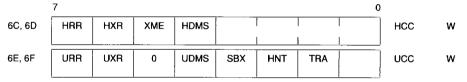

#### Control of the MONITOR Channel Handler

The MONITOR channel handler is controlled by four bits of the MONITOR Channel Control Register (MOCR). They are listed in **table 4**.

Table 4

MONITOR Channel Control Bits

| Bit Name | Bit No. | Function                                                                                                                                                                                                                                                                             |  |  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MXC      | 0       | MONITOR Channel Transmit Control Controls the operation of the transmitter. If set to '0', the MX stays '1' and MOX1 transmits 'FF' (idle). If set to '1', data writinto the MOX1 register will be transfered according to MONITOR channel protocol.                                 |  |  |

| MIE      | 1       | MONITOR Channel Interrupt Enable When set to '1', the status bits MDA, MER and MAB may generate an interrupt. Otherwise, the interrupts are masked.                                                                                                                                  |  |  |

| MRC      | 2       | MONITOR Channel Receive Control Controls the operation of the receiver. When set to '0', MDR status changes are blocked except for the first byte of a message. When set to '1', received bytes will be acknowledged automatically after they have been read from the MOR1 register. |  |  |

| MRE      | 3       | MONITOR Channel Receive Enable When set to '0', the generation of MDR status changes is disabled including the first byte of a message. When set to '1', the MDR status is set for each MONITOR address byte (if MCR = 0) or for each received byte (MRC = 1).                       |  |  |

# **Operational Description**

#### Indications of the MONITOR Channel Handler

Changes in the MONITOR channel handler are indicated by four status bits in the MONITOR Channel Status Register (MOSR). There meaning is shown in table 5.

Table 5

MONITOR Channel Indications

| Bit Name | Bit No. | Meaning                                                                                                                                                                                                                 |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAB      | 0       | MONITOR Channel Abort If set to '1', the opposite receiver has aborted the transmission.                                                                                                                                |

| MDA      | 1       | MONITOR Channel Data Acknowledge If set to '1', the opposite receiver has acknowledge the data transfer. A new byte may be entered into the MOX1 register or the MXC-bit may be cleared to indicate the end of message. |

| MER      | 2       | MONITOR Channel End of Receiption If set to '1', the local receiver has detected an end of message condition. The MCR-bit may be cleared to indicate the end of transmission.                                           |

| MDR      | 3       | MONITOR Channel Data Received  If set to '1', the local receiver has received a new byte. It can be read from the MOR1 register, which will automatically generate the acknowledgement if MCR = 1.                      |

#### **CI-Channel Control**

The IOM-2 handler of the ITAC allows the control of bit 5 and 6 in the upstream direction of Command/Indicate (CI)- Channel 1. The inverted value is written into the CIX5 and CIX6 bits of the MOCR register.

#### Software Awake

In order to activate a deactivated IOM-2 interface, the SDX/DU pin can be controlled via the SAW-bit. If set to '1', the SDX/DU output is forced to '0' while the following condition is true: FSC\*IOM2\*SAW=1. Since the FSC signal is high during the first IOM-2 channel and low during the remaining period, MONITOR channel 1 is available to indicate the active condition of the IOM-2 interface and to indicate that the SAW-bit can be reset.

#### 2.4 Clock Generation

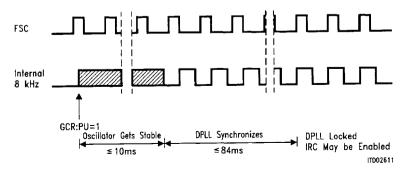

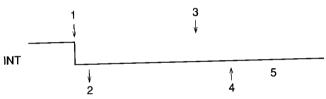

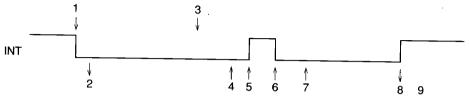

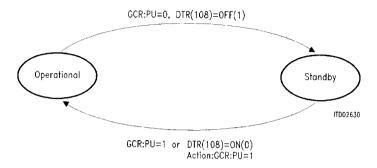

The ITAC derives all its clock signal from the on-chip oscillator which requires a 10.752-MHz crystal. The oscillator is controlled by the power-up bit (PU) in the GCR register and in case of an asynchronous interface also from the DTR input.

#### Oscillator

If a synchronous interface is selected (GCR:ASY=0), the oscillator stops if GCR:PU = 0 and starts if GCR:PU = 1.

If an asynchronous interface is selected (GCR:ASY=1), the oscillator stops if GCR:PU = 0 and the level on the DTR input is high (OFF). It is started when either GCR:PU is set to '1' or the level on DTR changes to low (ON). This will automatically set the GCR:PU bit to '1'.

The oscillator needs a maximum period of 10 ms to generate a stable clock signal.

The external crystal is connected between the XTAL1 and XTAL2 pin. XTAL1 is the oscillator input and XTAL2 its output. If an external clock source is used to generate the 10.752-MHz clock, its signal is connected to XTAL1.

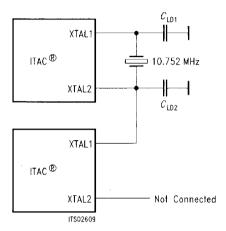

Figure 16 Connection of Clock Sources

Note: Value of CLD is determined by the XTAL-specification.

Two or more ITAC on the same board may share one crystal. This crystal is connected to XTAL1 and XTAL2 of one ITAC. The XTAL1 input of the other ITACs are connected to the XTAL2 output of the crystal. The XTAL2 output of the other ITACs are left open.

The load capacity of both crystal pins should be same. On XTAL1, there is just the input capacity of one ITAC. On XTAL2, there is the sum of one output capacity plus the input capacity of the other ITACs and the capacities of the line. To calculate the resulting capacities, each input capacity has a maximum value of 7 pF.

Please note that the power up bit (GCR:PU) of the ITAC to which the crystal is connected has to be '1' in order to provide a clock signal on XTAL2.

Figure 17

Driving Two ITAC® Oscillators by One Crystal

### Operation of the DPLL

The DPLL generates four clock signals which are synchronized to the 8-kHz clock on the FSC input. The four clock signals are the user rate, which specifies the speed of the DCE interface and the DCE side of the ASC, the network rate, which specifies the speed of the IRC and the IRC side of the ASC, the intermediate rate, which specifies the speed between the IRC and the BRC and the 8-kHz reference signal for the DPLL.

Figure 18 Clock Synchronization

The DPLL evaluates the phase difference between the internal 8-kHz signal and the input signal on the FSC pin and adjusts its clock by one oscillator step (93 ns) every 125 microseconds. The maximum phase difference is one half of the 8-kHz signal which is 62.5 microseconds. If the DPLL starts to adjust in this situation it takes 62.5 us/93 ns = 672 steps which needs 84 ms.

The adjustment of 1 oscillator period per 125 microseconds guarantees a maximum jitter of less than 1 % for synchronous data transmission at 64 kbit/s.

Figure 19 Synchronization of the DPLL

### **Operational Description**

#### Selection of the User Rate, Network Rate and Intermediate Rate

The user rate and the network rate are programmed in the BRS register. The intermediate rate is automatically selected by the value of the network rate.

Table 6 shows the possible settings for the network rate.

Table 6

Network Rates

| NR3 | NR2 | NR1 | NR0 | Network<br>Rate | Intermediate<br>Rate | Number of Bits per time-slot | Remarks                                          |

|-----|-----|-----|-----|-----------------|----------------------|------------------------------|--------------------------------------------------|

| 0   | 0   | 0   | 0   | _               | _                    | _                            | reserved                                         |

| 0   | 0   | 0   | 1   | 600 bit/s       | 8 kbit/s             | 1                            | 4x80 bit framing                                 |

| 0   | 0   | 1   | 0   | 1200 bit/s      | 8 kbit/s             | 1                            | 2x80 bit framing                                 |

| 0   | 0   | 1   | 1   | 2400 bit/s      | 8 kbit/s             | 1                            | 80 bit framing                                   |

| 0   | 1   | 0   | 0   | 4800 bit/s      | 8 kbit/s             | 1                            | 80 bit framing                                   |

| 0   | 1   | 0   | 1   | 9600 bit/s      | 16 kbit/s            | 2                            | 80 bit framing                                   |

| 0   | 1   | 1   | 0   | 19200 bit/s     | 32 kbit/s            | 4                            | 80 bit framing                                   |

| 0   | 1   | 1   | 1   | 38400 bit/s     | 64 kbit/s            | 8                            | 80 bit framing                                   |

| 1   | 0   | 0   | 0   | 48000 bit/s     | 64 kbit/s            | 8                            | 32 bit framing                                   |

| 1   | 0   | 0   | 1   | 56000 bit/s     | 56/64 kbit/s         | 7/8                          | 7 bit framing<br>8 bit framing<br>64 bit framing |

| 1   | 0   | 1   | 0   | 64000 bit/s     | 64 kbit/s            | 8                            | 8 bit transparent                                |

| 1   | 0   | 1   | 1   | _               | _                    | _                            | reserved                                         |

| 1   | 1   | x   | x   | _               | _                    | _                            | reserved                                         |

The selectable user rates depend on the selected DCE interface type. If an asynchronous interface (GCR:ASY = 1) is selected, the user rate can be set between 300 and 38400 baud. The user rate may range between 600 and 64000 bit/s if a synchronous interface is selected (GCR:ASY = 0).

Table 7 User Rates

| UR3 | UR2 | UR1 | UR0 | Sync. Data Rate | Async. Data Rate | Remarks  |

|-----|-----|-----|-----|-----------------|------------------|----------|

| 0   | 0   | 0   | 0   | _               | 300 bit/s        |          |

| 0   | 0   | 0   | 1   | 600 bit/s       | 600 bit/s        |          |

| 0   | 0   | 1   | 0   | 1200 bit/s      | 1200 bit/s       |          |

| 0   | 0   | 1   | 1   | 2400 bit/s      | 2400 bit/s       |          |

| 0   | 1   | 0   | 0   | 4800 bit/s      | 4800 bit/s       |          |

| 0   | 1   | 0   | 1   | 9600 bit/s      | 9600 bit/s       |          |

| 0   | 1   | 1   | 0   | 19200 bit/s     | 19200 bit/s      |          |

| 0   | 1   | 1   | 1   | 38400 bit/s     | 38400 bit/s      | }        |

| 1   | 0   | 0   | 0   | 48000 bit/s     | -                |          |

| 1   | 0   | 0   | 1   | 56000 bit/s     | _                |          |

| 1   | 0   | 1   | 0   | 64000 bit/s     | _                |          |

| 1   | 0   | 1   | 1   | _               | _                | reserved |

| 1   | 1   | x   | x   | _               | -                | reserved |

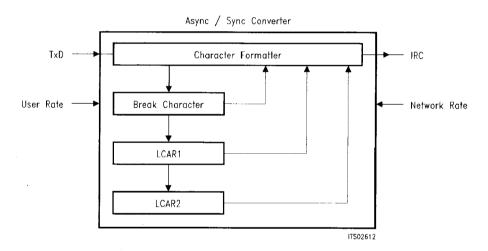

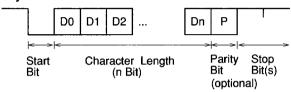

### 2.5 Async/Sync Converter (ASC)

The Async/Sync Converter transforms a stream of Start/Stop bit formatted characters at the user rate into a synchronous bit stream at the network rate and vice versa. It is active if the DCE interface is set to asynchronous operation (GCR:ASY = 1).

### Functions of the ASC in Transmit Direction (to the network)

The ASC block diagram of the transmitter is shown in figure 20.

Figure 20 ASC Transmitter

In transmit direction the ASC will frame the incoming characters (from the DCE interface) and transfer them to the IRC at the network rate. If the user rate is less than the network rate, the gaps between characters are padded by stop bits. The ASC will not operate properly if the user rate is higher than the network rate. If the actual data rate at the DCE interface is higher than the nominal user rate, stop bits will be deleted within the limits of the selected tolerance range. If AICR:TR = 0 the tolerance range is 12.5 %. This means that every eighth stop bit may be deleted. If AICR:TR = 1 the tolerance range is set to 25 %. This means that every fourth stop bit may be deleted. The ASC will also recognize a break signal. The break signal is detected when at least M bits of start polarity have been received. M denotes the number of bits per character in the selected format including start and stop bits. If the ASC detects a break condition from the DCE interface, it will transmit at least 2M+1 start bits towards the IRC.

# Functions of the ASC in Receive Direction (from the network)

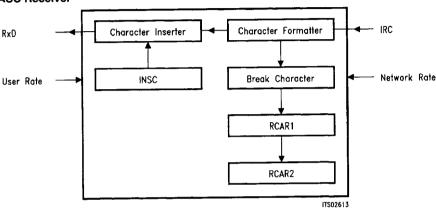

The ASC receiver is shown in figure 21.

Figure 21 ASC Receiver

In receive direction the ASC receives the synchronous bit stream at the network rate and transfers it into a character stream at the user rate which is transmitted to the DCE interface. If the network rate is less than the user rate, the gaps between characters are padded by stop bits. The receive direction will not operate properly if the network rate is higher than the user rate. If a missing stop element is detected in the data stream, the length of the stop bits transmitted to the DCE interface is reduced according to the selected tolerance range.

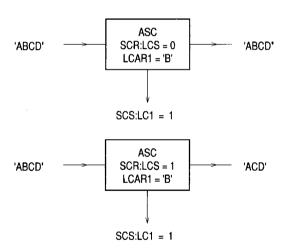

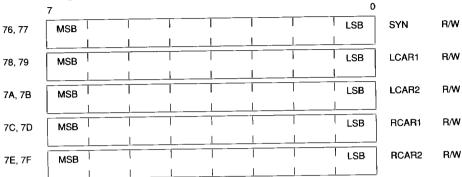

#### Recognition of Special Characters (flow control)

Two programmable characters can be specified for each direction. If a character is received from the DCE interface, which matches the value of LCAR1 or LCAR2 the corresponding status bit is set in the Special Condition Status register (SCS). If the Local Character Stop bit in the Special Configuration register (SCR:LCS) is set to '1', the received character bits are substituted by stop bits. Thus the character is deleted from the data stream. The same function is available for the received data from the network. The special character registers are RCAR1 and RCAR2. The Remote Character Stop bit (SCR:RCS) controls the substitution of the character bits.

Figure 22 Special Character Recognition

This feature may be used to detect and remove flow control characters (XON/XOFF) from the data stream.

#### Insertion of Characters

The Character Insert Register INSC allows to insert characters in the receive data stream (from the network). The character which has to be inserted is written into the INSC register and automatically inserted at the next opportunity. The status whether the character has been inserted or not is supervised by the CIS bit in the Status register STR.

This feature may be used to add flow control characters in the data stream towards the DCF interface.

The character written into the INSC register has to contain a possible parity bit and unused bits have to be filled with ones.

If the ASC receives data while a character has to be inserted, it will insert the character after the current character has been completed and it will reduce the length of the stop bits of the following characters. Thus the received characters are not pertubed.

Figure 23 Character Insertion Using INSC

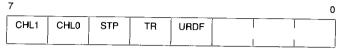

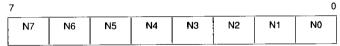

### Selecting the character format for the ASC

The character format of the ASC is programmed by the AICR and the UMR register.

If a parity bit is selected, the format of a character is incremented by one bit. The ASC will not check the parity on the received character.

Table 8

Character Format of the ASC

| 1   |       |                  |         |          |

|-----|-------|------------------|---------|----------|

| - 1 | Start | Character Length | Parity  | Stop     |

| ĺ   |       | J                |         |          |

| -   |       |                  |         |          |

|     |       | AICR:CHL1,0      | UMR:PTY | AICR:STP |

|           | AICR |                        |

|-----------|------|------------------------|

| CHL1 CHL1 |      | Character Length (Bit) |

| 0         | 0    | Eight                  |

| 0         | 1    | Seven                  |

| 1         | 0    | Six                    |

| 1         | 1    | Five                   |

|     | UMR | !   |            |  |

|-----|-----|-----|------------|--|

| PTY | PY1 | PY0 | Parity Bit |  |

| 0   | х   | Х   | no         |  |

| 1   | X   | Х   | yes        |  |

| AICR:STP | Number of Stop Bits |  |

|----------|---------------------|--|

| 0        | 1                   |  |

| 1        | 2                   |  |

### 2.6 Intermediate Rate Converter

The intermediate rate converter performs the framing according to V.110 or X.30. The source and destination of the D bits may be the DCE interface, the Serial Communications Logic or register bits. The source and destination of the S bits may be the DCE interface or register bits. The source and destination of the X and E bits are always register bits.

The operation of the IRC is controlled by the ENFR bit (GCR). Before the ENFR bit is set to '1', the network rate, the V.110/X.30 frame format and the time-slot has to be programmed. If one of the register values needs to be changed, the ENFR bit has to be cleared for one period of the previous intermediate rate.

#### Frame Structures

The frame structure depends on the selected network rate. For network rates from 600 to 38400 bit/s a 80-bit frame is used. For a network rate of 48000 bit/s a 32-bit frame is used. For a data rate of 56000 bit/s one of two frame alternatives may be selected. One uses a 8-bit frame while the second one uses a 64-bit frame. If the 8-bit frame is selected and the status of the IRC is masked, a transparent 56 kbit/s channel is available. No framing is performed if the network rate is 64000 bit/s.

Table 9 to 16 show the framing for the individual data rates.

Table 9 Frame Structure for 600 bit/s

Table 10 Frame Structure for 1200 bit/s

| I lame of dotain in the sea |    |     |      |       |          |    |    |     |                       |    |     |     |     |     |     |      |    |

|-----------------------------|----|-----|------|-------|----------|----|----|-----|-----------------------|----|-----|-----|-----|-----|-----|------|----|

| Octet                       | F  | ame | Stru | cture | <u> </u> |    |    |     | Octet Frame Structure |    |     |     |     |     |     |      |    |

| No.                         | 1  | 2   | 3    | 4     | 5        | 6  | 7  | 8   | No.                   | 1  | 2   | 3   | 4   | 5   | 6   | 7    | 8  |

|                             | 0  | 0   | 0    | 0     | 0        | 0  | 0  | 0   | 1                     | To | 0   | 0   | 0   | 0   | 0   | 0    | 0  |

| 1                           | 1  | D1  | D1   | D1    | Ď1       | D1 | D1 | S1  | 2                     | 1  | D1  | D1  | D1  | D1  | D2  | D2   | S1 |

| 2                           | 11 |     | D1   | D2    | D2       | D2 | D2 | X   | 3                     | 1  | D2  | D2  | D3  | D3  | D3  | D3   | Х  |

| 3                           |    | D1  |      | D2    | D2       | D3 | D3 | S3  | 4                     | 1  | D4  | D4  | D4  | D4  | D5  | D5   | S3 |

| 4                           | ון | D2  | D2   |       |          | D3 | D3 | S4  | 5                     | 1  | D5  | D5  | D6  | D6  | D6  | D6   | S4 |

| 5                           | 1  | D3  | D3   | D3    | D3       |    | E6 | E7* | 6                     | 14 | E1  | E2  | E3  | E4  | E5  | E6   | E7 |

| 6                           | 1  | E1  | E2   | E3    | E4       | E5 |    |     | 7                     | 1  | D7  | D7  | D7  | D7  | D8  | D8   | S6 |

| 7                           | 1  | D4  | D4   | D4    | D4       | D4 | D4 | S6  | ,                     | 1: | D8  | D8  | D9  | D9  | D9  | D9   | Х  |

| 8                           | 1  | D4  | D4   | D5    | D5       | D5 | D5 | X   | 8                     | 11 |     | D10 | D10 | D10 | D11 | D11  | SB |

| 9                           | 1  | D5  | D5   | D5    | D5       | D6 | D6 | S8  | 9                     | 11 | D10 |     | D10 |     | D12 | _ :: |    |

| 10                          | 1  | D6  | D6   | D6    | D6       | D6 | D6 | _S9 | 10                    | 1  | D11 | D11 | D12 | 012 | 012 |      |    |

<sup>\*</sup>E7 is controlled automatically and transmits 1011.

Table 11 Frame Structure for 2400 bit/s

| Table 12        |     |       |       |        |

|-----------------|-----|-------|-------|--------|

| Frame Structure | for | 4800, | 9600. | 19200. |

| 38400 bit/s     |     | ĺ     | ,     |        |

|                 |     |       |       |        |

|       |   |      |      |       |     |     |     |    |       |                 | -   |     |     |     |     |     |    |

|-------|---|------|------|-------|-----|-----|-----|----|-------|-----------------|-----|-----|-----|-----|-----|-----|----|

| Octet | F | rame | Stru | cture | •   |     |     |    | Octet | Frame Structure |     |     |     |     |     |     |    |

| No.   | 1 | 2    | 3    | 4     | 5   | 6   | 7   | 8  | No.   | 1               | 2   | 3   | 4   | 5   | 6   | 7   | 8  |

| 1     | 0 | 0    | 0    | 0     | 0   | 0   | 0   | 0  | 1     | 0               | 0   | 0   | 0   | 0.  | 0   | 0   | 0  |

| 2     | 1 | D1   | D1   | D2    | D2  | D3  | D3  | S1 | 2     | 1               | D1  | D2  | D3  | D4  | D5  | D6  | Š1 |

| 3     | 1 | D4   | D4   | D5    | D5  | D6  | D6  | Х  | 3     | 1               | D7  | D8  | D9  | D10 | D11 | D12 | x. |

| 4     | 1 | D7   | D7   | D8    | D8  | D9  | D9  | S3 | 4     | 1               | D13 | D14 | D15 | D16 | D17 | D18 | S3 |

| 5     | 1 | D10  | D10  | D11   | D11 | D12 | D12 | S4 | 5     | 1               | D19 | D20 | D21 | D22 | D23 | D24 |    |

| 6     | 1 | E1   | E2   | E3    | E4  | E5  | E6  | E7 | 6     | 1               | E1  | E2  | E3  | E4  | F5  | F6  | F7 |

| 7     | 1 | D13  | D13  | D14   | D14 | D15 | D15 | S6 | 7     | 11              | D25 | D26 | D27 | D28 | D29 | D30 | SA |

| 8     | 1 | D16  | D16  | D17   | D17 | D18 | D18 | Х  | 8     | 1               | D31 | D32 | D33 | D34 | D35 | D36 |    |

| 9     | 1 | D19  | D19  | D20   | D20 | D21 | D21 | S8 | 9     | 1               | D37 | D38 | D39 | D40 | D41 | D42 |    |

| 10    | 1 | D22  | D22  | D23   | D23 | D24 | D24 | S9 | 10    | 1               | D43 | D44 | D45 | D46 | D47 | D48 |    |

Table 13

Frame Structure for 56000 bit/s

Frame Alternative 1

| Octet | Frame Structure |     |     |     |     |     |     |   |  |  |  |  |

|-------|-----------------|-----|-----|-----|-----|-----|-----|---|--|--|--|--|

| No.   | 1               | 2   | 3   | 4   | 5   | 6   | 7   | 8 |  |  |  |  |

| 1     | D1              | D2  | D3  | D4  | D5  | D6  | D7  | 1 |  |  |  |  |

| 2     | D8              | D9  | D10 | D11 | D12 | D13 | D14 | 1 |  |  |  |  |

| 3     | D15             | D16 | D17 | D18 | D19 | D20 | D21 | 1 |  |  |  |  |

| 4     | D22             | D23 | D24 | D25 | D26 | D27 | D28 | 1 |  |  |  |  |

| 5     | D29             | D30 | D31 | D32 | D33 | D34 | D35 | 1 |  |  |  |  |

| 6     | D36             | D37 | D38 | D39 | D40 | D41 | D42 | 1 |  |  |  |  |

| 7     | D43             | D44 | D45 | D46 | D47 | D48 | D49 | 1 |  |  |  |  |

| 8     | D50             | D51 | D52 | D53 | D54 | D55 | D56 | 1 |  |  |  |  |

Table 14

Frame Structure for 56000 bit/s

Frame Alternative 2

| Oakat        | 1                         |     |     |     |     |     |     |    |  |

|--------------|---------------------------|-----|-----|-----|-----|-----|-----|----|--|

| Octet<br>No. | Frame Structure 1 2 3 4 5 |     |     |     |     |     | 7   | 8  |  |

| 1            | D1                        | D2  | D3  | D4  | D5  | D6  | D7  | 0  |  |

| 2            | D8                        | D9  | D10 | D11 | D12 | D13 | D14 | Х  |  |

| 3            | D15                       | D16 | D17 | D18 | D19 | D20 | D21 | S3 |  |

| 4            | D22                       | D23 | D24 | D25 | D26 | D27 | D28 | S4 |  |

| 5            | D29                       | D30 | D31 | D32 | D33 | D34 | D35 | 1  |  |

| 6            | D36                       | D37 | D38 | D39 | D40 | D41 | D42 | 1  |  |

| 7            | D43                       | D44 | D45 | D46 | D47 | D48 | D49 | 1  |  |

| 8            | D50                       | D51 | D52 | D53 | D54 | D55 | D56 | 1  |  |

Table 15 Frame Structure for 48000 bit/s

| Octet | F | rame | Stru | cture | •   |     |     |    |

|-------|---|------|------|-------|-----|-----|-----|----|

| No.   | 1 | 2    | 3    | 4     | 5   | 6   | 7   | 8  |

| 1     | 1 | D1   | D2   | D3    | D4  | D5  | D6  | S1 |

| 2     | 0 | D7   | D8   | D9    | D10 | D11 | D12 | Х  |

| 3     | 1 | D13  | D14  | D15   | D16 | D17 | D18 | S3 |

| 4     | 1 | D19  | D20  | D21   | D22 | D23 | D24 | S4 |

Table 16 Frame Structure for 64000 bit/s

| Octet        | Fra | me S | Struc | ture |    |    |    |    |

|--------------|-----|------|-------|------|----|----|----|----|

| Octet<br>No. | 1   | 2    | 3     | 4    | 5  | 6  | 7  | 8  |

| 1            | D1  | D2   | D3    | D4   | D5 | D6 | D7 | D8 |

# **Explanation of the Frame Elements**

All frames consist of five basic elements. The first element is the frame synchronization pattern. The other four are the D-bits, the S-, X- and E-bits.

# Frame Synchronization Pattern

The frame synchronization pattern are shown in table17 to 20.

The frame synchronization pattern for a network rate of 600 bit/s uses E7 for super frame synchronization. Network rates of 48000 bit/s or 56000 bit/s use the octet alignment provided by the B channel. Bit 1 of each octet is tested at 48000 bit/s while bit 8 is used at 56000 bit/s

Table 17 work Rates 600 ... 38400 bit/s

Frame Structure Octet 7 8 5 6 No. 1 2 3 4 n 0 0 ብ 0 0 Λ 1 2 3 1 1 4 5 1 (E7)\* 1 6 7 1 8 1

Table 18 Frame Synchronization Pattern for Net- Frame Synchronization Pattern for a Network Rate of 48000 bit/s

| Octet | Fra | Frame Structure |   |   |   |   |   |   |  |

|-------|-----|-----------------|---|---|---|---|---|---|--|

| No.   | 1   | 2               | 3 | 4 | 5 | 6 | 7 | 8 |  |

| 1     | 1   |                 |   |   |   |   |   |   |  |

| 2     | 0   |                 |   |   |   |   |   |   |  |

| 3     | 1   |                 |   |   |   |   |   |   |  |

| 4     | 1   |                 |   |   |   |   |   |   |  |

Table 19 Network Rate of 56000 bit/s Frame Alternative 1

10

Table 20 Frame Synchronization Pattern for a Frame Synchronization Pattern for a Network Rate of 56000 bit/s Frame Alternative 2

| Frame Alternative 1 |     |          |           |      |        |   | Tanic |   |              |         |          |           |           |        |   |   |   |

|---------------------|-----|----------|-----------|------|--------|---|-------|---|--------------|---------|----------|-----------|-----------|--------|---|---|---|

| Octet<br>No.        | Fra | ame<br>2 | Stru<br>3 | ctur | e<br>5 | 6 | 7     | 8 | Octet<br>No. | Fr<br>1 | ame<br>2 | Stru<br>3 | ctur<br>4 | e<br>5 | 6 | 7 | 8 |

| <del>.</del>        | -   |          |           |      |        |   |       | 1 | 1            |         |          |           |           |        |   |   | 0 |

| 1                   |     |          |           |      |        |   |       | 1 | 2            |         |          |           |           |        |   |   |   |

| 3                   |     |          |           |      |        |   |       | 1 | 3            |         |          |           |           |        |   |   |   |

| 4                   | ì   |          |           |      |        |   |       | 1 | 4            |         |          |           |           |        |   |   | 1 |

| 5                   |     |          |           |      |        |   |       | 1 | 5<br>6       |         |          |           |           |        |   |   | 1 |

| 6                   |     |          |           |      |        |   |       | 1 | 7            |         |          |           |           |        |   |   | 1 |

| 8                   |     |          |           |      |        |   |       | 1 | 8            |         |          |           |           |        |   |   | 1 |

<sup>\*</sup>E7 is controlled automatically at 600 bit/s.

#### **D-Bits**

The D-bit positions (D1 ... D48) are used to transfer the data stream between both ends. The data stream includes all character, parity, start and stop bits. If the network rate is less or equal to 4800 bit/s each bit of the data stream is transmitted twice, four or eight times to match the intermediate rate.

#### S-Bits

The S-bits are used to transfer the state of interchange circuits. In a V.110 frame, two S-bit groups SA and SB are available. SA transmits the state of the DTR/C interchange circuit (108) to the DSR interchange circuit (107). SB transmits the state of the RTS interchange circuit (105) to the DCD/I interchange circuit (109).

In an X.30 frame all S-bits are used to transfer the state of the C/DTR (108) interchange circuit onto the I/DCD (109) interchange circuit.

The selection between both S-bit alternatives is done by the V110 bit in the General Configuration Register. If GCR:V110 = 0, the X.30 frame is selected. GCR:V110 = 1 selects the V.110 frame.

#### Table 21

| V.110 frame (GCR:V110 = '1'                                                                     | X.30 frame (GCR:V110 = '0') |             |               |   |               |             |

|-------------------------------------------------------------------------------------------------|-----------------------------|-------------|---------------|---|---------------|-------------|

| $\begin{array}{ccc} DTR/C \ (108) & \to & SA & \to \\ RTS \ (105) & \to & SB & \to \end{array}$ | DSR (107)<br>DCD/I (109)    | DTR/C (108) | $\rightarrow$ | S | $\rightarrow$ | DCD/I (109) |

Note:

SA = S1, S3, S6, S8

SB = S4, S9

#### X-Bits

The X-bits are used to perform flow control between both terminal adapters.

#### E-Bits

The E-bits are used to transfer information between both terminal adapters. In a V.110 frame, E1 to E3 are used to identify the user rate. E7 is automatically controlled if the network rate is set to 600 bit/s.

### Sample Points of the S-Bits

The coordination between the sampling of the D- and S-bits for a synchronous DCE interface (GCR:ASY = 0) is shown in **table 22**.

Table 22 Sample points of the S-Bits

| S Bit |           | D Bit   |  |

|-------|-----------|---------|--|

|       | Octet No. | Bit No. |  |

| S1    | 2         | 3 (D8)  |  |

| S3    | 3         | 4 (D16) |  |

| S4    | 4         | 7 (D24) |  |

| S6    | 7         | 3 (D32) |  |

| S8    | 8         | 5 (D40) |  |

| S9    | 9         | 7 (D48) |  |

If the DCE interface is asynchronous (GCR:ASY = 1), the S bits are sampled while the stop bit of the character is received. If no character is received, the S-bits are sampled during D8, D16, D24, D32, D40 and D48. During a break condition, the S-bits are not sampled for version VA1, VB1. The version V2.2 samples the S bits every eight D-bits during a break condition.

#### **Function of the Transmitter**

The IRC-transmitter is enabled by setting the ENFR bit to '1'.

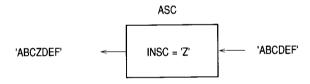

The transmitter part of the IRC will format the required frame. Therefore it will generate the frame synchronization pattern and insert the D-, S-, X- and E-bits. The source of the D-bits can either be the DCE interface, the Serial Communications Logic or the register bit XD. The source of the S-bits can either be the DCE interface control lines or the register bits S/SA and SB. The source of the X- and E-bits will always be the register bits. **Figure 24** illustrates the possible data paths.

Figure 24 IRC Transmitter

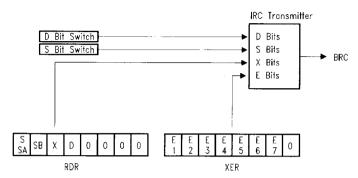

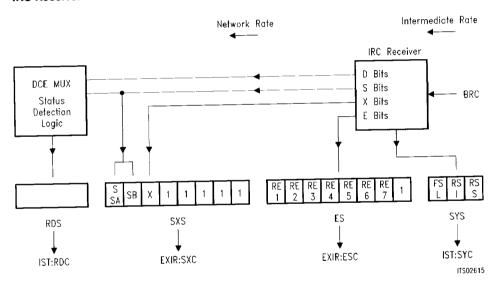

### **Function of the Receiver**

The IRC receiver is enabled by setting the ENFR bit to '1'. The receiver part of the IRC will search for the frame synchronization pattern. A status register tells the actual status of the receiver. The receiver also extracts the D-, S-, X- and E-bits and forwards them to their programmed destination. The received D-bits may be transmitted to the DCE interface. They are always transmitted to the Serial Communication Logic. The received S-bits may also be transmitted to the DCE interface. They are always transmitted to the SXS Status register. An interrupt is generated on every status change. The received X-bits are always transmitted to the SXS Status register and E-bits to the ES register. An interrupt is generated on every X- or E-bit change.

Figure 25 IRC Receiver

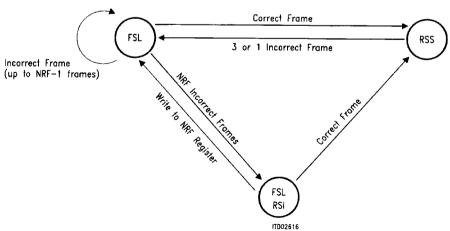

### **Synchronization Status**

The IRC receiver reports its frame synchronization status in the SYS register. The most significant three bits are used. **Table 23** shows the indicated states.

Table 23 States of the IRC Receiver

|     | SYS |     |                                                                                                                                                  |

|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| FSL | RSI | RSS | Status                                                                                                                                           |

| 1   | 0   | 0   | No synchronization is achieved. Status while ENFR = 0 or after 1 or 3 incorrect frames.                                                          |

| 1   | 1   | 0   | Resynchronization impossible. Status after the number of frames specified in the NFR register were counted down without gaining synchronization. |

| 0   | 0   | 0   | Synchronization achieved. Status after one correct frame has been received.                                                                      |

If the IRC is enabled, it will always search for the synchronization pattern regardless of its actual state. If it finds the synchronization pattern it will change to RSS. **Figure 25** illustrates the state machine of the IRC receiver.

Figure 26

Synchronization State Machine

The IRC receiver will always output data even if FSL = 1. Therefore the data path should be selected after RSS has been detected.

In case of a network rate of 64 kbit/s, FSL stays '1' and RSI, RSS are '0'.

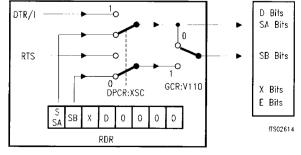

#### Remote DTE Status Indications

The received S/SA- and D bits are evaluated by the remote DTE status logic. The detected combinations are reported by the RDS register. Changes in the RDS register set the RDC status bit in the IST register which may activate the INT output.

The remote DTE status logic is in 'no-state' after reset. 'No-state' is indicate by a value of zero in the RDS register. The remote DTE status logic starts to sample the S/SA- and D-bits after ENFR has been set to '1', regardless of the current synchronization status of the IRC receiver. The sampled data is compared against different possibilities after 16 D-bit samples were taken. If a match is detected the RDS register changes to the new value and the RDC status bit is set to '1'. If a status is detected which is different from LONX or LOFX, the remote DTE status detection logic will sample four D-bits before the pattern is varified again. If the status is no longer true, the RDS register changes to 'no-state' and the RDC status bit is set to '1'. The next status indication will be indicated after another 16 D-bits have been sampled.

If LONX or LOFX or no valid status is detected after 16 samples, the status detection logic will check its last 16 samples after every D-bit.

The valid status are shown in table 24.

Table 24

Remote DTE Status Indications

| Status | Status Name     | Sampled Data                                  | Register Bit |

|--------|-----------------|-----------------------------------------------|--------------|

| RONX   | Remote (X, ON)  | D XXXXXXXX XXXXXXXX<br>S/SA 00000000 00000000 | Bit 7        |

| ROFX   | Remote (X, OFF) | D                                             | Bit 6        |

| RON1   | Remote (1, ON)  | D 11111111 11111111<br>S/SA 00000000 00000000 | Bit 5        |

| ROF1   | Remote (1, OFF) | D 11111111 11111111<br>S/SA 11111111 11111111 | Bit 4        |

| ROF0   | Remote (0, OFF) | D 00000000 00000000<br>S/SA 11111111 11111111 | Bit 3        |

| RL2    | Remote Loop 2   | D 00110011 00110011<br>S/SA 00000000 00000000 | Bit 2        |

For network rates which do not provide a S-bit (64 kbit/s; 56 kbit/s, F56 = 0), the value of the S/SA-bit in the remote DTE status detection logic is set to '1'. The RDS register will only indicate ROFX, ROF1, ROF0.

The remote DTE status detection may be used to detect the (S/SA = OFF, D = 0) condition which indicates a disconnect request according to V.110.

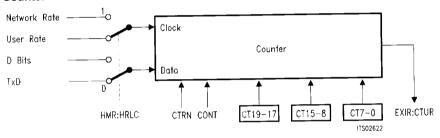

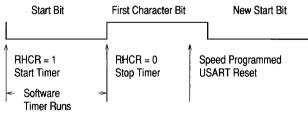

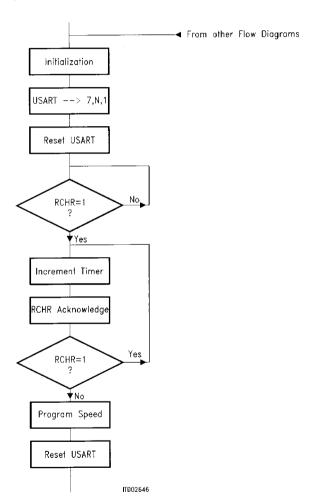

### 2.7 Bearer Rate Converter