# DATA SHEET

S5D2501F

#### **OVERVIEW**

The S5D2501F is used to display some characters or symbols on a screen of monitor. Basically, the operation is to control the internal memory on chip and generate the R,G,B signals for some characters or symbols. The R,G,B signals are synchronized with the horizontal sync. Then the R,G,B signals are mixed with the main video signal in the Video Amp IC.

The font data for characters or symbols are stored in the internal ROM. This stored data are accessed and controlled by the control data from a micro controller. The control data are transmitted through the I<sup>2</sup>C bus. All timing control signals including the system clock are synchronized with the horizontal sync. Therefore there is a PLL circuitry on chip.

#### **FEATURES**

- Build in 1K-byte SRAM

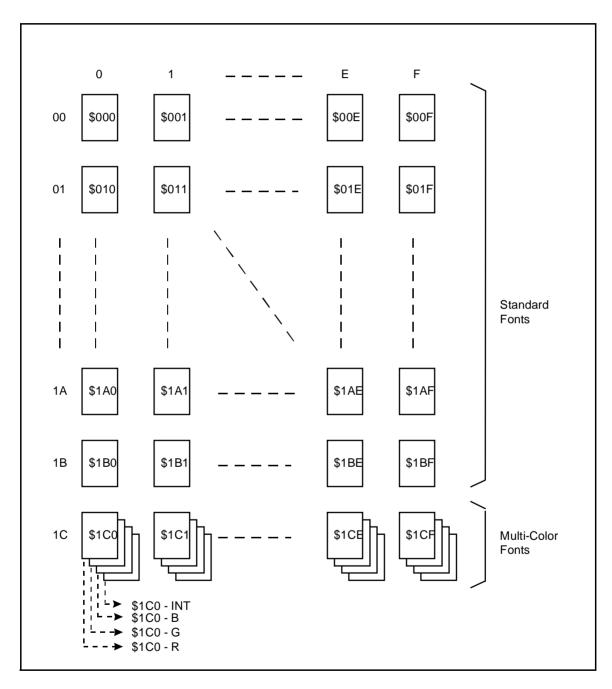

- 464 ROM fonts (448 standard fonts + 16 Multi-color fonts)

- Full Screen Memory Architecture

- Wide range PLL available (15 kHz 120 kHz)

- · Programmable vertical height of character

- Programmable vertical and horizontal positioning

- Character color selection up to 16 different colors

- Programmable background color (Up to 16 colors)

- Character blinking, bordering and shadowing

- Color blinking

- Character scrolling

- Fade-in and fade-out

- · Row to row spacing control

- Window outline and shadowing

- Box drawing

- Character sizing up to four times

- 8 PWM DAC channels with 8-bit resolution

- 96 MHz pixel frequency from on-chip PLL

- I2C Protocol Data Transmission (Slave Address : BAH)

- OSD Vertical Bouncing Auto Detect / Correction

- Back Raster Blanking (Row Control)

#### ORDERING INFORMATION

| Device   | Package    | Operating Temperature |

|----------|------------|-----------------------|

| S5D2501F | 24-DIP-300 | 0°C — 70°C            |

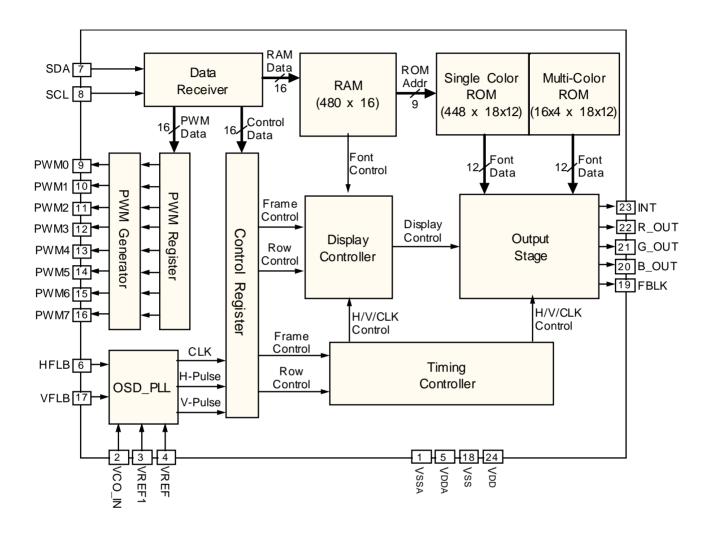

# **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

•

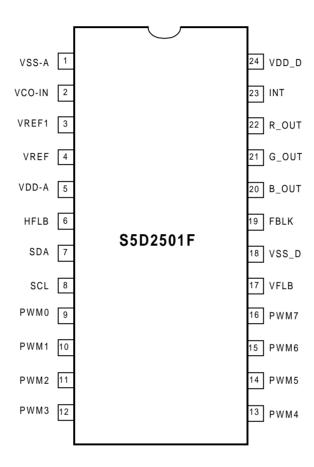

# **PIN CONFIGURATIONS**

Figure 2. Pin Configurations

# **PIN DESCRIPTIONS**

**Table 1. Pin Descriptions**

| Pin No. | Signal | Active | I/O    | Description                                                                                                                                                    |

|---------|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VSS_A  | -      | -      | Ground (Analog Part)                                                                                                                                           |

| 2       | VCO_IN | -      | Input  | This voltage is generated at the external loop filter and goes into the input stage of the VCO.                                                                |

| 3       | VREF1  | -      | Input  | 1.26 V DC Voltage from the Bandgap Reference. Connected to ground through a resistor to make internal reference current (Typical 36 k $\Omega$ for 27 $\mu$ A) |

| 4       | VREF   | -      | Input  | Bandgap Reference Voltage (Typical 1.26 V)                                                                                                                     |

| 5       | VDD_A  | -      | -      | +5 V Supply Voltage for Analog Part                                                                                                                            |

| 6       | HFLB   | Low    | Input  | Horizontal Flyback Signal                                                                                                                                      |

| 7       | SDA    | -      | In/Out | Serial Data (I <sup>2</sup> C)                                                                                                                                 |

| 8       | SCL    | -      | In/Out | Serial Clock (I <sup>2</sup> C)                                                                                                                                |

| 9       | PWM 0  | -      | Output | PWM DAC 0 Output                                                                                                                                               |

| 10      | PWM 1  | -      | Output | PWM DAC 1 Output                                                                                                                                               |

| 11      | PWM 2  | -      | Output | PWM DAC 2 Output                                                                                                                                               |

| 12      | PWM 3  | -      | Output | PWM DAC 3 Output                                                                                                                                               |

| 13      | PWM 4  | -      | Output | PWM DAC 4 Output                                                                                                                                               |

| 14      | PWM 5  | -      | Output | PWM DAC 5 Output                                                                                                                                               |

| 15      | PWM 6  | -      | Output | PWM DAC 6 Output                                                                                                                                               |

| 16      | PWM 7  | -      | Output | PWM DAC 7 Output                                                                                                                                               |

| 17      | VFLB   | Low    | Input  | Vertical Flyback Signal                                                                                                                                        |

| 18      | VSS_D  | -      | -      | Ground for Digital Part                                                                                                                                        |

| 19      | FBLK   | -      | Output | Fast Blank Signal                                                                                                                                              |

| 20      | B_OUT  | -      | Output | Video Signal Output (B)                                                                                                                                        |

| 21      | G_OUT  | -      | Output | Video Signal Output (G)                                                                                                                                        |

| 22      | R_OUT  | -      | Output | Video Signal Output (R)                                                                                                                                        |

| 23      | INT    | -      | Output | Intensity Signal Output                                                                                                                                        |

| 24      | VDD_D  | -      | -      | +5 V Supply Voltage for Dogital Part                                                                                                                           |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameters                  | Symbol           |      | Unit |      |      |

|-----------------------------|------------------|------|------|------|------|

| raianieters                 | Symbol           | Min. | Тур. | Max. | Onit |

| Maximum Supply Voltage      | VDD              | -    | -    | 6.5  | V    |

| Input Voltage               | V <sub>I</sub>   | -    | -    | 5.25 | V    |

| Operating Temperature Range | T <sub>OPR</sub> | -20  | -    | 70   | °C   |

| Storage Temperature Range   | T <sub>STG</sub> | -40  |      | 125  | °C   |

| Power Dissipation           | P <sub>D</sub>   | -    | -    | 1200 | mW   |

NOTE: PKG Thermal Resistance : 64.2 °C/W

# **ELECTRICAL CHARACTERISTICS**

#### **DC Electrical Characteristics**

(Ta = 25  $^{\circ}$ C, V<sub>DD</sub> = 5 V)

**Table 2. DC Electrical Characteristics**

| Parameters (Conditions)                   | Symbol           | Min.               | Тур. | Max.                  | Unit |

|-------------------------------------------|------------------|--------------------|------|-----------------------|------|

| Supply Voltage                            | $V_{DD}$         | 4.75               | 5.00 | 5.25                  | V    |

| Supply Current<br>(No load on any output) | I <sub>DD</sub>  | -                  | -    | 25                    | mA   |

| Lea (Million)                             | $V_{IH}$         | 0.8V <sub>DD</sub> | -    | -                     | V    |

| Input Voltage                             | V <sub>IL</sub>  | -                  | -    | V <sub>SS</sub> + 0.4 | V    |

| Output Voltage                            | V <sub>OH</sub>  | 0.8V <sub>DD</sub> | -    | -                     | V    |

| $(lout = \pm 1mA)$                        | V <sub>OL</sub>  | -                  | -    | V <sub>SS</sub> + 0.4 | V    |

| Input Leakage Current                     | I <sub>IL</sub>  | -10                | -    | 10                    | μΑ   |

| VCO Input Voltage                         | V <sub>VCO</sub> |                    | 2.5  |                       | V    |

# **OPERATION TIMINGS**

**Table 3. Operation Timings**

| Parameters (Conditions)                             | Symbol            | Min.           | Тур.          | Max. | Unit |

|-----------------------------------------------------|-------------------|----------------|---------------|------|------|

| Output Signal R/G/B_OUT, INT, FBLK                  | (Ta = 25°C VDD    | A = VDD = 5 V, | CLOAD = 30pF) |      | •    |

| Rise Time                                           | t <sub>R</sub>    | -              | -             | 6    | nsec |

| Fall Time                                           | t <sub>F</sub>    | -              | -             | 6    | nsec |

| Input Signal HFLB, VFLB                             | •                 |                |               |      | •    |

| Horizontal Flyback Signal Frequency                 | f <sub>HFLB</sub> | -              | -             | 120  | kHz  |

| Vertical Flyback Signal Frequency                   | f <sub>VFLB</sub> | -              | -             | 200  | Hz   |

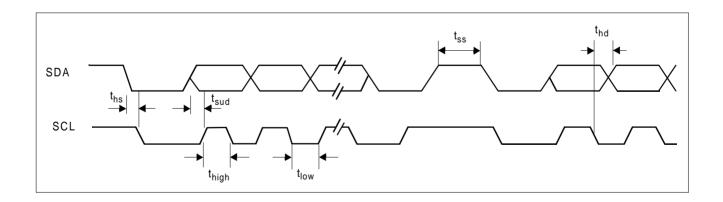

| I <sup>2</sup> C Interface SDA, SCL (Refer to Figur | e 3)              |                |               |      |      |

| SCL Clock Frequency                                 | f <sub>SCL</sub>  | -              | -             | 300  | kHz  |

| Hold Time for start condition                       | t <sub>hs</sub>   | 500            | -             | -    | ns   |

| Set Up Time for stop condition                      | t <sub>sus</sub>  | 500            | -             | -    | ns   |

| Low Duration of clock                               | t <sub>low</sub>  | 400            | -             | -    | ns   |

| High Duration of clock                              | t <sub>high</sub> | 400            | -             | -    | ns   |

| Hold Time for data                                  | t <sub>hd</sub>   | 0              | -             | -    | ns   |

| Set Up Time for data                                | t <sub>sud</sub>  | 500            | -             | -    | ns   |

| Time between 2 access                               | t <sub>ss</sub>   | 500            | -             | -    | ns   |

| Fall Time of SDA                                    | t <sub>fSDA</sub> | -              | -             | 20   | ns   |

| Rise Time of both SCL and SDA                       | t <sub>rSDA</sub> | -              | -             | -    | ns   |

Figure 3. I<sup>2</sup>C Bus Timing Diagram

#### **FUNCTIONAL DESCRIPTIONS**

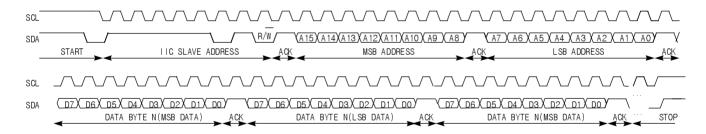

#### Data Transmission to the S5D2501F

According to the I<sup>2</sup>C protocol, the S5D2501F receives the data from a micro controller. The SDA line and the SCL line are shown in Figure 4. As shown in Figure 4, after the starting pulse, the slave address with R/W\* bit and an acknowledge are transmitted in sequence, an internal register address of the S5D2501F is followed. The first 8-bit byte is the upper 8bits of the register address. The lower 8bits of the register address are followed after the second acknowledge. There is a data transmission format and are two address bit patterns in the S5D2501F as following. The slave address of the S5D2501F is BAH(in hexadecimal).

#### **Data Transmission Format**

Row Address -> Column Address -> Data Byte N -> Data Byte N+1 -> Data Byte N+2 -> ....

### Address Bit Pattern for Display Registers Data

(a) Row Address Bit Pattern

R3 - R0: Valid Data for Row Address

| A1 | 5 | A14 | A13 | A12 | A11 | A10 | A9 | A8 |

|----|---|-----|-----|-----|-----|-----|----|----|

| Х  |   | Χ   | Χ   | Х   | R3  | R2  | R1 | R0 |

(b) Column Address Bit Pattern

C4 - C0: Valid Data for Column Address

| A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|----|

| Х  | Х  | Х  | C4 | C3 | C2 | C1 | C0 |

After addressing, data bytes are followed as the above data transmission format. The Figure 4 describes the data transmission with the I<sup>2</sup>C bus protocol.

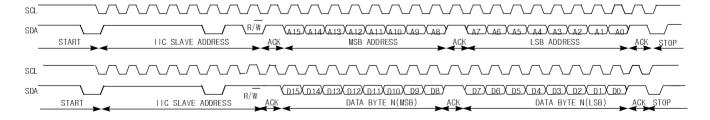

Figure 4. (a) SDA line and SCL line (Write Operation)

Figure 4. (b)SDA line and SCL line (Read Operation)

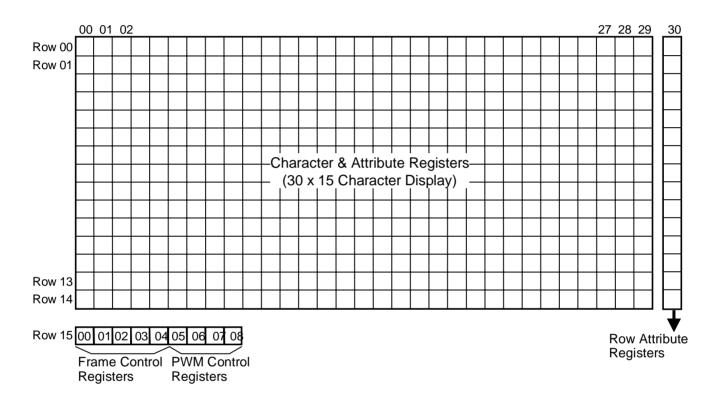

#### **Memory Map**

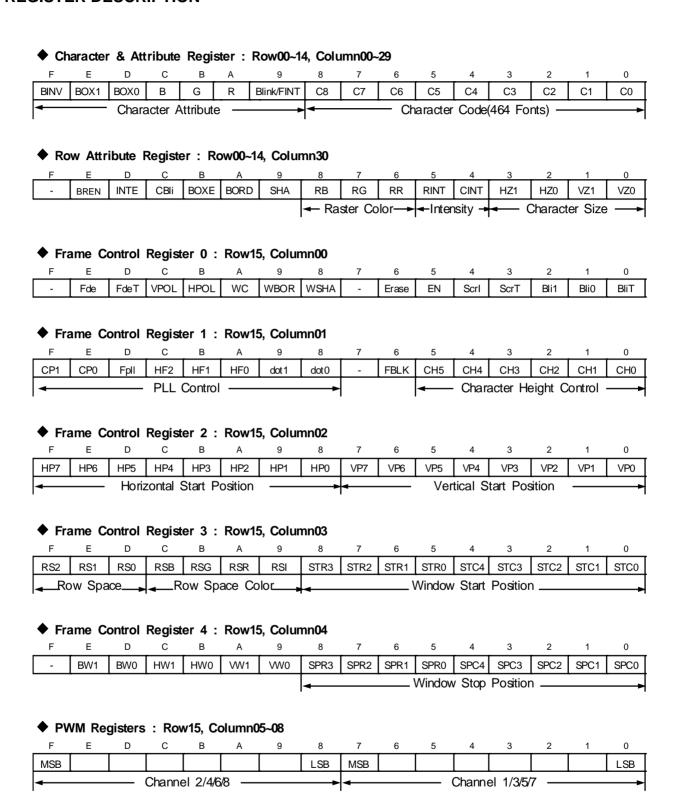

The display RAM is addressed with the row and column number in sequence. The display RAM consists of four register groups: Character & Attribute Registers, Row Attribute Registers, Frame Control Registers and PWM Control Registers. As the display area in a monitor screen is 30 columns by 15 rows, the related Character & Attribute Registers are also 30 columns by 15 rows. Each register contains a character address and an attribute corresponding to display location on a monitor screen. And one register is composed of 16 bits. The lower 9 bits select characters out of 464 ROM fonts. The upper 7 bits are assigned to give a character attribute to a selected font. Row Attribute Registers occupy the 31th column of Display RAM and provide the row attribute of a blank mode, raster color, raster color intensity, character color intensity, horizontal character size, vertical character size. Frame Control Registers and PWM Control Registers are located at the 16th row.

The content of each register is described in Figure 5 and following register set.

Figure 5. Memory Map of Display Registers

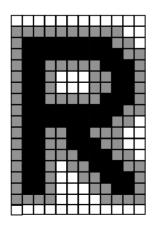

#### **ROM Fonts**

S5D2501F is able to supply 464 ROM fonts for describing an OSD icon. So a multi-language OSD icon can be generated. 448 fonts of 464 ROM fonts are standard fonts and 16 fonts are multi-color fonts as following figure. The standard font \$000 is reserved for blank data.

Each multi-color font consists of 4-color attribute ROM fonts as following figure.

Figure 6. Array of ROM Fonts

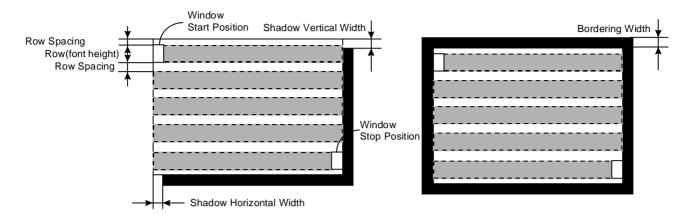

# Window, Window Shadowing and Bordering

#### Scroll

The scrolling function is to display or erase a character slowly from the top line to the bottom. The scrolling time is controlled by 'ScrT'bit of the frame control registers. If 'ScrT' bit is high, then the time is 1 sec. Otherwise, 0.5 sec.

# **Character Bordering & Shadowing**

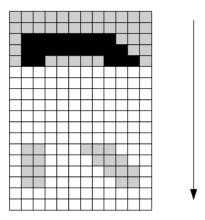

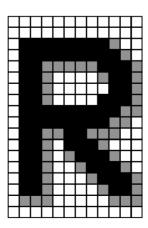

#### **Character Height Control**

Two examples of the height-controlled character are shown in the following figure. The height control is performed by repeating some lines. The repeating line-number comes from the equation below.

```

[# of the repeating lines = 2 + N \times M], where N = 1,2,3,... and M = round{14 \div (CH[5:0]-18)}.

```

If the M value is less than or equal to 1, all the lines of the standard font are repeated once or more. This is described as following.

(i) If CH[5:0] is greater than 32, and less than or equal to 46 (  $32 < CH[5:0] \le 46$  ), then all lines are repeated once or twice. The lines repeated twice are selected by the following equation.

```

[# of the repeating lines = 2 + N \times M], where N = 1,2,3,... and M= round{14 \div (CH[5:0]-32)}.

```

(ii) If CH[5:0] is greater than 46, and less than or equal to 60 (  $46 < CH[5:0] \le 60$  ), then all lines are repeated twice or three times. The lines repeated three times are

selected by the following equation.

```

[# of the repeating lines = 2 + N \times M], where N = 1,2,3,... and M= round{14 \div (CH[5:0]-46)}.

```

iii) If CH[5:0] is greater than 60, and less than or equal to 64 (  $60 < CH[5:0] \le 64$  ), then all lines are repeated three or four times. The lines repeated four times are

then all lines are repeated three or four times. The lines repeated four times are selected by the following equation.

```

[# of the repeating lines = 2 + N \times M ] , where N = 1,2,3,... and M= round{14÷(CH[5:0]-60)}.

```

The repeating line-number is limited to 16.

SAMSUNG ELECTRONICS

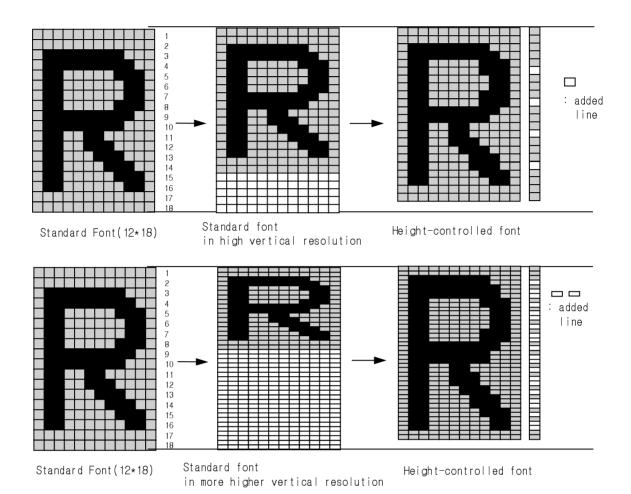

# **PWM OUTPUT**

The frequency of PWM signal (fPWM) is dependent on the horizontal flyback signal frequency and horizontal mode (320dots/line, ...) as shown in the following table.

| Horizontal Mode      | 320 dots/line<br>(fрwм) | 480 dots/line<br>(fрwм) | 640 dots/line<br>(fрwм) | 800 dots/line<br>(fpwm) |

|----------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| 15kHz < Hf < 20kHz   |                         |                         | (640/256) * Hf          | (800/256) * Hf          |

| 20kHz < Hf < 35kHz   |                         | (480/256) * Hf          |                         |                         |

| 35kHz < Hf < 50kHz   | (320/256) * Hf          |                         | (640/256) * (Hf/2)      | (800/256) * (Hf/2)      |

| 50kHz < Hf < 65kHz   |                         | (480/256) * (Hf/2)      |                         |                         |

| 65kHz < Hf < 80kHz   |                         |                         |                         |                         |

| 80kHz < Hf < 95kHz   |                         |                         | (640/256) * (Hf/4)      | (800/256) * (Hf/4)      |

| 95kHz < Hf < 110kHz  | (320/256) * (Hf/2)      |                         |                         | (333,233) (1.11/1)      |

| 110kHz < Hf < 120kHz |                         |                         |                         |                         |

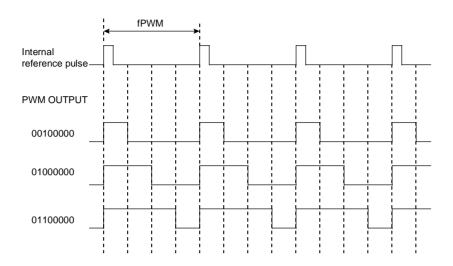

#### **FRAME CONTROL & TIMING**

Figure 7 shows the composition of display frame with the OSD characters.

Figure 7. Frame Composition with the OSD Characters

User can determine the dot frequency by the equation of H freq. x the number of horizontal resolution. And the number of horizontal resolution is determined by the bit9 - 8 (dot 1,dot 0) of the frame Control registers-1. If dot 0 = "0", dot 1 = "0", then the dot frequency is calculated by the equation of H freq.  $\times$  320. If the H freq. = 15 kHz, then the dot frequency is 15 kHz $\times$  320 = 4.8 MHz.

If dot 0 = "1", dot 1 = "1" and the horizontal frequency is 120 kHz, then the dot frequency is 120 kHz  $\times$  800 = 96 MHz. 96 MHz is the maximum clock frequency in this processor.

#### REGISTER DESCRIPTION

'-'; Don't care bit

**Table 4. Register Description**

| Registers                                     | Bits                         |                    |                           |                                   | D                     | escription                                                                                                                                   |  |  |

|-----------------------------------------------|------------------------------|--------------------|---------------------------|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Character & Attribute<br>Register (Row 00—14, | C8—C0<br>(Bit 8—0)           | Charac             | ter Cod                   | e Addre                           | ess of 4              | 64 ROM Fonts.                                                                                                                                |  |  |

| Column 00—29)                                 | Blink<br>(Bit 9)             | Set this<br>by the | 'Bli T' bi<br>E' bit is h | ictivate<br>t and th<br>nigh, thi | e duty i<br>s bit co  | king effect. The blinking period is set s selected by the 'Bli 0' and 'Bli 1' bits. ntrols the font intensity combined with following table. |  |  |

|                                               |                              | INTE               | Function                  |                                   |                       |                                                                                                                                              |  |  |

|                                               |                              | 0                  | 0                         | -                                 | -                     | Normal                                                                                                                                       |  |  |

|                                               |                              | 0                  | 1                         | -                                 | -                     | Blink                                                                                                                                        |  |  |

|                                               |                              | 1                  | 0                         | -                                 | -                     | Normal                                                                                                                                       |  |  |

|                                               |                              | 1                  | 1                         | 0                                 | 1                     | Character Intensity                                                                                                                          |  |  |

|                                               |                              | 1                  | 1                         | 1                                 | 0                     | Raster Intensity                                                                                                                             |  |  |

|                                               |                              | 1                  | 1                         | 1                                 | 1                     | Character & Raster Intensity                                                                                                                 |  |  |

|                                               |                              |                    |                           |                                   |                       |                                                                                                                                              |  |  |

|                                               | B,G,R<br>(Bit C—A)           |                    |                           |                                   |                       |                                                                                                                                              |  |  |

|                                               | BOX 1,<br>BOX0<br>(Bit E, D) | The co<br>modes    | as follo                  | ons of thowing. T                 | his two<br>Γhe follo  | bits generate four different box drawing bwing example is the case that box font 'A'.                                                        |  |  |

|                                               |                              |                    | E                         | BOX0<br>BOX1                      | 0                     | 1                                                                                                                                            |  |  |

|                                               |                              |                    |                           | 0                                 | вох                   | off A                                                                                                                                        |  |  |

|                                               |                              |                    |                           | 1                                 | P                     | A A                                                                                                                                          |  |  |

|                                               |                              | 'BOXE<br>the 'E    | E' bit lov                | v. Rast<br>oit is lov             | er color<br>v. Priori | so used for raster color by setting the of a font is determined by this bits if ty of raster color selected here is higher                   |  |  |

Table 4. Register Description (Continued)

| Registers                                          | Bits                  |                                                                                                                                  |                                                                                                                                                                                                 |               | Description                                 |            |  |  |

|----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------|------------|--|--|

| Character & Attribute<br>Register                  | BINV<br>(Bit F)       | Box Inversion.  The box drawing activated by the bit E and D is changed to white box from black and conversely.                  |                                                                                                                                                                                                 |               |                                             |            |  |  |

| Row Attribute Register<br>(Row 00 — 14, Column 30) | VZ1,VZ0<br>(Bit 1, 0) | Ver                                                                                                                              | tical Charac<br>tical charac<br>as followir                                                                                                                                                     | ter size is c | ontrol.<br>letermined by the combinations o | f this two |  |  |

|                                                    |                       |                                                                                                                                  | VZ1                                                                                                                                                                                             | VZ0           | Vertical Character Size                     |            |  |  |

|                                                    |                       |                                                                                                                                  | 0                                                                                                                                                                                               | 0             | 1X                                          |            |  |  |

|                                                    |                       |                                                                                                                                  | 0                                                                                                                                                                                               | 1             | 2X                                          |            |  |  |

|                                                    |                       |                                                                                                                                  | 1                                                                                                                                                                                               | 0             | 3X                                          |            |  |  |

|                                                    |                       |                                                                                                                                  | 1                                                                                                                                                                                               | 1             | 4X                                          |            |  |  |

|                                                    | HZ1,HZ0<br>(Bit 3, 2) | Horizontal Character Size Control.  The horizontal character size is determined by the combine this two bits as following table. |                                                                                                                                                                                                 |               |                                             |            |  |  |

|                                                    |                       |                                                                                                                                  | HZ1                                                                                                                                                                                             | HZ0           | Horizontal Character Size                   |            |  |  |

|                                                    |                       |                                                                                                                                  | 0                                                                                                                                                                                               | 0             | 1X                                          |            |  |  |

|                                                    |                       |                                                                                                                                  | 0                                                                                                                                                                                               | 0             | 2X<br>3X                                    |            |  |  |

|                                                    |                       |                                                                                                                                  | 1                                                                                                                                                                                               | 1             | 4X                                          |            |  |  |

|                                                    |                       |                                                                                                                                  | '                                                                                                                                                                                               | <u>'</u>      | 4//                                         |            |  |  |

|                                                    | CINT<br>(Bit 4)       | If I                                                                                                                             | naracter Col<br>NTE, Blink the same ro                                                                                                                                                          | and this bit  | is set, the color intensity of chara        | acters     |  |  |

|                                                    | RINT<br>(Bit 5)       | If I                                                                                                                             | aster Color li<br>NTE, Blink a<br>the same ro                                                                                                                                                   | and this bit  | is set, the color intensity of raste        | ers        |  |  |

|                                                    | RB,RG,RR<br>(Bit 8—6) | 8 d<br>giv                                                                                                                       | Raster Color is determined by these bits. 8 colors can be selected and the color intensity of a character is given by 'RINT' bit of Row Attribute Registers. So you can select up to 16 colors. |               |                                             |            |  |  |

|                                                    | SHA<br>(BIT 9)        |                                                                                                                                  | naracter Sha<br>et this bit to a                                                                                                                                                                |               | aracters shadowing.                         |            |  |  |

|                                                    | BORD<br>(Bit A)       |                                                                                                                                  | naracter Bor<br>et this bit to a                                                                                                                                                                |               | aracters bordering.                         |            |  |  |

**Table 4. Register Description (Continued)**

| Registers              | Bits            | Description                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Row Attribute Register | BOXE<br>(Bit B) | BOX Enable.  If this bit is set, Bit F-D in the Character & Attribute Registers are used for the box-drawing function.  Otherwise,those are used for raster color of a font.  Even though the raster color attribute is given by Bit 8-6 in the row attribute registers, the priority of Bit F-D in the character & attribute registers is higher. |

|                        | CBli<br>(Bit C) | Color Blink Enable.  If this bit is high, color blinking effect is activated. The color effect is to repeat color inversion between character and raster.  Color blinking time and the duty is controlled byBil T, Bil 1 and Bli 0.                                                                                                                |

|                        | INTE<br>(Bit D) | Intensity Enable. If this bit and Blink bit(CHARACTERATTRIBUTE) is high, character and raster intensity can be controlled.                                                                                                                                                                                                                         |

|                        | BREN<br>(Bit E) | Back Raster Enable.  If this bit is high and back raster color is black, back raster color is blank.                                                                                                                                                                                                                                               |

|                        | Bit F           | Reserved                                                                                                                                                                                                                                                                                                                                           |

Table 4. Register Description (Continued)

| Registers                                    | Bits                     | Description                                                                                                          |                              |                                                           |                |  |  |  |

|----------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------|----------------|--|--|--|

| Frame Control Register 0 (Row 15, Column 00) | Bli T<br>(Bit 0)         | Blink Time C                                                                                                         |                              | k time is 0.5 sec. Otherwise,                             | I sec.         |  |  |  |

|                                              | Bli 1,Bli 0<br>(Bit 2,1) | Blinking Duty<br>The blinking<br>following.                                                                          |                              | olled by the combination of th                            | is two bits as |  |  |  |

|                                              |                          | Bli 1                                                                                                                | Bli 0                        | Blinking Duty                                             |                |  |  |  |

|                                              |                          | 0                                                                                                                    | 0                            | Blink Off                                                 |                |  |  |  |

|                                              |                          | 0                                                                                                                    | 1                            | Duty 25%                                                  |                |  |  |  |

|                                              |                          | 1                                                                                                                    | 0                            | Duty 50%                                                  |                |  |  |  |

|                                              |                          | 1                                                                                                                    | 1                            | Duty 75%                                                  |                |  |  |  |

|                                              | ScrT<br>(Bit 3)          | Scroll Time Control.  If this bit is high, the scroll time is 1 sec. Otherwise, 0.5 sec.                             |                              |                                                           |                |  |  |  |

|                                              | Scrl<br>(Bit 4)          | Scroll Enable. The scroll display is activated by setting this bit high.                                             |                              |                                                           |                |  |  |  |

|                                              | EN<br>(Bit 5)            | OSD Enable. The character display is controlled by this bit. If this bit is high, OSD is enable. Otherwise, disable. |                              |                                                           |                |  |  |  |

|                                              | Erase<br>(Bit 6)         | RAM Erasing. RAM data are erased by setting this bit.                                                                |                              |                                                           |                |  |  |  |

|                                              | WSHA<br>(Bit 8)          | Window Sha<br>Set this bit to                                                                                        | -                            | ndow shadowing.                                           |                |  |  |  |

|                                              | WBOR<br>(Bit 9)          | Window Bor<br>Set this bit to                                                                                        | -                            | ndow bordering.                                           |                |  |  |  |

|                                              | WC<br>(Bit A)            |                                                                                                                      | nigh, the colo               | window border and shadow.<br>or of window border and shad | ow is white.   |  |  |  |

|                                              | HPOL<br>(Bit B)          | Polarity of H                                                                                                        | orizontal Fly                | Back Signal. Positive 1, Neg                              | ative 0        |  |  |  |

|                                              | VPOL<br>(Bit C)          | Polarity of V                                                                                                        | ertical Fly Ba               | nck Signal. Positive 1, Negativ                           | re 0           |  |  |  |

|                                              | FdeT<br>(Bit D)          |                                                                                                                      | fade-out Tim                 | ne Control.<br>e is 1 sec. Otherwise, 0.5 sec             | <b>).</b>      |  |  |  |

|                                              | Fde<br>(Bit E)           |                                                                                                                      | fade-out Ena<br>and fade-out | able.<br>effect is activated by setting t                 | this bit high. |  |  |  |

|                                              | Bit F                    | Reserved.                                                                                                            |                              |                                                           |                |  |  |  |

**Table 4. Register Description (Continued)**

| Registers                                       | Bits                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                                                               |  |  |

|-------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------|--|--|

| Frame Control Register 1<br>(Row 15, Column 01) | CH5—CH0<br>(Bit 5—0)     | Character Height Control. The vertical character size is determined by the bit 'VZ1' and VZ0'. This six bits are available to get a proper character height by setting a binary value. According to the value made by this six bits, the character height is determined. If the value is 32, the number of vertical pixel of character font is 32. Eventually, the character height is expanded from 18 to 63. The binary vlaue must be greater than 18. |       |                                                                               |  |  |

|                                                 | FBLK<br>(Bit 6)          | It determines the configuration of FBLK output pin. When it is clear, FBLK pin outputs high during displaying characters or rasters. Otherwise, FBLK pin outputs high only during displaying characters.                                                                                                                                                                                                                                                 |       |                                                                               |  |  |

|                                                 | dot 1,dot 0<br>(Bit 9,8) | This two bits determine the number of dots per horizontal line. Refer to following table.                                                                                                                                                                                                                                                                                                                                                                |       |                                                                               |  |  |

|                                                 |                          | dot 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | dot 0 | No. of Dots                                                                   |  |  |

|                                                 |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 320 dots/line                                                                 |  |  |

|                                                 |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     | 480 dots/line                                                                 |  |  |

|                                                 |                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 640 dots/line                                                                 |  |  |

|                                                 |                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     | 800 dots/line                                                                 |  |  |

|                                                 | HF2—HF0<br>(Bit C—A)     | These three bits decide horizontal frequency range (region). Please refer to Application Note for more information.                                                                                                                                                                                                                                                                                                                                      |       |                                                                               |  |  |

|                                                 | FPLL<br>(Bit D)          | If this bit is high, the VCO block of OSD_PLL operates on full range (4 MHz - 96 MHz).                                                                                                                                                                                                                                                                                                                                                                   |       |                                                                               |  |  |

| Frame Control Register 1                        | CP 1,CP 0                | This bit controls charge pump output current.                                                                                                                                                                                                                                                                                                                                                                                                            |       |                                                                               |  |  |

| (Row 15, Column 01)                             | (Bit F,E)                | CP 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CP 0  | Charge Pump Current                                                           |  |  |

|                                                 |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0.75mA                                                                        |  |  |

|                                                 |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     | 1 mA                                                                          |  |  |

|                                                 |                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 1.25mA                                                                        |  |  |

|                                                 |                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     | 1.5 mA                                                                        |  |  |

| Frame Control Register 2<br>(Row 15, Column 02) | VP7—VP0<br>(Bit 7—0)     | Vertical Start Position Control. It means the top margin height from the V-sync reference edge. ( = $VP[7:0] \times 4$ )                                                                                                                                                                                                                                                                                                                                 |       |                                                                               |  |  |

|                                                 | HP7—HP0<br>(Bit F—8)     | It means the                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | Control.<br>lisplay delay from the H-sync<br>sition of characters. ( = HP[7:0 |  |  |

Table 4. Register Description (Continued)

| Registers                                       | Bits                 | Description                                                                                                                                          |  |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Frame Control Register 3 (Row 15, Column 02)    | STC 4<br>—STC 0      | Window Start Column Position. It means the column address that window starts from.                                                                   |  |

|                                                 | STR 3<br>—STR 0      | Window Start Row Position.<br>It means the row address that window starts from.                                                                      |  |

|                                                 | RSI                  | Row Space Color Intensity.                                                                                                                           |  |

|                                                 | RSR,RSG,<br>RSB      | Row Space Color Attribute.                                                                                                                           |  |

|                                                 | RS2—RS0<br>(Bit F—D) | Row Space. It means the line number between a character row and the next row. The defaut value is 0. (line number for spacing = $RS[2:0] \times 2$ ) |  |

| Frame Control Register 4<br>(Row 15, Column 04) | SPC 4—<br>SPC 0      | Window Stop Column Position. It means the column address that window stops on.                                                                       |  |

|                                                 | SPR 3—<br>SPR 0      | Window Stop Row Position. It means the row address that window stops on.                                                                             |  |

|                                                 | VW 1, 0              | Vertical width of window shadowing.                                                                                                                  |  |

|                                                 | HW 1, 0              | Horizontal width of window shadowing.                                                                                                                |  |

|                                                 | BW 1, 0              | Width of window bordering.                                                                                                                           |  |

| PWM Registers<br>(Row 15, Column 05 - 08)       | Bit 7— 0             | This 8-bit value decides the output duty cycle and waveforms of PWM for channel 1,3,5 and 7.                                                         |  |

|                                                 | Bit F—8              | This 8-bit value decides the output duty cycle and waveforms of PWM for channel 2,4,6 and 8.                                                         |  |

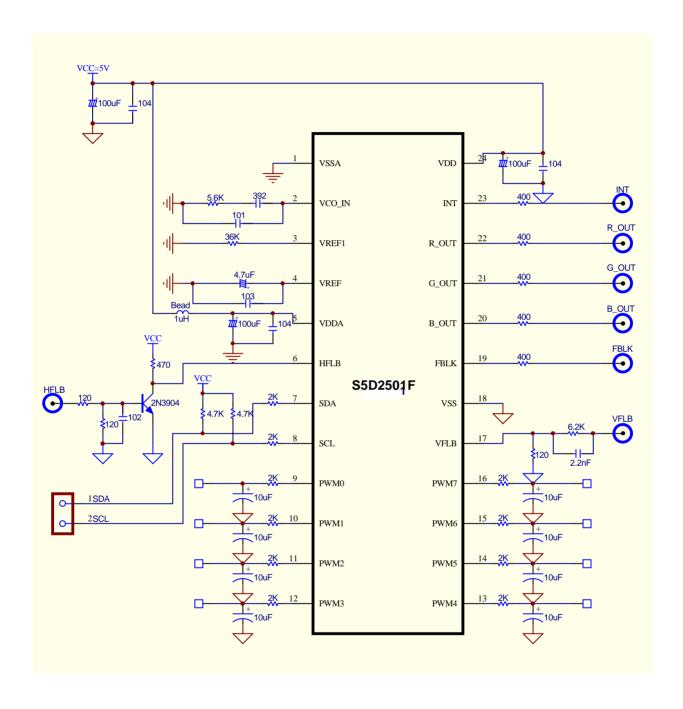

# **APPLICATION CIRCUIT**