October 1988 Revised May 2000

## DM93S41 4-Bit Arithmetic Logic Unit

## **General Description**

The DM93S41 4-bit arithmetic logic units can perform all the possible 16 logic operations on two variables and a variety of arithmetic operations; the Add and Subtract modes are the most important.

## **Ordering Code:**

| Order Number | der Number Package Number Package Description |                                                                       |

|--------------|-----------------------------------------------|-----------------------------------------------------------------------|

| DM93S41N     | N24A                                          | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide |

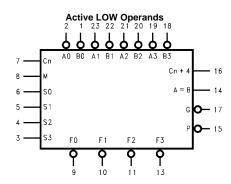

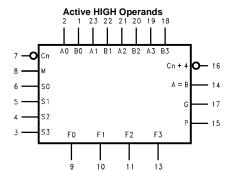

## **Logic Symbols**

## **Connection Diagram**

## **Pin Descriptions**

| Pin Name          | Description                         |

|-------------------|-------------------------------------|

| A0–A3, B0–B3      | Operand Inputs (Active LOW)         |

| S0-S3             | Function Select Inputs              |

| М                 | Mode Control Input                  |

| Cn                | Carry Input                         |

| F0-F3             | Function Outputs (Active LOW)       |

| A = B             | Comparator Output                   |

| $\frac{A = B}{G}$ | Carry Generate Output (Active LOW)  |

| P                 | Carry Propagate Output (Active LOW) |

| C <sub>n+4</sub>  | Carry Output                        |

## **Functional Description**

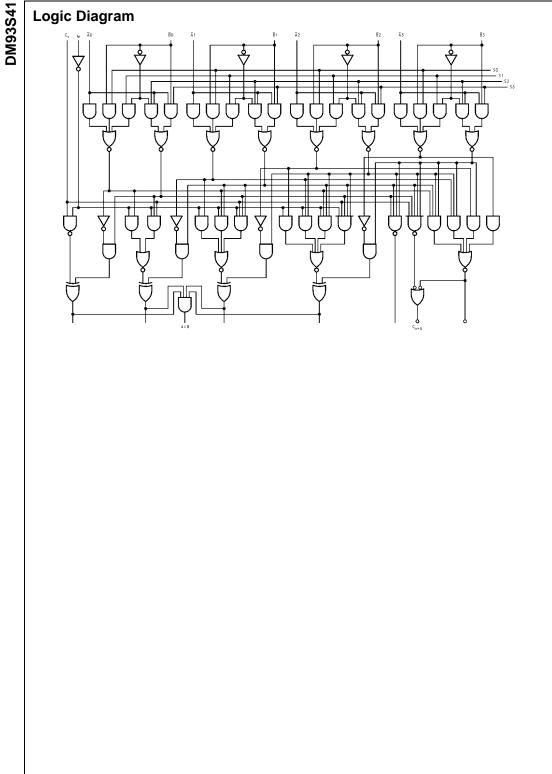

The DM93S41 is a 4-bit high speed parallel arithmetic logic unit (ALU). Controlled by the four Function Select inputs (S0-S3) and the Mode Control input (M), it can perform all the 16 possible operations or 16 different arithmetic operations on active HIGH or active LOW operands. The Function Table below lists these operations.

When the Mode Control input (M) is HIGH, all internal carries are inhibited and the device performs logic operations on the individual bits as listed. When the Mode Control input is LOW, the carries are enabled and the device performs arithmetic operations on the two 4-bit words. The device incorporates full internal carry lookahead and provides for either ripple carry between devices using the C<sub>n+4</sub> output, or for carry lookahead between packages using the signals P (Carry Propagate) and G (Carry Generate). P and G are not affected by carry in. When speed requirements are not stringent, the DM93S41 can be used in a simple ripple carry mode by connecting the Carry output (Cn+4) signal to the Carry input (Cn) of the next unit. For super high speed operation the Schottky DM93S41 should be used in conjunction with the '42 carry lookahead circuit.

The A = B output from the DM93S41 goes HIGH when all four  $\overline{F}_n$  outputs are HIGH and can be used to indicate logic equivalence over four bits when the unit is in the subtract mode. The A = B output is open-collector and can be wired-AND with the other A = B outputs to give a comparison for more than four bits. The A = B signal can also be used with the  $C_{n+4}$  signal to indicate A > B and A < B.

The Function Table lists the arithmetic operations that are performed without a carry in. An incoming carry adds a one to each operation. Thus select code LHHL generates A minus B minus 1 (2s complement notation) without a carry in and generates A minus B when a carry is applied. Because subtraction is actually performed by complementary addition (1s complement), a carry out means borrow; thus a carry is generated when there is no underflow and no carry is generated when there is underflow.

As indicated the '41 can be used with either active LOW inputs producing active LOW outputs or with active HIGH inputs producing active HIGH outputs. For either case the table lists the operations that are performed to the operands labeled inside the logic symbol.

#### **Function Table**

| Mode Select |        |    |    | Active LOW Inputs                  |                                                      | Active HIGH Inputs            |                                                                 |  |

|-------------|--------|----|----|------------------------------------|------------------------------------------------------|-------------------------------|-----------------------------------------------------------------|--|

|             | Inputs |    |    |                                    | & Outputs                                            | & Outputs                     |                                                                 |  |

|             |        |    |    | Logic                              | Arithmetic (Note 2)                                  | Logic Arithmetic (Note 2)     |                                                                 |  |

| S3          | S2     | S1 | S0 | (M = H)                            | $(\mathbf{M}=\mathbf{L})  (\mathbf{C_n}=\mathbf{L})$ | (M = H)                       | $(\mathbf{M}=\mathbf{L})\ (\mathbf{C}_{\mathbf{n}}=\mathbf{H})$ |  |

| L           | L      | L  | L  | Ā                                  | A minus 1                                            | Ā                             | A                                                               |  |

| L           | L      | L  | Н  | ĀB                                 | AB minus 1                                           | $\overline{A} + \overline{B}$ | A + B                                                           |  |

| L           | L      | Н  | L  | $\overline{A} + \overline{B}$      | AB minus 1                                           | ĀB                            | $A + \overline{B}$                                              |  |

| L           | L      | Н  | Н  | Logic 1                            | minus 1                                              | Logic 0                       | minus 1                                                         |  |

| L           | Н      | L  | L  | $\overline{A} + \overline{B}$      | A plus $(A + \overline{B})$                          | AB                            | A plus AB                                                       |  |

| L           | Н      | L  | Н  | В                                  | AB plus $(A + \overline{B})$                         | B                             | (A +B) plus AB                                                  |  |

| L           | Н      | Н  | L  | $\overline{A} \oplus \overline{B}$ | A minus B minus 1                                    | A ⊕ B                         | A minus B minus 1                                               |  |

| L           | Н      | Н  | Н  | $A + \overline{B}$                 | $A + \overline{B}$                                   | AB                            | AB minus 1                                                      |  |

| Н           | L      | L  | L  | ĀB                                 | A plus (A + B)                                       | A + B                         | A plus AB                                                       |  |

| Н           | L      | L  | Н  | $A \oplus B$                       | A plus B                                             | A ⊕ B                         | A plus B                                                        |  |

| Н           | L      | Н  | L  | В                                  | $A\overline{B}$ plus $(A + B)$                       | В                             | $(A + \overline{B})$ plus AB                                    |  |

| Н           | L      | Н  | Н  | A + B                              | A + B                                                | AB                            | AB minus 1                                                      |  |

| Н           | Н      | L  | L  | Logic 0                            | A plus A (Note 1)                                    | Logic 1                       | A plus A (Note 1)                                               |  |

| Н           | Н      | L  | Н  | $A\overline{B}$                    | AB plus A                                            | $A + \overline{B}$            | (A + B) plus A                                                  |  |

| Н           | Н      | Н  | L  | AB                                 | AB minus A                                           | A + B                         | $(A + \overline{B})$ plus A                                     |  |

| Н           | Н      | Н  | Н  | Α                                  | Α                                                    | Α                             | A minus 1                                                       |  |

H = HIGH Voltage Level

L = LOW Voltage Level

Note 1: Each bit is shifted to the next more significant position

Note 2: Arithmetic operations expressed in 2s complement notation

|                                                                                                                                                          | Input                                  | Other Input Same Bit                        |                                              | Other D                                                                                   | Output                                                                                                                                           |                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| Symbol                                                                                                                                                   | Under<br>Test                          | Apply<br>4.5V                               | Apply<br>GND                                 | Apply<br>4.5V                                                                             | Apply<br>GND                                                                                                                                     | Under<br>Test                              |  |

| PLH, tPHL                                                                                                                                                | Ā                                      | B <sub>i</sub>                              | None                                         | Remaining A to B                                                                          | C <sub>n</sub>                                                                                                                                   | Fi                                         |  |

| PLH, tPHL                                                                                                                                                | B <sub>i</sub>                         | Ā                                           | None                                         | Remaining A to B                                                                          | C <sub>n</sub>                                                                                                                                   | Fi                                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | B <sub>i</sub>                              | None                                         | C <sub>n</sub>                                                                            | Remaining A and B                                                                                                                                | F <sub>i+1</sub>                           |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B <sub>i</sub>                         | Ā                                           | None                                         | C <sub>n</sub>                                                                            | Remaining A and B                                                                                                                                | F <sub>i+1</sub>                           |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | B                                           | None                                         | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | P                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B                                      | Ā                                           | None                                         | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | P                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | None                                        | В                                            | Remaining B                                                                               | Remaining A, C <sub>n</sub>                                                                                                                      | G                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B                                      | None                                        | Ā                                            | Remaining B                                                                               | Remaining $\overline{A}$ , $C_n$                                                                                                                 | G                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | None                                        | B                                            | Remaining B                                                                               | Remaining A, C <sub>n</sub>                                                                                                                      | C <sub>n + 4</sub>                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B                                      | None                                        | Ā                                            | Remaining B                                                                               | Remaining A, C <sub>n</sub>                                                                                                                      | C <sub>n+4</sub>                           |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | C <sub>n</sub>                         | None                                        | None                                         | All A                                                                                     | All B                                                                                                                                            | Any F or C <sub>n</sub>                    |  |

|                                                                                                                                                          | TABL                                   | E 2. DIFF MOI                               | DE TEST Fund                                 | ction Inputs: S1 = S2 = 4                                                                 | I.5V,S0 = S3 = M = 0V                                                                                                                            |                                            |  |

|                                                                                                                                                          | Input                                  | Other Inpu                                  | t Same Bit                                   | Other D                                                                                   | ata Inputs                                                                                                                                       | Output                                     |  |

| Symbol                                                                                                                                                   | Under                                  | Apply                                       | Apply                                        | Apply                                                                                     | Apply                                                                                                                                            | Under                                      |  |

|                                                                                                                                                          | Test                                   | 4.5V                                        | GND                                          | 4.5V                                                                                      | GND                                                                                                                                              | Test                                       |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | None                                        | B                                            | Remaining A                                                                               | Remaining B, C <sub>n</sub>                                                                                                                      | Fi                                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B                                      | Ā                                           | None                                         | Remaining A                                                                               | Remaining B, C <sub>n</sub>                                                                                                                      | Fi                                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | None                                        | B <sub>i</sub>                               | Remaining $\overline{B}$ , $C_n$                                                          | Remaining A                                                                                                                                      | F <sub>i+1</sub>                           |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B <sub>i</sub>                         | $\overline{A}_{i}$                          | None                                         | Remaining B, C <sub>n</sub>                                                               | Remaining A                                                                                                                                      | F <sub>i+1</sub>                           |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | None                                        | B                                            | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | P                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | B                                      | Ā                                           | None                                         | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | P                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | Ā                                      | B                                           | None                                         | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | G                                          |  |

|                                                                                                                                                          | B                                      | None                                        | Ā                                            | None                                                                                      | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$                                                                                              | G                                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | _                                      | None                                        | B                                            | Remaining A                                                                               | Remaining B, C <sub>n</sub>                                                                                                                      | A = B                                      |  |

|                                                                                                                                                          | Α                                      |                                             |                                              |                                                                                           |                                                                                                                                                  |                                            |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      | A<br>B                                 | Ā                                           | None                                         | Remaining A                                                                               | Remaining B, C <sub>n</sub>                                                                                                                      | A = B                                      |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>                                                                                                                      |                                        |                                             | None<br>None                                 | Remaining A  None                                                                         | Remaining $\overline{\overline{B}}$ , $C_n$<br>Remaining $\overline{\overline{A}}$ and $\overline{\overline{B}}$ , $C_n$                         | $A = B$ $C_n + 4$                          |  |

| t <sub>PLH</sub> , t <sub>PHL</sub> t <sub>PLH</sub> , t <sub>PHL</sub> t <sub>PLH</sub> , t <sub>PHL</sub>                                              | B                                      | Ā                                           |                                              |                                                                                           | •                                                                                                                                                |                                            |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>          | B                                      | Ā<br>B                                      | None                                         | None                                                                                      | Remaining A and B, C <sub>n</sub>                                                                                                                | C <sub>n</sub> + 4                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>          | B<br>A<br>B<br>C <sub>n</sub>          | A<br>B<br>None<br>None                      | None A                                       | None<br>None                                                                              | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ None                                     | C <sub>n</sub> + 4                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub>          | B<br>A<br>B<br>C <sub>n</sub>          | A<br>B<br>None<br>None                      | None  None  DE TEST Fun                      | None None All $\overline{A}$ and $\overline{B}$ ction Inputs: S1 = S2 =                   | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ None                                     | C <sub>n</sub> + 4                         |  |

| t <sub>PLH</sub> , t <sub>PHL</sub> t <sub>PLH</sub> , t <sub>PHL</sub> t <sub>PLH</sub> , t <sub>PHL</sub>                                              | B A B C <sub>n</sub> TABLE             | A B None None 3. LOGIC MO                   | None  None  DE TEST Fun                      | None None All $\overline{A}$ and $\overline{B}$ ction Inputs: S1 = S2 =                   | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ None  M = 4.5V, S0 = S3 = 0V             | $C_n + 4$ $C_n + 4$ $C_n + 4$              |  |

| tplh, tphl                                                                  | B A B C <sub>n</sub> TABLE             | A B None None 3. LOGIC MO                   | None  A  None  DE TEST Fun  t Same Bit       | None None All $\overline{A}$ and $\overline{B}$ ction Inputs: S1 = S2 = Other D           | Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ Remaining $\overline{A}$ and $\overline{B}$ , $C_n$ None  M = 4.5V, S0 = S3 = 0V  ata Inputs | $C_n + 4$ $C_n + 4$ $C_n + 4$ Output       |  |

| t <sub>РLH</sub> , t <sub>РHL</sub><br>t <sub>РLH</sub> , t <sub>РHL</sub><br>t <sub>РLH</sub> , t <sub>РHL</sub><br>t <sub>РLH</sub> , t <sub>РHL</sub> | B A B C <sub>n</sub> TABLE Input Under | A B None None S. LOGIC MO Other Input Apply | None  A  None  DE TEST Fun t Same Bit  Apply | None  None  All $\overline{A}$ and $\overline{B}$ ction Inputs: S1 = S2 =  Other D  Apply | Remaining A and B, C <sub>n</sub> Remaining A and B, C <sub>n</sub> None  M = 4.5V, S0 = S3 = 0V  ata Inputs  Apply                              | $C_n + 4$ $C_n + 4$ $C_n + 4$ Output Under |  |

## Absolute Maximum Ratings(Note 3)

Supply Voltage 7V Input Voltage: 5.5V Operating Free Air Temperature Range  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature Range  $-65^{\circ}$ C to  $+150^{\circ}$ C

Note 3: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| I <sub>OH</sub> | HIGH Level Output Current      |      |     | -1   | mA    |

| I <sub>OL</sub> | LOW Level Output Current       |      |     | 20   | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                         | Conditions                                                                         | Min | Typ<br>(Note 4) | Max  | Units |

|------------------|-----------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------|-------|

| VI               | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$                                               |     |                 | -1.2 | V     |

| V <sub>OH</sub>  | HIGH Level                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max                                       | 2.7 | 3.4             |      | V     |

|                  | Output Voltage                    | $V_{IL} = Max$                                                                     | 2.1 |                 |      | v     |

| V <sub>OL</sub>  | LOW Level<br>Output Voltage       | $V_{CC} = Min, I_{OL} = Max$<br>$V_{IH} = Min$                                     |     | 0.35            | 0.5  | V     |

| I                | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 5.5V$                                                         |     |                 | 1    | mA    |

| I <sub>IH</sub>  | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.7V$                                                         |     |                 | 50   | μΑ    |

| I <sub>IL</sub>  | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.5V$                                                         |     |                 | -1.6 | mA    |

| Ios              | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 5)                                                     | -40 |                 | -100 | mA    |

| I <sub>CCL</sub> | Supply Current                    | $V_{CC} = Max$ M, S0-S3 = 4.5V All Other Inputs = 0V                               |     |                 | 150  | mA    |

| I <sub>CCH</sub> | Supply Current                    | $V_{CC} = Max$ $C_n$ , $\overline{B}0-\overline{B}3 = GND$ All Other Inputs = 4.5V |     |                 | 140  | mA    |

Note 4: All typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

Note 5: Not more than one output should be shorted at a time, and the duration should not exceed one second.

# Switching Characteristics $V_{CC}$ = +5.0V, $T_A$ = +25°C

|                  |                                                              |                           | CL =              | 15 pF |          |  |

|------------------|--------------------------------------------------------------|---------------------------|-------------------|-------|----------|--|

| Symbol           | Parameter                                                    | Conditions                | $R_L = 280\Omega$ |       | Units    |  |

|                  |                                                              |                           | Min               | Max   | 1        |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M = GND                   |                   | 12    | ns       |  |

| t <sub>PHL</sub> | C <sub>n</sub> to C <sub>n+4</sub>                           |                           |                   | 12    |          |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M = GND                   |                   | 12    |          |  |

| t <sub>PHL</sub> | C <sub>n</sub> to F                                          |                           |                   | 12    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S1, S2 = GND           |                   | 14    |          |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $\overline{G}$       | S0, S3 = 4.5V             |                   | 14    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 15    |          |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $\overline{G}$       | S1, S2 = 4.5V             |                   | 15    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S1, S2 = GND           |                   | 14    | ns       |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $\overline{P}$       | S0, S3 = 4.5V             |                   | 14    |          |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 15    | ns       |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $\overline{P}$       | S1, S2 = 4.5V             |                   | 15    |          |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S1, S3 = GND           |                   | 20    |          |  |

| t <sub>PHL</sub> | A <sub>i</sub> or B <sub>i</sub> to F <sub>i</sub>           | S0, S3 = 4.5V             |                   | 20    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 21    |          |  |

| t <sub>PHL</sub> | $\overline{A}_i$ or $\overline{B}_i$ to $\overline{F}_i$     | S1, S2 = 4.5V             |                   | 21    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S1, S2 = GND           |                   | 24    |          |  |

| t <sub>PHL</sub> | $\overline{A}_i$ or $\overline{B}_i$ to $\overline{F}_{i+1}$ | S0, S3 = 4.5V             |                   | 24    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 25    | ns       |  |

| t <sub>PHL</sub> | $\overline{A}_i$ or $\overline{B}_i$ to $\overline{F}_{i+1}$ | S1, S2 = 4.5V             |                   | 25    | 115      |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M = 4.5V                  |                   | 20    |          |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $\overline{F}$       |                           |                   | 20    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S1, S2 = GND           |                   | 18.5  | <b>†</b> |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $C_{n+1}$            | S0, S3 = 4.5V             |                   | 18.5  | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 23    | ne       |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $C_{n+1}$            | S1, S2 = 4.5V             |                   | 23    | ns       |  |

| t <sub>PLH</sub> | Propagation Delay                                            | M, S0, S3 = GND           |                   | 23    |          |  |

| t <sub>PHL</sub> | $\overline{A}_n$ or $\overline{B}_n$ to $A = B$              | S1, S2 = 4.5V             |                   | 23    | ns       |  |

|                  |                                                              | $R_L = 400\Omega$ to 5.0V |                   |       |          |  |

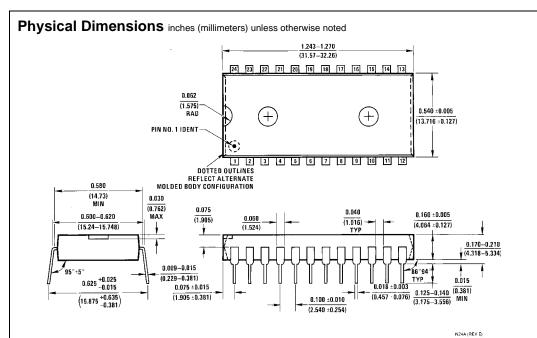

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide Package Number N24A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com