# **SHARP**

### **Data Sheet**

# LRS1341/LRS1342 Stacked Chip 16M Flash Memory and 2M SRAM

### **FEATURES**

- · Flash Memory and SRAM

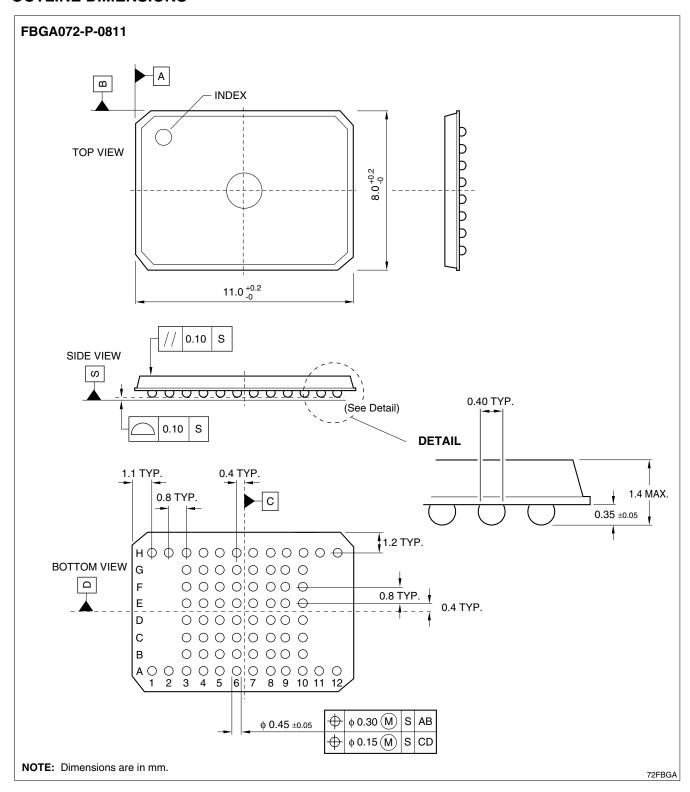

- · Stacked Die Chip Scale Package

- 72-ball CSP (FBGA072-P-0811) plastic package

- Power supply: 2.7 V to 3.6 V

- Operating temperature: -25°C to +85°C

- · Flash Memory

- Access time (MAX.): 100 ns

- Operating current (MAX.):

The current for F-V<sub>CC</sub> pin

- Read: 25 mA (t<sub>CYCLF</sub> = 200 ns)

- Word write: 17 mABlock erase: 17 mA

- − Deep power down current (the current for F- $V_{CC}$  pin): 10 μA (MAX. F- $\overline{CE}$  ≥ F- $V_{CC}$  0.2 V, F- $\overline{RP}$  ≤-0.2 V, F- $V_{PP}$  ≤0.2 V)

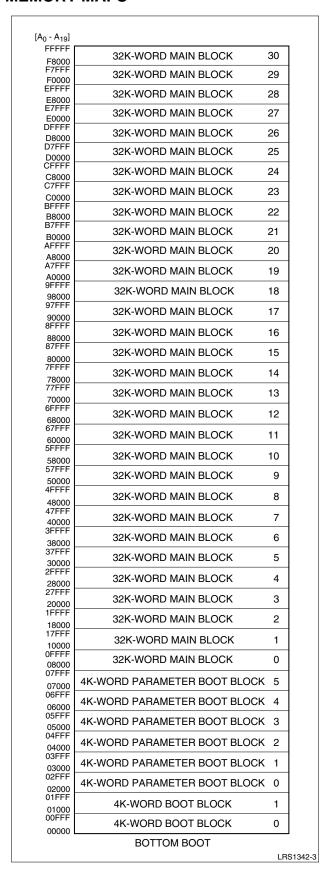

- Optimized array blocking architecture

- Two 4K-word boot blocks

- Six 4K-word parameter blocks

- Thirty-one 32K-word main blocks

- Top/Bottom boot location versions

- Extended cycling capability

- 100,000 block erase cycles

- Enhanced automated suspend options

- Word write suspend to read

- Block erase suspend to word write

- Block erase suspend to read

### SRAM

- Access time (MAX.): 85 ns

- Operating current (MAX.):

- 45 mA

- 8 mA (t<sub>RC</sub>, t<sub>WC</sub> = 1  $\mu$ s)

- Standby current: 45 μA (MAX.)

- Data retention current: 35 μA (MAX.)

### DESCRIPTION

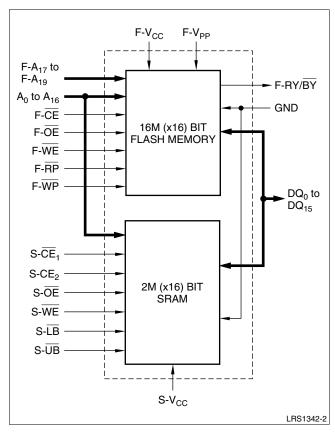

The LRS1341/LRS1342 is a combination memory organized as  $1,048,576 \times 16$ -bit flash memory and  $131,072 \times 16$ -bit static RAM in one package.

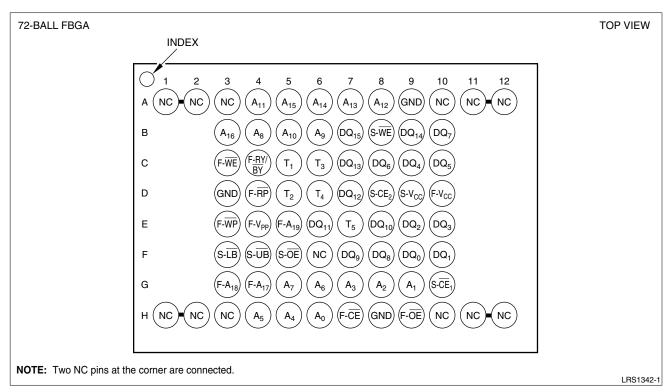

### PIN CONFIGURATION

Figure 1. LRS1341/LRS1342 Pin Configuration

Figure 2. LRS1341/LRS1342 Block Diagram

**Table 1. Pin Descriptions**

| PIN                                    | DESCRIPTION                                                                                                                                                        | TYPE         |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| A <sub>0</sub> to A <sub>16</sub>      | Address Inputs (Common)                                                                                                                                            | Input        |

| F-A <sub>17</sub> to F-A <sub>19</sub> | Address Inputs (Flash)                                                                                                                                             | Input        |

| F-CE                                   | Chip Enable Input (Flash)                                                                                                                                          | Input        |

| S-CE <sub>1</sub> , S-CE <sub>2</sub>  | Chip Enable Inputs (SRAM)                                                                                                                                          | Input        |

| F-WE                                   | Write Enable Input (Flash)                                                                                                                                         | Input        |

| S-WE                                   | Write Enable Input (SRAM)                                                                                                                                          | Input        |

| F-OE                                   | Output Enable Input (Flash)                                                                                                                                        | Input        |

| S-OE                                   | Output Enable Input (SRAM)                                                                                                                                         | Input        |

| S- <u>LB</u>                           | SRAM Byte Enable Input (DQ <sub>0</sub> to DQ <sub>7</sub> )                                                                                                       | Input        |

| S- <del>UB</del>                       | SRAM Byte Enable Input (DQ <sub>8</sub> to DQ <sub>15</sub> )                                                                                                      | Input        |

| F-RP                                   | Reset/Power Down (Flash) Block erase and Word Write: V <sub>IH</sub> or V <sub>HH</sub> Read: V <sub>IH</sub> or V <sub>HH</sub> Reset/Power Down: V <sub>IL</sub> | Input        |

| F-WP                                   | Write Protect (Flash) Two Boot Blocks Locked: V <sub>IL</sub> (with F-RP = V <sub>HH</sub> Erase of Write can operate to all blocks)                               | Input        |

| F-RY/BY                                | Ready/Busy (Flash) During an Erase or Write operation: V <sub>OL</sub> Block Erase and Word Write Suspend: HIGH-Z Deep Power Down: V <sub>OH</sub>                 | Output       |

| DQ <sub>0</sub> to DQ <sub>15</sub>    | Data Input/Outputs (Common)                                                                                                                                        | Input/Output |

| F-V <sub>CC</sub>                      | Power Supply (Flash)                                                                                                                                               | Power        |

| S-V <sub>CC</sub>                      | Power Supply (SRAM)                                                                                                                                                | Power        |

| F-V <sub>PP</sub>                      | Write, Erase Power Supply (Flash) Block Erase and Word Write: F-V <sub>PP</sub> = V <sub>PPLK</sub> All Blocks Locked: F-V <sub>PP</sub> < V <sub>PPLK</sub>       | Power        |

| GND                                    | Ground (Common)                                                                                                                                                    | Power        |

| NC                                     | No Connection                                                                                                                                                      | _            |

| T <sub>1</sub> to T <sub>5</sub>       | Test Pins (Should be Open)                                                                                                                                         | _            |

# Table 2. Truth Table<sup>1</sup>

| FLASH            | SRAM    | F-CE | F-RP | F-OE | F-WE | S-CE <sub>1</sub> | S-CE <sub>2</sub> | S-OE | S-WE | S-LB              | S-ŪB       | DQ <sub>0</sub> -<br>DQ-7 | DQ <sub>8</sub> -<br>DQ <sub>15</sub> | NOTES      |

|------------------|---------|------|------|------|------|-------------------|-------------------|------|------|-------------------|------------|---------------------------|---------------------------------------|------------|

| Read             | Standby | L    | Н    | L    | Н    |                   |                   | Х    | Х    |                   |            | D <sub>C</sub>            | UT                                    | 2, 3       |

| Output Disable   | Standby | L    | Н    | Н    | Н    | See N             | Note 4            | Х    | Χ    | See N             | Note 4     | HIG                       | H-Z                                   | 3          |

| Write            | Standby | L    | Н    | Н    | L    |                   |                   | Х    | Χ    |                   |            | D                         | IN                                    | 2, 3, 5, 6 |

|                  | Read    | Н    | Н    | Х    | Х    | L                 | Н                 | L    | Н    |                   | See Note 7 |                           |                                       |            |

| Standby          | Output  | Н    | Н    | Х    | Х    | L                 | Н                 | Н    | Н    | Х                 | Χ          | HIG                       | H-Z                                   |            |

| Standby          | Disable | Н    | Н    | Х    | Х    | L                 | Н                 | Х    | Χ    | Н                 | Н          | HIG                       | H-Z                                   |            |

|                  | Write   | Н    | Н    | Х    | Х    | L                 | Н                 | L    | L    |                   | 200.1      | Note 7                    |                                       |            |

|                  | Read    | Х    | L    | Х    | Х    | L                 | Н                 | L    | Н    |                   | See i      | NOIE /                    |                                       |            |

| Reset/Power Down | Output  | Х    | L    | Х    | Х    | L                 | Н                 | Н    | Н    | Х                 | Χ          | HIG                       | H-Z                                   |            |

| Resel/Power Down | Disable | Х    | L    | Х    | Х    | L                 | Н                 | Х    | Χ    | Н                 | Н          | HIG                       | H-Z                                   |            |

|                  | Write   | Х    | L    | Х    | Х    | L                 | Н                 | L    | L    |                   | See N      | Note 7                    |                                       |            |

| Standby          | Standby | Н    | Н    | Х    | Х    | Cook              | loto 1            | Х    | Χ    | Cook              | lata 1     | HIG                       | H-Z                                   | 3          |

| Reset/Power Down | Standby | Х    | L    | Х    | Х    | 5ee r             | Note 4            | Х    | Х    | See Note 4 HIGH-Z |            | 3                         |                                       |            |

### NOTES:

- 1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = H or L. Refer to DC Characteristics.

- Refer to the 'Flash Memory Command Definition' section for valid D<sub>IN</sub> during a write operation.

- 3. F- $\overline{\text{WP}}$  set to  $V_{\text{IL}}$  or  $V_{\text{IH}}$ .

- 4. SRAM standby mode. See Table 2a.

Command writes involving block erase or word write are reliably executed when F-V<sub>PP</sub> = V<sub>PPH</sub> and F-V<sub>CC</sub> = 2.7 V to 3.6 V. Block erase or word write with V<sub>IH</sub> < RP < V<sub>HH</sub> produce spurious results and should not be attempted.

- 6. Never hold F-OE LOW and F-WE LOW at the same time.

- 7. S-\overline{IB}, S-\overline{IB} control mode. See Table 2b.

Table 2a.

| MODE              |                   | PINS              |      |      |  |  |  |  |  |

|-------------------|-------------------|-------------------|------|------|--|--|--|--|--|

| WIODE             | S-CE <sub>1</sub> | S-CE <sub>2</sub> | S-LB | S-UB |  |  |  |  |  |

| Ot a sa allas s   | Н                 | Х                 | Х    | Х    |  |  |  |  |  |

| Standby<br>(SRAM) | Х                 | L                 | Х    | Х    |  |  |  |  |  |

| (- /              | Х                 | Х                 | Н    | Н    |  |  |  |  |  |

Table 2b.

| MODE       |      |                             | PINS                              |                                    |

|------------|------|-----------------------------|-----------------------------------|------------------------------------|

| (SRAM)     | S-LB | S-LB S-UB DQ <sub>0</sub> - |                                   | DQ <sub>8</sub> - DQ <sub>15</sub> |

|            | L    | L                           | D <sub>OUT</sub> /D <sub>IN</sub> | D <sub>OUT</sub> /D <sub>IN</sub>  |

| Read/Write | L    | Н                           | D <sub>OUT</sub> /D <sub>IN</sub> | HIGH-Z                             |

|            | Н    | L                           | HIGH-Z                            | D <sub>OUT</sub> /D <sub>IN</sub>  |

Table 3. Command Definition for Flash Memory<sup>1</sup>

| COMMAND                               | BUS CYCLES | FIR                    | ST BUS CYCL          | E                 | SECON                  | ID BUS CYCL          | E                 | NOTES |

|---------------------------------------|------------|------------------------|----------------------|-------------------|------------------------|----------------------|-------------------|-------|

| COMMAND                               | REQUIRED   | OPERATION <sup>2</sup> | ADDRESS <sup>3</sup> | DATA <sup>3</sup> | OPERATION <sup>2</sup> | ADDRESS <sup>3</sup> | DATA <sup>3</sup> | NOTES |

| Read Array/Reset                      | 1          | Write                  | XA                   | FFH               |                        |                      |                   |       |

| Read Identifier Codes                 | ≥ 2        | Write                  | XA                   | 90H               | Read                   | IA                   | ID                | 4     |

| Read Status Register                  | 2          | Write                  | XA                   | 70H               | Read                   | XA                   | SRD               |       |

| Clear Status Register                 | 1          | Write                  | XA                   | 50H               |                        |                      |                   |       |

| Block Erase                           | 2          | Write                  | ВА                   | 20H               | Write                  | BA                   | D0H               | 5     |

| Word Write                            | 2          | Write                  | WA                   | 40H or 10H        | Write                  | WA                   | WD                | 5     |

| Block Erase and Word<br>Write Suspend | 1          | Write                  | XA                   | ВОН               |                        |                      |                   | 5     |

| Block Erase and Word<br>Write Resume  | 1          | Write                  | XA                   | D0H               |                        |                      |                   | 5     |

### NOTES:

- Commands other than those shown in table are reserved by SHARP for future device implementations and should not be used.

- 2. BUS operations are defined in Table 2.

- 3. XA = Any valid address within the device;

IA = Identifier code address;

BA = Address within the block being erased;

- WA = Address of memory location to be written;

- SRD = Data read from status register, see Table 6;

- WD = Data to be written at location WA. Data is latched on the rising edge of  $F-\overline{WE}$  or  $F-\overline{CE}$  (whichever goes high first);

- ID = Data read from identifier codes.

- 4. See Table 4 for Identifier Codes.

- 5. See Table 5 for Write Protection Alternatives.

### **Table 4. Identifier Codes**

| CODES            | ADDRESS<br>(A <sub>0</sub> - A <sub>18</sub> ) | LRS1341 DATA<br>(DQ <sub>0</sub> - DQ <sub>7</sub> ) | LRS1342 DATA<br>(DQ <sub>0</sub> - DQ <sub>7</sub> ) |

|------------------|------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| Manufacture Code | 00000H                                         | ВОН                                                  | ВОН                                                  |

| Device Code      | 00001H                                         | 48H                                                  | 49H                                                  |

### **Table 5. Write Protection Alternatives**

| OPERATION                    | F-V <sub>PP</sub>   | F-RP            | F-WP            | EFFECT                 |

|------------------------------|---------------------|-----------------|-----------------|------------------------|

|                              | V <sub>IL</sub>     | Х               | Х               | All blocks locked      |

|                              |                     | V <sub>IL</sub> | Х               | All blocks locked      |

| Block Erase or<br>Word Write | > V <sub>PPLK</sub> | V <sub>HH</sub> | Х               | All blocks unlocked    |

|                              |                     | V <sub>IH</sub> | V <sub>IL</sub> | Two boot blocks locked |

|                              |                     | V <sub>IH</sub> | V <sub>IH</sub> | All blocks unlocked    |

### **Table 6. Status Register Definition**

| WSMS | ESS | ES | WWS | VPPS | WWSS | DPS | R |

|------|-----|----|-----|------|------|-----|---|

| 7    | 6   | 5  | 4   | 3    | 2    | 1   | 0 |

SR.7 = Write State Machine Status (WSMS)

1 = Ready

0 = Busy

SR.6 = Erase Suspend Status (ESS)

1 = Block Erase Suspended

0 = Block Erase in Progress/Completed

SR.5 = Erase Status (ES)

1 = Error in Block Erasure

0 = Successful Block Erase

SR.4 = Word Write Status (WWS)

1 = Error in Word Write

0 = Successful Word Write

$SR.3 = V_{PP} Status (VPPS)$

1 = F-V<sub>PP</sub> LOW Detect, Operation Abort

$0 = F-V_{PP} Okay$

SR.2 = Word Write Suspend Status (WWSS)

1 = Word Write Suspended

0 = Word Write in Progress/Completed

SR.1 = Device Protect Status (DPS)

1 = F-WP and/or F-RP Lock Detected, Operation Abort

0 = Unlock

SR.0 = Reserved for future enhancements (R)

### NOTES:

- Check RY/BY or SR.7 to determine block erase or word write completion. SR.6 - SR.0 are invalid while SR.7 = 0.

- 2. If both SR.5 and SR.4 are '1's after a block erase attempt, an improper command sequence was entered.

- SR.3 does not provide a continuous indication of F-V<sub>PP</sub> level. The WSM interrogates and indicates the F-V<sub>PP</sub> level only after Block Erase or Word Write command sequences. SR.3 is not guaranteed to report accurate feedback only when F-V<sub>PP</sub> ≠ V<sub>PPH1</sub>, V<sub>PPH2</sub>.

- The WSM interrogates the F-WP and F-RP only after Block Erase or Word Write command sequences. It informs the system, depending on the attempted operation, if the F-WP is not V<sub>IH</sub> or F-RP is not V<sub>HH</sub>.

- 5. SR.0 is reserved for future use and should be masked out when polling the status register.

### **MEMORY MAPS**

Figure 3. Bottom Boot for Flash Memory

| A <sub>0</sub> - A <sub>19</sub> ] | TOP BOOT                     |    |

|------------------------------------|------------------------------|----|

| FFFFF<br>F8000                     | 4K-WORD BOOT BLOCK           | 0  |

| F7FFF<br>F0000                     | 4K-WORD BOOT BLOCK           | 1  |

| EFFFF<br>E8000                     | 4K-WORD PARAMETER BOOT BLOCK | 0  |

| E7FFF<br>E0000                     | 4K-WORD PARAMETER BOOT BLOCK | 1  |

| DFFFF<br>D8000                     | 4K-WORD PARAMETER BOOT BLOCK | 2  |

| D7FFF<br>D0000                     | 4K-WORD PARAMETER BOOT BLOCK | 3  |

| CFFFF<br>C8000                     | 4K-WORD PARAMETER BOOT BLOCK | 4  |

| C7FFF<br>C0000                     | 4K-WORD PARAMETER BOOT BLOCK | 5  |

| BFFFF<br>B8000                     | 32K-WORD MAIN BLOCK          | 0  |

| B7FFF<br>B0000                     | 32K-WORD MAIN BLOCK          | 1  |

| AFFFF<br>A8000                     | 32K-WORD MAIN BLOCK          | 2  |

| A7FFF<br>A0000                     | 32K-WORD MAIN BLOCK          | 3  |

| 9FFFF<br>98000                     | 32K-WORD MAIN BLOCK          | 4  |

| 97FFF<br>90000                     | 32K-WORD MAIN BLOCK          | 5  |

| 8FFFF<br>88000                     | 32K-WORD MAIN BLOCK          | 6  |

| 87FFF<br>80000                     | 32K-WORD MAIN BLOCK          | 7  |

| 7FFFF<br>78000                     | 32K-WORD MAIN BLOCK          | 8  |

| 77FFF<br>70000                     | 32K-WORD MAIN BLOCK          | 9  |

| 6FFFF<br>68000                     | 32K-WORD MAIN BLOCK          | 10 |

| 67FFF<br>60000                     | 32K-WORD MAIN BLOCK          | 11 |

| 5FFFF<br>58000                     | 32K-WORD MAIN BLOCK          | 12 |

| 57FFF                              | 32K-WORD MAIN BLOCK          | 13 |

| 50000<br>4FFFF                     | 32K-WORD MAIN BLOCK          | 14 |

| 48000<br>47FFF                     | 32K-WORD MAIN BLOCK          | 15 |

| 40000<br>3FFFF                     | 32K-WORD MAIN BLOCK          | 16 |

| 38000<br>37FFF                     | 32K-WORD MAIN BLOCK          | 17 |

| 30000<br>2FFFF                     | 32K-WORD MAIN BLOCK          | 18 |

| 28000<br>27FFF                     | 32K-WORD MAIN BLOCK          | 19 |

| 20000<br>1FFFF                     | 32K-WORD MAIN BLOCK          | 20 |

| 18000<br>17FFF                     | 32K-WORD MAIN BLOCK          | 21 |

| 10000<br>0FFFF                     | 32K-WORD MAIN BLOCK          | 22 |

| 08000<br>07FFF                     | 32K-WORD MAIN BLOCK          |    |

| 07000<br>06FFF                     |                              | 23 |

| 06000<br>05FFF                     | 32K-WORD MAIN BLOCK          | 24 |

| 05000<br>04FFF                     | 32K-WORD MAIN BLOCK          | 25 |

| 04000<br>03FFF                     | 32K-WORD MAIN BLOCK          | 26 |

| 03000<br>02FFF                     | 32K-WORD MAIN BLOCK          | 27 |

| 02000<br>01FFF                     | 32K-WORD MAIN BLOCK          | 28 |

| 01000<br>00FFF                     | 32K-WORD MAIN BLOCK          | 29 |

| 00000                              | 32K-WORD MAIN BLOCK          | 30 |

Figure 4. Top Boot for Flash Memory

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                 | SYMBOL            | RATINGS                      | UNIT | NOTES   |

|---------------------------|-------------------|------------------------------|------|---------|

| Supply voltage            | V <sub>CC</sub>   | -0.2 to +3.9                 | V    | 1, 2    |

| Input voltage             | V <sub>IN</sub>   | -0.2 to V <sub>CC</sub> +0.3 | V    | 1, 3, 4 |

| Operating temperature     | T <sub>OPR</sub>  | -25 to +85                   | °C   |         |

| Storage temperature       | T <sub>STG</sub>  | -55 to +125                  | °C   |         |

| F-V <sub>PP</sub> voltage | F-V <sub>PP</sub> | -0.2 to +14.0                | V    | 1, 4, 5 |

| F-RP voltage              | F-RP              | -0.5 to +14.0                | V    | 1, 4, 5 |

### NOTES:

- 1. The maximum applicable voltage on any pins with respect to GND.

- Except F-V<sub>PP</sub>.

Except F-RP.

- 4.  $-2.0\ \text{V}$  undershoot is allowed when the pulse width is less than 20 ns.

- 5. +14.0 V overshoot is allowed when the pulse width is less than 20 ns.

# RECOMMENDED DC OPERATING CONDITIONS

$T_A = -25^{\circ}C$  to  $+85^{\circ}C$

| PARAMETER      | SYMBOL          | MIN. | TYP. | MAX.                  | UNIT | NOTES |

|----------------|-----------------|------|------|-----------------------|------|-------|

| Supply voltage | V <sub>CC</sub> | 2.7  | 3.0  | 3.6                   | V    |       |

|                | V <sub>IH</sub> | 2.2  |      | V <sub>CC</sub> + 0.2 | V    | 1     |

| Input voltage  | V <sub>IL</sub> | -0.2 |      | 0.6                   | V    | 2     |

|                | V <sub>HH</sub> | 11.4 |      | 12.6                  | V    | 3     |

- 1.  $V_{CC}$  is the lower one of S-V<sub>CC</sub> and F-V<sub>CC</sub>.

- 2. -2.0 V undershoot is allowed when the pulse width is less than 20 ns.

- 3. This voltage is applicable to  $F-\overline{RP}$  pin only.

# PIN CAPACITANCE

$T_A = 25$ °C, f = 1 MHz

| PARAMETER          | SYMBOL           | CONDITION             | MIN. | TYP. | MAX. | UNIT |

|--------------------|------------------|-----------------------|------|------|------|------|

| Input capacitance* | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V |      |      | 20   | pF   |

| I/O capacitance*   | C <sub>I/O</sub> | $V_{I/O} = 0 V$       |      |      | 22   | pF   |

NOTE: \*Sampled by not 100% tested.

# **DC CHARACTERISTICS**

$T_A = -25$ °C to + 85°C,  $V_{CC} = 2.7$  V to 3.6 V

|                                                                                                                                               | PARAMETER                                                            | SYMBOL                                 | CONDITION                                                                                                                                                                                   | MIN.                                           | TYP. <sup>1</sup> | MAX.                  | UNIT | NOTES |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-----------------------|------|-------|

| Input le                                                                                                                                      | akage current                                                        | ILI                                    | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                                                                                                    | -1.5                                           |                   | +1.5                  | μΑ   |       |

| Output                                                                                                                                        | leakage current                                                      | I <sub>LO</sub>                        | V <sub>OUT</sub> = V <sub>CC</sub> or GND                                                                                                                                                   | -1.5                                           |                   | +1.5                  | μΑ   |       |

| F-V <sub>CC</sub>                                                                                                                             | Standby Current                                                      | I <sub>ccs</sub>                       | $F-\overline{CE} = F-\overline{RP} = F-V_{CC} \pm 0.2 \text{ V}$ $F-\overline{WP} = F-V_{CC} \pm 0.2 \text{ V}$ or F-GND \pm 0.2 V                                                          | $F-\overline{WP} = F-V_{CC} \pm 0.2 \text{ V}$ |                   | 50                    | μΑ   | 2     |

|                                                                                                                                               |                                                                      |                                        | $F-\overline{CE} = F-\overline{RP} = V_{IH}, F-\overline{WP} = V_{IH} \text{ or } V_{IL}$                                                                                                   |                                                | 0.2               | 2                     | mA   |       |

|                                                                                                                                               | Deep Power-Down Current                                              | I <sub>CCD</sub>                       | $F-\overline{RP} = F-GND \pm 0.2 \text{ V},$<br>$I_{OUT} (F-RY/\overline{BY}) = 0 \text{ mA}$                                                                                               |                                                | 5                 | 10                    | μΑ   |       |

| ,                                                                                                                                             | Read Current                                                         | I <sub>CCR</sub>                       | CMOS input, F- $\overline{CE}$ = F-GND,<br>f = 5 MHz, I <sub>OUT</sub> = 0 mA                                                                                                               |                                                |                   | 25                    | mA   | 3, 4  |

| F-V <sub>CC</sub>                                                                                                                             | Thead Guillett                                                       | CCR                                    | TTL input, $F \cdot \overline{CE} = F \cdot GND$ ,<br>f = 5 MHz, $I_{OUT} = 0$ mA                                                                                                           |                                                |                   | 30                    | mA   | 3, 4  |

|                                                                                                                                               | Word Write Current                                                   | I <sub>CCW</sub>                       | F-V <sub>PP</sub> = 2.7 V to 3.6 V                                                                                                                                                          |                                                |                   | 17                    | mA   |       |

|                                                                                                                                               | Trefa Trine Garrent                                                  | ·CCW                                   | F-V <sub>PP</sub> = 11.4 V to 12.6 V                                                                                                                                                        |                                                |                   | 12                    | mA   |       |

|                                                                                                                                               | Block Erase Current                                                  | I <sub>CCE</sub>                       | $F-V_{PP} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                                                                                                |                                                |                   | 17                    | mA   |       |

|                                                                                                                                               | Block Erase Garrent                                                  | ICCE                                   | F-V <sub>PP</sub> = 11.4 V to 12.6 V                                                                                                                                                        |                                                |                   | 12                    | mA   |       |

| F-V <sub>CC</sub> Input LO Input HIC Output H F-V <sub>PP</sub> LC F-V <sub>PP</sub> W Operatio F-V <sub>CC</sub> LC                          | Word Write Block Erase<br>Suspend Current                            | I <sub>CCWS</sub>                      | F-CE = V <sub>IH</sub>                                                                                                                                                                      |                                                |                   | 6                     | mA   |       |

|                                                                                                                                               | Standby or Read Current                                              | I <sub>PPS</sub>                       | $F-V_{PP} = F-V_{CC}$                                                                                                                                                                       |                                                | ±2                | ±15                   | μΑ   |       |

| F-V <sub>PP</sub>                                                                                                                             | Standby of Head Current                                              | I <sub>PPR</sub>                       | F-V <sub>PP</sub> > F-V <sub>CC</sub>                                                                                                                                                       |                                                | 10                | 200                   | μΑ   |       |

|                                                                                                                                               | Deep Power-Down Current                                              | I <sub>PPD</sub>                       | $F-\overline{RP} = F-GND \pm 0.2 V$                                                                                                                                                         |                                                | 0.1               | 5                     | μΑ   |       |

| F-V <sub>PP</sub>                                                                                                                             | Word Write Current                                                   | 1                                      | F-V <sub>PP</sub> = 2.7 V to 3.6 V                                                                                                                                                          |                                                | 12                | 40                    | mA   |       |

| F-V <sub>PP</sub>                                                                                                                             | Word Write Gurrent                                                   | I <sub>PPW</sub>                       | F-V <sub>PP</sub> = 11.4 V to 12.6 V                                                                                                                                                        |                                                |                   | 30                    | mA   |       |

| F-V <sub>CC</sub>                                                                                                                             | Block Erase Current                                                  | I                                      | $F-V_{PP} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                                                                                                |                                                | 8                 | 25                    | mA   |       |

|                                                                                                                                               | Block Liase Guilent                                                  | I <sub>PPE</sub>                       | F-V <sub>PP</sub> = 11.4 V to 12.6 V                                                                                                                                                        |                                                |                   | 20                    | mA   |       |

| F-V <sub>CC</sub> F-V <sub>PP</sub> Input LO  Input HIC  Output H  F-V <sub>PP</sub> LC  F-V <sub>PP</sub> W  Operation  F-V <sub>CC</sub> LC | Word Write or Block Erase<br>Suspend Current                         | I <sub>PPWS</sub><br>I <sub>PPES</sub> | F-V <sub>PP</sub> = V <sub>PPH</sub>                                                                                                                                                        |                                                | 10                | 200                   | μΑ   |       |

|                                                                                                                                               | Standby Current                                                      | I <sub>SB</sub>                        | $S-\overline{CE}_1$ , $S-CE_2 \ge S-V_{CC} - 0.2 V$<br>or $S-CE_2 \le 0.2 V$                                                                                                                |                                                |                   | 45                    | μΑ   |       |

|                                                                                                                                               |                                                                      | I <sub>SB1</sub>                       | $S-\overline{CE}_1 = V_{IH} \text{ or } S-CE_2 = V_{IL}$                                                                                                                                    |                                                |                   | 3                     | mA   |       |

| S-V <sub>CC</sub>                                                                                                                             |                                                                      | I <sub>CC1</sub>                       | $S-\overline{CE}_1 = V_{IL}, S-CE_2 = V_{IH}, V_{IN} = V_{IL} \text{ or } V_{IH}, t_{CYCLE} = MIN., I_{I/O} = 0 \text{ mA}$                                                                 |                                                |                   | 45                    | mA   |       |

|                                                                                                                                               | Operation Current                                                    | I <sub>CC2</sub>                       | $S-\overline{CE}_1 = 0.2 \text{ V}, S-CE_2 = S-V_{CC}-0.2 \text{ V}, \ V_{IN} = S-V_{CC}-0.2 \text{ V}, \text{ or } 0.2 \text{ V} \ t_{CYCLE} = 1 \ \mu\text{s}, \ I_{I/O} = 0 \ \text{mA}$ |                                                |                   | 8                     | mA   |       |

| Input Lo                                                                                                                                      | OW Voltage                                                           | V <sub>IL</sub>                        |                                                                                                                                                                                             | -0.2                                           |                   | 0.6                   | V    |       |

| Input H                                                                                                                                       | IGH Voltage                                                          | V <sub>IH</sub>                        |                                                                                                                                                                                             | 2.2                                            |                   | V <sub>CC</sub> + 0.2 | V    |       |

| Output                                                                                                                                        | LOW Voltage                                                          | V <sub>OL</sub>                        | I <sub>OL</sub> = 0.5 mA                                                                                                                                                                    |                                                |                   | 0.4                   | V    | 2     |

|                                                                                                                                               |                                                                      | V <sub>OH1</sub>                       | I <sub>OH</sub> = -0.5 mA                                                                                                                                                                   | 2.2                                            |                   |                       | V    | 2     |

| F-V <sub>PP</sub> L                                                                                                                           | F-V <sub>PP</sub> Lockout during Normal Operations V <sub>PPLK</sub> |                                        |                                                                                                                                                                                             |                                                |                   | 1.5                   | V    | 5     |

| F-V <sub>PP</sub> \                                                                                                                           | Word Write or Block Erase                                            | V <sub>PPH1</sub>                      |                                                                                                                                                                                             | 2.7                                            |                   | 3.6                   | V    |       |

| Operati                                                                                                                                       | ons                                                                  | V <sub>PPH2</sub>                      |                                                                                                                                                                                             | 11.4                                           |                   | 12.6                  | ٧    |       |

| F-V <sub>CC</sub> I                                                                                                                           | Lockout Voltage                                                      | $V_{LKO}$                              |                                                                                                                                                                                             | 1.5                                            |                   |                       | V    |       |

| F-RP U                                                                                                                                        | Inlock Voltage                                                       | V <sub>HH</sub>                        | Unavailable F-WP                                                                                                                                                                            | 11.4                                           |                   | 12.6                  | V    | 6     |

### NOTES:

- 1. Reference values at  $V_{CC}$  = 3.0 V and  $T_A$  = +25°C.

- 2. Includes F-RY/ $\overline{BY}$ .

- 3. Automatic Power Savings (APS) for Flash Memory reduces typi-

- cal I<sub>CCR</sub> to 3 mA at 2.7 V<sub>CC</sub> in static operation. 4. CMOS inputs are either V<sub>CC</sub>  $\pm$  0.2 V or GND  $\pm$  0.2 V. TTL inputs are either  $V_{\text{IL}}$  or  $V_{\text{IH}}$ .

- 5. Block erases and word writes are inhibited when F-V<sub>PP</sub>  $\leq$ V<sub>PPLK</sub> and not guaranteed in the range between  $V_{\mbox{\footnotesize{PPLK}}}$  (MAX.) and  $V_{\mbox{\footnotesize{PPH}}}$ (MIN.), and above  $V_{\mbox{\footnotesize{PPH}}}$  (MAX.).

- 6.  $F-\overline{RP}$  connection to a  $V_{HH}$  supply is allowed for a maximum cumulative period of 80 hours.

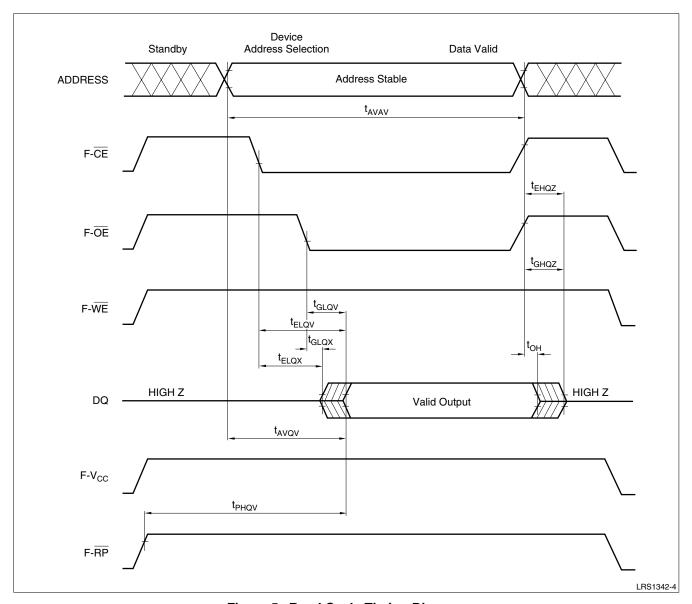

# FLASH MEMORY AC CHARACTERISTICS

# **AC Test Conditions**

| PARAMETER                               | CONDITION                     |

|-----------------------------------------|-------------------------------|

| Input pulse level                       | 0 V to 2.7 V                  |

| Input rise and fall time                | 10 ns                         |

| Input and Output timing reference level | 1.35 V                        |

| Output load                             | 1TTL + C <sub>L</sub> (30 pF) |

# **Read Cycle**

$T_A = -25^{\circ}C$  to +85°C,  $V_{CC} = 2.7 \text{ V}$  to 3.6 V

| PARAMETER                                                             | SYMBOL            | MIN. | MAX. | UNIT |

|-----------------------------------------------------------------------|-------------------|------|------|------|

| Read Cycle Time                                                       | t <sub>AVAV</sub> | 100  |      | ns   |

| Address to Output Delay                                               | t <sub>AVQV</sub> |      | 100  | ns   |

| F-CE to Output Delay*                                                 | t <sub>ELQV</sub> |      | 100  | ns   |

| F-RP HIGH to Output Delay                                             | t <sub>PHQV</sub> |      | 10   | μs   |

| F-OE to Output Delay*                                                 | t <sub>GLQV</sub> |      | 45   | ns   |

| F-CE to Output in LOW-Z                                               | t <sub>ELQX</sub> | 0    |      | ns   |

| F-CE HIGH to Output in HIGH-Z                                         | t <sub>EHQZ</sub> |      | 45   | ns   |

| F-OE to Output in LOW Z                                               | t <sub>GLQX</sub> | 0    |      | ns   |

| F-OE HIGH to Output in HIGH-Z                                         | t <sub>GHQZ</sub> |      | 20   | ns   |

| Output Hold from Address, F-CE or F-OE change, whichever occurs first | t <sub>ОН</sub>   | 0    |      | ns   |

$\textbf{NOTE: } ^{\star} \textbf{F-} \overline{\textbf{OE}} \text{ may be delayed up to } \textbf{t}_{\text{ELQV}} \textbf{-} \textbf{t}_{\text{GLQV}} \text{ after the falling edge of } \textbf{F-} \overline{\textbf{CE}} \text{ without impact on } \textbf{t}_{\text{ELQV}}.$

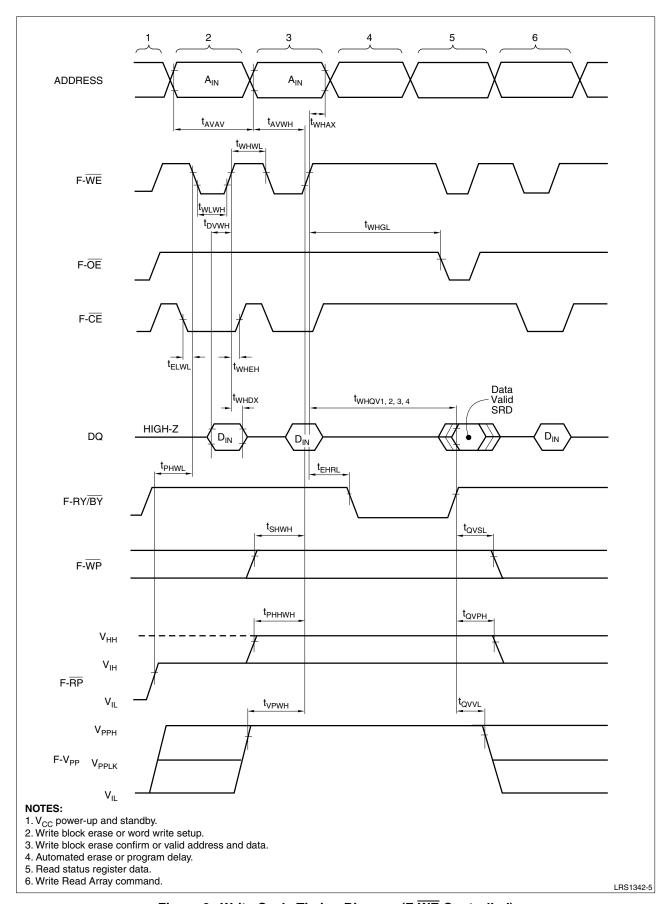

# Write Cycle (F-WE Controlled)<sup>1</sup>

$T_A = -25$ °C to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| PARAMETER                                                | SYMBOL             | MIN. | MAX. | UNIT |

|----------------------------------------------------------|--------------------|------|------|------|

| Write Cycle Time                                         | t <sub>AVAV</sub>  | 100  |      | ns   |

| F-RP HIGH Recovery to F-WE going to LOW                  | t <sub>PHWL</sub>  | 10   |      | μs   |

| F-CE Setup to F-WE going LOW                             | t <sub>ELWL</sub>  | 0    |      | ns   |

| F-WE Pulse Width                                         | t <sub>WLWH</sub>  | 50   |      | ns   |

| F-RP V <sub>HH</sub> Setup to F-WE going HIGH            | t <sub>PHHWH</sub> | 100  |      | ns   |

| F-WP V <sub>IH</sub> Setup to F-WE going HIGH            | t <sub>SHWH</sub>  | 100  |      | ns   |

| F-V <sub>PP</sub> Setup to F-WE going HIGH               | t <sub>VPWH</sub>  | 100  |      | ns   |

| Address Setup to F-WE going HIGH <sup>2</sup>            | t <sub>AVWH</sub>  | 50   |      | ns   |

| Data Setup to F-WE going HIGH <sup>2</sup>               | t <sub>DVWH</sub>  | 50   |      | ns   |

| Data Hold from F-WE HIGH                                 | t <sub>WHDX</sub>  | 0    |      | ns   |

| Address Hold from F-WE HIGH                              | t <sub>WHAX</sub>  | 0    |      | ns   |

| F-CE Hold from F-WE HIGH                                 | t <sub>WHEH</sub>  | 0    |      | ns   |

| F-WE Pulse Width HIGH                                    | t <sub>WHWL</sub>  | 30   |      | ns   |

| F-WE HIGH to F-RY/BY going LOW                           | t <sub>WHRL</sub>  |      | 100  | ns   |

| Write Recovery before Read                               | t <sub>WHGL</sub>  | 0    |      | ns   |

| F-V <sub>PP</sub> Hold from Valid SRD, F-RY/BY HIGH-Z    | t <sub>QVVL</sub>  | 0    |      | ns   |

| F-RP V <sub>HH</sub> Hold from Valid SRD, F-RY/BY HIGH-Z | t <sub>QVPH</sub>  | 0    |      | ns   |

| F-WP V <sub>IH</sub> Hold from Valid SRD, F-RY/BY HIGH   | t <sub>QVSL</sub>  | 0    |      | ns   |

### NOTES:

Read timing characteristics during block erase and word write operations are the same as during read-only operations. Refer to AC Characteristics for Read Cycle.

<sup>2.</sup> Refer to the 'Flash Memory Command Definition' section for valid  $A_{\text{IN}}$  and  $D_{\text{IN}}$  for block erase or word write.

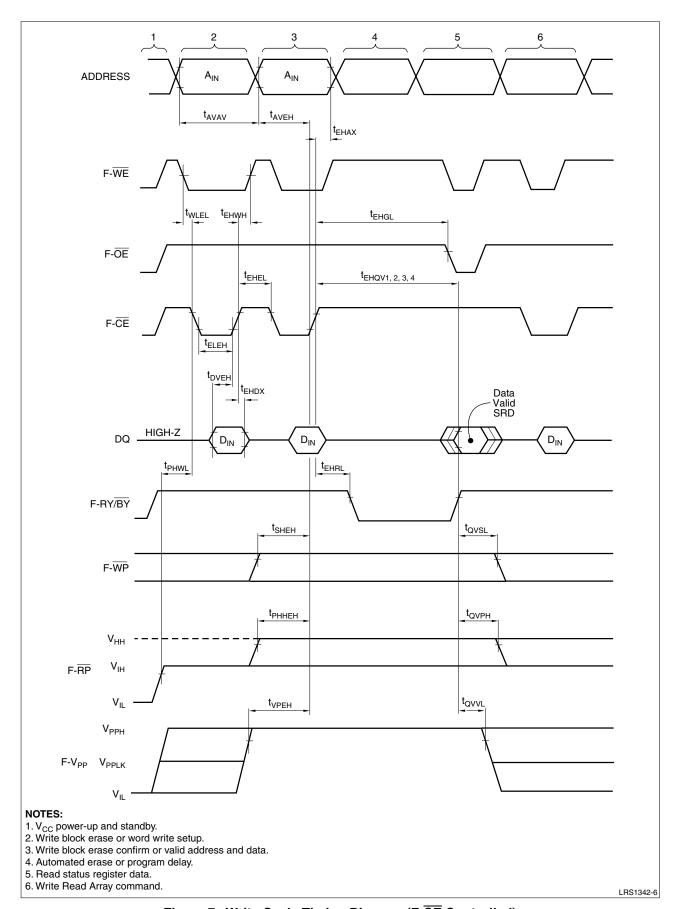

# Write Cycle (F-CE Controlled)<sup>1</sup>

$T_A = -25^{\circ}C$  to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| PARAMETER                                                | SYMBOL            | MIN. | MAX. | UNIT |

|----------------------------------------------------------|-------------------|------|------|------|

| Write Cycle Time                                         | t <sub>AVAV</sub> | 100  |      | ns   |

| F-RP HIGH Recovery to F-CE going to LOW                  | t <sub>PHEL</sub> | 10   |      | μs   |

| F-WE Setup to F-CE going LOW                             | t <sub>WLEL</sub> | 0    |      | ns   |

| F-CE Pulse Width                                         | t <sub>ELEH</sub> | 70   |      | ns   |

| F-RP V <sub>HH</sub> Setup to F-CE going HIGH            | t <sub>PHEH</sub> | 100  |      | ns   |

| F-WP V <sub>IH</sub> Setup to F-CE going HIGH            | t <sub>SHEH</sub> | 100  |      | ns   |

| F-V <sub>PP</sub> Setup to F-CE going HIGH               | t <sub>VPEH</sub> | 100  |      | ns   |

| Address Setup to F-CE going HIGH <sup>2</sup>            | t <sub>AVEH</sub> | 50   |      | ns   |

| Data Setup to F-CE going HIGH <sup>2</sup>               | t <sub>DVEH</sub> | 50   |      | ns   |

| Data Hold from F-CE HIGH                                 | t <sub>EHDX</sub> | 0    |      | ns   |

| Address Hold from F-CE HIGH                              | t <sub>EHAX</sub> | 0    |      | ns   |

| F-WE Hold from F-CE HIGH                                 | t <sub>EHWH</sub> | 0    |      | ns   |

| F-CE Pulse Width HIGH                                    | t <sub>EHEL</sub> | 25   |      | ns   |

| F-CE HIGH to F-RY/BY going LOW                           | t <sub>EHRL</sub> |      | 100  | ns   |

| Write Recovery before Read                               | t <sub>EHGL</sub> | 0    |      | ns   |

| F-V <sub>PP</sub> Hold from Valid SRD, F-RY/BY HIGH-Z    | t <sub>QVVL</sub> | 0    |      | ns   |

| F-RP V <sub>HH</sub> Hold from Valid SRD, F-RY/BY HIGH-Z | t <sub>QVPH</sub> | 0    |      | ns   |

| F-WP V <sub>IH</sub> Hold from Valid SRD, F-RY/BY HIGH   | t <sub>QVSL</sub> | 0    |      | ns   |

### NOTES:

- Read timing characteristics during block erase and word write operations are the same as during read-only operations. Refer to AC Characteristics for Read Cycle.

- 2. Refer to the 'Flash Memory Command Definition' section for valid  $A_{\text{IN}}$  and  $D_{\text{IN}}$  for block erase or word write.

# **Block Erase and Word Write Performance**

$T_A = -25$ °C to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| SYMBOL                                   | PARAMETER                               | V <sub>PP</sub> = 2 |                   | V <sub>PP</sub> = 2.7 V to 3.6 V |      | V <sub>PP</sub> = 11.4 V to 12.6 V |      |      | NOTES  |

|------------------------------------------|-----------------------------------------|---------------------|-------------------|----------------------------------|------|------------------------------------|------|------|--------|

| STWIBOL                                  | FANAMETEN                               | MIN.                | TYP. <sup>1</sup> | MAX.                             | MIN. | TYP. <sup>1</sup>                  | MAX. | UNIT | 110120 |

| t <sub>WHQV1</sub>                       | Word Write Time 32K-word Block          |                     | 55                |                                  |      | 15                                 |      | μs   | 2      |

| t <sub>EHQV1</sub>                       | Word Write Time 4K-word Block           |                     | 60                |                                  |      | 30                                 |      | μs   | 2      |

|                                          | Block Write Time 32K-word Block         |                     | 1.8               |                                  |      | 0.6                                |      | S    | 2      |

|                                          | Block Write Time 4K-word Block          |                     | 0.3               |                                  |      | 0.2                                |      | S    | 2      |

| t <sub>WHQV2</sub>                       | Block Erase Time 32K-word Block         |                     | 1.2               |                                  |      | 0.7                                |      | S    | 2      |

| t <sub>EHQV2</sub>                       | Block Erase Time 4K-word Bock           |                     | 0.5               |                                  |      | 0.5                                |      | S    | 2      |

| t <sub>WHRZ1</sub>                       | Word Write Suspend Latency Time to Read |                     | 7.5               | 8.6                              |      | 6.5                                | 7.5  | μs   |        |

| t <sub>WHRZ2</sub><br>t <sub>EHRZ2</sub> | Erase Suspend Latency Time to Read      |                     | 19.3              | 23.6                             |      | 11.8                               | 15   | μs   |        |

### NOTES:

- 1. Reference values at  $T_A$  = +25°C and  $V_{CC}$  = 3.0 V,  $V_{PP}$  = 3.0 V.

- 2. Excludes system-level overhead.

# FLASH MEMORY AC CHARACTERISTICS TIMING DIAGRAMS

Figure 5. Read Cycle Timing Diagram

Figure 6. Write Cycle Timing Diagram (F-WE Controlled)

Figure 7. Write Cycle Timing Diagram (F-CE Controlled)

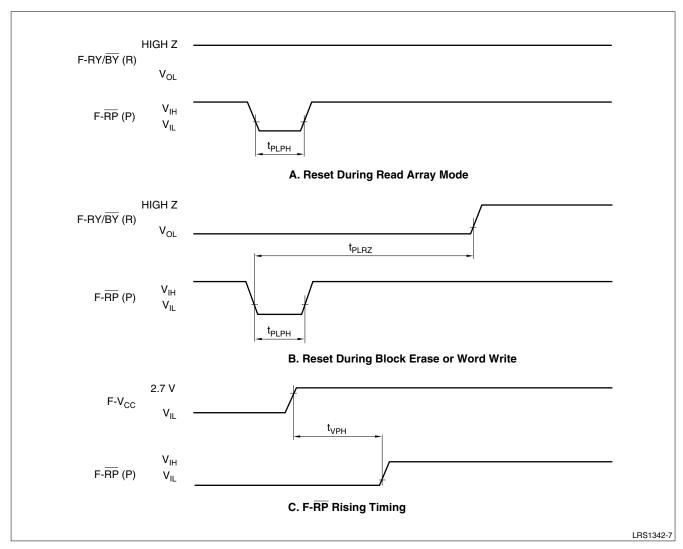

# **RESET OPERATIONS**

$T_A = -25$ °C to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| PARAMETER                                                                                                                         | SYMBOL            | MIN. | MAX. | UNIT | NOTES |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|-------|

| $\overline{\text{F-RP}}$ Pulse LOW Time (if $\overline{\text{F-RP}}$ is tied to $V_{CC}$ , this specification is not applicable). | t <sub>PLPH</sub> | 100  |      | ns   |       |

| F-RP LOW to Reset during Block Erase or Word Write                                                                                | t <sub>PLRZ</sub> |      | 23.6 | μs   | 1, 2  |

| F-V <sub>CC</sub> 2.7 V to F-RP HIGH                                                                                              | t <sub>VPH</sub>  | 100  |      | ns   | 3     |

### NOTES:

- If F-RP is asserted while a block erase or word write operation is not executing, the reset will complete with 100 ns.

- 2. A reset time  $t_{PHQV}$  is required from the later of F-RY/ $\overline{BY}$  going HIGH-Z, or F- $\overline{RP}$  going HIGH until outputs are valid.

- When the device power-up, holding F-RP LOW minimum 100 ns is required after V<sub>CC</sub> has been in predefined range and also has been stable there.

Figure 8. AC Waveform for Reset Operation

# SRAM AC ELECTRICAL CHARACTERISTICS AC Test Conditions

| PARAMETER                               | CONDITION                     |

|-----------------------------------------|-------------------------------|

| Input Pulse Level                       | 0.4 V to 2.7 V                |

| Input Rise and Fall Time                | 5 ns                          |

| Input and Output Timing Reference Level | 1.5 V                         |

| Output Load*                            | 1TTL + C <sub>L</sub> (30 pF) |

NOTE: \*Including scope and jig capacitance.

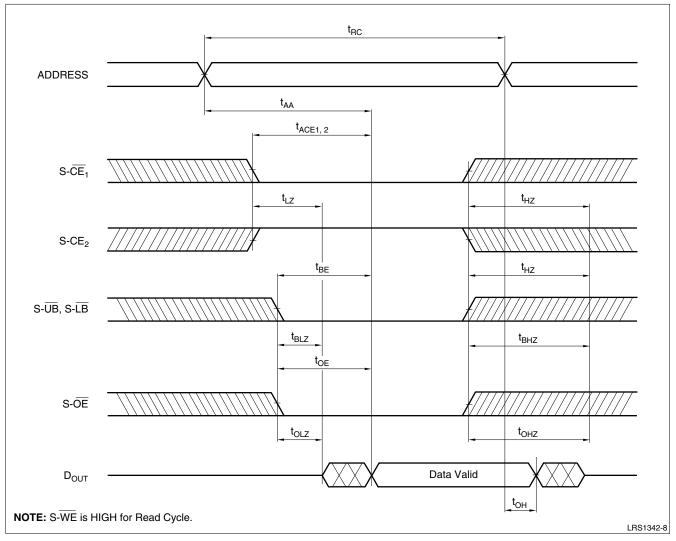

# **Read Cycle**

$T_A = -25$ °C to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| PARAMETER                                                                   |                   | SYMBOL            | MIN.                                                                                                                                                                                                                    | MAX. | UNIT |

|-----------------------------------------------------------------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Read Cycle Time                                                             |                   | t <sub>RC</sub>   | 85                                                                                                                                                                                                                      |      | ns   |

| Address Access Time                                                         |                   | t <sub>AA</sub>   |                                                                                                                                                                                                                         | 85   | ns   |

| Chin Enghla Aggass Time                                                     | S-CE <sub>1</sub> | t <sub>ACE1</sub> |                                                                                                                                                                                                                         | 85   | ns   |

| Chip Enable Access Time                                                     | S-CE <sub>2</sub> | t <sub>ACE2</sub> | t <sub>RC</sub> 85 t <sub>AA</sub> 85 ACE1 85 ACE2 85 t <sub>BE</sub> 85 t <sub>OE</sub> 45 t <sub>LZ1</sub> 10 t <sub>LZ2</sub> 10 t <sub>OLZ</sub> 10 t <sub>BLZ</sub> 10 t <sub>HZ1</sub> 0 25 t <sub>HZ1</sub> 0 25 | 85   | ns   |

| Byte Enable Access Time                                                     |                   | t <sub>BE</sub>   |                                                                                                                                                                                                                         | 85   | ns   |

| Output Enable to Output Valid                                               |                   | t <sub>OE</sub>   |                                                                                                                                                                                                                         | 45   | ns   |

| Output hold from address change                                             |                   | t <sub>OH</sub>   | 10                                                                                                                                                                                                                      |      | ns   |

| S-CE <sub>1</sub> , S-CE <sub>2</sub> LOW to Output Active*                 | S-CE <sub>1</sub> | t <sub>LZ1</sub>  | 10                                                                                                                                                                                                                      |      | ns   |

| 3-OE <sub>1</sub> , 3-OE <sub>2</sub> LOW to Output Active                  | S-CE <sub>2</sub> | t <sub>LZ2</sub>  | 10                                                                                                                                                                                                                      |      | ns   |

| S-OE LOW to Output Active*                                                  |                   | t <sub>OLZ</sub>  | 10                                                                                                                                                                                                                      |      | ns   |

| S-UB or S-LB LOW to Output in HIGH Impedance*                               |                   | t <sub>BLZ</sub>  | 10                                                                                                                                                                                                                      |      | ns   |

| S-CE <sub>1</sub> , S-CE <sub>2</sub> HIGH to Output in HIGH Impedance*     | S-CE <sub>1</sub> | t <sub>HZ1</sub>  | 0                                                                                                                                                                                                                       | 25   | ns   |

| 5-0E <sub>1</sub> , 5-0E <sub>2</sub> fild fill output in fild fill pedance | S-CE <sub>2</sub> | t <sub>HZ2</sub>  | 0                                                                                                                                                                                                                       | 25   | ns   |

| S-OE HIGH to Output in HIGH Impedance*                                      |                   | t <sub>OHZ</sub>  | 0                                                                                                                                                                                                                       | 25   | ns   |

| S-UB or S-LB HIGH to Output in HIGH Impedance*                              |                   | t <sub>BHZ</sub>  | 0                                                                                                                                                                                                                       | 25   | ns   |

**NOTE:** \*Active output to HIGH impedance and HIGH impedance to output active tests specified for a ±200 mV transition from steady state levels into the test load.

# **Write Cycle**

$T_A = -25^{\circ}C$  to +85°C,  $V_{CC} = 2.7$  V to 3.6 V

| PARAMETER                             | SYMBOL          | MIN. | MAX. | UNIT |

|---------------------------------------|-----------------|------|------|------|

| Write Cycle Time                      | t <sub>WC</sub> | 85   |      | ns   |

| Chip Enable to End of Write           | t <sub>CW</sub> | 75   |      | ns   |

| Address Valid to End of Write         | t <sub>AW</sub> | 75   |      | ns   |

| Byte Enable to End of Write           | t <sub>BW</sub> | 75   |      | ns   |

| Address Setup Time                    | t <sub>AS</sub> | 0    |      | ns   |

| Write Pulse Width                     | t <sub>WP</sub> | 65   |      | ns   |

| Write Recovery Time                   | t <sub>WR</sub> | 0    |      | ns   |

| Input Data Setup Time                 | t <sub>DW</sub> | 35   |      | ns   |

| Input Data Hold Time                  | t <sub>DH</sub> | 0    |      | ns   |

| S-WE HIGH to Output Active*           | t <sub>OW</sub> | 5    |      | ns   |

| S-WE LOW to Output in HIGH Impedance* | t <sub>WZ</sub> | 0    | 25   | ns   |

**NOTE:** \*Active output to HIGH impedance and HIGH impedance to output active tests specified for a ±200 mV transition from steady state levels into the test load.

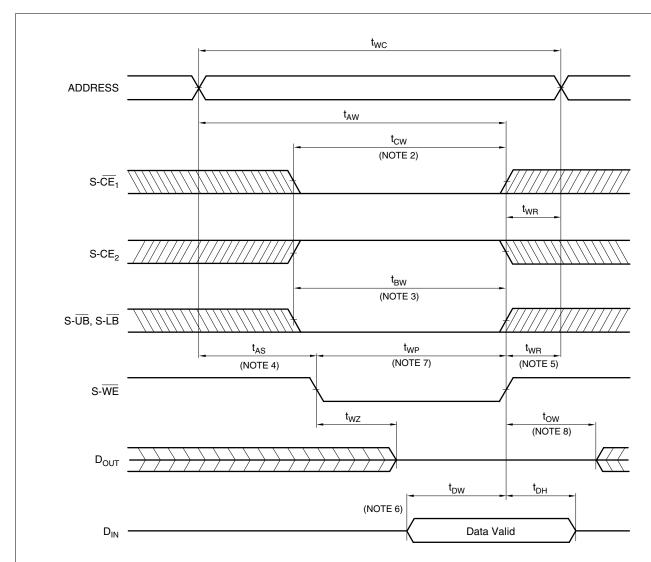

# **SRAM AC CHARACTERISTICS TIMING DIAGRAMS**

Figure 9. Read Cycle Timing Diagram

LRS1342-9

### NOTES:

- 1. A write occurs during the overlap of a LOW S-CE<sub>1</sub>, a HIGH S-CE<sub>2</sub> and a LOW S-WE. A write begins at the latest transition among S-CE<sub>1</sub> going LOW, S-CE<sub>2</sub> going HIGH and S-WE going LOW. A write ends at the earliest transition among S-CE<sub>1</sub> going HIGH, S-CE<sub>2</sub> going LOW and S-WE going HIGH. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 2. t<sub>CW</sub> is measured from the later of S- $\overline{\text{CE}}_1$  going LOW or S-CE<sub>2</sub> going HIGH to the end of write

- 3.  $t_{BW}$  is measured from the time of going LOW S- $\overline{\text{UB}}$  or LOW S- $\overline{\text{LB}}$  to the end of write.

- 4.  $t_{\mbox{\scriptsize AS}}$  is measured from the address valid to the beginning of write.

- 5.  $t_{WR}$  is measured from the end of write to the address change.

- During this period, DQ pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- 7. If S-CE<sub>1</sub> goes LOW or S-CE<sub>2</sub> goes HIGH simultaneously with S-WE going LOW or after S-WE going LOW, the outputs remain in HIGH impedance state.

- 8. If  $S-\overline{CE}_1$  goes HIGH or  $S-\overline{CE}_2$  goes LOW simultaneously with  $S-\overline{WE}$  going HIGH or  $S-\overline{WE}$  going HIGH, the outputs remain in HIGH impedance state.

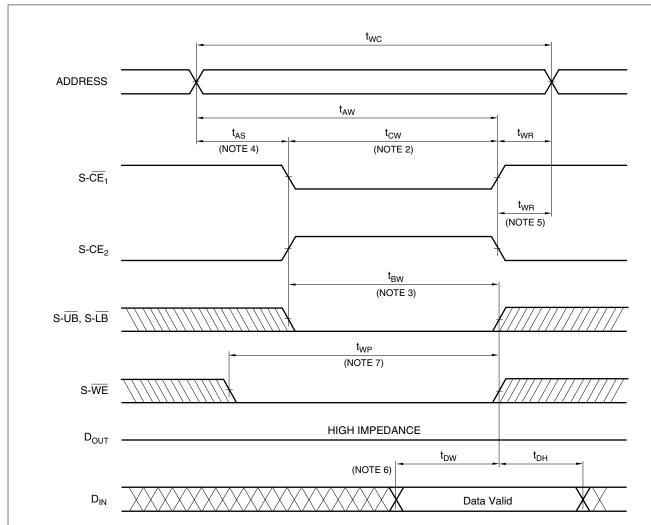

Figure 10. Write Cycle Timing Diagram (S-WE Controlled)

### NOTES:

- 1. A write occurs during the overlap of a LOW S-CE<sub>1</sub>, a HIGH S-CE<sub>2</sub> and a LOW S-WE. A write begins at the latest transition among S-CE<sub>1</sub> going LOW, S-CE<sub>2</sub> going HIGH and S-WE going LOW. A write ends at the earliest transition among S-CE<sub>1</sub> going HIGH, S-CE<sub>2</sub> going LOW and S-WE going HIGH. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 2.  $t_{CW}$  is measured from the later of S- $\overline{CE}_1$  going LOW or S- $CE_2$  going HIGH to the end of write.

- 3.  $t_{BW}$  is measured from the time of going LOW S- $\overline{\text{UB}}$  or LOW S- $\overline{\text{LB}}$  to the end of write.

- 4.  $t_{\mbox{\scriptsize AS}}$  is measured from the address valid to the beginning of write.

- 5.  $t_{\mbox{\scriptsize WR}}$  is measured from the end of write to the address change.

- 6. During this period, DQ pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- 7. If  $S-\overline{CE}_1$  goes LOW or  $S-\overline{CE}_2$  goes HIGH simultaneously with  $S-\overline{WE}$  going LOW or after  $S-\overline{WE}$  going LOW, the outputs remain in HIGH impedance state.

LRS1342-10

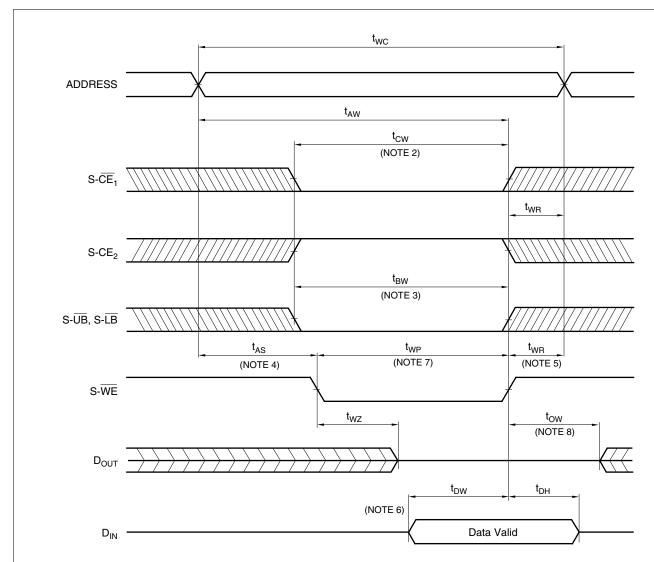

Figure 11. Write Cycle Timing Diagram (S-CE Controlled)

### NOTES:

- 1. A write occurs during the overlap of a LOW S-\overline{CE}\_1, a HIGH S-CE\_2 and a LOW S-\overline{WE}. A write begins at the latest transition among S-\overline{CE}\_1 going LOW, S-CE\_2 going HIGH and S-\overline{WE} going LOW. A write ends at the earliest transition among S-\overline{CE}\_1 going HIGH, S-CE\_2 going LOW and S-\overline{WE} going HIGH. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 2. t<sub>CW</sub> is measured from the later of S- $\overline{\text{CE}}_1$  going LOW or S-CE<sub>2</sub> going HIGH to the end of write

- 3.  $t_{BW}$  is measured from the time of going LOW S- $\overline{\text{UB}}$  or LOW S- $\overline{\text{LB}}$  to the end of write.

- 4. t<sub>AS</sub> is measured from the address valid to the beginning of write.

- 5. t<sub>WR</sub> is measured from the end of write to the address change.

- During this period, DQ pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- 7. If S-\overline{\overline{\text{CE}}\_1} goes LOW or S-CE<sub>2</sub> goes HIGH simultaneously with S-\overline{\text{WE}} going LOW or after S-\overline{\text{WE}} going LOW, the outputs remain in HIGH impedance state.

- If S-OE<sub>1</sub> goes HIGH or S-CE<sub>2</sub> goes LOW simultaneously with S-WE going HIGH or S-WE going HIGH, the outputs remain in HIGH impedance state.

LRS1342-11

Figure 12. Write Cycle Timing (S-UB, S-LB Controlled)

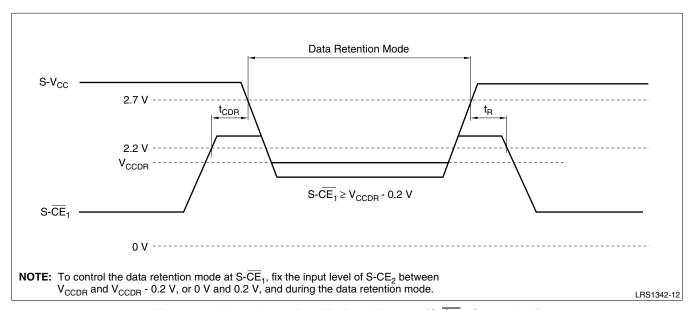

### SRAM DATA RETENTION CHARACTERISTICS

$T_A = -25^{\circ}C \text{ to } +85^{\circ}C$

| PARAMETER                     | SYMBOL            | CONDITIONS                                                                                     | MIN. | TYP. <sup>1</sup> | MAX. | UNIT | NOTES |

|-------------------------------|-------------------|------------------------------------------------------------------------------------------------|------|-------------------|------|------|-------|

| Data Retention Supply Voltage | V <sub>CCDR</sub> | $S-CE_2 \le 0.2 \text{ V or}$<br>$S-\overline{CE}_1 \ge V_{CCDR} - 0.2 \text{ V}$              | 2.0  |                   | 3.6  | V    | 2     |

| Data Retention Supply Current | I <sub>CCDR</sub> | $V_{CCDR} = 3V$ , S-CE <sub>2</sub> $\leq$ 0.2 V or S- $\overline{CE}_1 \geq V_{CCDR} - 0.2 V$ |      |                   | 35   | μΑ   | 2     |

| Chip Enable Setup Time        | t <sub>CDR</sub>  |                                                                                                | 0    |                   |      | ns   |       |

| Chip Enable Hold Time         | t <sub>R</sub>    |                                                                                                | 5    |                   |      | ms   |       |

### NOTES:

- 1. Reference value at  $T_A$  = 25°C, S-V<sub>CC</sub> = 3.0 V. 2. S- $\overline{\text{CE}}_1 \ge \text{V}_{\text{CC}}$  0.2 V, S-CE<sub>2</sub>  $\ge \text{V}_{\text{CC}}$  0.2 V (S- $\overline{\text{CE}}_1$  controlled) or S-CE<sub>2</sub>  $\le$ 0.2 V (S-CE<sub>2</sub> controlled).

Figure 13. Data Retention Timing Diagram (S-\overline{CE}\_1 Controlled)

Figure 14. Data Retention Timing Diagram (S-CE<sub>2</sub> Controlled)

# **GENERAL DESIGN GUIDELINES**

# **Supply Power**

Maximum difference (between F-V $_{CC}$  and S-V $_{CC}$ ) of the voltage is less than 0.3 V.

# Power Supply and Chip Enable of Flash Memory and SRAM

$S-\overline{CE}_1$  should not be LOW and  $S-\overline{CE}_2$  should not be HIGH when  $F-\overline{CE}$  is LOW simultaneously.

If the two memories are active together, they may not operate normally because of interference noises or data collision on DQ bus.

Both F-V<sub>CC</sub> and S-V<sub>CC</sub> need to be applied by the recommended supply voltage at the same time except SRAM data retention mode.

# **Power Up Sequence**

When turning on Flash memory power supply, keep F-RP LOW. After F-V<sub>CC</sub> reaches over 2.7 V, keep F-RP LOW for more than 100 ns.

# **Device Decoupling**

The power supply needs to be designed carefully because one of the SRAM and the Flash Memory is in standby mode when the other is active. A careful decoupling of power supplies is necessary between SRAM and Flash Memory. Note peak current caused by transition of control signals (F-CE, S-CE<sub>1</sub>, S-CE<sub>2</sub>).

### FLASH MEMORY DATA PROTECTION

Noises having a level exceeding the limit specified in the specification may be generated under specific operating conditions on some systems.

Such noises, when induced onto F-WE signal or power supply may be interpreted as false commands, causing undesired memory updating.

To protect the data stored in the flash memory against unwanted overwriting, systems operating with the flash memory should have the following write protect designs, as appropriate:

### **Protecting Data in Specific Block**

By setting a F-WP to LOW, only the boot block can be protected against overwriting. Parameter and main blocks cannot be locked. System program, etc., can be locked by storing them in the boot block. When a high voltage is applied to F-RP, overwrite operation is enabled for all blocks.

For further information on setting/resetting of block bit, and controlling of F-WP and F-RP, refer to the 'Command Definitions' section.

# Data Protection Through F-V<sub>PP</sub>

When the level of F-V<sub>PP</sub> is lower than F-V<sub>PPLK</sub> (lockout voltage), write operation on the flash memory is disabled. All blocks are locked and the data in the blocks are completely write protected.

For the lockout voltage refer to the 'DC Characteristics' section.

# Data Protection During Voltage Transition DATA PROTECTION THROUGH F-RP

When the F-RP is kept LOW during power up and power down sequence, write operation on the flash memory is disabled, write protecting all blocks.

For details of F-RP control refer to the 'Flash Memory AC Electrical Characteristics' section.

# **DESIGN CONSIDERATIONS**

# **Power Supply Decoupling**

To avoid a bad effect on the system by flash memory power switching characteristics, each device should have a 0.1  $\mu F$  ceramic capacitor connected between its  $V_{CC}$  and GND and between its  $V_{PP}$  and GND. LOW inductance capacitors should be placed as close as possible to package leads.

# **VPP** Trace on Printed Circuit Boards

Updating the memory contents of flash memories that reside in the target system requires that the printed circuit board designer pay attention to the  $V_{PP}$  Power Supply trace. Use similar trace widths and layout considerations given to the  $V_{CC}$  power bus.

# The Inhibition of Overwrite Operation

Please do not execute reprogramming '0' for the bit which has already been programmed '0'. Overwrite operation may generate unerasable bit. In case of reprogramming '0' to the data which has been programmed '1'.

- Program '0' for the bit in which you want to change data from '1' to '0'.

- Program '1' for the bit which has already been programmed '0'.

For example, changing data from '1011110110111101' to '1010110110111100' requires '11101111111111110' programming.

### Power Supply

Block erase, full chip erase, word write and lock-bit configuration with an invalid  $V_{PP}$  (see 'DC Characteristics') produce spurious results and should not be attempted. Device operations at invalid  $V_{CC}$  voltage product spurious results and should be attempted.

# **OUTLINE DIMENSIONS**

### LIFE SUPPORT POLICY

SHARP components should not be used in medical devices with life support functions or in safety equipment (or similiar applications where component failure would result in loss of life or physical harm) without the written approval of an officer of the SHARP Corporation.

### LIMITED WARRANTY

SHARP warrants to its Customer that the Products will be free from defects in material and workmanship under normal use and service for a period of one year from the date of invoice. Customer's exclusive remedy for breach of this warranty is that SHARP will either (i) repair or replace, at its option, any Product which fails during the warranty period because of such defect (if Customer promptly reported the failure to SHARP in writing) or, (ii) if SHARP is unable to repair or replace, refund the purchase price of the Product upon its return to SHARP. This warranty does not apply to any Product which has been subjected to misuse, abnormal service or handling, or which has been altered or modified in design or construction, or which has been serviced or repaired by anyone other than Sharp. The warranties set forth herein are in lieu of, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will Sharp be liable, or in any way responsible, for any incidental or consequential economic or property damage.

The above warranty is also extended to Customers of Sharp authorized distributors with the following exception: reports of failures of Products during the warranty period and return of Products that were purchased from an authorized distributor must be made through the distributor. In case Sharp is unable to repair or replace such Products, refunds will be issued to the distributor in the amount of distributor cost.

SHARP reserves the right to make changes in specifications at any time and without notice. SHARP does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied.

### **NORTH AMERICA**

SHARP Microelectronics of the Americas 5700 NW Pacific Rim Blvd. Camas, WA 98607, U.S.A. Phone: (360) 834-2500 Telex: 49608472 (SHARPCAM) Facsimile: (360) 834-8903

### **EUROPE**

SHARP Electronics (Europe) GmbH Microelectronics Division Sonninstraße 3 20097 Hamburg, Germany Phone: (49) 40 2376-2286 Facsimile: (49) 40 2376-2232 http://www.sharpmed.com

# <u>ASIA</u>

SHARP Corporation Integrated Circuits Group 2613-1 Ichinomoto-Cho Tenri-City, Nara, 632, Japan Phone: +81-743-65-1321 Facsimile: +81-743-65-1532 http://www.sharp.co.jp

http://www.sharpsma.com