# **PE3293**

## **Product Description**

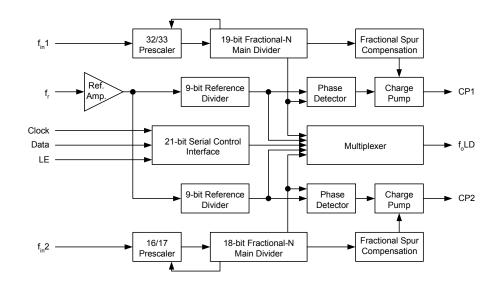

The PE3293 is a dual fractional-N phase-lock loop (PLL) IC designed for frequency synthesis and fabricated on Peregrine's patented UTSi® CMOS process. Each PLL includes a prescaler, phase detector, charge pump and on-board fractional spur compensation.

The patented spur compensation circuitry designed into the device ensures superior spur performance over the full temperature and VCO tuning range.

The PE3293 provides fractional-N division with power-oftwo denominator values up to 32. This allows comparison frequencies up to 32 times the channel spacing, providing a lower phase noise floor than integer PLLs. The 32/33 RF prescaler (PLL1) operates up to 1.8 GHz and the 16/17 IF prescaler (PLL2) operates up to 550 MHz.

#### **Applications**

- Triple mode, dual-band PCS / Cellular handset

- PCS/CDMA/Cellular handsets

- PCS/CDMA/Cellular base stations

## 1.8 GHz / 550 MHz Dual Fractional-N Ultra-Low Spurious PLL for Frequency Synthesis

#### **Features**

- Industry leading fractional spur compensation: no adjusting required, stable over temp.

- Ultra-Low Power consumption:

4.0 mA typical, both loops operating

- Modulo-32 fractional-N main counters

- Supply voltage range 2.7 to 3.3 VDC

#### Figure 1. Block Diagram

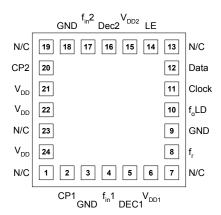

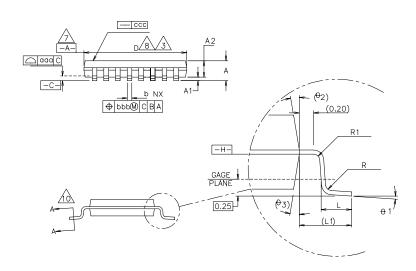

Figure 2. Pin Configuration: TSSOP (JEDEC MO-153-AC)

**Table 1. Pin Descriptions**

| Pin No. | Pin Name          | Type     | Description                                                                                                                                                                                                  |

|---------|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | N/C               |          | No connect.                                                                                                                                                                                                  |

| 2       | V <sub>DD</sub>   | (Note 1) | Power supply voltage input. Input may range from 2.7 V to 3.3 V. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                         |

| 3       | CP1               | Output   | Internal charge-pump output from PLL1 for connection to a loop filter for driving the input of an external VCO.                                                                                              |

| 4       | GND               |          | Ground.                                                                                                                                                                                                      |

| 5       | f <sub>in</sub> 1 | Input    | Prescaler input from the PLL1 (RF) VCO. Maximum frequency is 1.8 GHz.                                                                                                                                        |

| 6       | Dec1              |          | Power supply decoupling pin for PLL1. A capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                                                           |

| 7       | V <sub>DD1</sub>  |          | PLL1 prescaler power supply. 3.3 kohm resistor to V <sub>DD</sub> .                                                                                                                                          |

| 8       | f <sub>r</sub>    | Input    | Reference frequency input.                                                                                                                                                                                   |

| 9       | GND               |          | Ground.                                                                                                                                                                                                      |

| 10      | f₀LD              | Output   | Multiplexed output of the PLL1 and PLL2 main counters or reference counters, Lock Detect signals, and data out of the shift register. CMOS output (see Table 11, f <sub>o</sub> LD Programming Truth Table). |

| 11      | Clock             | Input    | CMOS clock input. Serial data for the various counters is clocked in on the rising edge into the 21-bit shift register.                                                                                      |

| 12      | Data              | Input    | Binary serial data input. CMOS input data entered MSB first. The two LSBs are the control bits.                                                                                                              |

| 13      | LE                | Input    | Load Enable CMOS input. When LE is high, data word stored in the 21-bit serial shift register is loaded into one of the four appropriate latches (as assigned by the control bits).                          |

| 14      | $V_{DD2}$         | Output   | PLL2 prescaler power supply. 3.3 kohm resistor to V <sub>DD</sub> .                                                                                                                                          |

| 15      | Dec2              | Output   | Power supply decoupling pin for PLL2. A capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                                                           |

| 16      | f <sub>in</sub> 2 | Input    | Prescaler input from the PLL2 (IF) VCO. Maximum frequency is 550 MHz.                                                                                                                                        |

| 17      | GND               |          | Ground.                                                                                                                                                                                                      |

| 18      | CP2               | Output   | Internal charge-pump output for PLL2. For connection to a loop filter for driving the input of an external VCO.                                                                                              |

| 19      | V <sub>DD</sub>   | (Note 1) | Same as pin 2.                                                                                                                                                                                               |

| 20      | V <sub>DD</sub>   | (Note 1) | Same as pin 2.                                                                                                                                                                                               |

Note 1:  $V_{DD}$  pins 2, 19, and 20 are connected by diodes and must be supplied with the same voltage level.

File No. 70/0015~02C | UTSi ® CMOS RFIC SOLUTIONS

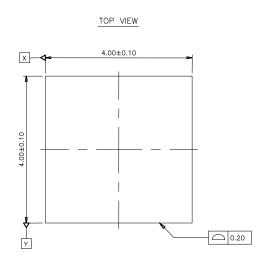

Figure 3. Pin Configuration: 24-Pin BCC (Top View)

**Table 2. Pin Descriptions**

| Pin No. | Pin Name          | Type     | Description                                                                                                                                                                                                  |

|---------|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | N/C               |          | No connect.                                                                                                                                                                                                  |

| 2       | CP1               | Output   | Internal charge-pump output from PLL1 for connection to a loop filter for driving the input of an external VCO.                                                                                              |

| 3       | GND               |          | Ground                                                                                                                                                                                                       |

| 4       | f <sub>in</sub> 1 | Input    | Prescaler input from the PLL1 (RF) VCO. Maximum frequency is 1.8 GHz.                                                                                                                                        |

| 5       | Dec1              |          | Power supply decoupling pin for PLL1. A capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                                                           |

| 6       | V <sub>DD1</sub>  |          | PLL1 prescaler power supply (FlexiPower 1).                                                                                                                                                                  |

| 7       | N/C               |          | No connect.                                                                                                                                                                                                  |

| 8       | f <sub>r</sub>    | Input    | Reference frequency input.                                                                                                                                                                                   |

| 9       | GND               |          | Ground.                                                                                                                                                                                                      |

| 10      | f <sub>o</sub> LD | Output   | Multiplexed output of the PLL1 and PLL2 main counters or reference counters, Lock Detect signals, and data out of the shift register. CMOS output (see Table 11, f <sub>o</sub> LD Programming Truth Table). |

| 11      | Clock             | Input    | CMOS clock input. Serial data for the various counters is clocked in on the rising edge into the 21-bit shift register.                                                                                      |

| 12      | Data              | Input    | Binary serial data input. CMOS input data entered MSB first. The two LSBs are the control bits.                                                                                                              |

| 13      | N/C               |          | No connect.                                                                                                                                                                                                  |

| 14      | LE                | Input    | Load Enable CMOS input. When LE is high, data word stored in the 21-bit serial shift register is loaded into one of the four appropriate latches (as assigned by the control bits).                          |

| 15      | $V_{DD2}$         |          | PLL2 prescaler power supply. 3.3 kohm resistor to V <sub>DD</sub> .                                                                                                                                          |

| 16      | Dec2              |          | Power supply decoupling pin for PLL2. A capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                                                           |

| 17      | f <sub>in</sub> 2 | Input    | Prescaler input from the PLL2 (IF) VCO. Maximum frequency is 550MHz.                                                                                                                                         |

| 18      | GND               |          | Ground.                                                                                                                                                                                                      |

| 19      | N/C               |          | No connect.                                                                                                                                                                                                  |

| 20      | CP2               | Output   | Internal charge-pump output for PLL2. For connection to a loop filter for driving the input of an external VCO.                                                                                              |

| 21      | V <sub>DD</sub>   | (Note 1) | Power supply voltage input. Input may range from 2.7 V to 3.3 V. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                         |

| Pin No. | Pin Name        | Туре     | Description     |  |  |  |  |  |

|---------|-----------------|----------|-----------------|--|--|--|--|--|

| 22      | V <sub>DD</sub> | (Note 1) | Same as pin 21. |  |  |  |  |  |

| 23      | N/C             |          | No connect.     |  |  |  |  |  |

| 24      | V <sub>DD</sub> | (Note 1) | Same as pin 21. |  |  |  |  |  |

Note 1: VDD pins 21, 22, and 24 are connected by diodes and must be supplied with the same voltage level.

#### PE3293 Description

The PE3293 is intended for such applications as the local oscillator for the RF and first IF of dual-conversion transceivers. The RF PLL (PLL1) includes a 32/33 prescaler with a 1.8 GHz maximum frequency of operation, where the IF PLL (PLL2) incorporates a 16/17 prescaler with a 550 MHz maximum frequency of operation. Using an advanced fractional-N phase-locked loop technique, the PE3293 can generate a stable, very low phase- noise signal. The dual fractional architecture allows fine resolution in both PLLs, with no degradation in phase noise performance.

Data is transferred into the PE3293 via a three-wire interface (Data, Clock, LE). Supply voltage can range from 2.7 to 3.3 volts for  $V_{DD}$ . PE3293 features very low power consumption and is available in a JEDEC MO-153-AC (TSSOP), 20-pin package and 24-lead BCC package.

#### **Spurious Response**

A critical parameter for synthesizer designs is spurious output. Spurs occur at the integer multiples of the step size away from center tone. An important feature of fractional synthesizers is their ability to reduce these spurious sidebands. The PE3293 has a built-in method for reducing these spurs, with no external components or tuning required. In addition, this circuitry works over the full commercial temperature and VCO tuning range.

#### **Table 3. Absolute Maximum Ratings**

| Symbol             | Parameter/Conditions      | Min  | Max                   | Units |

|--------------------|---------------------------|------|-----------------------|-------|

| $V_{DD}$           | Supply voltage            | -0.3 | 4.0                   | V     |

| $V_{DDI}, V_{DD}2$ | Prescaler supply voltage  | -0.3 | $V_{DD}$              | V     |

| Vı                 | Voltage on any input      | -0.3 | V <sub>DD</sub> + 0.3 | ٧     |

| l <sub>l</sub>     | DC into any input         | -10  | +10                   | mA    |

| $T_{stg}$          | Storage temperature range | -65  | 150                   | °C    |

#### **Table 4. Operating Ratings**

| Symbol            | Parameter/Conditions                | Min | Max             | Units |

|-------------------|-------------------------------------|-----|-----------------|-------|

| $V_{DD}$          | Supply voltage                      | 2.7 | 3.3             | V     |

| $V_{DD}1,V_{DD}2$ | Prescaler supply voltage            | 0.8 | $V_{\text{DD}}$ | °C    |

| T <sub>A</sub>    | Operating ambient temperature range | -40 | 85              | °C    |

#### **Table 5. ESD Ratings**

| Symbol           | Parameter/Conditions                  | Level | Units |

|------------------|---------------------------------------|-------|-------|

| V <sub>ESD</sub> | ESD voltage human body model (Note 1) | 2000  | V     |

Note 1: Periodically sampled, not 100% tested. Tested per MIL-STD-883, M3015 C2

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UTSi device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in Table 5.

### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UTSi CMOS devices are immune to latch-up.

## **Table 6. DC Characteristics**

$V_{DD}$  = 3.0 V, -40° C <  $T_{A}$  < 85° C, unless otherwise specified

| Symbol                                              | Parameter                                      | Conditions                                                                                                            | Min                   | Тур | Max                   | Units |

|-----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| I <sub>DD</sub>                                     | 3 V supply current                             | C <sub>10</sub> , C <sub>20</sub> = 00 (both PLLs on)                                                                 |                       | 4.0 |                       | mA    |

| I <sub>stby</sub>                                   | Total standby current                          |                                                                                                                       |                       | 5.0 | 50                    | μА    |

| Digital inputs:                                     | Clock, Data, LE                                |                                                                                                                       |                       |     | •                     |       |

| V <sub>IH</sub>                                     | High level input voltage                       | V <sub>DD</sub> = 2.7 to 3.3 volts                                                                                    | 0.7 x V <sub>DD</sub> |     |                       | V     |

| V <sub>IL</sub>                                     | Low level input voltage                        | V <sub>DD</sub> = 2.7 to 3.3 volts                                                                                    |                       |     | 0.3 x V <sub>DD</sub> | V     |

| I <sub>IH</sub>                                     | High level input current                       | $V_{IH} = V_{DD} = 3.3 \text{ volts}$                                                                                 | -1                    |     | +1                    | μА    |

| I <sub>IL</sub>                                     | Low level input current                        | V <sub>IL</sub> = 0, V <sub>DD</sub> = 3.3 volts                                                                      | -1                    |     | +1                    | μΑ    |

| Reference Div                                       | ider input: f <sub>r</sub>                     |                                                                                                                       |                       |     | •                     |       |

| I <sub>IHR</sub>                                    | Input current                                  | $V_{IH} = V_{DD} = 3.3 \text{ volts}$                                                                                 |                       |     | +25                   | μА    |

| I <sub>ILR</sub>                                    | Input current                                  | V <sub>IL</sub> = 0, V <sub>DD</sub> = 3.3 volts                                                                      | -25                   |     |                       | μА    |

| Digital output:                                     | f <sub>o</sub> LD                              |                                                                                                                       |                       |     | •                     |       |

| $V_{OLD}$                                           | Output voltage LOW                             | I <sub>out</sub> = 1 mA                                                                                               |                       |     | 0.4                   | V     |

| $V_{OHD}$                                           | Output voltage HIGH                            | I <sub>out</sub> = -1 mA                                                                                              | V <sub>DD</sub> - 0.4 |     |                       | V     |

| Charge Pump                                         | outputs: CP1, CP2                              |                                                                                                                       |                       |     |                       |       |

| I <sub>CP - Source</sub>                            | - Drive current                                | V <sub>CP</sub> = V <sub>DD</sub> / 2                                                                                 |                       | -70 |                       | μΑ    |

| I <sub>CP - Sink</sub>                              | - Drive current                                | VCP - VDD / Z                                                                                                         |                       | -70 |                       | μА    |

| I <sub>CPL</sub>                                    | Leakage current                                | $0.5 \text{ V} < \text{V}_{CP} < \text{V}_{DD} - 0.5 \text{ volt}$                                                    | -5                    |     | 5                     | nA    |

| I <sub>CP - Source</sub> VS. I <sub>CP - Sink</sub> | Sink vs. source mismatch                       | V <sub>CP</sub> = V <sub>DD</sub> / 2, T <sub>A</sub> = 25° C                                                         |                       |     | 10                    | %     |

| I <sub>CP</sub> vs T <sub>A</sub>                   | Output current vs. temperature                 | $V_{CP} = V_{DD} / 2$                                                                                                 |                       | 10  |                       | %     |

| I <sub>CP</sub> vs. V <sub>CP</sub>                 | Output current magnitude variation vs. voltage | $0.5 \text{ V} < \text{V}_{\text{CP}} < \text{V}_{\text{DD}} - 0.5 \text{ volt}, T_{\text{A}} = 25^{\circ} \text{ C}$ |                       | 10  |                       | %     |

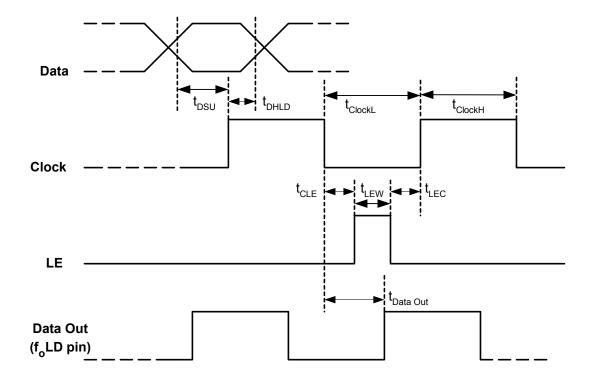

#### **Table 7. AC Characteristics**

$V_{DD}$  = 3.0 V, -40° C <  $T_A$  < 85° C, unless otherwise specified

| Symbol                | Parameter                                          | Conditions                    | Min      | Max  | Units     |

|-----------------------|----------------------------------------------------|-------------------------------|----------|------|-----------|

| Control Interfac      | ce and Latches (see figure 6)                      |                               |          |      |           |

| f <sub>Clock</sub>    | Serial data clock frequency                        |                               |          | 10   | MHz       |

| t <sub>ClockH</sub>   | Serial clock HIGH time                             |                               | 50       |      | ns        |

| t <sub>ClockL</sub>   | Serial clock LOW time                              |                               | 50       |      | ns        |

| t <sub>DSU</sub>      | Data set-up time to Clock rising edge              |                               | 50       |      | ns        |

| t <sub>DHLD</sub>     | Data hold time after Clock rising edge             |                               | 10       |      | ns        |

| t <sub>LEW</sub>      | LE pulse width                                     |                               | 50       |      | ns        |

| t <sub>CLE</sub>      | Clock falling edge to LE rising edge               |                               | 50       |      | ns        |

| t <sub>LEC</sub>      | LE falling edge to Clock rising edge               |                               | 50       |      | ns        |

| t <sub>Data Out</sub> | Data Out delay after Clock falling edge (foLD pin) | C <sub>L</sub> = 50 pf        |          | 90   | ns        |

| Main Divider (Ir      | ncluding Prescaler)                                |                               | <u>.</u> |      |           |

| f <sub>in</sub> 1     | Operating frequency                                |                               | 300      | 1800 | MHz       |

| f <sub>in</sub> 2     | Operating frequency                                |                               | 45       | 550  | MHz       |

| Pf <sub>in</sub> 1    | Input level range                                  | External AC coupling          | -7       | 5    | dBm       |

| Pf <sub>in</sub> 2    | Input level range                                  | External AC coupling          | -10      | 5    | dBm       |

| f <sub>c</sub>        | Comparison frequency                               |                               |          | 10   | MHz       |

| Reference Divid       | der                                                |                               | •        | •    | •         |

| f <sub>r</sub>        | Operating frequency                                |                               |          | 50   | MHz       |

| V <sub>fr</sub>       | Input sensitivity                                  | External AC coupling (note 1) | 0.5      |      | $V_{P-P}$ |

Note 1: CMOS logic levels may be used if DC coupled.

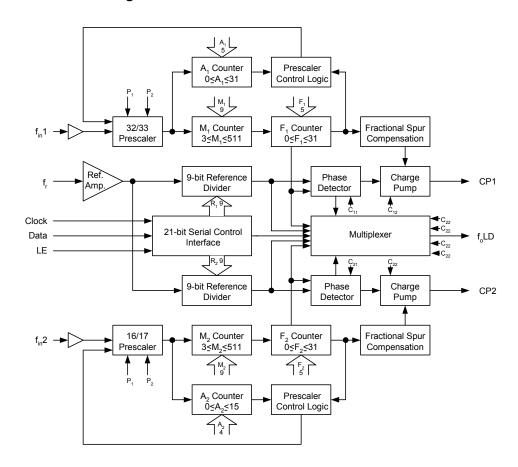

#### **Functional Description**

The Functional Block Diagram in Figure 5 shows a 21-bit serial control register, a multiplexed output, and PLL sections PLL1 and PLL2. Each PLL contains a fractional-N main counter chain, a reference counter, a phase detector, and an internal charge pump with on-chip fractional spur compensation. Each fractional-N main counter chain includes an internal dual modulus prescaler, supporting counters, and a fractional accumulator.

Serial input data is clocked on the rising edge of Clock, MSB first. The last two bits are the address bits that determine the register address. Data is transferred into the counters as shown in Table 8, PE3293 Register Set. If the f<sub>o</sub>LD pin is configured as data out, then the contents of shift register bit  $S_{20}$ are clocked on the falling edge of Clock onto the f<sub>o</sub>LD pin. This feature allows the PE3293 and compatible devices to be connected in a daisychain configuration.

The PLL1 (RF) VCO frequency f<sub>in</sub>1 is related to the reference frequency f<sub>r</sub> by the following equation:

$$f_{in}1 = [(32 \times M_1) + A_1 + (F_1/32)] \times (f_r/R_1)$$

(1) Note that A<sub>1</sub> must be less than or equal to M<sub>1</sub>. Also, f<sub>in</sub>1 must be greater than or equal to 1024 x  $(f_r/R_1)$  to obtain contiguous channels.

The PLL2 (IF) VCO frequency f<sub>in</sub>2 is related to the reference frequency f<sub>r</sub> by the following equation:

$$f_{in}2 = [(16 \times M_2) + A_2 + (F_2/32)] \times (f_r/R_2)$$

(2) Note that  $A_2$  must be less than or equal to  $M_2$ . Also, fin2 must be greater than or equal to 256 x (fr/ R<sub>2</sub>) to obtain contiguous channels.

$F_1$  sets PLL1 fractionality. If  $F_1$  is an even number, the PE3293 automatically reduces the fraction. For example, if  $F_1$  = 12, then the fraction 12/32 is automatically reduced to 3/8. In this way, fractional denominators of 2, 4, 8, 16 and 32 are available. F<sub>2</sub> sets the fractionality for PLL2 in the same manner.

Figure 4. Functional Block Diagram

File No. 70/0015~02C | UTSi ® CMOS RFIC SOLUTIONS

## Table 8. Register Set

| S <sub>20</sub> | S <sub>19</sub>                                                                                                                                         | S <sub>18</sub> | S <sub>17</sub> | S <sub>16</sub> | S <sub>15</sub> | S <sub>14</sub> | S <sub>13</sub>                                    | S <sub>12</sub> | S <sub>11</sub> | S <sub>10</sub>                                  | S <sub>9</sub>  | S <sub>8</sub>  | S <sub>7</sub>                                         | S <sub>6</sub>  | S <sub>5</sub>  | S <sub>4</sub>  | S <sub>3</sub>  | S <sub>2</sub>  | S <sub>1</sub> | S <sub>0</sub> |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------------------------------------|-----------------|-----------------|--------------------------------------------------|-----------------|-----------------|--------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

|                 | Reserved Test PLL2 Synthesizer control                                                                                                                  |                 |                 |                 |                 |                 | PLL2 Reference counter R <sub>2</sub> divide ratio |                 |                 |                                                  |                 |                 | Add                                                    | ress            |                 |                 |                 |                 |                |                |

|                 |                                                                                                                                                         |                 |                 | 0               | C <sub>24</sub> | C <sub>23</sub> | C <sub>22</sub>                                    | C <sub>21</sub> | C <sub>20</sub> | R <sub>28</sub>                                  | R <sub>27</sub> | R 26            | R <sub>25</sub>                                        | R <sub>24</sub> | R <sub>23</sub> | R 22            | R <sub>21</sub> | R <sub>20</sub> | 0              | 0              |

| Res.            | PLL2 Mai                                                                                                                                                |                 |                 | Main co         | ounter N        | ∕I₂ divide      | e ratio                                            |                 |                 | PLL2 Swallow counter A <sub>2</sub> divide ratio |                 |                 | PLL2 Fractional counter F <sub>2</sub> numerator value |                 |                 |                 | Add             | ress            |                |                |

| 1103.           | M <sub>28</sub>                                                                                                                                         | M <sub>27</sub> | M <sub>26</sub> | M <sub>25</sub> | M <sub>24</sub> | M <sub>23</sub> | M <sub>22</sub>                                    | M <sub>21</sub> | M <sub>20</sub> | A <sub>23</sub>                                  | A <sub>22</sub> | A <sub>21</sub> | A <sub>20</sub>                                        | F <sub>24</sub> | F <sub>23</sub> | F <sub>22</sub> | F <sub>21</sub> | F <sub>20</sub> | 0              | 1              |

| Re              | ve.                                                                                                                                                     |                 | Power vo        |                 | Р               | LL1 Sy          | nthesize                                           | er contr        | ol              |                                                  | F               | PLL1 Re         | eference                                               | e counte        | er R₁ div       | vide rati       | 0               |                 | Add            | ress           |

| 17.6            |                                                                                                                                                         | P <sub>2</sub>  | Res.            | P <sub>1</sub>  | C <sub>14</sub> | C <sub>13</sub> | C <sub>12</sub>                                    | C <sub>11</sub> | C <sub>10</sub> | R <sub>18</sub>                                  | R <sub>17</sub> | R <sub>16</sub> | R <sub>15</sub>                                        | R <sub>14</sub> | R <sub>13</sub> | R <sub>12</sub> | R <sub>11</sub> | R <sub>10</sub> | 1              | 0              |

|                 | PLL1 Main counter M <sub>1</sub> divide ratio  PLL1 Swallow counter A <sub>1</sub> divide ratio  PLL1 Fractional counter F <sub>1</sub> numerator value |                 |                 |                 |                 | Add             | ress                                               |                 |                 |                                                  |                 |                 |                                                        |                 |                 |                 |                 |                 |                |                |

| M <sub>18</sub> | M <sub>17</sub>                                                                                                                                         | M <sub>16</sub> | M <sub>15</sub> | M <sub>14</sub> | M <sub>13</sub> | M <sub>12</sub> | M <sub>11</sub>                                    | M <sub>10</sub> | A <sub>14</sub> | A <sub>13</sub>                                  | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub>                                        | F <sub>14</sub> | F <sub>13</sub> | F <sub>12</sub> | F <sub>11</sub> | F <sub>10</sub> | 1              | 1              |

Figure 5. Serial Interface Mode Timing Diagram

# Programmable Divide Values (R1, R2, F1, F2, A1, A2, M1, M2)

Data is clocked into the 21-bit shift register, MSB first. When LE is asserted HIGH, data is latched into the registers addressed by the last two bits shifted into the 21-bit register, according to Table 8. For example, to program the PLL1 (RF) swallow counter,  $A_1$ , the last two bits shifted into the register  $(S_0, S_1)$  would be (1,1). The 5-bit  $A_1$  counter would then be programmed according to Table 9. For normal operation,  $S_{16}$  of address (0,0) (the Test bit) must be programmed to 0 even if PLL2 (IF) is not used.

**Table 9. PE3293 Counter Programming Example**

| Divide Value | MSB             |                 |                 |                 | LSB             | Add            | ress           |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

|              | S <sub>11</sub> | S <sub>10</sub> | S <sub>9</sub>  | S <sub>8</sub>  | S <sub>7</sub>  | S <sub>1</sub> | S <sub>0</sub> |

|              | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | 1              | 1              |

| 0            | 0               | 0               | 0               | 0               | 0               | 1              | 1              |

| 1            | 0               | 0               | 0               | 0               | 1               | 1              | 1              |

| 2            | 0               | 0               | 0               | 1               | 0               | 1              | 1              |

| -            | -               | -               | -               | -               | -               | 1              | 1              |

| 31           | 1               | 1               | 1               | 1               | 1               | 1              | 1              |

#### **Program Modes**

Several modes of operation can be programmed with bits  $C_{10}$  -  $C_{14}$  and  $C_{20}$  -  $C_{24}$ , including the phase detector polarity, charge pump high impedance, output of the  $f_oLD$  pin and power-down modes. The PE3293 modes of operation are shown on Table 10. The truth table for the  $f_oLD$  output is shown in Table 11.

Table 10. PE3293 Program Modes

| S <sub>15</sub>                 | S <sub>14</sub>                 | S <sub>13</sub>                                             | S <sub>12</sub>                                                                          | S <sub>11</sub>                                         | S <sub>1</sub> | S <sub>0</sub> |

|---------------------------------|---------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|----------------|

| C <sub>24</sub><br>See Table 11 | C <sub>23</sub><br>See Table 11 | C <sub>22</sub><br>0 = PLL1 CP normal<br>1 = PLL1 CP High Z | C <sub>21</sub> (Note 2) 0 = PLL2 Phase Detector inverted 1 = PLL2 Phase Detector normal | C <sub>20</sub> (Note 1)<br>0 = PLL2 on<br>1 = PLL2 off | 0              | 0              |

| C <sub>14</sub><br>See Table 11 | C <sub>13</sub><br>See Table 11 | C <sub>12</sub><br>0 = PLL1 CP normal<br>1 = PLL1 CP High Z | C <sub>11</sub> (Note 2) 0 = PLL1 Phase Detector inverted 1 = PLL1 Phase Detector normal | C <sub>10</sub> (Note 1)<br>0 = PLL1 on<br>1 = PLL1 off | 1              | 0              |

**Note 1:** The PLL1 power-down mode disables all of PLL1's components except the  $R_1$  counter and the reference frequency input buffer, with CP1 (pin 3) and  $f_{in}1$  (pin 5) becoming high impedance. The power down of PLL2 has similar results with CP2 (pin 18) and  $f_{in}2$  (pin 16) becoming high impedance. Power down of both PLL1 and PLL2 further disables counters  $R_1$  and  $R_2$ , the reference frequency input, and the  $f_0$ LD output, causing  $f_r$  (pin 8) and  $f_0$ LD (pin 10) to become high impedance. The Serial Control Interface remains active at all times.

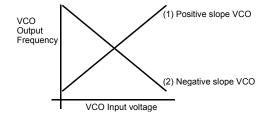

**Note 2:** The  $C_{11}$  and  $C_{21}$  bits should be set according to the voltage versus frequency slope of the VCO as shown in Figure 7. This relationship presumes the use of a passive loop filter. If an inverting active loop filter is used the relationship is also inverted.

Figure 6. VCO Characteristics

- When VCO1 (RF) slope is positive like (1), C<sub>11</sub> should be set HIGH.

- When VCO1 (RF) slope is negative like (2), C<sub>11</sub> should be set LOW.

- When VCO2 (IF) slope is positive like (1), C<sub>21</sub> should be set HIGH.

- When VCO2 (IF) slope is negative like (2), C<sub>21</sub> should be set LOW.

File No. 70/0015~02C | UTSi ® CMOS RFIC SOLUTIONS

#### Table 11. f<sub>o</sub>LD Programming Truth Table

X = don't care condition

| f <sub>o</sub> LD<br>Output State                   | C <sub>14</sub><br>(PLL1F <sub>0</sub> ) | C <sub>13</sub><br>(PLL1LD) | C <sub>24</sub><br>(PLL2F <sub>0</sub> ) | C <sub>23</sub><br>(PLL2LD) |

|-----------------------------------------------------|------------------------------------------|-----------------------------|------------------------------------------|-----------------------------|

| Disabled (Note 1)                                   | 0                                        | 0                           | 0                                        | 0                           |

| PLL 1 Lock detect<br>(Note 2) (LD1)                 | 0                                        | 1                           | 0                                        | 0                           |

| PLL2 Lock detect<br>(Note 2) (LD2)                  | 0                                        | 0                           | 0                                        | 1                           |

| PLL1 / PLL2 Lock detect<br>(Note 2)                 | 0                                        | 1                           | 0                                        | 1                           |

| PLL1 Reference divider output (f <sub>c</sub> 1)    | 1                                        | Х                           | 0                                        | 0                           |

| PLL2 Reference divider output (f <sub>c</sub> 2)    | 0                                        | X                           | 1                                        | 0                           |

| PLL1 Programmable divider output (f <sub>p</sub> 1) | 1                                        | Х                           | 0                                        | 1                           |

| PLL2 Programmable divider output (f <sub>p</sub> 2) | 0                                        | X                           | 1                                        | 1                           |

| Serial data out                                     | 1                                        | 0                           | 1                                        | 0                           |

| Reserved                                            | 1                                        | 0                           | 1                                        | 1                           |

| Reserved                                            | 1                                        | 1                           | 1                                        | 0                           |

| Counter reset (Note 3)                              | 1                                        | 1                           | 1                                        | 1                           |

Note 1: When the foLD is disabled the output is a CMOS LOW.

**Note 2:** Lock detect indicates when the VCO frequency is in "lock". When PLL1 is in lock and PLL1 lock detect is selected, the f₀LD pin will be HIGH with narrow pulses LOW. When PLL2 is in lock and PLL2 lock detect is selected, the f₀LD pin will be HIGH with narrow pulses LOW. When PLL1 / PLL2 lock detect is selected the f₀LD pin will be HIGH with narrow pulses LOW only when both PLL1 and PLL2 are in lock.

**Note 3:** The counter reset state when activated resets all counters. Upon removal of the reset, counters M, A, and F resume counting in close alignment with the R counter (the maximum error is one prescaler cycle). The reset bits can be activated to allow smooth acquisition upon powering up.

#### **Programming the Pre-scaler**

$P_2$  and  $P_1$  are used for internal testing of the prescaler and must be programmed with 0,0 for normal PLL operation.

#### **Phase Comparator Characteristics**

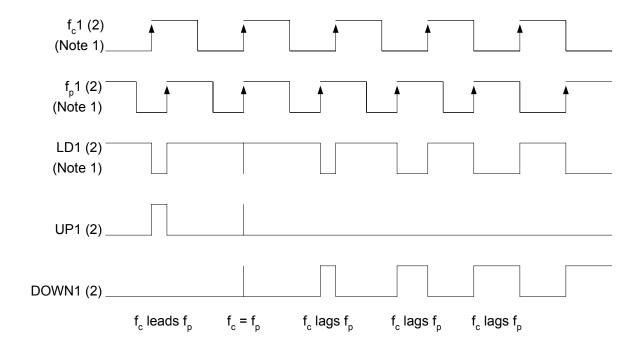

PLL1 has the timing relationships shown below for  $f_c1$ ,  $f_p1$ , LD1, UP1, and DOWN1. When  $C_{11}$  = HIGH, UP1 directs the internal PLL1 charge pump to source current and DOWN1 directs the PLL1 internal charge pump to sink current. If  $C_{11}$  = LOW, UP1 and DOWN1 are interchanged.

PLL2 has the timing relationships shown below for  $f_c2$ ,  $f_p2$ , LD2, UP2, and DOWN2. When  $C_{21}$  = HIGH, UP2 directs the internal PLL2 charge pump to source current and DOWN2 directs the PLL2 internal charge pump to sink current. If  $C_{21}$  = LOW, UP2 and DOWN2 are interchanged.

Figure 7. Phase Comparator Timing Diagram

Note 1: f<sub>c</sub>1(2), f<sub>p</sub>1(2), and LD1(2) are accessible via the f<sub>o</sub>LD pin per programming in Table 11.

#### **Loop Filter**

#### Second/Third Order Loops

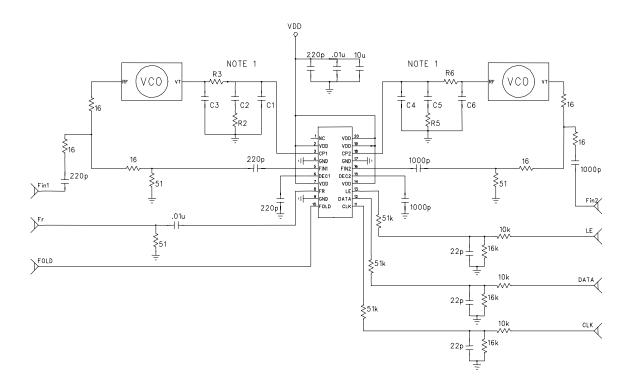

Choosing the optimum loop filter for a design encompasses many trade offs. The rule of thumb for choosing the loop filter bandwidth is 10 percent of the step size. A second order loop ( $C_1 \, C_2 \, R_2$  and  $C_4 \, C_5 \, R_5$  in Figure 9 omitting  $C_3 \, R_3 \, C_6$  and  $R_6$ ) will provide the least amount of components and the fastest lock times. If lock time is an issue, one might try opening up the loop filter, although if it is too wide, instability will dominate and worsen lock time. If lock time is not an issue, a narrower second order filter will minimize residual FM without requiring additional components.

Third Order loop filters ( $C_1$   $C_2$   $R_2$   $C_3$   $R_3$  and  $C_4$   $C_5$   $R_5$   $C_6$   $R_6$  in Figure 9) provide a good compromise between lock time and residual FM. We have found using a third order loop with 20 dB of rejection at the step size will halve the Residual FM as measured with a similar second order loop, with minimum effect on lock time.

#### **Loop Filter Bandwidth Design Considerations**

As part of the spur compensation circuitry, the PE329x series PLLs contain capacitors to ground internal to the charge pump. PLL1 contains a 50 pF capacitor and PLL2 contains a 100 pF capacitor. To ensure accurate loop filter calculations, it is critical that the calculated value of the first shunt capacitor ( $C_1$  &  $C_4$  in Figure 11) be at least 100 pF for PLL1 and 200 pF for PLL2. With this requirement satisfied, the remaining loop components can be calculated.

For a stable loop, it is also important that the loop bandwidth be less than or equal to one tenth of the step size.

#### **Digital Control Lines**

#### **Control Line Noise**

We have noticed frequency jitter during programming when a low impedance, such as a capacitor to ground, is placed next to any control line pin (clock, data, and load enable). The use of a 51 k ohm resistor in series with the control line will eliminate the problem with no effect to programming time.

#### **Enable Line Voltage**

The PE329x series PLLs use a level sensitive load enable. Therefore the digital controller must provide an active low to the part at all times except when the data is to be loaded into the shift register. If the PLL controller does not hold the voltage low, a high impedance resistor to ground should be added to the enable line to ensure stable operation.

#### 5 Volt Operation:

The PE329x series PLLs are not capable of accepting control voltages greater than 3.3 volts. Interface to 5 volt controllers requires the addition of resistor dividers to comply with the 3.3 volt maximum operation voltage.

#### Figure 8. Application Example

**Note 1:** For optimum fractional spur and lock-time performance  $C_2$  and  $C_5$  should be polyester (or poly propylene). In addition, the loop filter components must be free from contamination. Contamination will result in poor spur performance. For accurate loop bandwidth,  $C_1$  must be greater than or equal to 100 pF, and  $C_4$  must be greater than or equal to 200 pF.

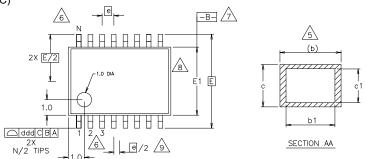

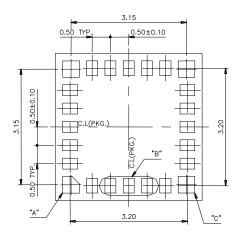

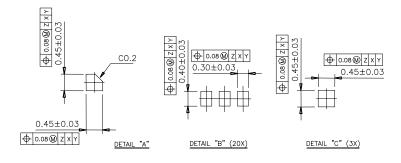

## Figure 9. Package Drawing

20-lead TSSOP (JEDEC MO-153-AC)

| S              | COMMON DIMENSION(MILLIMETERS) |      |      |  |  |

|----------------|-------------------------------|------|------|--|--|

| M<br>B<br>O    | 0.65mm LEAD PITCH             |      |      |  |  |

| L              | MIN                           | NOM  | MAX  |  |  |

| Α              |                               |      | 1.10 |  |  |

| A1             | 0.05                          |      | 0.15 |  |  |

| A2             | 0.85                          | 0.90 | 0.95 |  |  |

| L              | 0.50                          | 0.60 | 0.75 |  |  |

| R              | 0.09                          |      |      |  |  |

| R1             | 0.09                          |      |      |  |  |

| b              | 0.19                          |      | 0.30 |  |  |

| b1             | 0.19                          | 0.22 | 0.25 |  |  |

| С              | 0.09                          |      | 0.20 |  |  |

| c1             | 0.09                          |      | 0.16 |  |  |

| <del>0</del> 1 | 0°                            |      | 8°   |  |  |

| L1             | 1.0 REF                       |      |      |  |  |

| aaa            | 0.10                          |      |      |  |  |

| bbb            | 0.10                          |      |      |  |  |

| ccc            | 0.05                          |      |      |  |  |

| ddd            | 0.20                          |      |      |  |  |

| е              | 0.65 BSC                      |      |      |  |  |

| <del>0</del> 2 | 12° REF                       |      |      |  |  |

| <del>0</del> 3 | 12° REF                       |      |      |  |  |

| S           |          |     |      |      |             |

|-------------|----------|-----|------|------|-------------|

| M<br>B<br>O | AC       |     |      |      | N<br>O<br>T |

| L           | MIN      |     | NOM  | MAX  | Ė           |

| D           | 6.40     | )   | 6.50 | 6.60 | 3,8         |

| E1          | 4.30     | )   | 4.40 | 4.50 | 4,8         |

| E           | 6.4 BSC  |     |      |      |             |

| е           | 0.65 BSC |     |      |      |             |

| N           | 20       |     |      | 6    |             |

| NOTE        |          | 1,2 |      |      |             |

| ISS         | ISSUE    |     | A    |      |             |

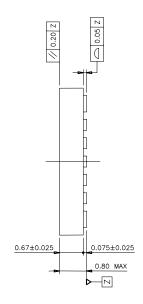

## Figure 10. Package Drawing

24-lead BCC

## **Table 12. Ordering Information**

| Order<br>Code | Part Marking | Description                                   | Package       | Shipping<br>Method |  |

|---------------|--------------|-----------------------------------------------|---------------|--------------------|--|

| 3293-11       | PE3293       | Screened to datasheet specs., fully qualified | 20-lead TSSOP | 74 units / Tube    |  |

| 3293-12       | PE3293       | Screened to datasheet specs., fully qualified | 20-lead TSSOP | 2000 unit / T&R    |  |

| 3293-14       | 3293         | Screened to datasheet specs., fully qualified | 24-lead BCC   | 640 Unit Trays     |  |

| 3293-15       | 3293         | Screened to datasheet specs., fully qualified | 24-lead BCC   | 2000 Unit T&R      |  |

| 3293-00       | PE3293EK     | Evaluation Board                              | 20-lead TSSOP | 1 / Box            |  |

| 3293-04       | PE3293EK     | Evaluation Board                              | 24-lead BCC   | 1 / Box            |  |