1,048,576-word × 4-bit High Speed Static Random Access Memory

# **HITACHI**

#### **Features**

- 1,048,576-word × 4-bit organization.

- Directly TTL compatible input and output.

- +5 V Single supply.

- Completely static memory.

- No clock or timing strobe required.

- Super fast access time: 15/20/25 ns (max).

- Revolutional pin arrangement.

## **Ordering Information**

| Type No.       | Access Time | Package                              |

|----------------|-------------|--------------------------------------|

| HM674100HJP-15 | 15 ns       | 400 mil 32 pin plastic SOJ (CP-32DB) |

| HM674100HJP-20 | 20 ns       |                                      |

| HM674100HJP-25 | 25 ns       |                                      |

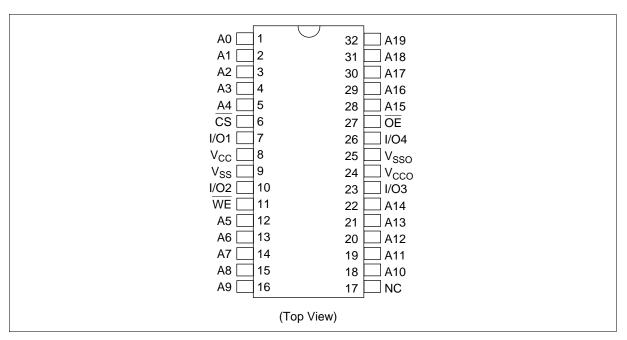

## **Pin Arrangement**

## **Pin Description**

| Pin Name         | Function                   |

|------------------|----------------------------|

| A0 to A19        | Address input              |

| I/O1 to I/O4     | input/output               |

| WE               | Write enable               |

| CS               | Chip select                |

| ŌĒ               | Output enable              |

| V <sub>cc</sub>  | +5 V Power supply          |

| V <sub>cco</sub> | Output buffer power supply |

| V <sub>SSO</sub> | Output buffer ground       |

| V <sub>SS</sub>  | Ground                     |

| NC               | Not connect                |

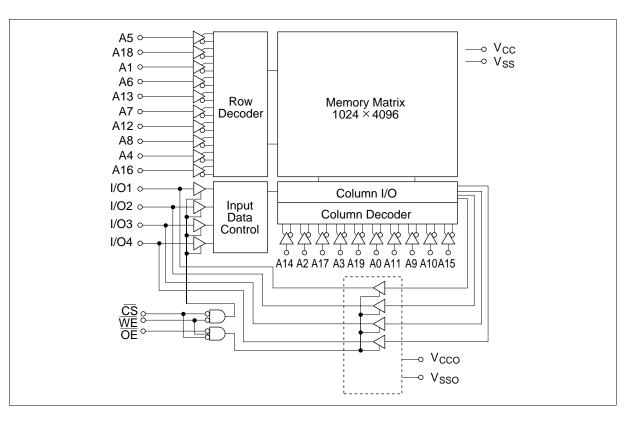

## **Block Diagram**

#### **Function Table**

#### Input

| -  |    |    |                 |          |                                    |                                |

|----|----|----|-----------------|----------|------------------------------------|--------------------------------|

| CS | WE | ŌĒ | Mode            | I/O Pin  | V <sub>cc</sub> Current            | Ref. Cycle                     |

| Н  | Х  | Х  | Not selected    | High-Z   | I <sub>SB</sub> , I <sub>SB1</sub> | _                              |

| L  | Н  | Н  | Output disabled | High-Z   | I <sub>CC</sub> , I <sub>CC1</sub> | _                              |

| L  | Н  | L  | Read            | Data Out | I <sub>cc</sub> , I <sub>cc1</sub> | Read Cycle (1), (2), (3)       |

| L  | L  | Н  | Write           | Data In  | I <sub>CC</sub> , I <sub>CC1</sub> | Write Cycle (1), (2), (3), (4) |

| L  | L  | L  | Write           | Data In  | I <sub>cc</sub> , I <sub>cc1</sub> | Write Cycle (5), (6)           |

Note: X: H or L

## **Absolute Maximum Ratings**

| Parameter                                         | Symbol          | Value                    | Unit |

|---------------------------------------------------|-----------------|--------------------------|------|

| Supply voltage <sup>*1</sup>                      | V <sub>cc</sub> | -0.5 to +7.0             | V    |

| Voltage on any pin relative to V <sub>SS</sub> *1 | V <sub>T</sub>  | $-0.5$ to $V_{CC}$ + 0.5 | V    |

| Power dissipation                                 | P <sub>T</sub>  | 1.0/1.5 <sup>*2</sup>    | W    |

| Operating temperature range                       | Topr            | 0 to +70                 | °C   |

| Storage temperature range (with bias)             | Tstg (Bias)     | –10 to +85               | °C   |

| Storage temperature range                         | Tstg            | −55 to +125              | °C   |

Notes: 1 With respect to  $V_{ss} = V_{sso}$

## **Recommended DC Operating Conditions** (Ta = 0 to +70°C)

| Parameter          | Symbol            | Min  | Тур | Max                   | Unit |  |

|--------------------|-------------------|------|-----|-----------------------|------|--|

| Supply voltage     | $V_{cc}, V_{cco}$ | 4.5  | 5.0 | 5.5                   | V    |  |

|                    | $V_{SS}, V_{SSO}$ | 0.0  | 0.0 | 0.0                   | V    |  |

| Input high voltage | V <sub>IH</sub>   | 2.2  | _   | V <sub>cc</sub> + 0.5 | V    |  |

| Input low voltage  | V <sub>IL</sub>   | -0.5 | _   | 0.8                   | V    |  |

$P_T = 1.5 \text{ W}$  is guaranteed under the minimum air flow exceeding 500 linear feet per minute. Under the DC and AC specifications shown in the Tables, this device is tested under the minimum transverse air flow exceeding 500 linear feet per minute.

**DC Characteristics** ( $V_{CC} = V_{CCO} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = V_{SSO} = 0 \text{ V}$ ,  $Ta = 0 \text{ to } +70^{\circ}\text{C}$ )

|                                |                  | HM674100H |     |     |     |     |     |      |                                                                                                                                                                                                       |

|--------------------------------|------------------|-----------|-----|-----|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                  | -15       |     | -20 |     | -25 |     | •    |                                                                                                                                                                                                       |

| Parameter                      | Symbol           | Min       | Max | Min | Max | Min | Max | Unit | Test Conditions                                                                                                                                                                                       |

| Input leakage current          | I <sub>LI</sub>  | _         | 2   | _   | 2   | _   | 2   | μΑ   | $V_{CC} = 5.5 \text{ V},$ $V_{IN} = 0 \text{ V to } V_{CC}$                                                                                                                                           |

| Output leakage current         | I <sub>LO</sub>  | _         | 10  | _   | 10  | _   | 10  | μΑ   | $\overline{\text{CS}} = V_{\text{IH}} \text{ or } \overline{\text{OE}} = V_{\text{IH}},$ $\overline{\text{WE}} = V_{\text{IL}}$ $V_{\text{I/O}} = 0 \text{ V to } V_{\text{CC}}$                      |

| Operating power supply current | I <sub>cc</sub>  | _         | 120 | _   | 120 | _   | 120 | mA   | $\overline{\text{CS}} = V_{\text{IL}}, I_{\text{I/O}} = 0 \text{ mA}$                                                                                                                                 |

| Average operating current      | I <sub>CC1</sub> | _         | 220 | _   | 200 | _   | 160 | mΑ   | min cycle, $I_{I/O} = 0 \text{ mA}$                                                                                                                                                                   |

| Standby power supply current   | I <sub>SB</sub>  | _         | 100 | _   | 80  | _   | 60  | mA   | $\overline{\text{CS}} = V_{\text{IH}}, V_{\text{IN}} = V_{\text{IH}} \text{ or } V_{\text{IL}}$                                                                                                       |

|                                | I <sub>SB1</sub> | _         | 10  | _   | 10  | _   | 10  | mA   | $\label{eq:control_control} \begin{split} \overline{CS} &\geq V_{\text{CC}} - 0.2 \text{ V} \\ V_{\text{IN}} &\leq 0.2 \text{ V or } V_{\text{IN}} \geq \\ V_{\text{CC}} - 0.2 \text{ V} \end{split}$ |

| Output low voltage             | V <sub>OL</sub>  | _         | 0.4 | _   | 0.4 | _   | 0.4 | V    | I <sub>OL</sub> = 8 mA                                                                                                                                                                                |

| Output high voltage            | Vou              | 2.4       |     | 2.4 |     | 2.4 |     | V    | $I_{ou} = -4 \text{ mA}$                                                                                                                                                                              |

## **Capacitance** (Ta = 25°C, f = 1 MHz)

| Parameter                | Symbol              | Max | Unit | Test Conditions        |

|--------------------------|---------------------|-----|------|------------------------|

| Input capacitance        | C <sub>IN</sub> *1  | 6   | pF   | $V_{IN} = 0 V$         |

| Input/Output capacitance | C <sub>I/O</sub> *1 | 10  | pF   | V <sub>I/O</sub> = 0 V |

Note: 1. This parameter is sampled and not 100% tested.

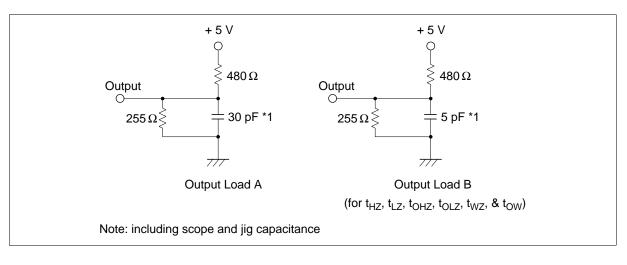

**AC Characteristics** ( $V_{CC} = V_{CCO} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = V_{SSO} = 0 \text{ V}$ ,  $Ta = 0 \text{ to } +70^{\circ}\text{C}$ , unless otherwise noted.)

#### **Test Conditions**

• Input pulse levels: V<sub>SS</sub> to 3.0 V

• Input timing reference levels: 1.5V

• Input rise and fall time: 4 ns

• Output reference levels: 1.5 V

• Output Load: See figure

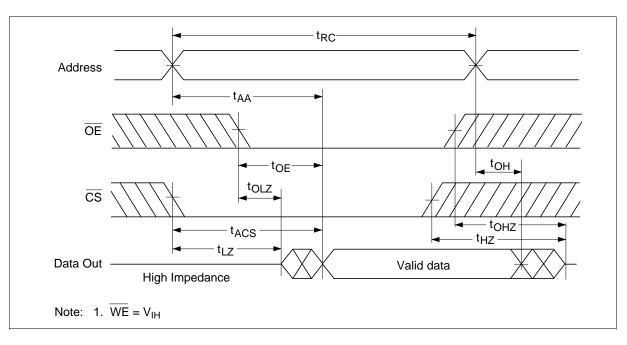

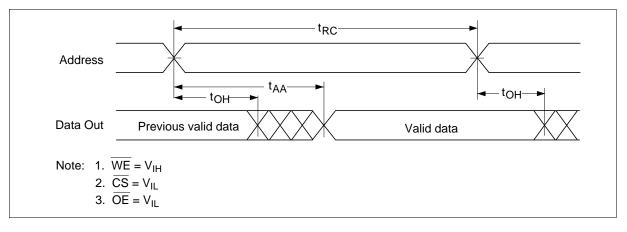

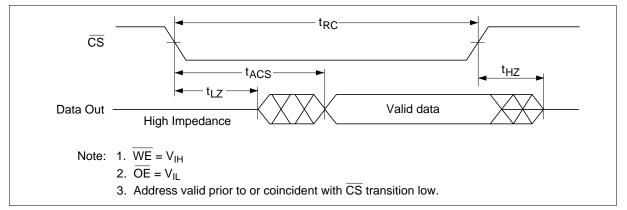

## **Read Cycle**

|                                      |                        | HM67 |     |     |     |     |     |      |

|--------------------------------------|------------------------|------|-----|-----|-----|-----|-----|------|

|                                      |                        | -15  |     | -20 |     | -25 |     |      |

| Parameter                            | Symbol                 | Min  | Max | Min | Max | Min | Max | Unit |

| Read cycle time                      | t <sub>RC</sub>        | 15   | _   | 20  | _   | 25  | _   | ns   |

| Address access time                  | t <sub>AA</sub>        | _    | 15  | _   | 20  | _   | 25  | ns   |

| Chip select access time              | t <sub>ACS</sub>       | _    | 15  | _   | 20  |     | 25  | ns   |

| Chip selection to output in low-Z    | t <sub>LZ</sub> *1,*2  | 5    | _   | 5   | _   | 5   | _   | ns   |

| Output enable to output Valid        | t <sub>OE</sub>        | _    | 8   | _   | 10  | _   | 15  | ns   |

| Output enable to output in low-Z     | t <sub>OLZ</sub> *1,*2 | 2    | _   | 2   | _   | 2   | _   | ns   |

| Chip deselection to output in high-Z | t <sub>HZ</sub> *1,*2  | 0    | 7   | 0   | 8   | 0   | 15  | ns   |

| Output hold from address change      | t <sub>oh</sub>        | 5    | _   | 5   | _   | 5   | _   | ns   |

Notes: 1. This parameter is sampled and not 100% tested.

<sup>2.</sup> Transition is measured ±200 mV from steady state voltage with specified loading in Load (B).

## **Timing Waveforms**

#### Read Cycle-1

#### Read Cycle-2

#### Read Cycle-3

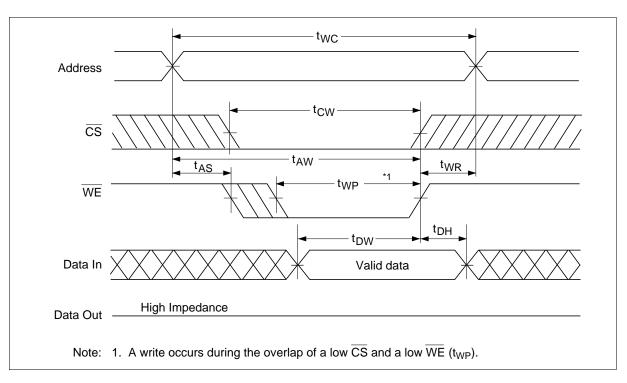

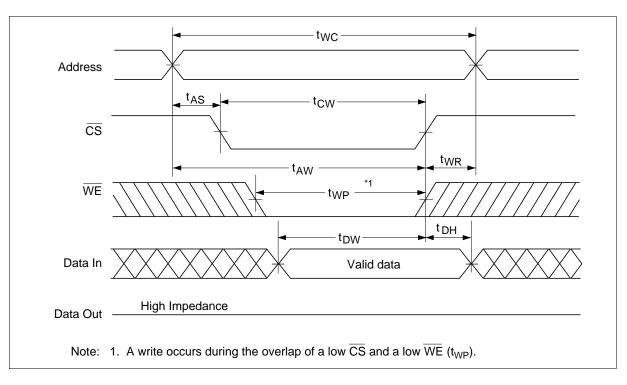

#### Write Cycle

|                                    |                         | HM67 |     |     |     |     |     |      |

|------------------------------------|-------------------------|------|-----|-----|-----|-----|-----|------|

|                                    |                         | -15  |     | -20 |     | -25 |     | _    |

| Parameter                          | Symbol                  | Min  | Max | Min | Max | Min | Max | Unit |

| Write cycle time                   | t <sub>wc</sub> *1      | 15   | _   | 20  | _   | 25  | _   | ns   |

| Chip selection to end of write     | t <sub>cw</sub>         | 12   | _   | 15  | _   | 17  | _   | ns   |

| Address valid to end of write      | t <sub>AW</sub>         | 12   | _   | 15  | _   | 17  | _   | ns   |

| Address setup time                 | t <sub>AS</sub>         | 0    | _   | 0   | _   | 0   | _   | ns   |

| Write pulse width                  | t <sub>WP</sub>         | 12   | _   | 15  | _   | 17  | _   | ns   |

| Write recovery time                | t <sub>wR</sub>         | 3    | _   | 3   | _   | 3   | _   | ns   |

| Data valid to end of write         | t <sub>DW</sub>         | 8    | _   | 10  | _   | 15  | _   | ns   |

| Data hold time                     | t <sub>DH</sub>         | 0    | _   | 0   | _   | 0   | _   | ns   |

| Write enable to output in high Z   | t <sub>wz</sub> *2, *3  | 0    | 7   | 0   | 8   | 0   | 12  | ns   |

| Output disable to output in high Z | t <sub>OHZ</sub> *2, *3 | 0    | 7   | 0   | 8   | 0   | 10  | ns   |

| Output active from end of write    | t <sub>ow</sub> *2, *3  | 2    | _   | 2   | _   | 2   | _   | ns   |

Notes: 1. All write cycle timings are referred from the last valid address to the first transitioning address.

- 2. This parameter is sampled and not 100% tested.

- 3. Transition is measured  $\pm 200$  mV from steady state voltage with specified loading in Load (B).

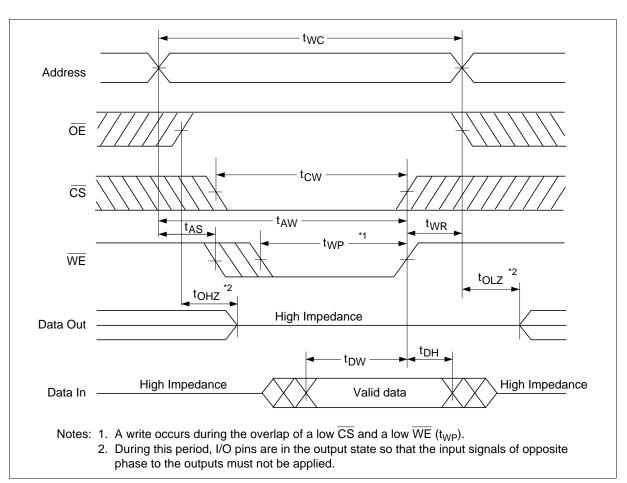

Write Cycle-1 ( $\overline{OE} = H$ ,  $\overline{WE}$  Controlled)

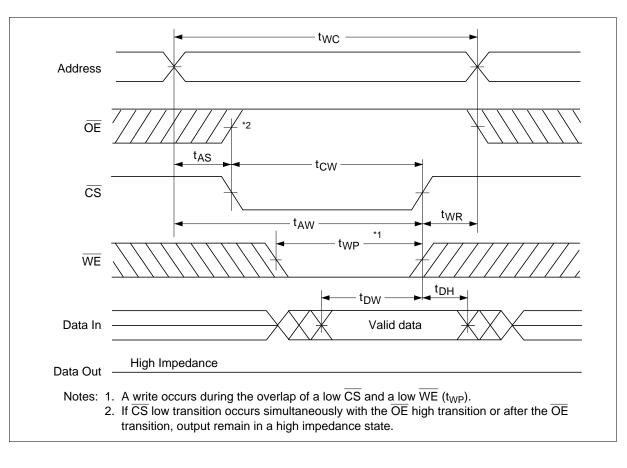

## Write Cycle-2 ( $\overline{OE} = H$ , $\overline{CS}$ Controlled)

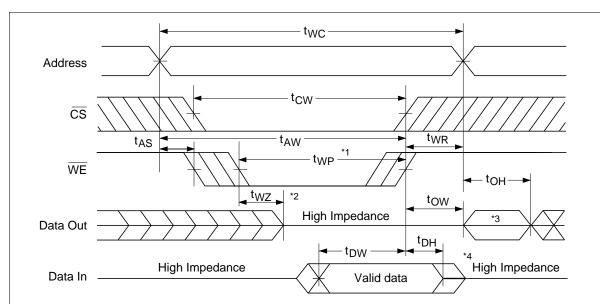

Write Cycle-3 ( $\overline{OE}$  = Clocked,  $\overline{WE}$  Controlled)

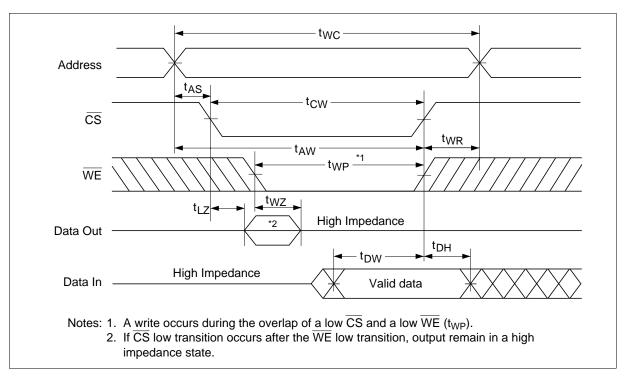

## Write Cycle-4 ( $\overline{OE}$ = Clocked, $\overline{CS}$ Controlled)

#### Write Cycle-5 ( $\overline{OE} = L$ , $\overline{WE}$ Controlled)

Notes: 1. A write occurs during the overlap of a low  $\overline{\text{CS}}$  and a low  $\overline{\text{WE}}$  (t<sub>WP</sub>).

- 2. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

- 3. Output data is the same phase of write data of this write cycle.

- 4. If  $\overline{\text{CS}}$  is low during this period, I/O pins are in the output state. Then, the data input signals of opposite phase to the outputs must not be applied them.

## Write Cycle-6 ( $\overline{OE} = L$ , $\overline{CS}$ Controlled)

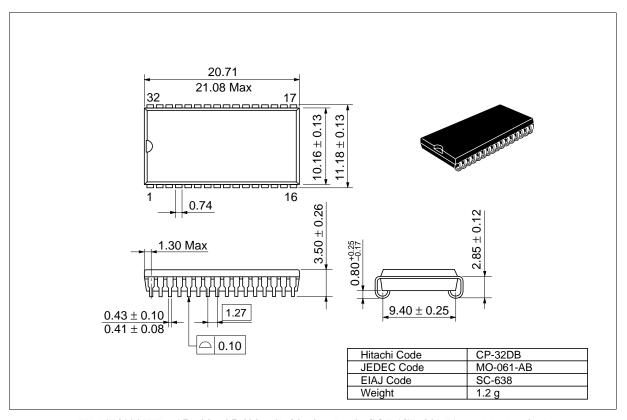

#### **Package Dimension**

#### HM674100HJP Series (CP-32DB)

Unit: mm

HM674100HJP -15, -20, -25 400 mil 32 pin plastic SOJ (CP-32DB) — Mechanical