National Semiconductor

# PC87391, PC87392, PC87393, PC87393F 100-Pin LPC SuperI/O Devices for Portable Applications

## **General Description**

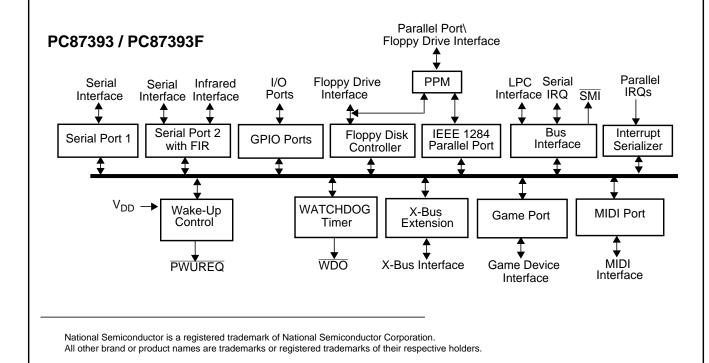

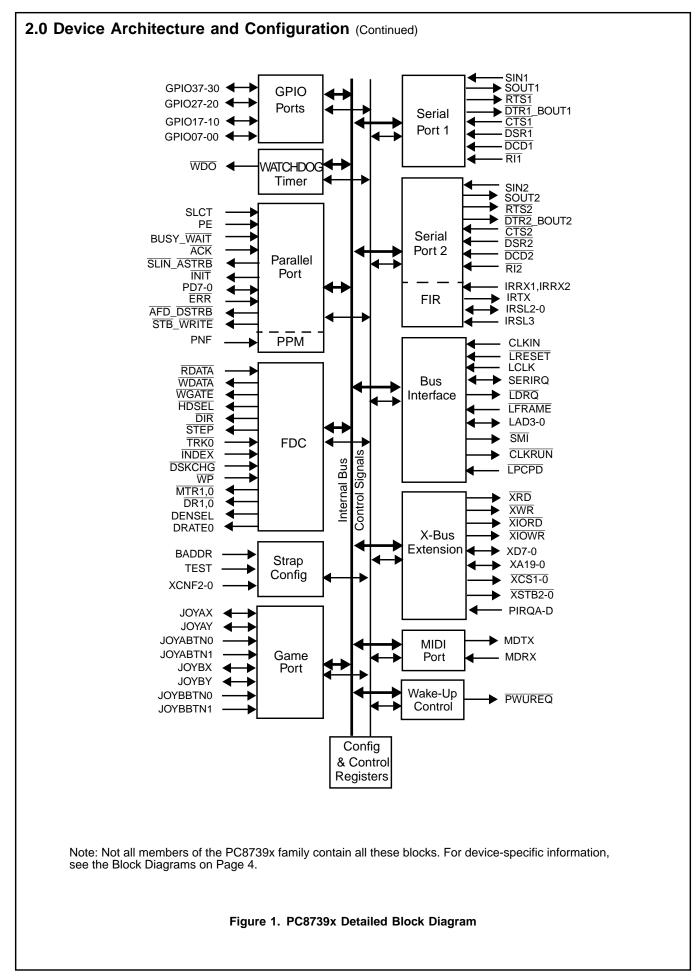

Block Diagram

National Semiconductor's PC8739x family of LPC SuperI/O devices is targeted for a wide range of portable applications. PC99 and ACPI compliant, the PC8739x family features an X-Bus Extension for read and write operations over the X-Bus, a full IEEE 1284 Parallel Port with a Parallel Port Multiplexer (PPM) for external Floppy Disk Drive (FDD) support, a Musical Instrument Digital Interface (MIDI) port, and a Game port. Like all National LPC SuperI/O devices, the PC8739x offers a single-chip solution to the most commonly used PC I/O peripherals.

The PC8739x family also incorporates: a Floppy Disk Controller (FDC), two enhanced Serial Ports (UARTs), one with Fast Infrared (FIR, IrDA 1.1 compliant), General-Purpose Input/Output (GPIO) support for a total of 32 ports, Interrupt Serializer for Parallel IRQs and an enhanced WATCH-DOG<sup>™</sup> timer.

The following features apply to the PC87393F. The feature lists for other PC8739x devices may differ. See the table on page 3 for a list of features for each device.

## **Outstanding Features**

- X-Bus Extension for read and write operations

- LPC bus interface, based on Intel's LPC Interface Specification Rev. 1.01, February 1999 (supports CLKRUN and LPCPD signals) and Intel FWH transactions

PRELIMINARY

September 2000 Revision 1.41

- PC99 and ACPI compliant

- Serial IRQ support (15 options)

- Interrupt Serializer (four Parallel IRQs to Serial IRQ)

- PPM for external FDD signal support

- MIDI interface compatible with MPU-401 UART mode

- Game port inputs for up to two joysticks

- Protection features, including GPIO lock and pin configuration lock

- 32 GPIO ports (16 standard, 16 with Assert IRQ/SMI)

- 5V tolerant and back-drive protected pins (except LPC bus pins)

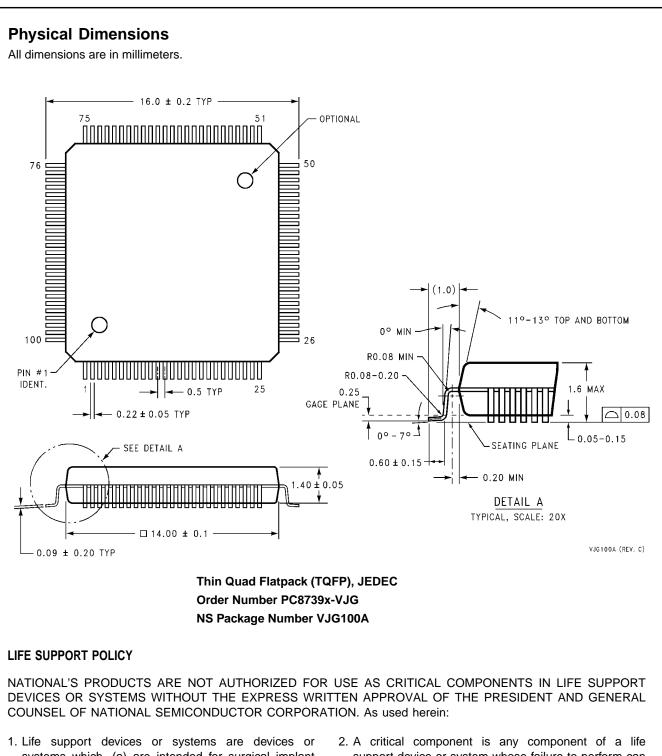

- 100-pin TQFP Package

#### Features

- LPC System Interface

- Synchronous cycles, up to 33 MHz bus clock

- 8-bit I/O cycles

- Up to four 8-bit DMA channels

- LPCPD and CLKRUN support

- Implements PCI mobile design guide recommendation (PCI Mobile Design Guide 1.1, Dec. 18, 1998)

- Memory and FWH transaction support

- Interrupt Serializer

- Four Parallel IRQs to Serial IRQ

- Musical Instrument Digital Interface (MIDI) Port

- Compatible with MPU-401 UART mode

- 16-byte Receive and Transmit FIFOs

- Loopback mode support

- Game Port

- Compatible with the Legacy Game Port definition

- Full digital implementation

- Supports up to two analog joysticks

- X-Bus Extension

- Supports read and write operations

- 8-bit data bus

- Up to 28-bit address bus supports up to 256MB data

- Two chip select pins

- Interrupt routing via PIRQ pins

- Supports BIOS flash devices

- PC99 and ACPI Compliant

- PnP Configuration Register structure

- Flexible resource allocation for all logical devices

- Relocatable base address

- Gilder Fifteen IRQ routing options

- Four optional 8-bit DMA channels (where applicable)

- Clock Sources

- 32.768 KHz, 14.318 MHz or 48 MHz clock input

- LPC clock, up to 33 MHz

- Power Supply

- 3.3V supply operation

- All pins are 5V tolerant

- All pins are back-drive protected, except LPC bus pins

- Wake-Up Control

- Optional routing of IRQ to power-up event

- 32 General-Purpose I/O (GPIO) Ports

- Sixteen standard, with Assert IRQ/SMI for 16 ports

- Programmable drive type for each output pin (opendrain, push-pull or output disable)

- Programmable option for internal pull-up resistor on each input pin

- Output lock option

- Input debounce mechanism

- Floppy Disk Controller (FDC)

- Programmable write protect

- FM and MFM mode support

- Enhanced mode command for three-mode Floppy Disk Drive (FDD) support

- Perpendicular recording drive support for 2.88 MB

- Burst and non-burst modes

- Full support for IBM Tape Drive register (TDR) implementation of AT and PS/2 drive types

- 16-byte data FIFO

- Error-free handling of data overrun and underrun

- Software compatible with the PC8477, which contains a superset of the FDC functions in the  $\mu DP8473$ , the NEC  $\mu PD765A$  and the N82077

- High-performance, digital separator

- Standard 5.25" and 3.5" FDD support

- Supports up to four floppy disk drives

- Supports fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

- Supports external drive via parallel port pins

- IEEE 1284 compliant Parallel Port

- ECP, including Level 2 (14 mA sink and source output buffers)

- Software or hardware control

- Enhanced Parallel Port (EPP) compatible with EPP 1.7 and EPP 1.9

- EPP support as mode 4 of the Extended Control Register (ECR)

- Selection of internal pull-up or pull-down resistor for Paper End (PE) pin

- Supports a demand DMA mode mechanism and a DMA fairness mechanism for improved bus utilization

- Protection circuit that prevents damage to the parallel port when a printer connected to it powers up or is operated at high voltages, even if the device is in power-down

- Parallel Port Multiplexer (PPM) to support additional external FDC signals on parallel port pins for FDD use

- Serial Port 1 (SP1)

- Software compatible with the 16550A and the 16450

- Shadow register support for write-only bit monitoring

- UART data rates up to 1.5 Mbaud

- Serial Port 2 with Fast Infrared (SP2 with FIR)

- Software compatible with the 16550A and the 16450

- Shadow register support for write-only bit monitoring

- UART data rates up to 1.5 Mbaud

- FIR IrDA 1.1 compliant

- HP-SIR

- ASK-IR option of SHARP-IR

- DASK-IR option of SHARP-IR

- Consumer Remote Control supports RC-5, RC-6, NEC, RCA and RECS 80

- DMA support one or two channels

- PnP dongle support

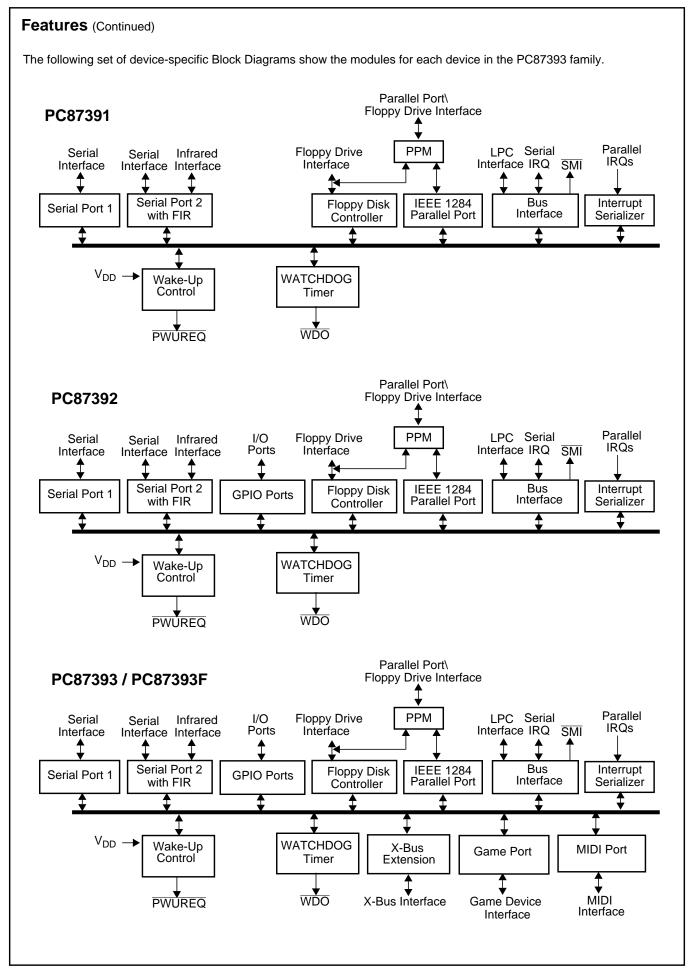

#### Features (Continued)

- WATCHDOG Timer

- Times out the system based on user-programmable time-out period

- System power-down capability for power saving

- User-defined trigger events to restart WATCHDOG

- Optional routing of WATCHDOG output on IRQ and/or SMI lines

#### **Device-specific Information**

The following table shows the main features for each device in the PC87393 family.

Function<sup>1</sup> PC87391 PC87392 PC87393 PC87393F LPC System Interface r V ~ V ~ Interrupt Serializer ~ V ~ Musical Instrument Digital Interface (MIDI) Port X X ~ ~ X Game Port X V 1 X-Bus Extension X X V V x x **FWH Emulation** X V PC99 and ACPI Compliant V ~ 1 V Wake-Up Control V 1 1 1 General-Purpose I/O (GPIO) Ports x V 1 V Floppy Disk Controller (FDC) V ~ ~ 1 IEEE 1284 compliant Parallel Port ~ V ~ V Serial Port 1 (SP1) V V V V Serial Port 2 with Fast Infrared (SP2 with FIR) ~ V V V WATCHDOG Timer ~ 1 ~ V

1. This datasheet contains notes that are device-specific. These notes can be found by searching for the specific device number.

- Strap Configuration

- Base Address (BADDR) strap to determine the base address of the Index-Data register pair

- Test strap to force the device into test mode (reserved for National Semiconductor use)

- X-Bus straps (XCNF2-0) define the functionality of the X-Bus at reset

# Table of Contents

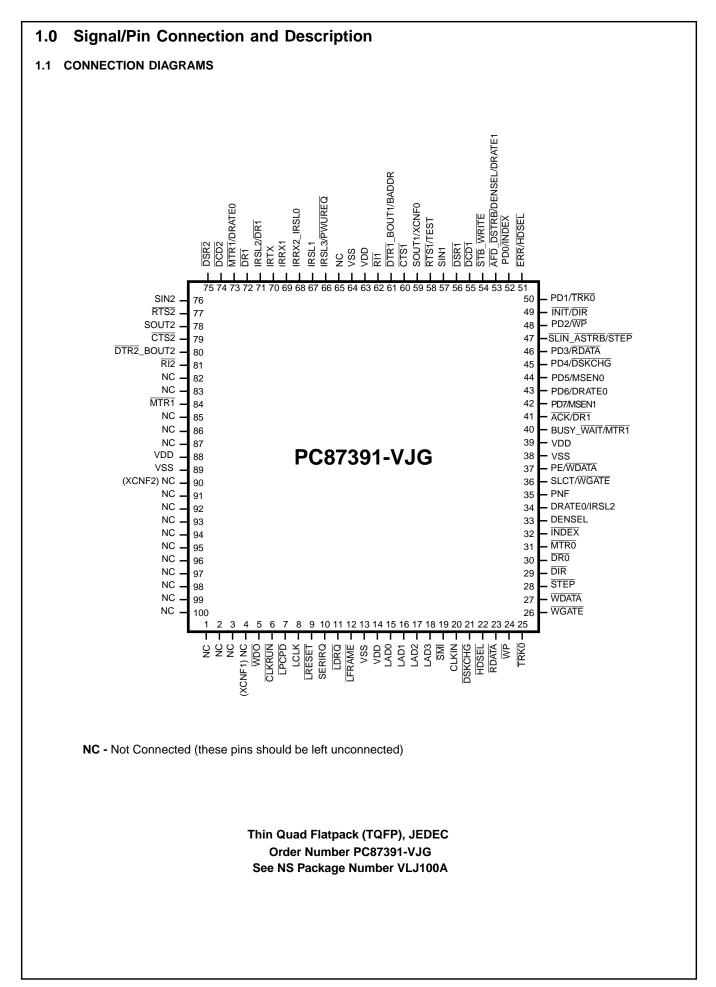

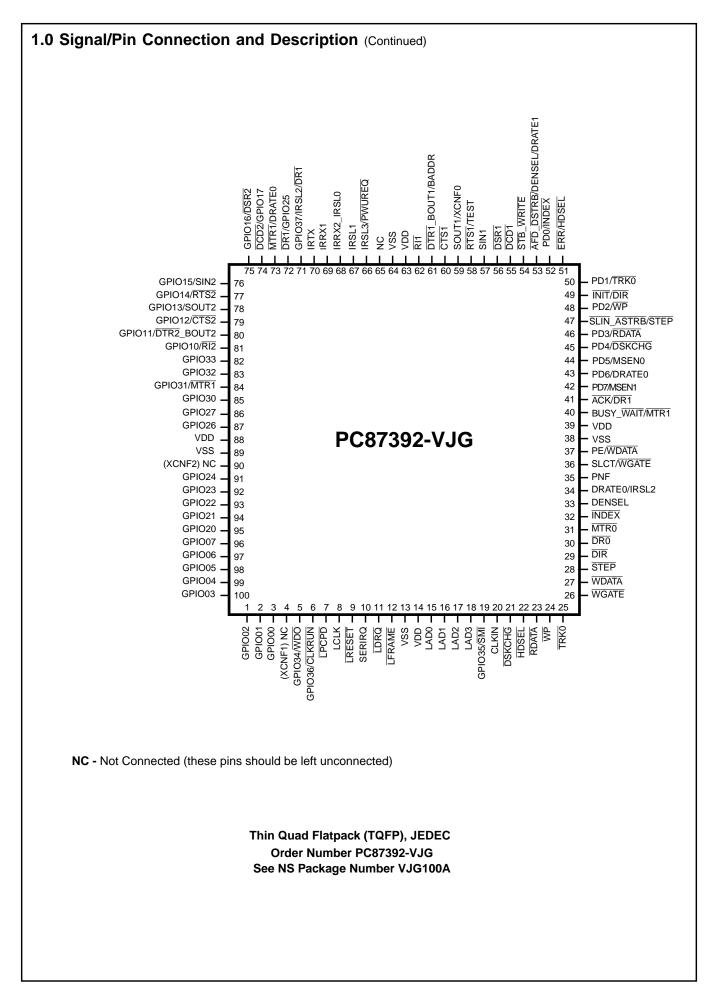

| 1.0 | Sign                                                                                     | al/Pin Connection and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

|-----|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

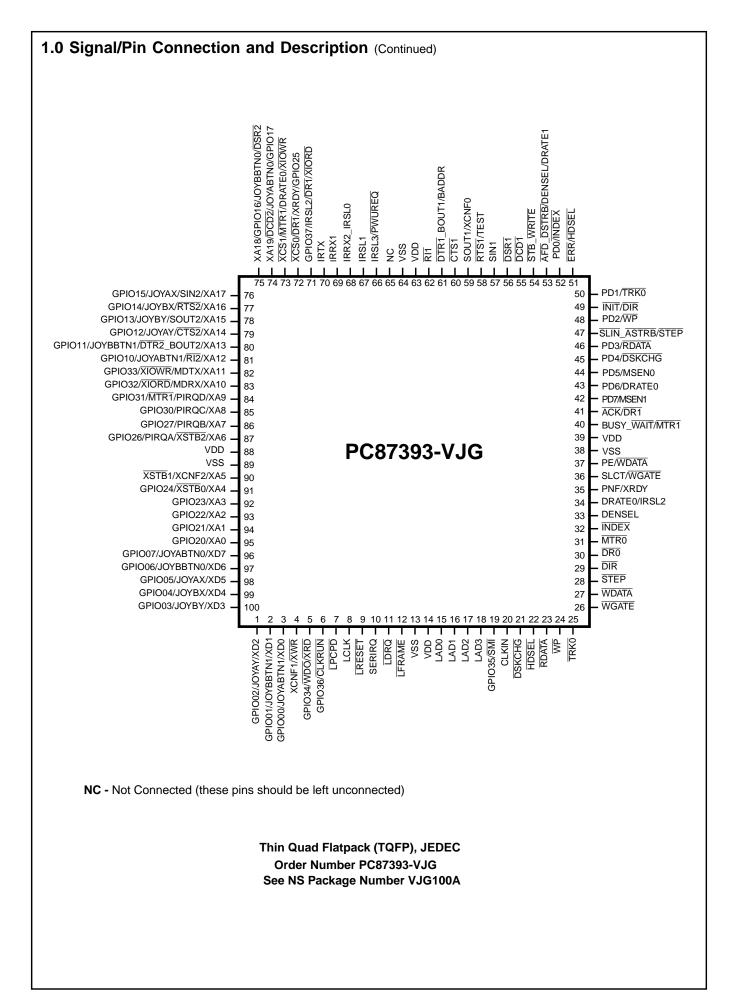

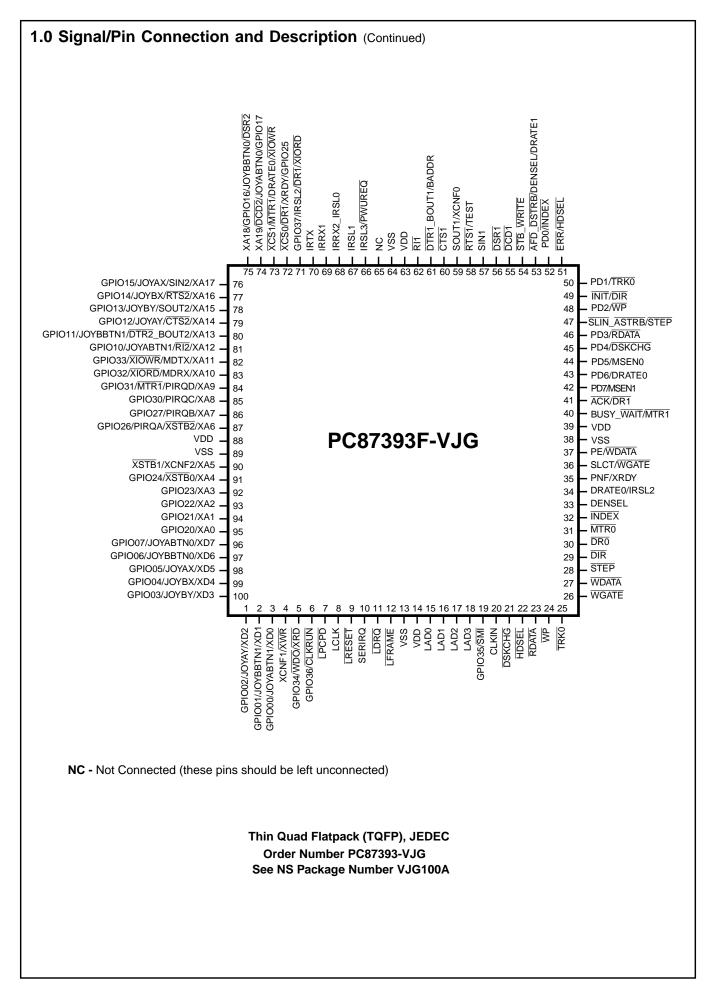

|     | 1.1                                                                                      | CONNECTION DIAGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                                             |

|     | 1.2                                                                                      | BUFFER TYPES AND SIGNAL/PIN DIRECTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                                                                             |

|     | 1.3                                                                                      | PIN MULTIPLEXING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                                                             |

|     | 1.4                                                                                      | PARALLEL PORT MULTIPLEXER (PPM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                             |

|     | 1.5                                                                                      | DETAILED SIGNAL/PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|     |                                                                                          | 1.5.1 Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                             |

|     |                                                                                          | 1.5.2 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

|     |                                                                                          | 1.5.3 Infrared (IR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

|     |                                                                                          | 1.5.4 Floppy Disk Controller (FDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

|     |                                                                                          | 1.5.5 Game Port (PC87393 and PC87393F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|     |                                                                                          | 1.5.6 General-Purpose Input/Output (GPIO) Ports (PC87392, PC87393 and PC87393F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

|     |                                                                                          | <ul> <li>1.5.7 Musical Instrument Digital Interface (MIDI) Port (PC87393 and PC87393F)</li> <li>1.5.8 Parallel Port</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|     |                                                                                          | 1.5.9 Power and Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|     |                                                                                          | 1.5.10 Serial Port 1 and Serial Port 2 (SP1 and SP2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|     |                                                                                          | 1.5.11 Strap Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|     |                                                                                          | 1.5.12 Wake-Up Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|     |                                                                                          | 1.5.13 WATCHDOG Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                                                                             |

|     |                                                                                          | 1.5.14 X-Bus Extension (PC87393 and PC87393F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                             |

|     | 1.6                                                                                      | INTERNAL PULL-UP AND PULL-DOWN RESISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                             |

|     |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| 2.0 | Devi                                                                                     | ce Architecture and Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

| 2.0 | <b>Devi</b><br>2.1                                                                       | ce Architecture and Configuration OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                             |

| 2.0 |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

| 2.0 | 2.1                                                                                      | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26                                                                                                             |

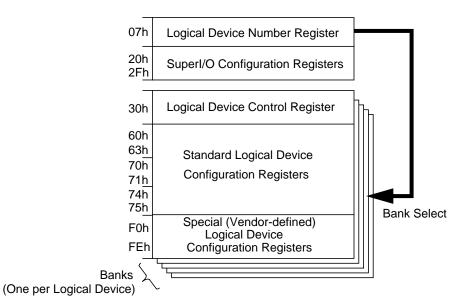

| 2.0 | 2.1                                                                                      | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26<br>26                                                                                                       |

| 2.0 | 2.1                                                                                      | OVERVIEW<br>CONFIGURATION STRUCTURE AND ACCESS<br>2.2.1 The Index-Data Register Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26<br>26<br>28                                                                                                 |

| 2.0 | 2.1                                                                                      | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26<br>26<br>28<br>29<br>31                                                                                     |

| 2.0 | 2.1                                                                                      | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup                                                                                                                                                                                                                                                                                                                                                                                                      | 26<br>26<br>28<br>29<br>31<br>32                                                                               |

| 2.0 | 2.1                                                                                      | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States                                                                                                                                                                                                                                                                                                                                                                     | 26<br>26<br>28<br>29<br>31<br>32<br>32                                                                         |

| 2.0 | 2.1<br>2.2                                                                               | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding                                                                                                                                                                                                                                                                                                                                | 26<br>28<br>29<br>31<br>32<br>32<br>32                                                                         |

| 2.0 | 2.1                                                                                      | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER                                                                                                                                                                                                                                                                                                   | 26<br>28<br>29<br>31<br>32<br>32<br>32<br>33                                                                   |

| 2.0 | 2.1<br>2.2                                                                               | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality                                                                                                                                                                                                                                                                 | 26<br>28<br>29<br>31<br>32<br>32<br>32<br>33<br>33                                                             |

| 2.0 | 2.1<br>2.2                                                                               | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up                                                                                                                                                                                                                               | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33                                                             |

| 2.0 | 2.1<br>2.2                                                                               | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock                                                                                                                                                                                       | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33                                                             |

| 2.0 | 2.1<br>2.2<br>2.3                                                                        | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications                                                                                                                                                    | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33                                                       |

| 2.0 | 2.1<br>2.2<br>2.3<br>2.4                                                                 | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications         INTERRUPT SERIALIZER                                                                                                                       | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33                                           |

| 2.0 | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                          | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications         INTERRUPT SERIALIZER       WAKE-UP CONTROL                                                                                                 | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33                                     |

| 2.0 | 2.1<br>2.2<br>2.3<br>2.4                                                                 | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications         INTERRUPT SERIALIZER       WAKE-UP CONTROL         THE PARALLEL PORT MULTIPLEXER (PPM)                                                     | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34                               |

| 2.0 | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ul> | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications         INTERRUPT SERIALIZER       WAKE-UP CONTROL         THE PARALLEL PORT MULTIPLEXER (PPM)       2.6.1         2.6.1       PPM Power Save Mode | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>35                   |

| 2.0 | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                          | OVERVIEW         CONFIGURATION STRUCTURE AND ACCESS         2.2.1       The Index-Data Register Pair         2.2.2       Banked Logical Device Registers Structure         2.2.3       Standard Logical Device Configuration Register Definitions         2.2.4       Standard Configuration Registers         2.2.5       Default Configuration Setup         2.2.6       Power States         2.2.7       Address Decoding         THE CLOCK MULTIPLIER         2.3.1       Functionality         2.3.2       Chip Power-Up         2.3.3       Disabling the Clock         2.3.4       Specifications         INTERRUPT SERIALIZER       WAKE-UP CONTROL         THE PARALLEL PORT MULTIPLEXER (PPM)                                                     | 26<br>28<br>29<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>36 |

## Table of Contents (Continued)

|      | 2.7.2   | GPIO Pin Function Lock                              |    |

|------|---------|-----------------------------------------------------|----|

| 2.8  | LPC IN  | TERFACE                                             |    |

|      | 2.8.1   | LPC Transactions Supported                          |    |

|      | 2.8.2   | CLKRUN Functionality                                |    |

|      | 2.8.3   | LPCPD Functionality                                 |    |

| 2.9  | REGIS   | TER TYPE ABBREVIATIONS                              |    |

| 2.10 | SUPER   | I/O CONFIGURATION REGISTERS                         | 37 |

|      | 2.10.1  | SuperI/O ID Register (SID)                          |    |

|      | 2.10.2  | SuperI/O Configuration 1 Register (SIOCF1)          |    |

|      | 2.10.3  | SuperI/O Configuration 2 Register (SIOCF2)          |    |

|      | 2.10.4  | SuperI/O Configuration 3 Register (SIOCF3)          |    |

|      | 2.10.5  | SuperI/O Configuration 4 Register (SIOCF4)          |    |

|      | 2.10.6  | SuperI/O Configuration 5 Register (SIOCF5)          |    |

|      | 2.10.7  | Superl/O Configuration 6 Register (SIOCF6)          |    |

|      | 2.10.8  | SuperI/O Revision ID Register (SRID)                |    |

|      | 2.10.9  | SuperI/O Configuration 8 Register (SIOCF8)          |    |

|      |         | SuperI/O Configuration 9 Register (SIOCF9)          |    |

|      | 2.10.11 | SuperI/O Configuration A Register (SIOCFA)          |    |

| 2.11 | FLOPP   | Y DISK CONTROLLER (FDC) CONFIGURATION               | 47 |

|      | 2.11.1  | General Description                                 | 47 |

|      | 2.11.2  | Logical Device 0 (FDC) Configuration                | 47 |

|      | 2.11.3  | FDC Configuration Register                          |    |

|      | 2.11.4  | Drive ID Register                                   |    |

| 2.12 |         | LEL PORT CONFIGURATION                              |    |

|      | 2.12.1  | General Description                                 |    |

|      | 2.12.2  | Logical Device 1 (PP) Configuration                 |    |

|      | 2.12.3  | Parallel Port Configuration Register                |    |

| 2.13 | -       | PORT 2 CONFIGURATION                                |    |

|      | 2.13.1  |                                                     |    |

|      | 2.13.2  | Logical Device 2 (SP2) Configuration                |    |

|      | 2.13.3  | Serial Port 2 Configuration Register                | 54 |

| 2.14 | SERIAL  | PORT 1 CONFIGURATION                                | 55 |

|      | 2.14.1  | Logical Device 3 (SP1) Configuration                |    |

|      | 2.14.2  | Serial Port 1 Configuration Register                | 55 |

| 2.15 | GENER   | RAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION | 56 |

|      | 2.15.1  | General Description                                 | 56 |

|      | 2.15.2  | Implementation                                      | 56 |

|      | 2.15.3  | Logical Device 7 (GPIO) Configuration               | 57 |

|      | 2.15.4  | GPIO Pin Select Register                            | 58 |

|      | 2.15.5  | GPIO Pin Configuration Register                     |    |

|      | 2.15.6  | GPIO Event Routing Register                         | 60 |

| 2.16 | WATCH   | HDOG TIMER (WDT) CONFIGURATION                      | 61 |

|      | 2.16.1  | Logical Device 10 (WDT) Configuration               | 61 |

|      | 2.16.2  | WATCHDOG Timer Configuration Register               | 61 |

## Table of Contents (Continued)

|     | 2.17    |          | PORT (GMP) CONFIGURATION                     |    |

|-----|---------|----------|----------------------------------------------|----|

|     |         | 2.17.1   | Logical Device 11 (GMP) Configuration        |    |

|     |         | 2.17.2   | Game Port Configuration Register             | 62 |

|     | 2.18    | MIDI PC  | ORT (MIDI) CONFIGURATION                     |    |

|     |         | 2.18.1   | Logical Device 12 (MIDI) Configuration       | 64 |

|     |         | 2.18.2   | MIDI Port Configuration Register             | 64 |

|     | 2.19    | X-BUS (  | CONFIGURATION                                | 65 |

|     |         | 2.19.1   | Logical Device 15 (X-Bus) Configuration      | 65 |

|     |         | 2.19.2   | X-Bus I/O Range Programming                  | 65 |

|     |         | 2.19.3   | X-Bus Memory Range Programming               | 66 |

|     |         | 2.19.4   | X-Bus I/O Configuration Register             | 66 |

|     |         | 2.19.5   | X-Bus I/O Base Address High Byte Register    | 68 |

|     |         | 2.19.6   | X-Bus I/O Base Address Low Byte Register     | 68 |

|     |         | 2.19.7   | X-Bus I/O Size Configuration Register        | 68 |

|     |         | 2.19.8   | X-Bus Memory Configuration Register          |    |

|     |         | 2.19.9   | X-Bus Memory Base Address High Byte Register |    |

|     |         |          | X-Bus Memory Base Address Low Byte Register  |    |

|     |         |          | X-Bus Memory Size Configuration Register     |    |

|     |         |          | X-Bus PIRQA and PIRQB Mapping Register       |    |

|     |         | 2.19.13  | X-Bus PIRQC and PIRQD Mapping Register       | 71 |

| 3.0 | Gene    | aral-Pur | pose Input/Output (GPIO) Port                |    |

| 5.0 |         |          |                                              |    |

|     | 3.1     | OVERV    | IEW                                          | 72 |

|     | 3.2     |          | FUNCTIONALITY                                |    |

|     |         | 3.2.1    | Configuration Options                        |    |

|     |         | 3.2.2    | Operation                                    | 73 |

|     | 3.3     | EVENT    | HANDLING AND SYSTEM NOTIFICATION             | 74 |

|     |         | 3.3.1    | Event Configuration                          | 74 |

|     |         | 3.3.2    | System Notification                          | 74 |

|     | 3.4     | GPIO P   | ORT REGISTERS                                | 75 |

|     |         | 3.4.1    | GPIO Pin Configuration (GPCFG) Register      | 76 |

|     |         | 3.4.2    | GPIO Pin Event Routing (GPEVR) Register      | 77 |

|     |         | 3.4.3    | GPIO Port Runtime Register Map               | 77 |

|     |         | 3.4.4    | GPIO Data Out Register (GPDO)                | 78 |

|     |         | 3.4.5    | GPIO Data In Register (GPDI)                 | 78 |

|     |         | 3.4.6    | GPIO Event Enable Register (GPEVEN)          | 79 |

|     |         | 3.4.7    | GPIO Event Status Register (GPEVST)          | 79 |

|     | \A/ A T |          |                                              |    |

| 4.0 | WAI     |          | G Timer (WDT)                                |    |

|     | 4.1     | OVERV    | IEW                                          | 80 |

|     | 4.2     | FUNCTI   | IONAL DESCRIPTION                            | 80 |

|     | 4.3     | WATCH    | IDOG TIMER REGISTERS                         | 81 |

|     |         | 4.3.1    | WATCHDOG Timer Register Map                  | 81 |

|     |         | 4.3.2    | WATCHDOG Timeout Register (WDTO)             |    |

|     |         | 4.3.3    | WATCHDOG Mask Register (WDMSK)               |    |

| Tabl | e of C | Contents (Continued)                                                                                                        |       |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------|-------|

|      |        | 4.3.4 WATCHDOG Status Register (WDST)                                                                                       | 83    |

|      | 4.4    |                                                                                                                             |       |

|      | 0      |                                                                                                                             |       |

| 5.0  |        | ne Port (GMP)                                                                                                               |       |

|      | 5.1    | OVERVIEW                                                                                                                    | 84    |

|      | 5.2    | FUNCTIONAL DESCRIPTION                                                                                                      |       |

|      |        | 5.2.1 Game Device Axis Position Indication                                                                                  | -     |

|      |        | 5.2.2 Capturing the Position                                                                                                |       |

|      |        | 5.2.3 Button Status Indication                                                                                              |       |

|      |        | 5.2.4 Operation Modes                                                                                                       |       |

|      |        | 5.2.5 Operation Control                                                                                                     |       |

|      | 5.3    | GAME PORT REGISTERS                                                                                                         |       |

|      |        | 5.3.1 Game Port Register Map                                                                                                |       |

|      |        | <ul> <li>5.3.2 Game Port Control Register (GMPCTL)</li> <li>5.3.3 Game Port Legacy Status Register (GMPLST)</li> </ul>      |       |

|      |        | <ul><li>5.3.3 Game Port Legacy Status Register (GMPLST)</li><li>5.3.4 Game Port Extended Status Register (GMPXST)</li></ul> |       |

|      |        | 5.3.5 Game Port Interrupt Enable Register (GMP/ST)                                                                          |       |

|      |        | 5.3.6 Game Device A X-Axis Position Low Byte (GMPAXL)                                                                       |       |

|      |        | 5.3.7 Game Device A X-Axis Position High Byte (GMPAXH)                                                                      |       |

|      |        | 5.3.8 Game Device A Y-Axis Position Low Byte (GMPAYL)                                                                       |       |

|      |        | 5.3.9 Game Device A Y-Axis Position High Byte (GMPAYH)                                                                      |       |

|      |        | 5.3.10 Game Device B X-Axis Position Low Byte (GMPBXL)                                                                      |       |

|      |        | 5.3.11 Game Device B X-Axis Position High Byte (GMPBXH)                                                                     |       |

|      |        | 5.3.12 Game Device B Y-Axis Position Low Byte (GMPBYL)                                                                      | 93    |

|      |        | 5.3.13 Game Device B Y-Axis Position High Byte (GMPBYH)                                                                     | 93    |

|      |        | 5.3.14 Game Port Event Polarity Register (GMPEPOL)                                                                          | 94    |

|      | 5.4    | GAME PORT BITMAP                                                                                                            | 95    |

| 6.0  | Mus    | ical Instrument Digital Interface (MIDI) Port                                                                               |       |

|      | 6.1    | OVERVIEW                                                                                                                    | 96    |

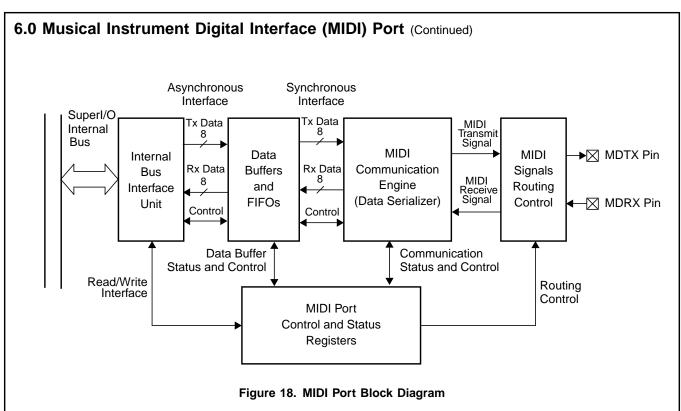

|      | 6.2    | FUNCTIONAL DESCRIPTION                                                                                                      | 96    |

|      | •      | 6.2.1 Internal Bus Interface Unit                                                                                           |       |

|      |        | 6.2.2 Port Control and Status Registers                                                                                     |       |

|      |        | 6.2.3 Data Buffers and FIFOs                                                                                                |       |

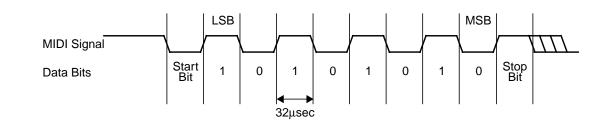

|      |        | 6.2.4 MIDI Communication Engine                                                                                             | 97    |

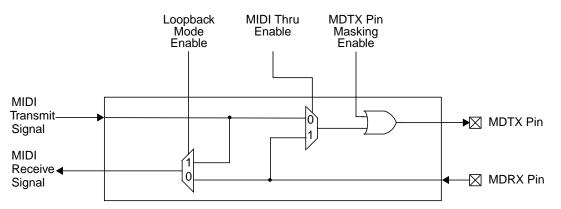

|      |        | 6.2.5 MIDI Signals Routing Control Logic                                                                                    | 98    |

|      |        | 6.2.6 Operation Modes                                                                                                       | 98    |

|      |        | 6.2.7 MIDI Port Status Flags                                                                                                | 99    |

|      |        | 6.2.8 MIDI Port Interrupts                                                                                                  |       |

|      |        | 6.2.9 Enhanced MIDI Port Features                                                                                           | . 101 |

|      | 6.3    | MIDI PORT REGISTERS                                                                                                         | .102  |

|      |        | 6.3.1 MIDI Port Register Map                                                                                                | .102  |

|      |        | 6.3.2 MIDI Data In Register (MDI)                                                                                           |       |

|      |        | 6.3.3 MIDI Data Out Register (MDO)                                                                                          |       |

|      |        | 6.3.4 MIDI Status Register (MSTAT)                                                                                          | . 103 |

| Tabl | e of C | Contents (Continued)                                                                                                                   |     |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

|      |        | <ul><li>6.3.5 MIDI Command Register (MCOM)</li><li>6.3.6 MIDI Control Register (MCNTL)</li></ul>                                       | 104 |

|      | 6.4    | MIDI PORT BITMAP                                                                                                                       | 105 |

| 7.0  | Χ-Βι   | us Extension                                                                                                                           |     |

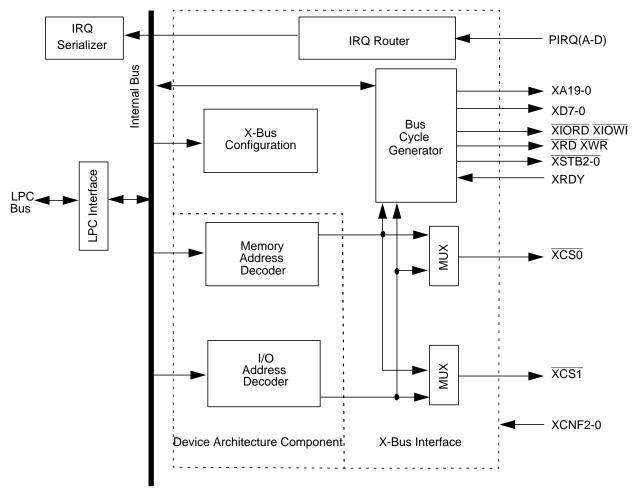

|      | 7.1    | OVERVIEW                                                                                                                               | 106 |

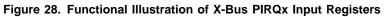

|      | 7.2    | IRQ ROUTING                                                                                                                            | 106 |

|      | 7.3    | X-BUS TRANSACTIONS                                                                                                                     |     |

|      |        | <ul> <li>7.3.1 Programmable I/O Range Chip Select</li> <li>7.3.2 LPC and FWH Address to X-Bus Address Translation</li> </ul>           |     |

|      |        | 7.3.3 Extended Read/Write Signal Mode                                                                                                  |     |

|      |        | 7.3.4 Indirect Memory Read and Write Transaction                                                                                       |     |

|      |        | 7.3.5 Normal Address Mode X-Bus Transactions                                                                                           |     |

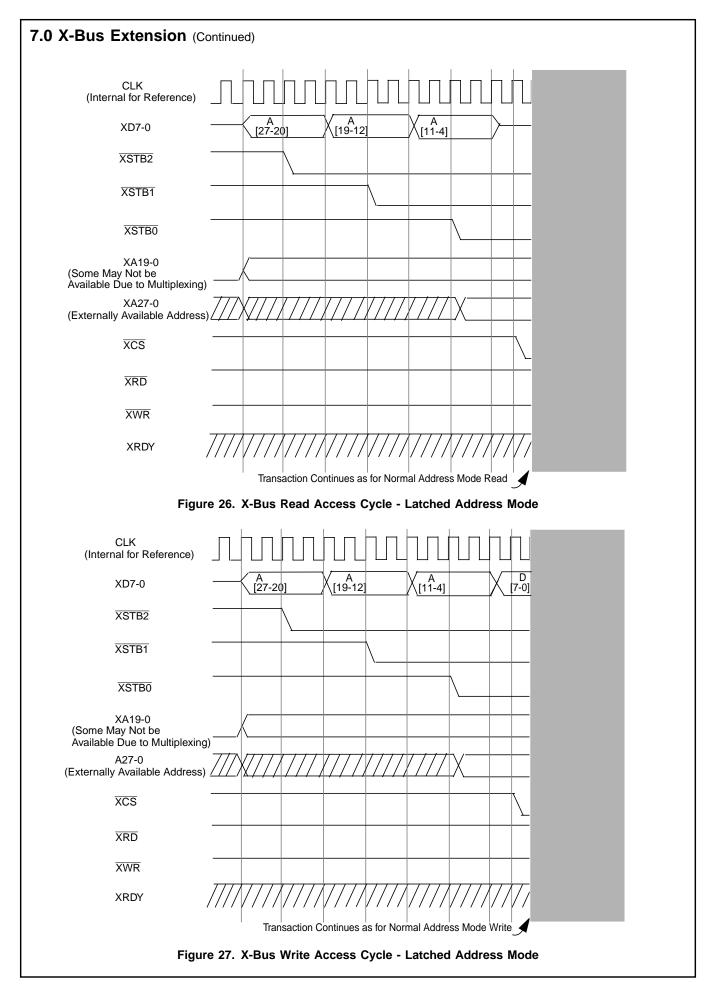

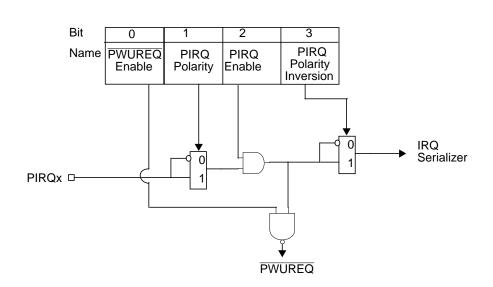

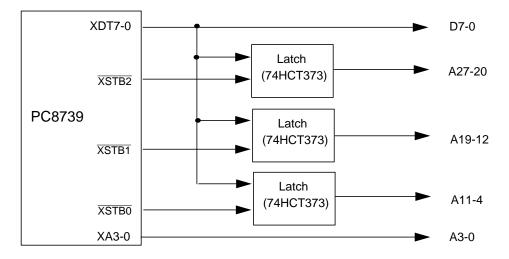

|      |        | 7.3.6 Latched Address Mode X-Bus Transactions                                                                                          | 110 |

|      | 7.4    | X-BUS CONFIGURATION REGISTERS                                                                                                          | 112 |

|      |        | 7.4.1 X-Bus Register Map                                                                                                               |     |

|      |        | 7.4.2 X-Bus Configuration Register (XBCNF)                                                                                             |     |

|      |        | <ul> <li>7.4.3 X-Bus Select 0 Configuration Register (XZCNF0)</li> <li>7.4.4 X-Bus Select 1 Configuration Register (XZCNF1)</li> </ul> |     |

|      |        | 7.4.4 X-Bus Select 1 Connigulation Register (XZCNF1)                                                                                   |     |

|      |        | 7.4.6 X-Bus Indirect Memory Address Register 0 (XIMA0)                                                                                 |     |

|      |        | 7.4.7 X-Bus Indirect Memory Address Register 1 (XIMA1)                                                                                 |     |

|      |        | 7.4.8 X-Bus Indirect Memory Address Register 2 (XIMA2)                                                                                 | 118 |

|      |        | 7.4.9 X-Bus Indirect Memory Address Register 3 (XIMA3)                                                                                 |     |

|      |        | 7.4.10 X-Bus Indirect Memory Data Register (XIMD)                                                                                      |     |

|      | 7.5    | USAGE HINTS                                                                                                                            | 118 |

|      | 7.6    | X-BUS EXTENSION BITMAP                                                                                                                 | 120 |

| 8.0  | Lega   | acy Functional Blocks                                                                                                                  |     |

|      | 8.1    | FLOPPY DISK CONTROLLER (FDC)                                                                                                           | 121 |

|      |        | 8.1.1 General Description                                                                                                              |     |

|      |        | 8.1.2 FDC Register Map                                                                                                                 |     |

|      |        | 8.1.3 FDC Bitmap Summary                                                                                                               |     |

|      | 8.2    |                                                                                                                                        |     |

|      |        | <ul><li>8.2.1 General Description</li><li>8.2.2 Parallel Port Register Map</li></ul>                                                   |     |

|      |        | 8.2.3 Parallel Port Bitmap Summary                                                                                                     |     |

|      | 8.3    | UART FUNCTIONALITY (SP1 AND SP2)                                                                                                       |     |

|      | 2.2    | 8.3.1 General Description                                                                                                              |     |

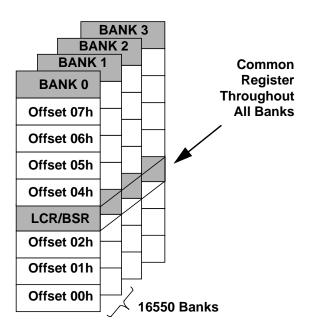

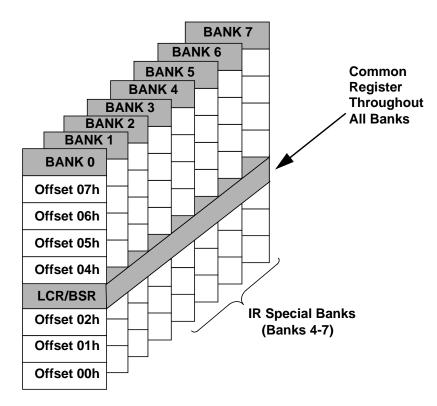

|      |        | 8.3.2 UART Mode Register Bank Overview                                                                                                 |     |

|      |        | 8.3.3 SP1 and SP2 Register Maps for UART Functionality                                                                                 |     |

|      |        | 8.3.4 SP1 and SP2 Bitmap Summary for UART Functionality                                                                                | 129 |

|      | 8.4    | IR FUNCTIONALITY (SP2)                                                                                                                 |     |

|      |        | 8.4.1 General Description                                                                                                              | 131 |

| Tabl | e of C | Content | S (Continued)                                                 |     |

|------|--------|---------|---------------------------------------------------------------|-----|

|      |        | 8.4.2   | IR Mode Register Bank Overview                                | 131 |

|      |        | 8.4.3   | SP2 Register Map for IR Functionality                         | 132 |

|      |        | 8.4.4   | SP2 Bitmap Summary for IR Functionality                       | 133 |

| 9.0  | Devi   | ice Cha | racteristics                                                  |     |

|      | 9.1    | GENER   | RAL DC ELECTRICAL CHARACTERISTICS                             | 135 |

|      |        | 9.1.1   | Recommended Operating Conditions                              | 135 |

|      |        | 9.1.2   | Absolute Maximum Ratings                                      | 135 |

|      |        | 9.1.3   | Capacitance                                                   | 135 |

|      |        | 9.1.4   | Power Consumption under Recommended Operating Conditions      | 135 |

|      | 9.2    | DC CH   | ARACTERISTICS OF PINS, BY I/O BUFFER TYPES                    | 135 |

|      |        | 9.2.1   | Input, CMOS Compatible                                        | 136 |

|      |        | 9.2.2   | Input, PCI 3.3V                                               | 136 |

|      |        | 9.2.3   | Input, Strap Pin                                              | 136 |

|      |        | 9.2.4   | Input, TTL Compatible                                         | 136 |

|      |        | 9.2.5   | Input, TTL Compatible with Schmitt Trigger                    | 137 |

|      |        | 9.2.6   | Output, PCI 3.3V                                              |     |

|      |        | 9.2.7   | Output, Totem-Pole Buffer                                     |     |

|      |        | 9.2.8   | Output, Open-Drain Buffer                                     |     |

|      |        | 9.2.9   | Exceptions                                                    | 137 |

|      | 9.3    | INTER   | NAL RESISTORS                                                 | 138 |

|      |        | 9.3.1   | Pull-Up Resistor                                              | 138 |

|      |        | 9.3.2   | Pull-Down Resistor                                            | 138 |

|      | 9.4    | AC ELE  | ECTRICAL CHARACTERISTICS                                      | 139 |

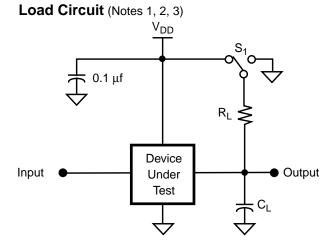

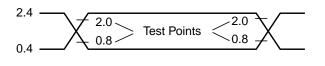

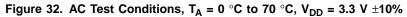

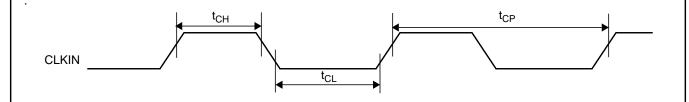

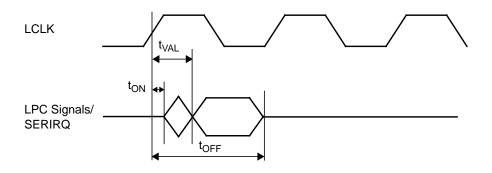

|      |        | 9.4.1   | AC Test Conditions                                            | 139 |

|      |        | 9.4.2   | Clock Timing                                                  | 139 |

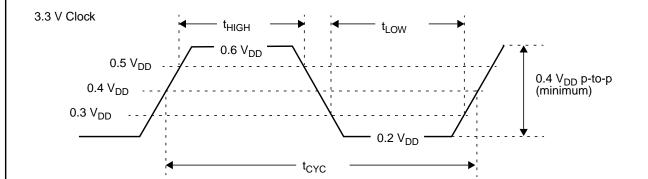

|      |        | 9.4.3   | LCLK and LRESET                                               | 140 |

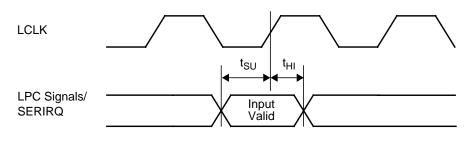

|      |        | 9.4.4   | LPC and SERIRQ Signals                                        |     |

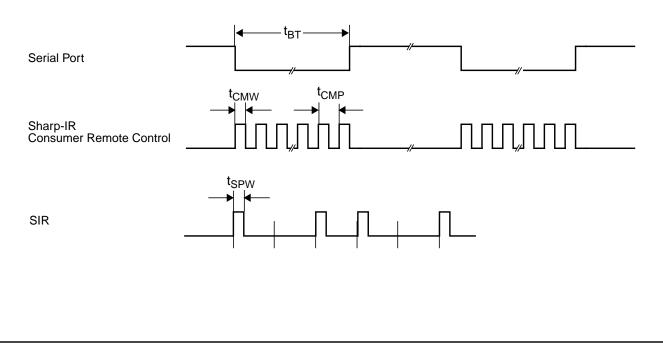

|      |        | 9.4.5   | Serial Port, Sharp-IR, SIR and Consumer Remote Control Timing | 142 |

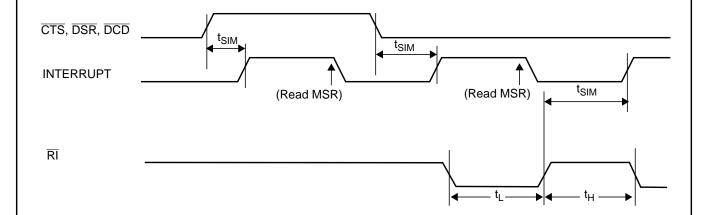

|      |        | 9.4.6   | Modem Control Timing                                          | 143 |

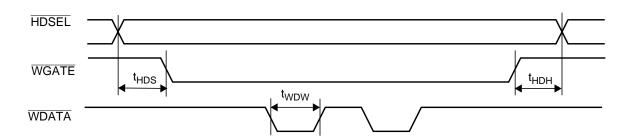

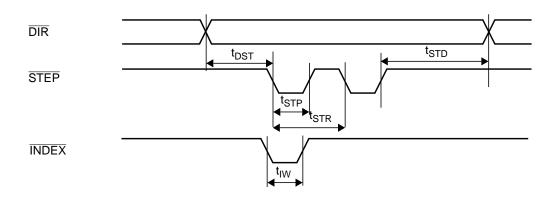

|      |        | 9.4.7   | FDC Write Data Timing                                         | 143 |

|      |        | 9.4.8   | FDC Drive Control Timing                                      | 144 |

|      |        | 9.4.9   | FDC Read Data Timing                                          | 144 |

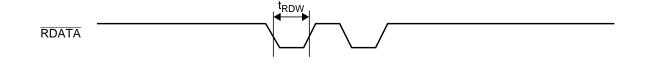

|      |        | 9.4.10  | Standard Parallel Port Timing                                 |     |

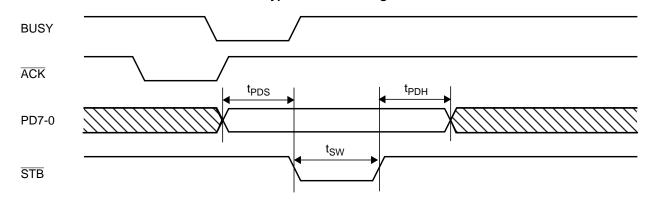

|      |        | 9.4.11  | Enhanced Parallel Port Timing                                 |     |

|      |        | 9.4.12  | Extended Capabilities Port (ECP) Timing                       |     |

|      |        | 9.4.13  | X-Bus Signals (PC87393 and PC87393F only)                     | 147 |

#### 1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY

The signal DC characteristics are denoted by a buffer type symbol, described briefly below and in further detail in Section 9.2. The pin multiplexing information refers to three different types of multiplexing:

- Multiplexed, denoted by a slash (/) between pins in the diagram in Section 1.1. Pins are shared between two different functions. Each function is associated with different board connectivity, and normally, the function selection is determined by the board design and cannot be changed dynamically. The multiplexing options must be configured by the BIOS upon power-up, in order to comply with the board implementation.

- Multiple Mode, denoted by an underscore (\_) between pins in the diagram in Section 1.1. Pins have two or more modes of operation within the same function. These modes are associated with the same external (board) connectivity. Mode selection may be controlled by the device driver, through the registers of the functional block, and do not require a special BIOS setup upon power-up. These pins are not considered multiplexed pins from the SuperI/O configuration perspective. The mode selection method (registers and bits) as well as the signal specification in each mode, are described within the functional description of the relevant functional block.

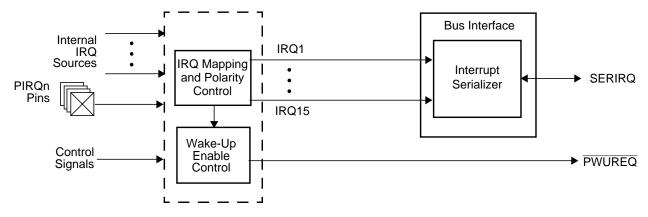

- Parallel Port Multiplexer, denoted by a slash (/) between pins in the diagram in Section 1.1. Parallel Port pins can be used to support external Floppy Disk Controller signals when the PPM is enabled and bit 7 of the SuperI/O Configuration 5 register (SIOCF5) is cleared. See Table 3 for a summary of all PPM options.

| Symbol             | Description                                                                    |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| IN <sub>C</sub>    | Input, CMOS compatible                                                         |  |  |  |  |  |

| IN <sub>PCI</sub>  | put, PCI 3.3V                                                                  |  |  |  |  |  |

| IN <sub>STRP</sub> | nput, Strap pin with weak pull-down during strap time                          |  |  |  |  |  |

| IN <sub>T</sub>    | Input, TTL compatible                                                          |  |  |  |  |  |

| IN <sub>TS</sub>   | Input, TTL compatible with Schmidt Trigger                                     |  |  |  |  |  |

| O <sub>PCI</sub>   | Output, PCI 3.3V                                                               |  |  |  |  |  |

| O <sub>p/n</sub>   | Output, push-pull buffer that is capable of sourcing $p$ mA and sinking $n$ mA |  |  |  |  |  |

| OD <sub>n</sub>    | Output, open-drain output buffer that is capable of sinking <i>n</i> mA        |  |  |  |  |  |

| PWR                | Power pin                                                                      |  |  |  |  |  |

| GND                | Ground pin                                                                     |  |  |  |  |  |

#### Table 1. Buffer Types

#### **1.3 PIN MULTIPLEXING**

Table 2 groups all multiplexed PC8739x pins in their associated functional blocks, and provides links to the relevant configuration registers and bit values for selecting multiplexed options.

| Functional<br>Block | Signal | Functional<br>Block | Signal | Functional<br>Block | Signal   | Functional<br>Block | Signal | Config<br>Section |

|---------------------|--------|---------------------|--------|---------------------|----------|---------------------|--------|-------------------|

| GPIO                | GPIO00 | X-Bus               | XD0    | Game Port           | JOYABTN1 |                     |        | 2.10.3            |

| GPIO                | GPIO01 | X-Bus               | XD1    | Game Port           | JOYBBTN1 |                     |        | 2.10.3            |

| GPIO                | GPIO02 | X-Bus               | XD2    | Game Port           | JOYAY    |                     |        | 2.10.3            |

| GPIO                | GPIO03 | X-Bus               | XD3    | Game Port           | JOYBY    |                     |        | 2.10.3            |

| GPIO                | GPIO04 | X-Bus               | XD4    | Game Port           | JOYBX    |                     |        | 2.10.3            |

| GPIO                | GPIO05 | X-Bus               | XD5    | Game Port           | JOYAX    |                     |        | 2.10.3            |

| GPIO                | GPIO06 | X-Bus               | XD6    | Game Port           | JOYBBTN0 |                     |        | 2.10.3            |

Table 2. Pin Multiplexing Configuration

| Functional<br>Block | Signal     | Functional<br>Block | Signal | Functional<br>Block | Signal     | Functional<br>Block | Signal   | Config<br>Section |

|---------------------|------------|---------------------|--------|---------------------|------------|---------------------|----------|-------------------|

| GPIO                | GPIO07     | X-Bus               | XD7    | Game Port           | JOYABTN0   |                     |          | 2.10.3            |

| GPIO                | GPIO10     | X-Bus               | XA12   | Serial Port         | RI2        | Game Port           | JOYABTN1 | 2.10.3            |

| GPIO                | GPIO11     | X-Bus               | XA13   | Serial Port         | DTR2_BOUT2 | Game Port           | JOYBBTN1 | 2.10.3            |

| GPIO                | GPIO12     | X-Bus               | XA14   | Serial Port         | CTS2       | Game Port           | JOYAY    | 2.10.3            |

| GPIO                | GPIO13     | X-Bus               | XA15   | Serial Port         | SOUT2      | Game Port           | JOYBY    | 2.10.3            |

| GPIO                | GPIO14     | X-Bus               | XA16   | Serial Port         | RTS2       | Game Port           | JOYBX    | 2.10.3            |

| GPIO                | GPIO15     | X-Bus               | XA17   | Serial Port         | SIN2       | Game Port           | JOYAX    | 2.10.3            |

| GPIO                | GPIO16     | X-Bus               | XA18   | Serial Port         | DSR2       | Game Port           | JOYBBTN0 | 2.10.3            |

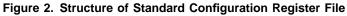

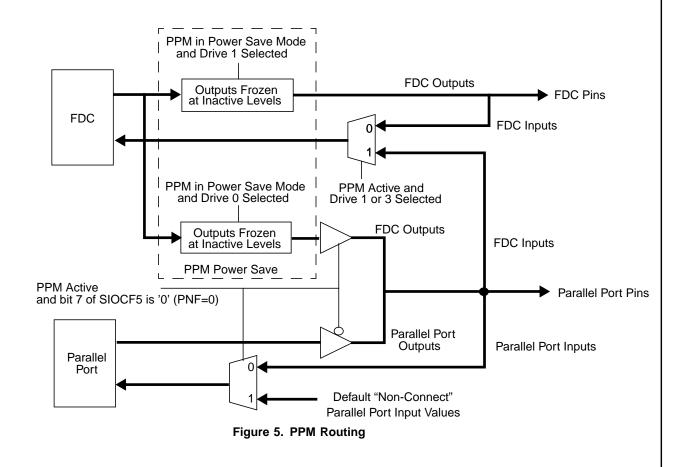

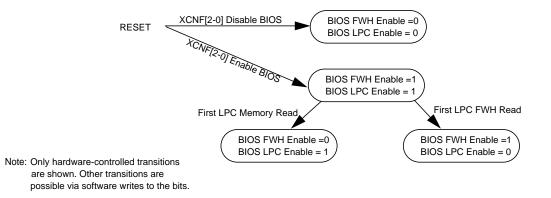

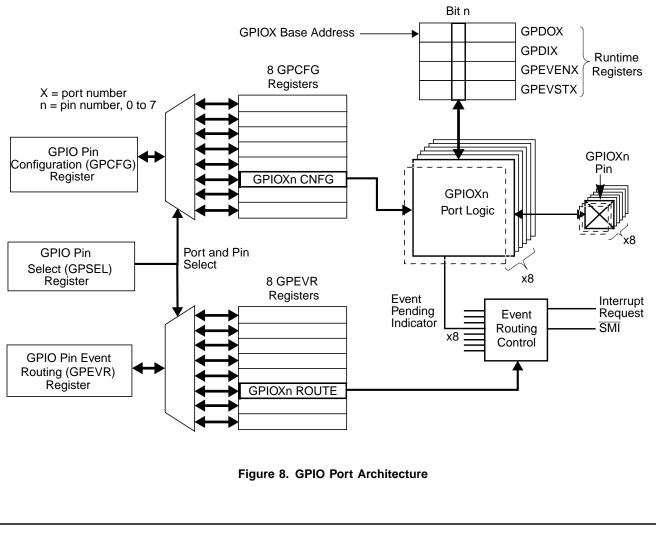

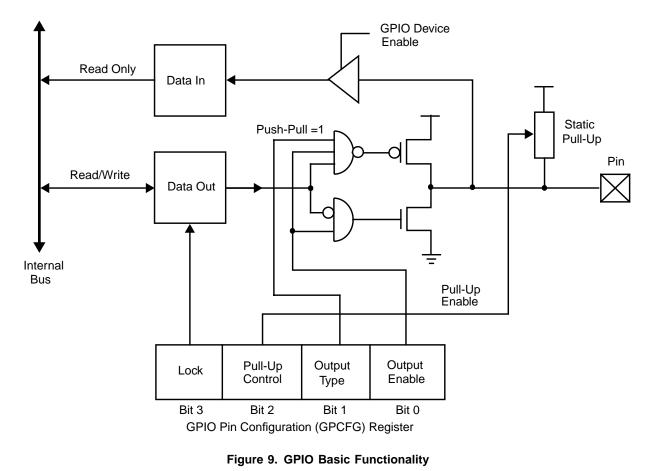

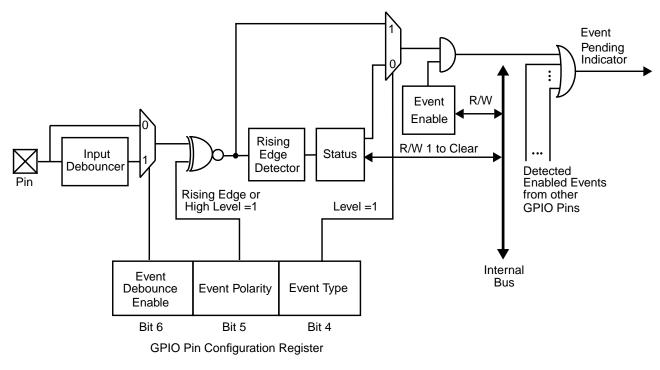

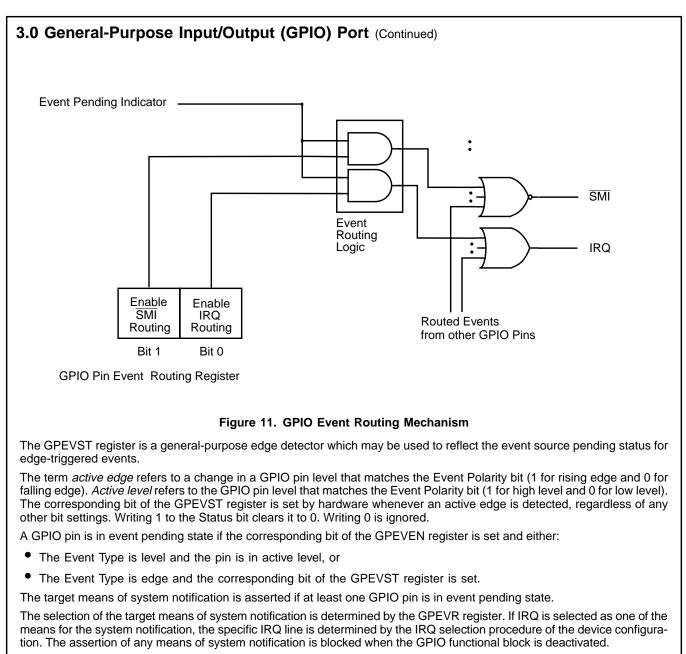

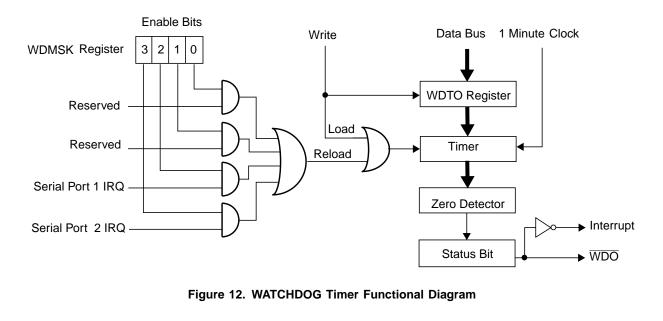

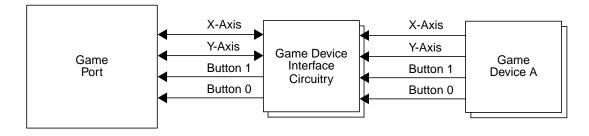

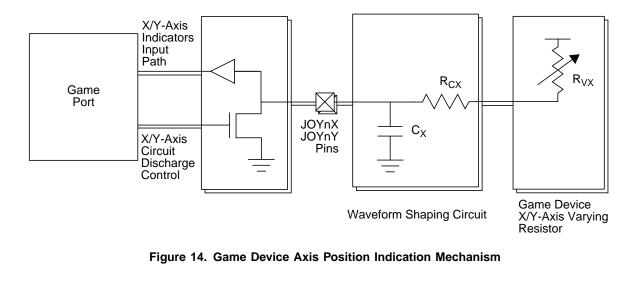

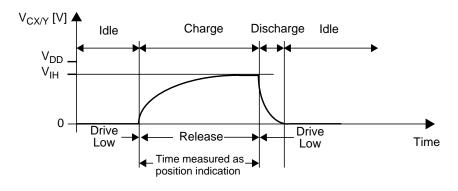

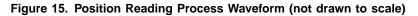

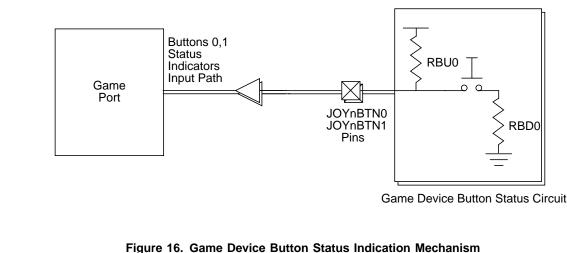

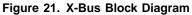

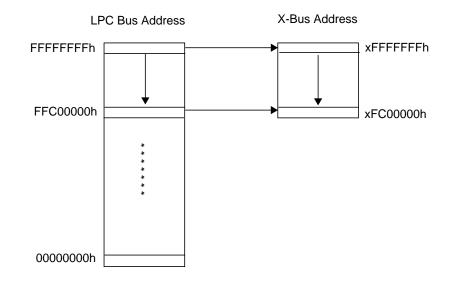

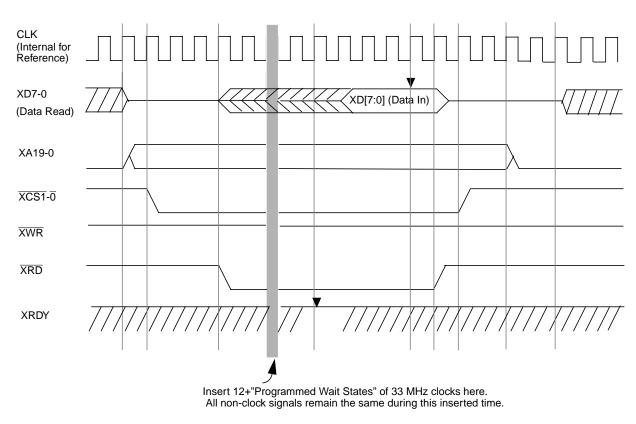

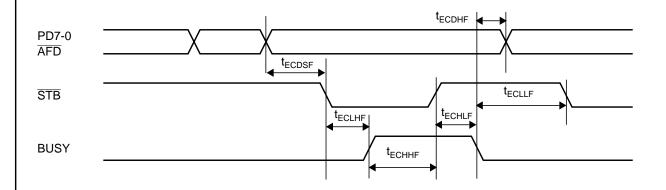

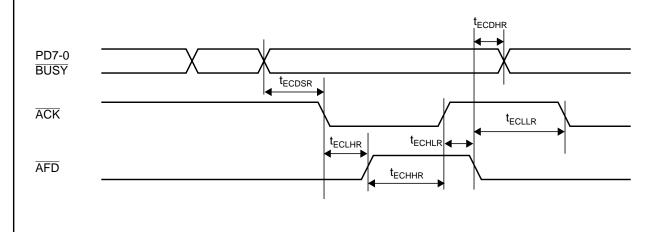

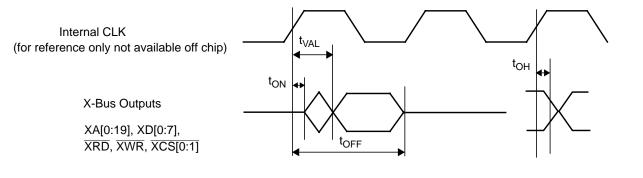

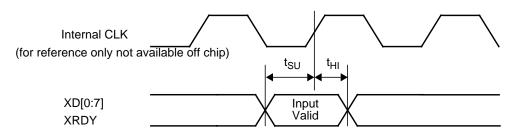

| GPIO                | GPIO17     | X-Bus               | XA19   | Serial Port         | DCD2       | Game Port           | JOYABTN0 | 2.10.3            |