# C8254 Programmable Timer/Counter Megafunction

# Introduction

The C8254 programmable interval timer/counter megafunction is a high-performance device, which is designed to solve the common timing control problems in microcomputer system design. It provides three independent 16-bit counters, and each counter may operate in a different mode. All modes are software programmable. Six programmable timer modes allow the device to be used as an event counter, elapsed time indicator, programmable one-shot, and in many other applications.

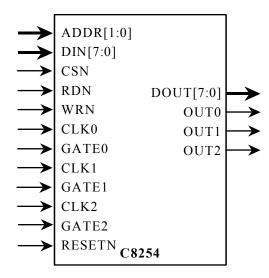

# **Symbol**

# **Applications**

The six programmable timer modes allow the C8254 to be used in applications requiring event counters, elapsed time indicators, and programmable one-shots among others.

### **Features**

- Three Independent 16-bit Counters

- Status Read-Back Command

- Counter Latch Command

- Read/Write LSB only or MSB only or LSB first then MSB

- Six Programmable Counter Modes

- Interrupt on Terminal Count

- Hardware Retriggerable One-Shot

- Rate Generator

- Square Wave Mode

- Software Triggered Strobe

- Hardware Triggered Strobe (Retriggerable)

- Binary or BCD Counting

- Also available in VHDL or Verilog

- Functionality based on the INTEL 8254

# **Pin Description**

| Name      | Type | Polarity | Description              |

|-----------|------|----------|--------------------------|

| DIN[7:0]  | In   | -        | Data Bus Input           |

| ADDR[1:0] | In   | -        | Address                  |

| CSN       | In   | Low      | Chip Select              |

| RDN       | In   | Low      | Read Control             |

| WRN       | In   | Low      | Write Control            |

| RESETN    | In   | Low      | Reset internal Registers |

| CLK0      | In   | Falling  | Clock input of Counter 0 |

| GATE0     | In   | -        | Gate input of Counter 0  |

| CLK1      | In   | Falling  | Clock input of Counter 1 |

| GATE1     | In   | -        | Gate input of Counter 1  |

| CLK2      | In   | Falling  | Clock input of Counter 2 |

| GATE2     | In   | -        | Gate input of Counter 2  |

| OUT0      | Out  | -        | Output of Counter 0      |

| OUT1      | Out  | -        | Output of Counter 1      |

| OUT2      | Out  | -        | Output of Counter 2      |

| DOUT[7:0] | Out  | -        | Data Bus Output          |

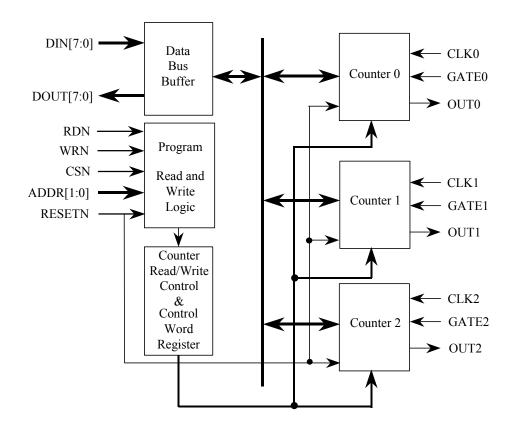

# **Block Diagram**

Figure 1 – Block Diagram

# **Functional Description**

This section provides a short description of each element of the Block Diagram (Figure 1).

#### **Data Bus Buffer**

8-bit input and output data bus buffer is used to interface the C8254 to the system bus.

# **Read/Write Logic**

The Read/Write Logic accepts inputs from the system bus and generates control signals for the other functional blocks of the C8254. ADDR[1:0]select one of the three counters or the control word register to be read from or written into. A "low" on RDN tells the C8254 that the CPU is reading one of the counters. A "low" on the WRN input tells the C8254 that the CPU is writing either a Control Word or an initial count. Both RDN and WRN are qualified by CSN. RDN and WRN are ignored unless the C8254 has been selected by holding CSN "low".

## **Control Word Register**

The Control Word Register is selected by the Read/Write Logic when ADDR[1:0] = 11. During writing, the data is stored in the Control Word Register and it is interpreted as a Control Word used to define the operation of the Counters.

#### **Control Word Format**

| D7  | D6  | D5  | D4  | D3 | D2 | D1 | D0  |

|-----|-----|-----|-----|----|----|----|-----|

| SC1 | SC0 | RW1 | RW0 | M2 | M1 | M0 | BCD |

| SC1 | SC0 |                   |

|-----|-----|-------------------|

| 0   | 0   | Select Counter 0  |

| 0   | 1   | Select Counter 1  |

| 1   | 0   | Select Counter 2  |

| 1   | 1   | Read-Back Command |

| RW1 | RW0 |                                |

|-----|-----|--------------------------------|

| 0   | 0   | Counter Latch Command          |

| 0   | 1   | Read/Write LSB only            |

| 1   | 0   | Read/Write MSB only            |

| 1   | 1   | Read/Write LSB first, then MSB |

| M2 | M1 | M0 |        |

|----|----|----|--------|

| 0  | 0  | 0  | Mode 0 |

| 0  | 0  | 1  | Mode 1 |

| Χ  | 1  | 0  | Mode 2 |

| Χ  | 1  | 1  | Mode 3 |

| 1  | 0  | 0  | Mode 4 |

| 1  | 0  | 1  | Mode 5 |

| BCD |                         |

|-----|-------------------------|

| 0   | Binary Counter 16-bits  |

| 1   | BCD Counter (4 Decades) |

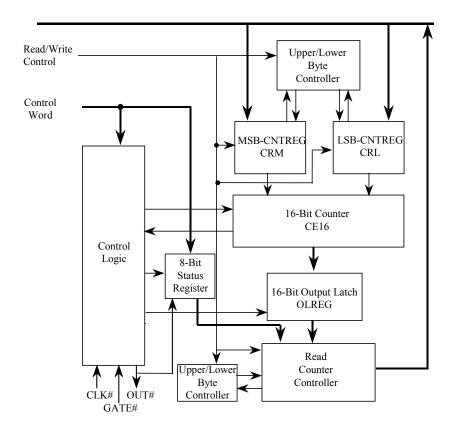

Figure 2 – Internal Counter Block Diagram

#### Counter 0, Counter 1, Counter 2

These three functional blocks are identical in operation, so only a single Counter will be described. The internal block diagram of a single counter is shown in Figure 2. The Counters are fully independent. Each Counter may operate in a different Mode.

#### **Control Logic**

This block controls the 16-bit counter for all counting modes and the Null flag of the counter.

## **Upper/Lower Byte Controller**

The width of the data bus is 8 bits, and the counter is 16 bits. The Upper/Lower Byte Controller allows one 8-bit Counter Register, MSB or LSB, to be loaded one at a time from the internal bus. If the Counter is programmed for two-byte read/write mode, this block will control which data byte will be read at the next read cycle.

#### **Counter Registers**

There are two 8-bit registers called CRM and CRL. Both are normally referred to as one unit and called just CR. When a new count is written to the Counter, the count is stored in the CR and later transferred to the CE16. At the rising-edge of WRN, it will write data to the register. One register at a time will be allowed to be loaded from the internal bus. After both registers have been loaded, both bytes are transferred to the CE16 simultaneously. CRM and CRL are cleared when the Counter is programmed.

Note that the CE16 can't be written into; whenever a count is written, it is written into the CR.

#### **16-Bit Counter**

This block contains a 16-bit Binary or BCD presettable synchronous down counter.

#### 8-Bit Status Register

The 8-bit Status Register contains the Control Word Register, the status of the output and null count flag. When there is a Read-Back Command with STATUSN bit enabled and its counter selected, it will latch present status information into Status Register. The status format is shown below:

| D7  | D6         | D5  | D4  | D3 | D2 | D1 | D0  |

|-----|------------|-----|-----|----|----|----|-----|

| Out | Null Count | RW1 | RW0 | M2 | M1 | M0 | BCD |

Bits D5 through D0 contain the counter's programmed Mode. Output bit D7 contains the current state of the OUT pin. This allows the user to monitor the counter's output via software. Null Count bit D6 indicates when the last count written to the counter register has been loaded into the counting element (CE16). The exact time this happens depends on the Mode of the counter.

# **8-Bit Output Latch Register**

At the time of receiving the Counter Latch Command or Read-Back Command with COUNTN bit enabled, the selected counter's output latch latches the count. This count is held in the latch until the CPU reads it or until the counter is reprogrammed. The count is then unlatched and the OL returns to be transparent of counting element outputs. The count must be read according to the programmed format. The Counter Latch Command is ignored before the count is read.

#### **Read Counter**

If both the count and the status of a counter are latched, the first read operation of that counter will return the latched status, regardless of which was latched first. The next one or two reads (depending on whether the counter is programmed for one or two byte counts) returns the latched count. Subsequent reads return the unlatched count. If the counter is programmed for two byte counts, it will read the LSB first then the MSB at the next read cycle.

## **Verification Methods**

The C8254 megafunction's functionality was verified by means of a proprietary hardware modeler. The same stimulus was applied to a hardware model that contained the original Intel 82C54 chip, and the results compared with the megafunction's simulation output

## **Device Utilization & Performance**

| Supported  | Device   |     | Performance |             |                  |

|------------|----------|-----|-------------|-------------|------------------|

| Family     | Tested   | LEs | Memory      | Memory bits | F <sub>max</sub> |

| Cyclone    | EP1C20-6 | 524 | 0           | 0           | 109 MHz          |

| Stratix    | EP1S20-5 | 524 | 0           | 0           | 119 MHz          |

| Stratix-II | EP2S60-3 | 536 | 0           | 0           | 166 MHz          |

# **Deliverables**

#### **Netlist License**

- Post-synthesis EDIF netlist

- Assignment & Configuration

- Symbol & Include files

- Testbench (self checking)

- Vectors & expected results for testing functionality

- Documentation

#### **HDL Source License**

- VHDL or Verilog RTL source code

- Testbenches (self checking)

- Wrapper for pin compatible replacement

- Vectors & expected results for testing functionality

- Synthesis and simulation scripts

- Documentation

# **Related Information**

# **Intel Microprocessor and Peripheral Handbook 1989**

Volume II - Microprocessor ISBN: 1-55512-041-5

## **Contact Information**

CAST, Inc.

11 Stonewall Court

Woodcliff Lake, New Jersey 07677 USA

Phone: +1 201-391-8300

Fax: +1 201-391-8694

E-Mail: info@cast-inc.com

Www.cast-inc.com

Copyright © CAST, Inc. 2004, All Rights Reserved. Contents subject to change without notice.