# Car Stereo Electronic Tone and Volume Control

#### Overview

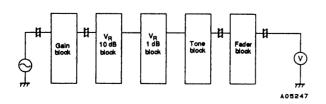

The LC75371M is an electronic tone/volume control LSI that can implement, with minimal external components, volume, balance, fader, bass and treble, loudness, input switching, and input level controls.

#### **Functions**

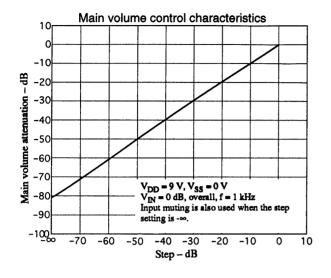

- Volume control: From 0 to -79 dB in 1-dB steps plus

-∞ for a total of 81 settings. Since the left and right levels can be set independently, this function can also be used to implement a balance function.

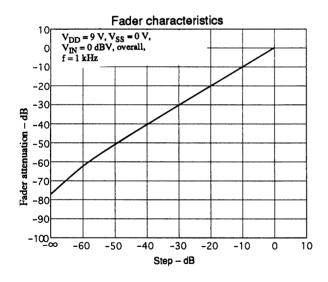

- Fader: Attenuates either the rear or front channels to one of 16 levels. (Provides 16 settings, namely, from 0 to −20 dB in 2-dB steps, from −20 to −25 dB in one 5-dB step, from −25 to −45 dB in 10-dB steps, −60 dB, and −∞.)

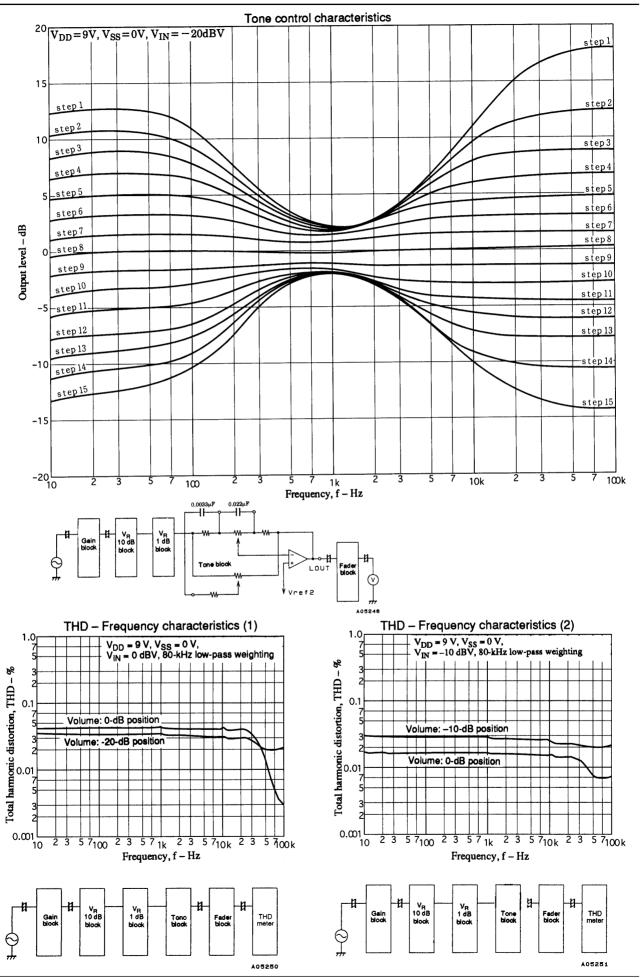

- Bass and treble controls: Forms an NF-type tone control circuit (LUX type) using external capacitors. Provides 15 settings each for the bass and treble controls.

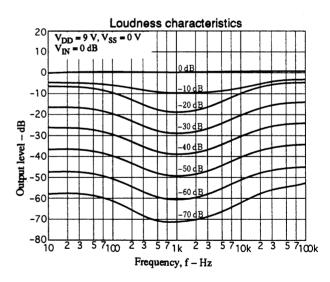

- Loudness control: A loudness function can be implemented by attaching external RC circuits at the taps provided from the volume control resistor ladder starting at the –20-dB position.

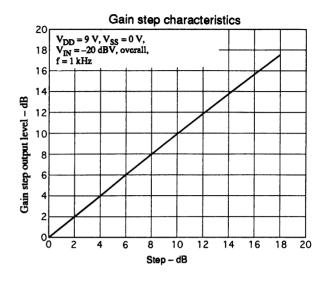

- The input signal can be selected from one of three inputs for each of the left and right channels. The input signal can be amplified by between 0 and +18 dB in 6-dB steps.

- Serial data input: Supports CCB\* format communication with the system controller.

#### **Features**

- Built-in buffer amplifiers allow applications to be implemented with few external components.

- A V<sub>DD</sub>/2 reference voltage generation circuit is provided on chip.

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

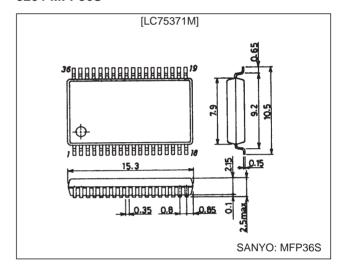

# **Package Dimensions**

unit: mm

#### 3204-MFP36S

# **Specifications**

# Absolute Maximum Ratings at $Ta=25^{\circ}C$ , $V_{SS}=0\ V$

| Parameter                   | Symbol              | Conditions                                           | Ratings                          | Unit |

|-----------------------------|---------------------|------------------------------------------------------|----------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | $V_{DD}$                                             | 12                               | V    |

| Maximum input voltage       | V <sub>IN</sub> max | CL, DI, CE, LIN, RIN, LFIN, RFIN, L1 to L3, R1 to R3 | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation | Pd max              | Ta ≤ 85°C                                            | 230                              | mW   |

| Operating temperature       | Topr                |                                                      | -40 to +85                       | °C   |

| Storage temperature         | Tstg                |                                                      | -50 to +125                      | °C   |

# Allowable Operating Ranges at $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                | Symbol          | Conditions                                           | min             | typ | max      | Unit |

|--------------------------|-----------------|------------------------------------------------------|-----------------|-----|----------|------|

| Supply voltage           | $V_{DD}$        | V <sub>DD</sub>                                      | 6.0             |     | 11.0     | V    |

| Input high-level voltage | $V_{IH}$        | CL, DI, CE                                           | 4.0             |     | $V_{DD}$ | V    |

| Input low-level voltage  | $V_{IL}$        | CL, DI, CE                                           | V <sub>SS</sub> |     | 1.0      | V    |

| Input voltage amplitude  | V <sub>IN</sub> | CL, DI, CE, LIN, RIN, LFIN, RFIN, L1 to L3, R1 to R3 | V <sub>SS</sub> |     | $V_{DD}$ | Vp-p |

| Input pulse width        | t <sub>øW</sub> | CL                                                   | 1               |     |          | μs   |

| Setup time               | tsetup          | CL, DI, CE                                           | 1               |     |          | μs   |

| Hold time                | thold           | CL, DI, CE                                           | 1               |     |          | μs   |

| Operating frequency      | fopg            | CL                                                   |                 |     | 500      | kHz  |

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}=9~V,\,V_{SS}=0~V$

| Parameter                       | Symbol             | Conditions                                                                               | min   | typ   | max   | Unit |

|---------------------------------|--------------------|------------------------------------------------------------------------------------------|-------|-------|-------|------|

| [Input Block]                   |                    |                                                                                          |       |       |       |      |

| Input resistance                | Rin                | L1 to L3, R1 to R3                                                                       | 30    | 50    | 70    | kΩ   |

| Minimum input gain              | Gin min            |                                                                                          | -2    | 0     | +2    | dB   |

| Maximum input gain              | Gin max            |                                                                                          | +16.0 | +18.0 | +20.0 | dB   |

| Step resolution                 | Gstep              |                                                                                          |       | +6.0  |       | dB   |

| [Volume Control Block]          |                    |                                                                                          | •     |       |       | •    |

| Innut registeres                | Rv10               | LIN, RIN: 10-dB steps, loudness off                                                      | 30    | 50    | 70    | kΩ   |

| Input resistance                | Rv1                | 1-dB steps                                                                               | 6     | 10    | 14    | kΩ   |

| Step resolution                 | ATstep             |                                                                                          |       | 1     |       | dB   |

| Cton orror                      | A.T                | step = 0 to -20 dB                                                                       | -1    | 0     | +1    | dB   |

| Step error                      | ATerr              | step = -20 to -50 dB                                                                     | -3    | 0     | +3    | dB   |

| [Fader Block]                   |                    |                                                                                          |       |       |       |      |

| Input resistance                | Rfed               | LFIN, RFIN                                                                               | 12    | 20    | 28    | kΩ   |

|                                 |                    | step = 0 to -20 dB                                                                       |       | 2     |       | dB   |

| Step resolution                 | ATstep             | step = -20 to -25 dB                                                                     |       | 5     |       | dB   |

|                                 |                    | step = -25 to -45 dB                                                                     |       | 10    |       | dB   |

| 0.                              |                    | step = 0 to -45 dB                                                                       | -2    | 0     | +2    | dB   |

| Step error                      | ATerr              | step = -45 dB                                                                            | -3    | 0     | +3    | dB   |

| Output load resistance          | R <sub>L</sub>     | LFOUT, LROUT, RFOUT, RROUT                                                               | 20    |       |       | kΩ   |

| [Bass and Treble Control Block] | •                  |                                                                                          |       |       |       | •    |

| Bass control range              | Gbass              | Max. boost/cut                                                                           | ±9    | ±10.5 | ±12   | dB   |

| Treble control range            | Gtre               | Max. boost/cut                                                                           | ±8    | ±10.5 | ±13   | dB   |

| [Overall Characteristics]       | •                  |                                                                                          |       |       |       | •    |

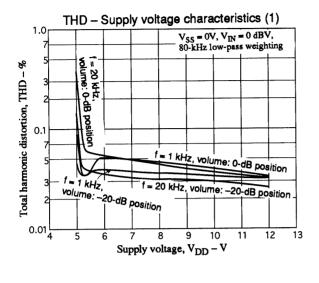

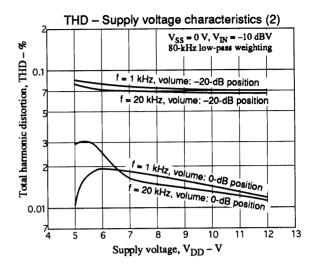

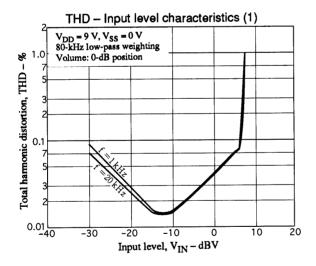

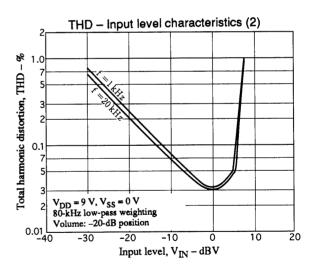

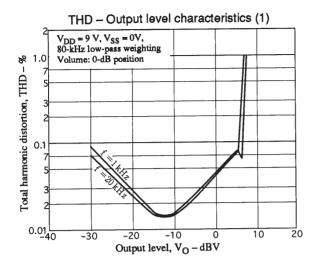

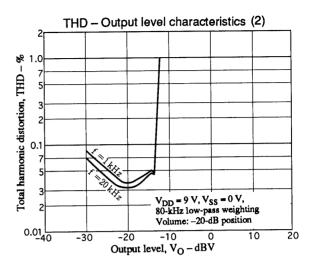

| Tatal barrassia diatantian      | THD1               | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, all settings flat overall                           |       | 0.045 |       | %    |

| Total harmonic distortion       | THD2               | V <sub>IN</sub> = 1 Vrms, f = 20 kHz, all settings flat overall                          |       | 0.045 |       | %    |

| Crosstalk                       | СТ                 | $V_{IN}$ = 1 Vrms, f = 1 kHz, all settings flat overall, Rg = 1 kΩ                       |       | 70    |       | dB   |

|                                 |                    | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, main volume control at -∞                           |       | -76   |       | dB   |

| Output at maximum attenuation   | V <sub>O</sub> min | $V_{IN}$ = 1 Vrms, f = 1 kHz, main volume control at $-\infty$ , INMUTE                  |       | -80   |       | dB   |

| Output raise valtage            | V <sub>N</sub> 1   | All settings flat overall (IHF-A), Rg = 1 k $\Omega$                                     |       | 12    | 30    | μV   |

| Output noise voltage            | V <sub>N</sub> 2   | All settings flat overall (DIN-AUDIO), Rg = 1 k $\Omega$                                 |       | 16    | 40    | μV   |

| Current drain                   | I <sub>DD</sub>    | V <sub>DD</sub> – V <sub>SS</sub> = 11 V                                                 |       | 19    | 22.8  | mA   |

| Input high-level current        | I <sub>IH</sub>    | CL, DI, CE: V <sub>IN</sub> = 9 V                                                        |       |       | 10    | μA   |

| Input low-level current         | I <sub>IL</sub>    | CL, DI, CE: V <sub>IN</sub> = 0 V                                                        | -10   |       |       | μA   |

| Maximum input level             | V <sub>CL</sub>    | THD = 1%, $R_L$ = 20 k $\Omega$ , all tsettings flat overall, test point = fader output. |       | 2     |       | Vrms |

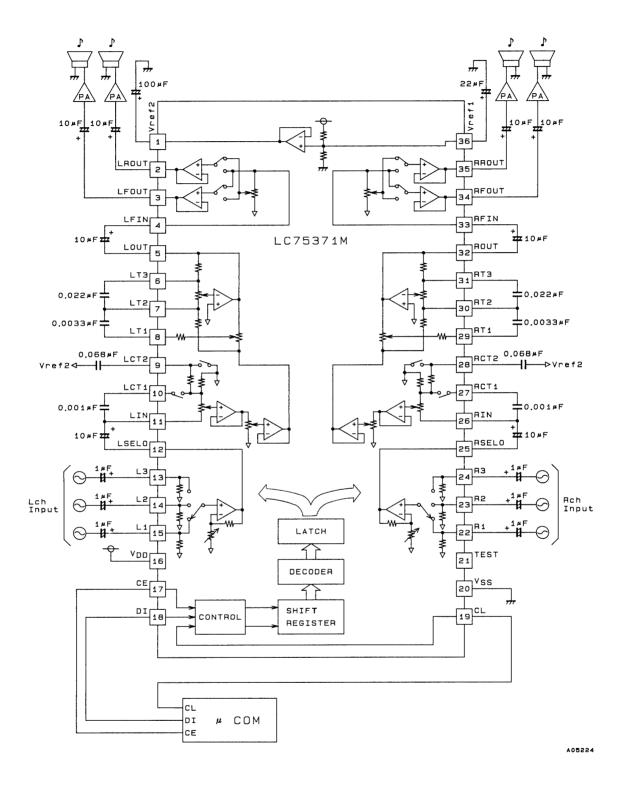

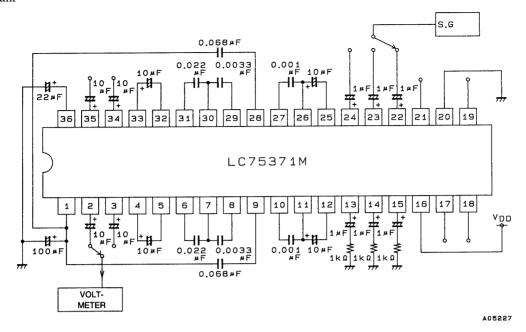

# **Equivalent Circuit Block Diagram and Sample Application Circuit**

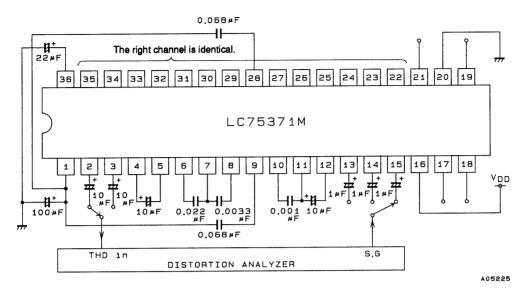

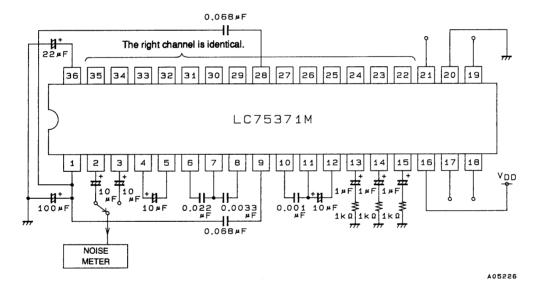

#### **Test Circuits**

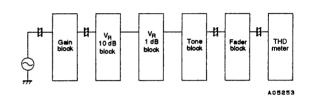

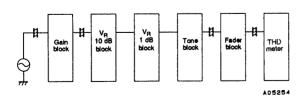

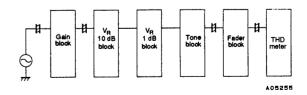

# 1. Total harmonic distortion

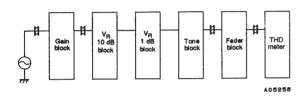

#### 2. Output noise voltage

#### 3. Crosstalk

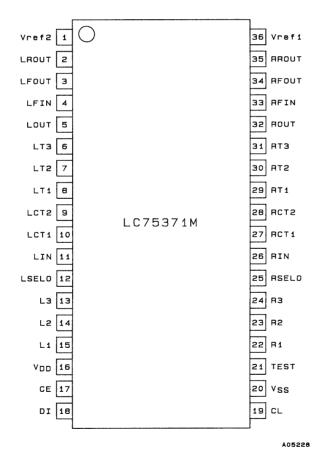

#### **Pin Assignment**

Top view

#### **Pin Functions**

| Pin No.                       | Symbol                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            | Notes           |

|-------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

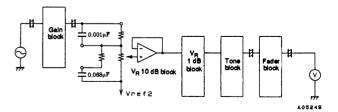

| 1                             | Vref2                                  | <ul> <li>Common pin for the main volume control block, fader block, tone control block, gain control block, and input switching block.</li> <li>Since the capacitor connected between Vref2 and V<sub>SS</sub> becomes the residual resistance when the volume control is set to maximum attenuation, the value of this capacitor must be selected carefully.</li> <li>The voltage applied to this pin must never exceed V<sub>DD</sub>.</li> </ul> | Vref1           |

| 36                            | Vref1                                  | $V_{DD}\!/\!2$ voltage generation block. A capacitor must be connected between Vref1 and $V_{SS}$ to suppress power supply ripple.                                                                                                                                                                                                                                                                                                                  | Vref2 777       |

| 2<br>3<br>35<br>34            | LROUT<br>LFOUT<br>RROUT<br>RFOUT       | <ul> <li>Fader outputs. The front and rear can be attenuated independently. The left and right attenuation levels are identical.</li> <li>These are low-impedance outputs, since they have built-in operational amplifiers.</li> </ul>                                                                                                                                                                                                              | A05231          |

| 4<br>33                       | LFIN<br>RFIN                           | Fader inputs     These inputs must be driven by low-impedance outputs.                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub> |

| 5<br>32                       | LOUT<br>ROUT                           | Tone control outputs                                                                                                                                                                                                                                                                                                                                                                                                                                | Vref2 ///       |

| 8<br>7<br>6<br>29<br>30<br>31 | LT1<br>LT2<br>LT3<br>RT1<br>RT2<br>RT3 | Connections for the bass and treble supplementary capacitors for the tone control circuit Connect high-frequency compensation capacitors between the T1/T2 pairs. Connect low-frequency compensation capacitors between the T2/T3 pairs.                                                                                                                                                                                                            | W A05234        |

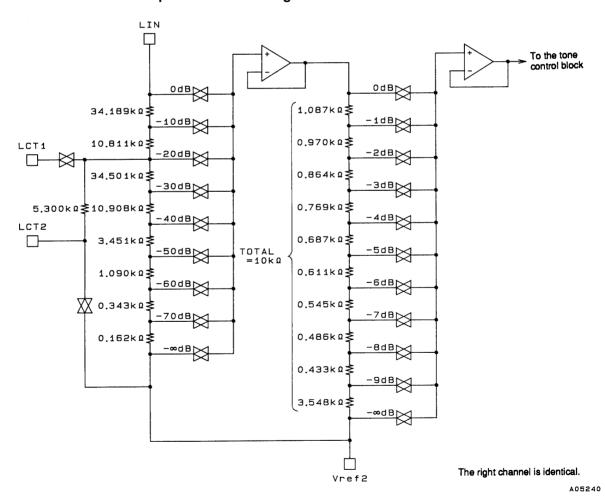

| 10<br>9<br>27<br>28           | LCT1<br>LCT2<br>RCT1<br>RCT2           | Loudness circuit connections. Connect high-frequency compensation capacitors between the LCT1/RCT1 and LIN/RIN pins, and connect low-frequency compensation capacitors between LCT2/RCT2 and Vref2.                                                                                                                                                                                                                                                 |                 |

Continued on next page.

#### Continued from preceding page.

| Pin No.                          | Symbol                           | Function                                                                                                                                                                                 | Notes            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 11<br>26                         | LIN<br>RIN                       | Main volume control inputs     These inputs must be driven by low-impedance outputs.                                                                                                     | A05235           |

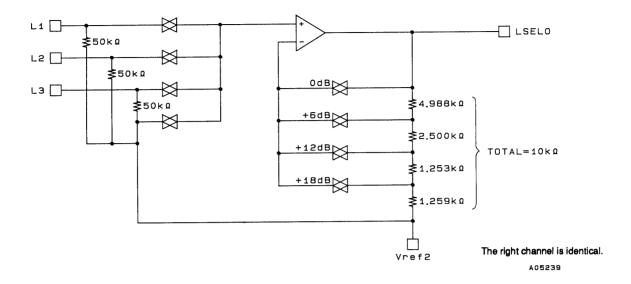

| 12<br>25                         | LSELO<br>RSELO                   | Input selector outputs                                                                                                                                                                   | A05236           |

| 15<br>14<br>13<br>22<br>23<br>24 | L1<br>L2<br>L3<br>R1<br>R2<br>R3 | Signal inputs                                                                                                                                                                            | Vref2 /// A05237 |

| 16                               | $V_{DD}$                         | Power supply                                                                                                                                                                             |                  |

| 20                               | V <sub>SS</sub>                  | Ground                                                                                                                                                                                   |                  |

| 17                               | CE                               | Chip enable. Data is loaded into the internal latch when this pin goes from high to low, and all analog switches operate at that time. Data transfers are enabled when this pin is high. | Z                |

| 18<br>19                         | DI<br>CL                         | Serial data and clock inputs for LSI control.                                                                                                                                            | 777 A05238       |

| 21                               | TEST                             | Test pin. This pin must be left open.                                                                                                                                                    |                  |

### Input Block Equivalent Circuit Diagram

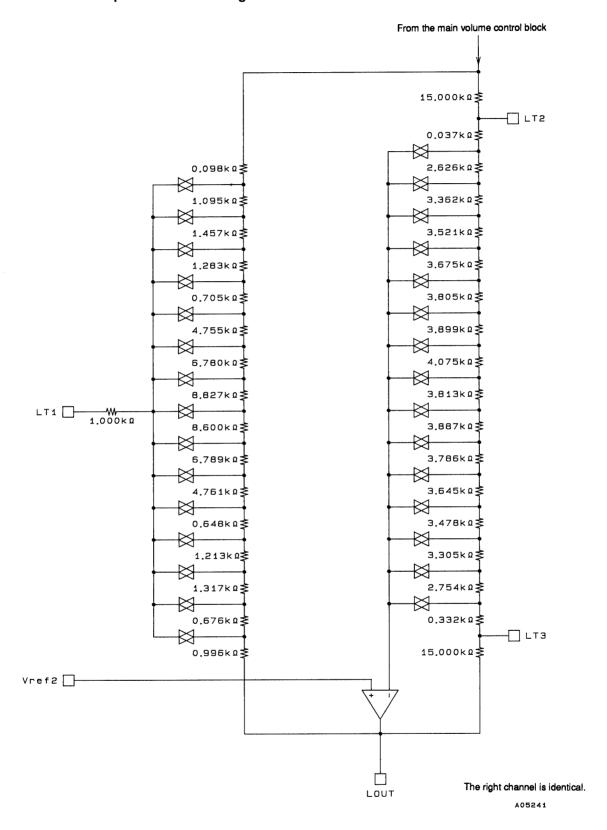

#### Main Volume Control Block Equivalent Circuit Diagram

#### **Tone Control Block Equivalent Circuit Diagram**

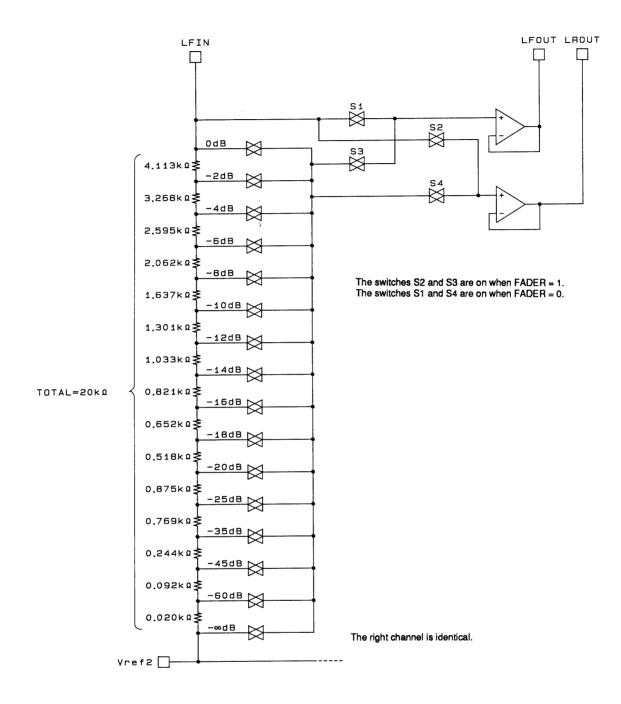

# **Fader Block Equivalent Circuit Diagram**

If data setting the main volume control 1-dB step to  $-\infty$  is sent to the LSI, the S1 and S2 switches will be opened and the S3 and S4 switches will be turned on (closed).

A05242

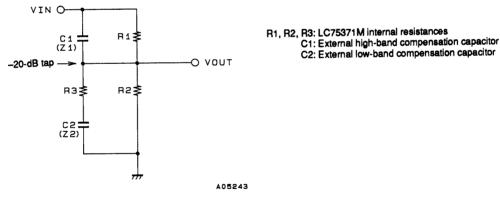

#### Sample Calculation of the Loudness Circuit External Constants

First, see the LC75371M 10-dB step internal equivalent circuit shown on page 9. Figure 1 below shows a version of that circuit to which the loudness circuit external components have been added, and which has been simplified for this calculation. The sample calculation below uses this circuit diagram to acquire a 5-dB boost at f = 100 Hz. (f = 100 Hz, 5-dB boost)

Assuming that the resistors and capacitors in Figure 1 have the following values:

$$R1 = R2 = 50 \text{ k}\Omega$$

$$R3 = 5 \text{ k}\Omega$$

$$And C1 = Z1 \text{ and } C2 = Z2.$$

Then:

$$V_{OUT} = \frac{\frac{R2 (R3 + Z2)}{R2 + R3 + Z2}}{(at = 1 \text{ kHz})} = -20 \text{ dB}$$

$$V_{OUT} = \frac{\frac{R2 (R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}}{\frac{R1 \cdot 10 \cdot Z1}{R1 + 10 \cdot Z1} + \frac{R2 (R3 + 10 \cdot Z2)}{R2 + R3 + 10 \cdot Z2}} = -15 \text{ dB}$$

From the above equations we find:

$$Z1 = 891.5 \text{ k}\Omega$$

and  $Z2 = 880 \Omega$ .

Therefore, the specifications will be met if capacitors that have these impedances at f = 1 kHz are connected externally. The result is that C1 = 178.5 pF and C2 = 0.18  $\mu$ F.

Figure 1

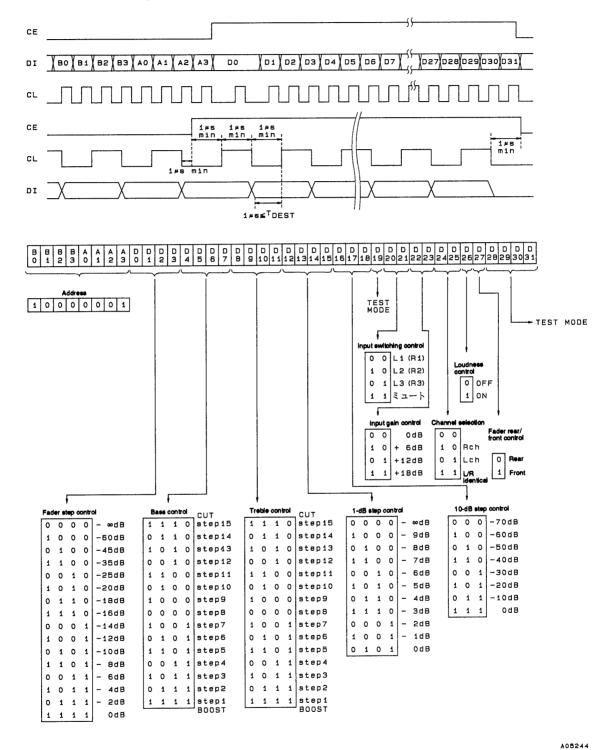

#### **Control System Timing and Data Format**

The LC75371M is controlled by applying data in the stipulated format to the CE, CL, and DI pins. The data consists of 40 bits, of which 8 bits are the chip address and 32 bits are the data.

Note: The bits D19 and D28 to D31 are LSI test bits, and must be set to 0.

#### **Usage Notes**

- 1. The states of the internal analog switches are undefined when power is first applied. Use an external muting circuit or other technique to mute the outputs until correct control data has been set up in the LC75371M.

- 2. Either cover the lines connected to the CL, DI, and CE pins with the ground pattern or use shielded cable for those lines to prevent the high-frequency digital signals on those lines from entering the analog system.

- 3. Muting by input switching must be used in conjunction with the volume control setting when the maximum volume control attenuation (the VOL =  $-\infty$  position) is used.

- 4. Since there is significant sample-to-sample variation in the magnitude of the main volume switching noise, request a switching noise verification sample to verify the maximum switching noise.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.