# **DAVICOM Semiconductor, Inc.**

## DM9161A

# 10/100 Mbps Fast Ethernet **Physical Layer Single Chip Transceiver**

DATA SHEET

**Preliminary**

Version: DM9161A-DS-P04

Jan. 19, 2005

Jan.19,2005

| Table of Contents                                          |       |

|------------------------------------------------------------|-------|

| 1. General Description                                     | 3     |

| 2. Features                                                |       |

| 3. Block Diagram                                           | 4     |

| 4. Pin Configuration:                                      |       |

| •                                                          |       |

| 5. Pin Description                                         | 6     |

| 5.1 Normal MII Interface, 21 pins                          |       |

| 5.2 Media Interface, 4 pins                                |       |

| 5.4 Mode, 2 pins                                           |       |

| 5.5 Bias and Clock, 4 pins                                 |       |

| 5.6 Power, 13 pins                                         |       |

| 5.7 Table A (Media Type Selection)                         | 9     |

| 5.8 Pin Maps of Normal MII, Reduced MII, and 10Base-T GPSI |       |

| (7-Wired) Mode                                             | 10    |

| 6. LED Configuration                                       | 11    |

| 6.1 LED Functional Description12                           | . 1 1 |

| 0.1 LED Functional Description12                           |       |

| 7. Functional Description                                  | .13   |

| 7.1 MII interface                                          | .13   |

| 7.2 100Base-TX Operation                                   | .15   |

| 7.2.1 100Base-TX Transmit                                  | .15   |

| 7.2.1.1 4B5B Encoder                                       |       |

| 7.2.1.2 Scrambler                                          |       |

| 7.2.1.3 Parallel to Serial Converter                       |       |

| 7.2.1.4 NRZ to NRZI Encoder                                |       |

| 7.2.1.5 MLT-3 Converter                                    |       |

| 7.2.1.6 MLT-3 Driver                                       |       |

| 7.2.1.7 4B3B Code Group  7.2.2 100Base-TX Receiver         |       |

| 7.2.2 Toobase-TX Receiver                                  |       |

| 7 2 2 2 Adaptive Equalizer                                 | 18    |

| 7.2.2.2 Adaptive Equalizer                                 | .18   |

| 7.2.2.4 Clock Recovery Module                              | .18   |

| 7.2.2.5 NRZI to NRZ                                        | .18   |

| 7.2.2.6 Serial to Parallel                                 | .18   |

| 7.2.2.7 Descrambler                                        |       |

| 7.2.2.8 Code Group Alignment                               | .18   |

| 7.2.2.9 4B5B Decoder                                       |       |

| 7.2.3 10Base-T Operation                                   | .18   |

| 7.2.4 Collision Detection                                  | .19   |

| 7.2.6 Auto-Negotiation                                     | 10    |

| 7.2.7 MII Serial Management                                |       |

| 7.2.8 Serial Management Interface                          | .20   |

|                                                            |       |

| 7.2.9 Management Interface – Read Frame                    | 20    |

| Structure Write Frame Structure                            |       |

| 7.2.10 Management Interface – Write Frame Structure        |       |

| 7.2.11 Power Reduced Mode                                  |       |

| 7.2.13 Reduced Transmit Power Mode                         |       |

| 7.2.14 Feedback Vout and Vin for 5V21                      | - '   |

| 7.3 Auto MDIX Functional Description                       | .22   |

|                                                            |       |

| 8. MII Register Description       23         8.1 Basic Mode Control Register (BMCR) - 00       24         8.2 Basic Mode Status Register (BMSR) - 01       25         8.3 PHY ID Identifier Register #1 (PHYIDR1) - 02       26         8.4 PHY ID Identifier Register #2 (PHYIDR2) - 03       26         8.5 Auto-negotiation Advertisement Register (ANAR)       - 04         - 04       27 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.6 Auto-negotiation Link Partner Ability Register (ANLPAR) - 0528<br>8.7 Auto-negotiation Expansion Register (ANER)<br>- 06                                                                                                                                                                                                                                                                  |

| 8.8 DAVICOM Specified Configuration Register (DSCR) –1629 8.9 DAVICOM Specified Configuration and Status Register (DSCSR) - 17                                                                                                                                                                                                                                                                |

| 8.10 10Base-T Configuration / Status (10BTCSR) - 1832                                                                                                                                                                                                                                                                                                                                         |

| 8.14 DAVICOM Consisted Interrupt Decistor 21                                                                                                                                                                                                                                                                                                                                                  |

| 8.11 DAVICOM Specified Interrupt Register - 21                                                                                                                                                                                                                                                                                                                                                |

| 8.12 DAVICOM Specified Receive Error Counter Register (RECR)                                                                                                                                                                                                                                                                                                                                  |

| 22                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.13 DAVICOM Specified Disconnect Counter Register (DISCR) -                                                                                                                                                                                                                                                                                                                                  |

| 23                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.14 DAVICOM Hardware Reset Latch State                                                                                                                                                                                                                                                                                                                                                       |

| Register (RLSR) - 2434                                                                                                                                                                                                                                                                                                                                                                        |

| 9. DC and AC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.1 Absolute Maximum Ratings(25°C)                                                                                                                                                                                                                                                                                                                                                            |

| 9.2 Operating Conditions                                                                                                                                                                                                                                                                                                                                                                      |

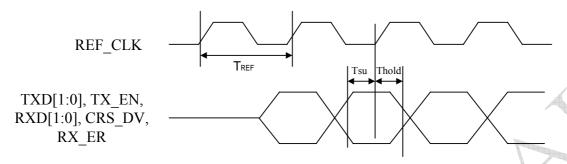

| 9.4 AC Electrical Characteristics & Timing                                                                                                                                                                                                                                                                                                                                                    |

| Waveform                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.4.1 TP Interface 37                                                                                                                                                                                                                                                                                                                                                                         |

| 9.4.2 Oscillator/Crystal Timing                                                                                                                                                                                                                                                                                                                                                               |

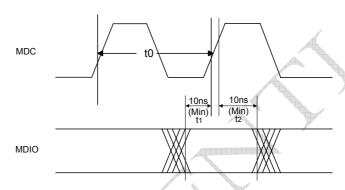

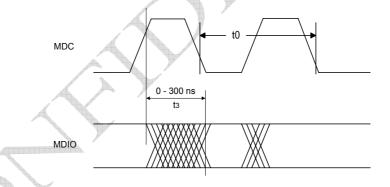

| 9.4.3 MDC/MDIO Timing                                                                                                                                                                                                                                                                                                                                                                         |

| 9.4.4 MDIO Timing when OUTPUT by STA                                                                                                                                                                                                                                                                                                                                                          |

| 9.4.5 MDIO Timing when OUTPUT by DM9161A                                                                                                                                                                                                                                                                                                                                                      |

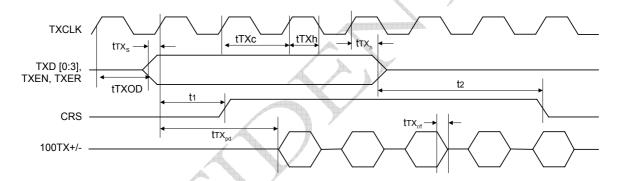

| 9.4.6 100Base-TX Transmit Timing Parameters                                                                                                                                                                                                                                                                                                                                                   |

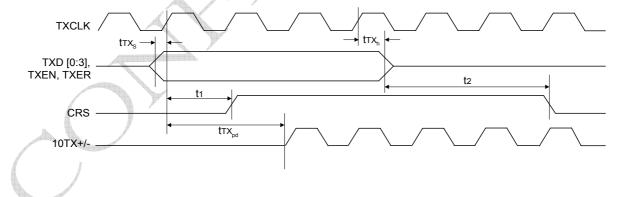

| 9.4.7 100Base-TX Transmit Timing Diagram39                                                                                                                                                                                                                                                                                                                                                    |

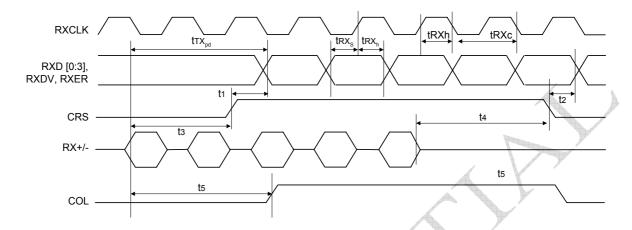

| 9.4.8 100Base-TX Receive Timing Parameters                                                                                                                                                                                                                                                                                                                                                    |

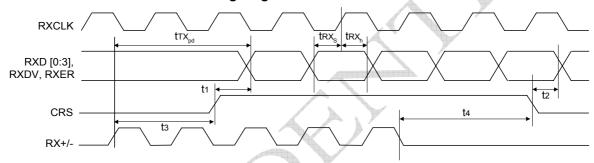

| 9.4.9 MII 100Base-TX Receive Timing Diagram40                                                                                                                                                                                                                                                                                                                                                 |

| 3 13                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                               |

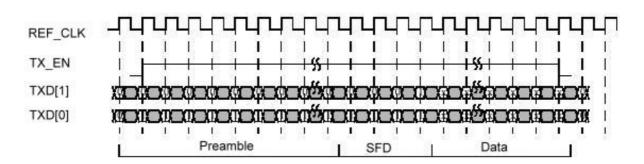

| 9.4.10 MII 10Base-T Nibble Transmit Timing Parameters40                                                                                                                                                                                                                                                                                                                                       |

| 9.4.11 MII 10Base-T Nibble Transmit Timing                                                                                                                                                                                                                                                                                                                                                    |

| Diagram40                                                                                                                                                                                                                                                                                                                                                                                     |

| 9.4.12 MII 10Base-T Receive Nibble Timing Parameters 41                                                                                                                                                                                                                                                                                                                                       |

| 9.4.13 MII 10Base-T Receive Nibble Timing                                                                                                                                                                                                                                                                                                                                                     |

| Diagram41                                                                                                                                                                                                                                                                                                                                                                                     |

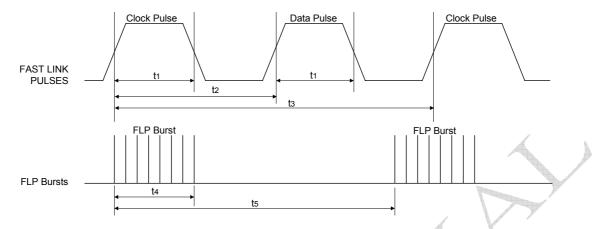

| 9.4.14 Auto-negotiation and Fast Link Pulse Timing Parameters41 9.4.15 Auto-negotiation and Fast Link Pulse Timing Diagram42                                                                                                                                                                                                                                                                  |

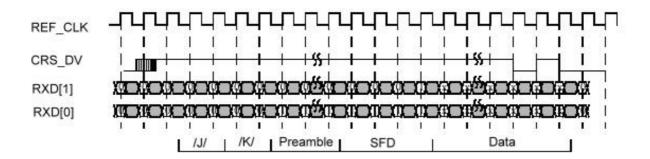

| 9.4.16 RMII Receive Timing Diagram                                                                                                                                                                                                                                                                                                                                                            |

| 9.4.17 RMII Transmit Timing Diagram                                                                                                                                                                                                                                                                                                                                                           |

| 9.4.17 RMII Transmit Timing Diagram                                                                                                                                                                                                                                                                                                                                                           |

| 3.4. TO INVITE HINING Diagram43                                                                                                                                                                                                                                                                                                                                                               |

| 9.4.19 RMII Timing Parameter43                                                                                                                                                                                                                                                                                                                                                                |

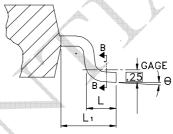

| 10. Package Information44                                                                                                                                                                                                                                                                                                                                                                     |

| 11.Order Information45                                                                                                                                                                                                                                                                                                                                                                        |

### 1. General Description

The DM9161A is a physical layer, single-chip, and low power transceiver for 100BASE-TX and 10BASE-T operations. On the media side, it provides a direct interface either to Unshielded Twisted Pair Category 5 Cable (UTP5) for 100BASE-TX Fast Ethernet, or UTP5/UTP3 Cable for 10BASE-T Ethernet. Through the Media Independent Interface (MII), the DM9161A connects to the Medium Access Control (MAC) layer, ensuring a high inter operability from different vendors.

TheDM9161A uses a low power and high performance advanced CMOS process. It contains the entire physical layer functions of 100BASE-TX as defined by IEEE802.3u, including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD), 10BASE-TX Encoder/Decoder (ENC/DEC), and Twisted Pair Media Access Unit (TPMAU). The DM9161A provides a strong support for the auto-negotiation function, utilizing automatic media speed and protocol selection. Furthermore, due to the built-in wave shaping filter, the DM9161A needs no external filter to transport signals to the media in 100BASE-TX or 10BASE-T Ethernet operation.

#### 2. Features

- Fully comply with IEEE 802.3 / IEEE 802.3u 10Base-T/ 100Base-TX, ANSI X3T12 TP-PMD 1995 standard

- Support MDI/MDI-X auto crossover function (Auto-MDI)

- Support Auto-Negotiation function, compliant with IEEE 802.3u

- Fully integrated Physical layer transceiver On-chip filtering with direct interface to magnetic transformer

- Selectable repeater or node mode

- Selectable MII or RMII (Reduced MII) mode for 100Base-TX and 10Base-TX. Selectable MII or GPSI (7-Wired) mode for 10Base-T

- Selectable full-duplex or half-duplex operation

- MII management interface with maskable interrupt output capability

- Provide Loopback mode for easy system diagnostics

- LED status outputs indicate Link/ Activity, Speed10/100 and Full-duplex/Collision. Support Dual-LED optional control

- Single low power Supply of 3.3V with an advanced CMOS technology

- Very Low Power consumption modes:

- Power Reduced mode (cable detection)

- Power Down mode

- Selectable TX drivers for 1:1 or 1.25:1 transformers for additional power reduction. 1: 1 transformers only when Auto MDIX Enable.

- Compatible with 3.3V and 5.0V tolerant I/Os

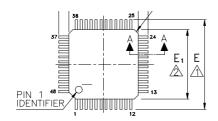

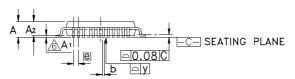

48-pin LQFP

3 Preliminary

Version: DM9161A-DS-P04 Jan. 19, 2005

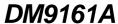

### 3. Block Diagram

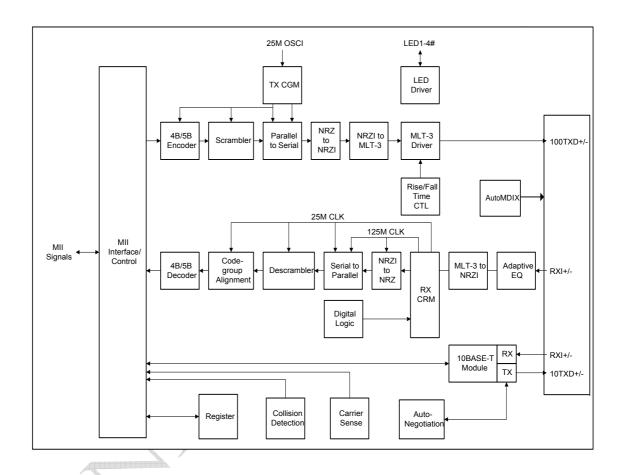

### 4. Pin Configuration:

### 5. Pin Description

I: Input, O: Output, LI: Latch input when power-up/reset, Z: Tri-State output, U: Pulled high D: Pulled low

5.1 Normal MII Interface, 21 pins

| Pin No.     | Pin Name                | I/O                   | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------|-------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 16          | TXER/TXD [4]            | I                     | Transmit Error/The Fifth TXD Data Bit In 100Mbps mode, when the signal indicates active high and TXEN is active, the HALT symbol substitutes the actual data nibble. In 10Mbps, the input is ignored In bypass mode (bypass BP4B5B), TXER becomes the TXD [4] pin, the fifth TXD data bit of the 5B symbol                                                                                                            |  |

| 20,19,18,17 | TXD [0:3]               | I                     | Transmit Data 4-bit nibble data inputs (synchronous to the TXCLK) when in 10/100Mbps nibble mode. In 10Mbps GPSI (7-Wired) mode, the TXD [0] pin is used as the serial data input pin, and TXD [1:3] are ignored.                                                                                                                                                                                                     |  |

| 21          | TXEN                    | I                     | Transmit Enable Active high indicates the presence of valid nibble data on the TXD [0:3] for both 100Mbps and 10Mbps nibble modes. In 10Mbps GPSI (7-Wired) mode, active high indicates the presence of valid 10Mbps data on TXD [0].                                                                                                                                                                                 |  |

| 22          | TXCLK/<br>ISOLATE       | O,<br>Z,<br>LI<br>(D) | Transmit Clock The transmitting clock provides the timing reference for the transfer of the TXEN, TXD, and TXER. TXCLK is provided by the PHY 25MHz in 100Mbps nibble mode, 2.5MHz in 10Mbps nibble mode, 10MHz in 10Mbps GPSI (7-Wired) mode ISOLATE Setting: (When power up reset, latch input) 0: Reg 0.10 will be initialized to "0". (Ref.to 8.1 Basic Control Register) 1: Reg 0.10 will be initialized to "1". |  |

| 24          | MDC                     | - I                   | Management Data Clock Synchronous clock for the MDIO management data. This clock is provided by management entity, and it is up to 2.5MHz                                                                                                                                                                                                                                                                             |  |

| 25          | MDIO                    | I/O                   | Management Data I/O Bi-directional management data which may be provided by the station management entity or the PHY                                                                                                                                                                                                                                                                                                  |  |

| 29,28,27,26 | RXD[0:3]<br>/PHYAD[0:3] | O,<br>Z,<br>LI<br>(D) | Receive Data Output 4-bit nibble data outputs (synchronous to RXCLK) when in 10/100Mbps MII mode In 10Mbps GPSI (7-Wired) mode, the RXD [0] pin is used as the serial data output pin, and the RXD [1:3] are ignored PHY address [0:3] (power up reset latch input) PHY address sensing input pins                                                                                                                    |  |

| 32          | MDINTR                  | IO,<br>LI<br>(D)      | Status Interrupt Output: Whenever there is a status change (link, speed, duplex depend on interrupt register [21]) The interrupt output assert low when pull up. Asserted high when pull down.                                                                                                                                                                                                                        |  |

| 34 | RXCLK<br>/10BTSER    | O,<br>Z,<br>LI<br>(U)                                                                                                                                                                                                                                                                                                                                                                | The received clock provides the timing reference for the transfer of the RXDV, RXD, and RXER. RXCLK is provided by PHY. The PHY may recover the RXCLK reference from the received data or it may derive the RXCLK reference from a nominal clock 25MHz in 100Mbps MII mode, 2.5MHz in 10Mbps MII mode, 10MHz in 10Mbps GPSI (7-Wired) mode 10BTSER only support for 10M mode; (power up reset latch input) 0 = GPSI (7-Wired) mode in 10M mode 1 = MII mode in 10M mode |

|----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35 | CRS<br>/PHYAD[4]     | O, Carrier Sense Detect/ PHYAD[4] Z, Asserted high to indicate the presence of carrier due to receive activities in half-duplex mode of 10BASE-T or 100BASE-TX. In mode or full-duplex mode, this signal is asserted high to indicate presence of carrier due to receive activity only This pin is also used as PHYAD [4] (power up reset latch input) PHY address sensing input pin |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36 | COL<br>/RMII         | O,<br>Z,<br>LI<br>(D)                                                                                                                                                                                                                                                                                                                                                                | Asserted high to indicate the detection of the collision conditions in half-duplex mode of 10Mbps and 100Mbps. In full-duplex mode, this signal                                                                                                                                                                                                                                                                                                                         |

| 37 | RXDV<br>/TESTMODE    | O,<br>Z,<br>LI<br>(D)                                                                                                                                                                                                                                                                                                                                                                | Receive Data Valid Asserted high to indicate that the valid data is presented on the RXD [0:3] Test mode control pin (power up reset latch input)                                                                                                                                                                                                                                                                                                                       |

| 38 | RXER/RXD[4]<br>/RPTR | O,<br>Z,<br>LI<br>(D)                                                                                                                                                                                                                                                                                                                                                                | Receive Data Error/The Fifth RXD Data Bit of the 5B Symbol Asserted high to indicate that an invalid symbol has been detected In decoder bypass mode (bypass BP4B5B), RXER becomes RXD [4], the fifth RXD data bit of the 5B symbol This pin is also used to select Repeater or Node mode. (power up reset latch input) 0 = Node Mode (default) 1 = Repeater Mode                                                                                                       |

| 31 | LEDMODE              | I                                                                                                                                                                                                                                                                                                                                                                                    | LED MODE Select Reference LED function description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |                      |                                                                                                                                                                                                                                                                                                                                                                                      | 0: support Dual-LED<br>1: Normal LED                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40 | RESET#               | I                                                                                                                                                                                                                                                                                                                                                                                    | Reset Active low input that initializes the DM9161A.                                                                                                                                                                                                                                                                                                                                                                                                                    |

7 Preliminary Version: DM9161A-DS-P04 Jan.19,2005

### 5.2 Media Interface, 4 pins

| Pin No. | Pin Name | I/O | Description                                              |  |

|---------|----------|-----|----------------------------------------------------------|--|

| 3,4     | RX+      | 1   | Differential Receive Pair                                |  |

|         | RX-      |     | Differential data is received from the media             |  |

| 7,8     | TX+      | 0   | Differential Transmit Pair/PECL Transmit Pair            |  |

|         | TX-      |     | Differential data is transmitted to the media in TP mode |  |

### 5.3 LED Interface, 3 pins

| Pin No. | Pin Name                                         | I/O             | Description                                                                                                                                                                                                                          |

|---------|--------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | LED0<br>/OP0                                     | O,<br>LI<br>(U) | LED Driver output 0 OP0: (power up reset latch input) This pin is used to control the forced or advertised operating mode of the DM9161A according to the Table A. The value is latched into the DM9161A registers at power-up/reset |

| 12      | LED1 O,<br>/OP1 LI LED<br>(U) OP1<br>This<br>DM9 |                 | LED Driver output 1 OP1: (power up reset latch input) This pin is used to control the forced or advertised operating mode of the DM9161A according to the Table A. The value is latched into the DM9161A registers at power-up/reset |

| 13      | LED2<br>/OP2                                     | O,<br>LI<br>(U) | LED Driver output 2 OP2: (power up reset latch input) This pin is used to control the forced or advertised operating mode of the DM9161A according to the Table A. The value is latched into the DM9161A registers at power-up/reset |

### 5.4 Mode, 3 pins

| Pin No. | Pin Name    | I/O    | Description                                                                                             |

|---------|-------------|--------|---------------------------------------------------------------------------------------------------------|

| 10      | PWRDWN      | 1      | Power Down Control                                                                                      |

|         |             | 454545 | Asserted high to force the DM9161A into power down mode. When in                                        |

|         | _           |        | power down mode, most of the DM9161A circuit block's power is turned                                    |

|         | 4           |        | off, only the MII management interface (MDC, MDIO) logic is available                                   |

|         |             | 4      | (the PHY should respond to management transactions and should not                                       |

|         |             | Age .  | generate spurious signals on the MII)). To leave power down mode, the                                   |

|         |             |        | DM9161A needs the hardware or software reset with the PWRDWN pin                                        |

| 1.1     | CARLECTO    |        | Ochla Statua ar Link Statua                                                                             |

| 14      | CABLESTS    | Ο,     | Cable Status or Link Status                                                                             |

|         | /LINKSTS LI |        | This pin is used to indicate the status of the cable connection when power up reset latch low (Default) |

|         | /           | (D)    | 0 = Without cable connection                                                                            |

|         |             |        | 1 = With cable connection                                                                               |

|         |             |        | This pin is used to indicate the status of the Link connection when power                               |

| 4       |             |        | up reset latch high                                                                                     |

|         |             |        | 0 = With link                                                                                           |

|         |             |        | 1 = Without link                                                                                        |

| 39      |             |        | Auto MDIX Control                                                                                       |

|         |             | (D)    | 1: Disable auto mode                                                                                    |

|         |             | . ,    | 0: Enable auto MDI/MDIX mode                                                                            |

### 5.5 Bias and Clock, 4 pins

| Pin No. | Pin Name | I/O | Description                                        |

|---------|----------|-----|----------------------------------------------------|

| 47      | BGRESG   | Р   | Bandgap Ground                                     |

| 48      | BGRES    | 0   | Bandgap Voltage Reference Resistor 6.8K ohm +/- 1% |

| 42      | XT2      | I/O | Crystal Output; REF_CLK input for RMII mode        |

| 43      | XT1      | -   | Crystal Input                                      |

### 5.6 Power, 12 pins

| Pin No.  | Pin Name | I/O | De                           | escription |

|----------|----------|-----|------------------------------|------------|

| 1,2      | AVDDR    | Р   | Analog Receive Power output  |            |

| 9        | AVDDT    | Р   | Analog Transmit Power output |            |

| 5        | AGND     | Р   | Analog Receive Ground        |            |

| 6        | AGND     | Р   | Analog Transmit Ground       |            |

| 46       | AGND     | Р   | Analog Substrate Ground      |            |

| 23,30,41 | DVDD     | Р   | Digital Power                |            |

| 15,33,44 | DGND     | Р   | Digital Ground               |            |

### 5.7 Table A (Media Type Seclection)

| OP2 | OP1 | OP0 | Function                                  |

|-----|-----|-----|-------------------------------------------|

| 0   | 0   | 0   | Dual Speed 100/10 HDX                     |

| 0   | 0   | 1   | Reserved                                  |

| 0   | 1   | 0   | Reserved                                  |

| 0   | 1   | 1   | Manually Select 10TX HDX                  |

| 1   | 0   | 0   | Manually Select 10TX FDX                  |

| 1   | 0   | 1   | Manually Select 100TX HDX                 |

| 1   | 1   | 0   | Manually Select 100TX FDX                 |

| 1   | 1   | 1   | Auto-negotiation Enables All Capabilities |

### 5.8 Pin Maps of Normal MII, Reduced MII, and 10Base-T GPSI (7-Wired) Mode

| Normal MII Mode       | Reduced MII Mode    | 10Base-T GPSI (7-Wired) Mode |

|-----------------------|---------------------|------------------------------|

| TXD [0:1]             | TXD [0:1]           | TXD [0] ; TXD [1] = NC       |

| TXD [2:3]             | NC                  | NC                           |

| TXEN                  | TXEN                | TXEN                         |

| TXER/TXD [4]          | NC                  | NC                           |

| TXCLK                 | NC                  | TXCLK                        |

| RXD [0:1]             | RXD [0:1]           | RXD [0] ; RXD [1] = NC       |

| RXD[2:3]              | NC                  | NC                           |

| RXER/RXD[4]/RPTR/NODE | RPTR/NODE           | RPTR/NODE                    |

| RXDV                  | CRS DV              | NC                           |

| RXCLK                 | NC                  | RXCLK                        |

| COL                   | NC                  | COL                          |

| CRS                   | NC                  | CRS                          |

| (PHYADR [2:4])        |                     |                              |

| (BP4B5B)              |                     |                              |

| MDC                   | MDC                 | MDC                          |

| MDIO                  | MDIO                | MDIO                         |

| RESET#                | RESET#              | RESET#                       |

| XT1 (25 MHz)          | XT2 (REF_CLK 50MHz) | XT1 (25 MHz)                 |

### **6.LED Configuration**

LEDs flash once per 500ms after power-on reset or software reset by writing PHY register. All LED pins are dual function pins, which can be configured as either active high or low by pulling them low or high accordingly. If the pin is pulled high, the LED is active low after reset. Likewise, if the pin is pulled low, the LED is active high.

### **6.1 LED Function Description**

#### Nornal LED mode

| LED0     | 11 | FDX <sup>1</sup>      | FDX <sup>1</sup> | Active depend on strap value <sup>2</sup> |

|----------|----|-----------------------|------------------|-------------------------------------------|

| LED1     | 12 | SPEED                 | SPEED            |                                           |

| LED2     | 13 | LK_ACT                | TX_RX_ACT        |                                           |

| CABLESTS | 14 | CABLESTS(High active) | LINK(low active) |                                           |

Note1 & Note2:

FDX:Active status indicate the full-duplex mode.

SPEED: Active status indicate the 100Mbps mode.

LK-ACT: Active status indicate the good link for 100Mbps and 100Mbps operations.It's flash when transnitting or receiving data

#### For Dual-LED.

|     | LEDMODE = 0      |                  |               |                  |      |                              |  |  |  |

|-----|------------------|------------------|---------------|------------------|------|------------------------------|--|--|--|

|     | Pin14, Pulldow   | 'n               | Pin_14 pullup |                  |      |                              |  |  |  |

| Pin | LinkFail         | 100M             |               | 10M              |      |                              |  |  |  |

|     |                  | Link             | Act           | Link             | Act  | 7                            |  |  |  |

| 11  | Lo               | Lo               | LoHi          | Hi               | HiLo | Same Previous define         |  |  |  |

| 12  | Lo               | Hi               |               | Lo               |      | Same Previous define         |  |  |  |

| 13  | FDX <sup>1</sup> | FDX <sup>1</sup> |               | FDX <sup>1</sup> |      | FDX_COL, collision flash out |  |  |  |

| 14  | CABLESTS(H       |                  |               |                  |      | LINK(low active)             |  |  |  |

When Half mode LED is blank. The collision status can flash output by change register 16.5, set to High.

TX-RX-ACT: Active flash when transmitting and receiving data.

CABLESTS: Active status indicate the cable connection.

LINK: Active status indicate the good link 10Mbps or 100Mbps operation.

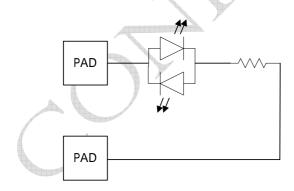

#### 16.1.1 Dual-LED application circuit.

### 7. Functional Description

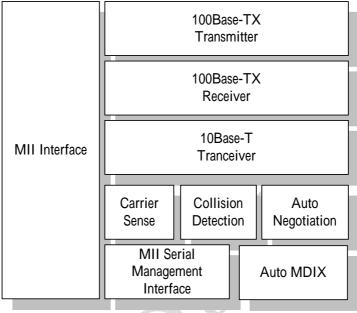

The DM9161A Fast Ethernet single chip transceiver,

providing the functionality as specified in IEEE 802.3u,

13

<sup>&</sup>lt;sup>2</sup> Application reference 6.1.0

integrates a complete 100Base-TX module and a complete 10Base-T module. The DM9161A provides a Media Independent Interface (MII) as defined in the IEEE 802.3u standard (Clause 22).

The DM9161A performs all PCS (Physical Coding Sublayer),

PMA (Physical Media Access), TP-PMD (Twisted Pair Physical Medium Dependent) sublayer, 10Base-T Encoder/Decoder, and Twisted Pair Media Access Unit (TPMAU) functions. Figure 7-1 shows the major functional blocks implemented in the DM9161A.

Figure 7-1

#### 7.1 MII Interface

The DM 9161A provides a Media Independent Interface (MII) as defined in the IEEE 802.3u standard (Clause 22).

The purpose of the MII interface is to provide a simple, easy to implement connection between the MAC Reconciliation layer and the PHY. The MII is designed to make the differences between various media transparent to the MAC sublayer.

The MII consists of a nibble wide receive data bus, a nibble wide transmit data bus, and control signals to facilitate data transfers between the PHY and the Reconciliation layer.

TXD (transmit data) is a nibble (4 bits) of data that are driven by the reconciliation sublayer synchronously with respect to TXCLK. For each TXCLK period, which TXEN is asserted, TXD (3:0) are accepted for transmission by the PHY.

- TXCLK (transmit clock) output to the MAC reconciliation sublayer is a continuous clock that provides the timing reference for the transfer of the TXEN, TXD, and TXER signals.

- TXEN (transmit enable) input from the MAC reconciliation sublayer indicates that nibbles are being presented on the MII for transmission on the physical medium.

#### MII Interface (continued)

- TXER (transmit coding error) transitions are synchronously with respect to TXCLK. If TXER is asserted for one or more clock periods, and TXEN is asserted, the PHY will emit one or more symbols that are not part of the valid data delimiter set somewhere in the frame being transmitted.

- RXD (receive data) is a nibble (4 bits) of data that are sampled by the reconciliation sublayer synchronously with respect to RXCLK. For each RXCLK period which RXDV is asserted, RXD (3:0) are transferred from the PHY to the MAC reconciliation sublayer.

- RXCLK (receive clock) output to the MAC reconciliation sublayer is a continuous clock that provides the timing reference for the transfer of the RXDV, RXD, and RXER signals.

- RXDV (receive data valid) input from the PHY indicates that the PHY is presenting recovered and decoded nibbles to the MAC reconciliation sublayer. To interpret a receive frame correctly by the reconciliation sublayer, RXDV must encompass the frame, starting no later than the Start-of-Frame delimiter and excluding any End-Stream delimiter.

- RXER (receive error) transitions are synchronously with respect to RXCLK. RXER will be asserted for 1 or more clock periods to indicate to the reconciliation sublayer that an error was detected somewhere in the frame being transmitted from the PHY to the reconciliation sublayer.

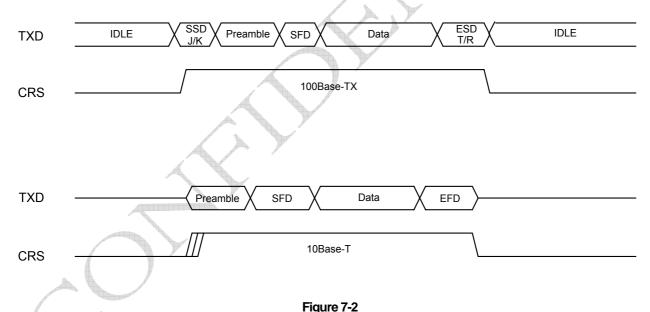

- CRS (carrier sense) is asserted by the PHY when either the transmit or receive medium is non-idle, and de-asserted by the PHY when the transmit and receive medium are idle. Figure 7-2 depicts the behavior of CRS during 10Base-T and 100Base-TX transmission.

**5**...

15 Preliminary

Version: DM9161A-DS-P04 Jan.19,2005

#### 7.2 100Base-TX Operation

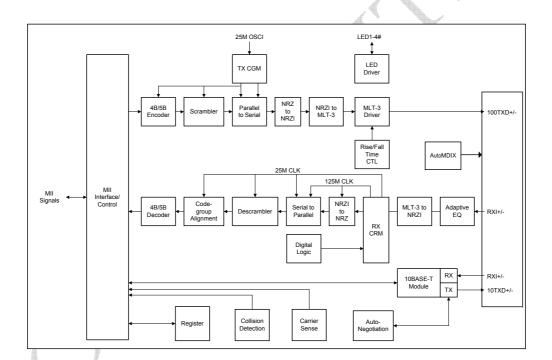

The 100Base-TX transmitter receives 4-bit nibble data clocked in at 25MHz at the MII, and outputs a scrambled 5-bit encoded MLT-3 signal to the media at 100Mbps. The on-chip clock circuit converts the 25MHz clock into a 125MHz clock for internal use.

The IEEE 802.3u specification defines the Media Independent Interface. The interface specification defines a dedicated receive data bus and a dedicated transmit data bus.

These two busses include various controls and signal indications that facilitate data transfers between the DM9161A and the Reconciliation layer.

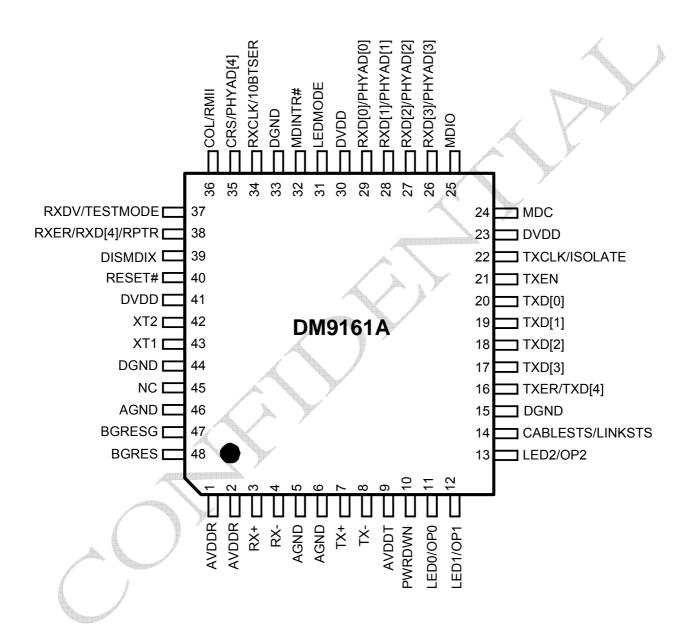

#### 7.2.1 100Base-TX Transmit

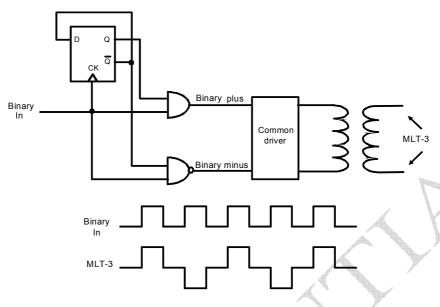

The 100Base-TX transmitter consists of the functional blocks shown in figure 7-3. The 100Base-TX transmit section converts 4-bit synchronous data provided by the MII to a scrambled MLT-3 125, a million symbols per second serial data stream.

Figure 7-3

The block diagram in figure 7-3 provides an overview of the functional blocks contained in the transmit section.

The transmitter section contains the following functional blocks:

- 4B5B Encoder

- Scrambler

- Parallel to Serial Converter

- NRZ to NRZI Encoder

- NRZI to MLT-3

- MLT-3 Driver

#### 7.2.1.1 4B5B Encoder

The 4B5B encoder converts 4-bit (4B) nibble data generated by the MAC Reconciliation Layer into a 5-bit (5B) code group for transmission, see reference Table 7-1. This conversion is required for control and packet data to be combined in code groups. The 4B5B encoder substitutes the first 8 bits of the MAC preamble with a J/K code group pair (11000 10001) upon transmit. The 4B5B encoder continues to replace subsequent 4B preamble and data nibbles with corresponding 5B code-groups. At the end of the transmit packet, upon the deassertion of the Transmit Enable signal from the MAC Reconciliation layer, the 4B5B encoder injects the T/R code group pair (01101 00111) indicating end of frame. After the T/R code group pair, the 4B5B encoder continuously injects IDLEs into the transmit data stream until Transmit Enable is asserted and the next transmit packet is detected.

The DM9161A includes a Bypass 4B5B conversion option within the 100Base-TX Transmitter for support of applications like 100 Mbps repeaters, which do not require 4B5B conversion.

#### 7.2.1.2 Scrambler

The scrambler is required to control the radiated emissions (EMI) by spreading the transmit energy across the frequency spectrum at the media connector and on the twisted pair cable in 100Base-TX operation.

By scrambling the data, the total energy presented to the cable is randomly distributed over a wide frequency range. Without the scrambler, energy levels on the cable could peak beyond FCC limitations at frequencies related to repeated 5B sequences like continuous transmission of IDLE symbols. The scrambler output is combined with the NRZ 5B data from the code group encoder via an XOR logic function. The result is a scrambled data stream with sufficient randomization to decrease radiated emissions at critical frequencies.

#### 7.2.1.3 Parallel to Serial Converter

The Parallel to Serial Converter receives parallel 5B scrambled data from the scrambler and serializes it (converts it from a parallel to a serial data stream). The serialized data stream is then presented to the NRZ to NRZI encoder block

#### 7.2.1.4 NRZ to NRZI Encoder

Since the transmit data stream has been scrambled and serialized, the data must be NRZI encoded for compatibility with the TP-PMD standard for 100Base-TX transmission over Category-5 unshielded twisted pair cable.

#### 7.2.1.5 MLT-3 Converter

The MLT-3 conversion is accomplished by converting the data stream output from the NRZI encoder into two binary data streams with alternately phased logic one events.

#### 7.2.1.6 MLT-3 Driver

The two binary data streams, created at the MLT-3 converter, are fed to the twisted pair output driver, which converts these streams to current sources and alternately drives either side of the transmit transformer's primary winding, resulting in a minimal current MLT-3 signal. Refer to figure 7-4 for the block diagram of the MLT-3 converter.

17 Preliminary

Version: DM9161A-DS-P04

### 7.2.1.7 4B5B Code Group

| Symbol     | Meaning | 4B code   | 5B Code |

|------------|---------|-----------|---------|

| <b>O</b> , |         | 3210      | 43210   |

| 0          | Data 0  | 0000      | 11110   |

| 1          | Data 1  | 0001      | 01001   |

| 2          | Data 2  | 0010      | 10100   |

| 3          | Data 3  | 0011      | 10101   |

| 4          | Data 4  | 0100      | 01010   |

| 5          | Data 5  | 0101      | 01011   |

| 6          | Data 6  | 0110      | 01110   |

| 7          | Data 7  | 0111      | 01111   |

| 8          | Data 8  | 1000      | 10010   |

| 9          | Data 9  | 1001      | 10011   |

| Α          | Data A  | 1010      | 10110   |

| В          | Data B  | 1011      | 10111   |

| С          | Data C  | 1100      | 11010   |

| D          | Data D  | 1101      | 11011   |

| Е          | Data E  | 1110      | 11100   |

| F          | Data F  | 1111      | 11101   |

|            |         |           |         |

| I          | Idle    | undefined | 11111   |

| J          | SFD (1) | 0101      | 11000   |

| K          | SFD (2) | 0101      | 10001   |

| Т          | ESD (1) | undefined | 01101   |

| R          | ESD (2) | undefined | 00111   |

| Н          | Error   | undefined | 00100   |

|            |         |           |         |

| V          | Invalid | undefined | 00000   |

| V          | Invalid | undefined | 00001   |

| V          | Invalid | undefined | 00010   |

| V          | Invalid | undefined | 00011   |

| V          | Invalid | undefined | 00101   |

| V          | Invalid | undefined | 00110   |

| V          | Invalid | undefined | 01000   |

| V          | Invalid | undefined | 01100   |

| V          | Invalid | undefined | 10000   |

| V          | Invalid | undefined | 11001   |

Table 7-1

#### Figure 7-4

#### 7.2.2 100Base-TX Receiver

The 100Base-TX receiver contains several function blocks that convert the scrambled 125Mb/s serial data to synchronous 4-bit nibble data, which is then provided to the MII.

The receive section contains the following functional blocks:

- Signal Detect

- Adaptive Equalizer

- MLT-3 to NRZI Decoder

- Clock Recovery Module

- NRZI to NRZ Decoder

- Serial to Parallel

- Descrambler

- Code Group Alianment

- 4B5B Decoder

#### 7.2.2.1 Signal Detect

The signal detect function meets the specifications mandated by the ANSI XT12 TP-PMD 100Base-TX Standards for both voltage thresholds and timing parameters.

#### 7.2.2.4 Clock Recovery Module

#### 7.2.2.2 Adaptive Equalizer

When transmitting data at high speeds over copper twisted pair cable, attenuation based on frequency becomes a concern. In high speed twisted pair signaling, the frequency content of the transmitted signal can vary greatly during normal operation based on the randomness of the scrambled data stream. This variation in signal attenuation caused by frequency variations must be compensated for to ensure the integrity of the received data. In order to ensure quality transmission when employing MLT-3 encoding, the compensation must be able to adapt to various cable lengths and cable types depending on the installed environment. The selection of long cable lengths for a given implementation requires significant compensation, which will be over-kill in a situation that includes shorter, less attenuating cable lengths. Conversely, the selection of short or intermediate cable lengths requiring less compensation will cause serious under-compensation for longer length cables. Therefore, the compensation or equalization must be adaptive to ensure proper conditioning of the received signal independent of the cable length.

#### 7.2.2.3 MLT-3 to NRZI Decoder

The DM9161A decodes the MLT-3 information from the Digital Adaptive Equalizer into NRZI data. The relation between NRZI and MLT-3 data is shown in figure 7-4.

The Clock Recovery Module accepts NRZI data from the MLT-3 to NRZI decoder. The Clock Recovery Module locks

19

onto the data stream and extracts the 125MHz reference clock. The extracted and synchronized clock and data are presented to the NRZI to NRZ Decoder.

#### **7.2.2.5 NRZI to NRZ**

The transmit data stream is required to be NRZI encoded in for compatibility with the TP-PMD standard for 100Base-TX transmission over Category-5 unshielded twisted pair cable. This conversion process must be reversed on the receive end. The NRZI to NRZ decoder, receives the NRZI data stream from the Clock Recovery Module and converts it to a NRZ data stream to be presented to the Serial to Parallel conversion block.

#### 7.2.2.6 Serial to Parallel

The Serial to Parallel Converter receives a serial data stream from the NRZI to NRZ converter, and converts the data stream to parallel data to be presented to the descrambler.

#### 7.2.2.7 Descrambler

Because the scrambling process requires to control the radiated emissions of transmit data streams, the receiver must descramble the receive data streams. The descrambler receives scrambled parallel data streams from the Serial to Parallel converter, descrambles the data streams, and presents the data streams to the Code Group alignment block.

#### 7.2.2.8 Code Group Alignment

The Code Group Alignment block receives un-aligned 5B data from the descrambler and converts it into 5B code group data. Code Group Alignment occurs after the J/K is detected, and subsequent data is aligned on a fixed boundary.

#### 7.2.2.9 4B5B Decoder

The 4B5B Decoder functions as a look-up table that translates incoming 5B code groups into 4B (Nibble) data. When receiving a frame, the first 2 5-bit code groups received are the start-of-frame delimiter (J/K symbols). The J/K symbol pair is stripped and two nibbles of preamble pattern are substituted. The last two code groups are the end-of-frame delimiter (T/R symbols).

The T/R symbol pair is also stripped from the nibble presented to the Reconciliation layer.

The 10Base-T transceiver is IEEE 802.3u compliant. When the DM9161A is operating in 10Base-T mode, the coding scheme is Manchester. Data processed for transmit is presented to the MII interface in nibble format, converted to a serial bit stream, then Manchester encoded. When receiving, the Manchester encoded bit stream is decoded and converted into nibble format for presentation to the MII interface.

#### 7.2.4 Collision Detection

For half-duplex operation, a collision is detected when the transmit and receive channels are active simultaneously. When a collision has been detected, it will be reported by the COL signal on the MII interface. Collision detection is disabled in Full Duplex operation.

#### 7.2.5 Carrier Sense

Carrier Sense (CRS) is asserted in half-duplex operation during transmission or reception of data. During full-duplex mode, CRS is asserted only during receive operations.

#### 7.2.6 Auto-Negotiation

The objective of Auto-negotiation is to provide a means to exchange information between segment linked devices and to automatically configure both devices to take maximum advantage of their abilities. It is important to note that Auto-negotiation does not test the link segment characteristics. The Auto-Negotiation function provides a means for a device to advertise supported modes of operation to a remote link partner, acknowledge the receipt and understanding of common modes of operation, and to reject un-shared modes of operation. This allows devices on both ends of a segment to establish a link at the best common mode of operation. If more than one common mode exists between the two devices, a mechanism is provided to allow the devices to resolve to a single mode of operation using a predetermined priority resolution function.

#### **Auto-Negotiation** (continued)

Auto-negotiation also provides a parallel detection function for devices that do not support the Auto-negotiation feature. During Parallel detection there is no exchange of configuration information, instead, the receive signal is examined. If it is discovered that the signal matches a technology, supported by the receiving device, a connection will be automatically established using that technology. This allows devices, which do not support Auto-negotiation but support a common mode of operation, to establish a link.

#### 7.2.7 MII Serial Management

The MII serial management interface consists of a data interface, basic register set, and a serial management interface to the register set. Through this interface it is possible to control and configure multiple PHY devices, get status and error information, and determine the type and capabilities of the attached PHY device(s).

The DM9161A management functions correspond to MII specification for IEEE 802.3u-1995 (Clause 22) for registers 0 through 6 with vendor-specific registers 16,17, 18, 21, 22, 23 and 24.

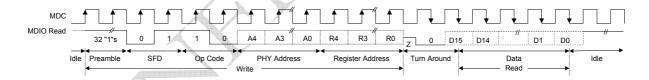

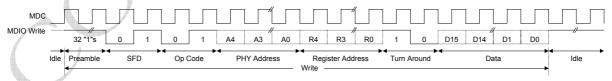

In read/write operation, the management data frame is 64-bits long and starts with 32 contiguous logic one bits (preamble) synchronization clock cycles on MDC. The Start of Frame Delimiter (SFD) is indicated by a <01> pattern followed by the operation code (OP):<10> indicates Read operation and <01> indicates Write operation. For read operation, a 2-bit turnaround (TA) filing between Register Address field and Data field is provided for MDIO to avoid contention. Following the turnaround time, 16-bit data is read from or written onto management registers.

#### 7.2.8 Serial Management Interface

The serial control interface uses a simple two-wired serial interface to obtain and control the status of the physical layer through the MII interface. The serial control interface consists of MDC (Management Data Clock), and MDI/O (Management Data Input/Output) signals.

The MDIO pin is bi-directional and may be shared by up to 32 devices.

#### 7.2.9 Management Interface - Read Frame Structure

#### 7.2.10 Management Interface - Write Frame Structure

Figure 7-5

Preliminary

Version: DM9161A-DS-P04 Jan.19,2005

#### 7.2.11 Power Reduced Mode

The Signal detect circuit is always turned on to monitor whether there is any signal on the media. In case of cable disconnection,, DM9161A will automatically turn off the power and enter the Power Reduced mode, regardless of its operation mode being N-way auto-negotiation or forced mode. While in the Power Reduced mode, the transmit circuit will continue sending out fast link pulse with minimum power consumption. If a valid signal is detected from the media, which might be N-way fast link pulse, 10Base-T normal link pules, or 100Base-TX MLT3 signals, the device wakes up and resumes normal operation mode.

Automatic reduced power down mode can be disabled by writing Zero to Reg.16.4.

#### 7.2.12 Power Down Mode

Power Down mode is entered by setting Reg.0.11 to ONE or pulling PWRDWN pin high, which disables all transmit and receive functions, and MII interface functions except the MDC/MDIO management interface.

#### 7.2.13 Reduced Transmit Power Mode

Additional transmit power reduction can be gained by designing with 1.25:1 turns ration magnetic on its TX side and using a 8.5K resistor on BGRES and BGRESG pins, and the TX+/TX- pulled high resistors being changed from 50 to 78. This configuration could reduce about 20% of transmit power.

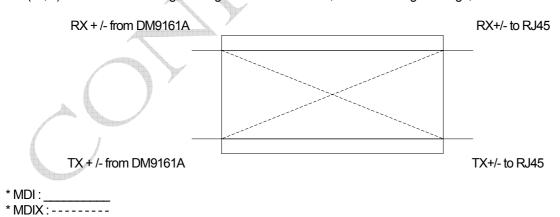

#### 7.3 Auto MDIX Functional Description

The DM9161A supports the automatic detect cable connection type, MDI/MDIX (straight through/cross over). A manual configuration by register bit for MDI or MDIX is still accepted.

When set to automatic, the polarity of MDI/MDIX controlled timing is generated by a 16-bits LFSR. The switching cycle time is located from 200ms to 420ms. The polarity control is always switch until detect received signal. After selected MDI or MDIX, the polarity status can be read by register bit (20.7).(See page33,8.12 specified config register-20 bit 7)7.3.1 Function Setting. Pin 39 is used to enable Auto MDIX function.

Pull pin 39 low will enable it, and pull pin 39 high will disable it.

Specified config Register 20 bit 4 (20, 4) is used by programmer to disable Auto MDIX function. Write register 20 bit 4 to "1" will disable Auto MDIX function. Its default value is "0". When the register 20 bit 4 (20, 4) is set to "1", the register 20 bit 5(20, 5) is used to select straight through or cross over mode, "0" is for straight through, and "1" is for cross over.

This feature is able to detect the required cable connection type.( straight through or crossed over ) and make correction automatically

### 8. MII Register Description

Preliminary Version: DM9161A-DS-P04 Jan.19, 2005

| AD<br>D | Name              | 15             | 14             | 13             | 12               | 11             | 10                    | 9                 | 8                  | 7               | 6               | 5                | 4               | 3                | 2               | 1                | 0                 |

|---------|-------------------|----------------|----------------|----------------|------------------|----------------|-----------------------|-------------------|--------------------|-----------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-------------------|

| 00      | CONTROL           | Reset          | Loop<br>back   | Speed select   | Auto-N<br>Enable | Power<br>Down  | Isolate               | Restart<br>Auto-N | Full<br>Duplex     | Coll.<br>Test   |                 |                  |                 | Reserved         |                 |                  |                   |

|         |                   | 0              | 0              | 1              | 1                | 0              | 0                     | 0                 | 1                  | 0               |                 |                  |                 | 0000_0000        |                 |                  |                   |

| 01      | STATUS            | T4<br>Cap.     | TX FDX<br>Cap. | TX HDX<br>Cap. | 10 FDX<br>Cap.   | 10 HDX<br>Cap. |                       | Rese              | erved              |                 | Pream.<br>Supr. | Auto-N<br>Compl. | Remote<br>Fault | Auto-N<br>Cap.   | Link<br>Status  | Jabber<br>Detect | Extd<br>Cap.      |

|         |                   | 0              | 1              | 1              | 1                | 1              |                       | 00                | 00                 |                 | 1               | 0                | 0               | 1                | 0               | 0                | 1                 |

| 02      | PHYID1            | 0              | 0              | 0              | 0                | 0              | 0                     | 0                 | 1                  | 1               | 0               | 0                | 0               | 0                | 0               | 0                | 0                 |

| 03      | PHYID2            | 1              | 0              | 1              | 1                | 1              | 0                     |                   |                    | Model No.       |                 |                  |                 | 1                | /ersion No.     |                  |                   |

|         |                   |                |                |                | -                |                |                       |                   |                    | 01010           |                 |                  |                 |                  | 0000            | A                | 1                 |

| 04      | Auto-Neg.         | Next           | FLP Rcv        | Remote         | Rese             | erved          | FC                    | T4                | TXFDX              | TX HDX          | 10 FDX          | 10 HDX           |                 | Advertised       | Protocol Se     | lector Field     |                   |

|         | Advertise         | Page           | Ack            | Fault          |                  |                | Adv                   | Adv               | Adv                | Adv             | Adv             | Adv              |                 |                  |                 |                  |                   |

| 05      | Link Part.        | LP             | LP             | LΡ             | Rese             | erved          | LP                    | LP                | LP                 | LP              | LP              | LP               | L               | ink Partner      | Protocol Se     | elector Field    |                   |

|         | Ability           | Next<br>Page   | Ack            | RF             |                  |                | FC                    | T4                | TXFDX              | TX HDX          | 10 FDX          | 10 HDX           |                 |                  |                 |                  |                   |

| 06      | Auto-Neg.         |                |                |                |                  |                | Reserved              |                   |                    |                 |                 | ı                | Pardet          | LP Next          | Next Pg         | New Pg           | LP AutoN          |

|         | Expansion         |                |                |                |                  | _              |                       | _                 |                    | -               | _               | _                | Fault           | Pg Able          | Able            | Rcv              | Cap.              |

| 16      | Specified Config. | BP<br>4B5B     | BP<br>SCR      | BP<br>ALIGN    | BP_ADP<br>OK     | Repeater       | TX                    | FEF_EN            | RMII_E<br>N        | Force<br>100LNK | TST_SE<br>L0    | LEDCO<br>L SEL   |                 | Reset<br>St. Mch | Pream.<br>Supr. | Sleep<br>mode    | Remote<br>LoopOut |

| 17      | Specified         | 100            | 100            | 10             | 10 HDX           | Reserve        | Reverse               | Reverse           |                    | PH              | YADDR           | 4:0]             |                 |                  | luto-N. Mor     | nitor Bit [3:0   |                   |

|         | Conf/Stat         | FDX            | HDX            | FDX            |                  | d              | d                     | d                 |                    |                 |                 |                  |                 |                  |                 |                  |                   |

| 18      | 10T               | Rsvd           | LP             | HBE            | SQUE             | JAB            | 10T                   |                   |                    |                 |                 | Reserved         | İ               | A. A.            |                 |                  | Polarity          |

|         | Conf/Stat         |                | Enable         | Enable         | Enable           | Enable         | Serial                |                   |                    |                 |                 | . €              |                 |                  |                 |                  | Reverse           |

| 19      | PWDOR             |                | L L            |                | Reserve          | d              | ·                     | I                 | PD10D<br>V         | R PD100         | )I PDchi        | p PDcm           | n PDaeq         | PDdrv            | PDedi           | PDedo            | PD10              |

| 20      | Specified         | TSTSE          | 1 TOTOE2       | FORCE          | FORCE            | 1              | Por                   | served            |                    | MDIX            | C AutoNe        | eg Mdix f        | iv Mdiv do      | MonSol           | MonSel0         | Dmii acc         | PD_valu           |

| 20      | config            | ISISE          | 1010L2         | TXSD           | FEF              |                | Nex                   | sciveu            |                    | NTL             | _dlpbl          |                  |                 | IVIOLISE         | IVIOLISCIO      | u<br>u           | e e               |

| 21      | MDINTR            | Int_sts        | Reserve<br>d   | Reserve<br>d   | Reverse<br>d     | Fdx_ms         | k Spd_ms              | k Lnk_ms          | k Int_ms           | k Reserv        | e Resen         | /e Revers        | e Fdx_chg       | Spd_cho          | Lnk_chg         | Reserve<br>d     | Int_sts           |

| _       | 50.55             |                | u              | u              | u                |                |                       |                   | <u> </u>           | 4               | -               | u                |                 |                  |                 | u                |                   |

| 22      | RCVER             |                |                |                |                  |                |                       |                   | Receiver           | Error Cour      | nter            |                  |                 |                  |                 |                  |                   |

| 23      | DIS_connec<br>t   | Reversed       |                |                |                  |                |                       | K                 | and the second     |                 | Disconne        | ect_counte       | r               |                  |                 |                  |                   |

| 24      | RSTLH             | Lh_led<br>mode |                | Lh_cabst<br>s  | Lh_isola<br>e    | t Lh_mii       | Lh_seril <sup>2</sup> | Lh_repe           | ea Lh_testr<br>ode | m Lh_op2        | 2 Lh_op         | 1 Lh_op          | 0 Lh_phya<br>d4 | Lh_phya<br>d3    | Lh_phya<br>d2   | Lh_phya<br>d1    | Lh_phya<br>d0     |

### **Key to Default**

In the register description that follows, the default column takes the form:

<Reset Value>, <Access Type> / <Attribute(s)>

### Where:

<Reset Value>:

1 Bit set to logic one

0 Bit set to logic zero

X No default value

(PIN#) Value latched in from pin # at reset

<Access Type>:

RO = Read only

RW = Read/Write

<Attribute (s)>: