## 500-kHz Push-Pull DC-DC Converter With Integrated Secondary Synchronous Rectification Control

### **FEATURES**

- 12-V to 72-V Input Voltage Range

- Compatible with ETSI 300 132-2 100 V, 100-ms Transients

- Integrated Push-Pull 1-A Primary Drivers

- Voltage Mode Control

- Voltage Feedforward Compensation

- High Voltage Pre-Regulator Operates During Start-Up

- Current Sensing On OUT<sub>B</sub> Primary Device

- Hiccup Current Control During Shorted Load

- Low Input Voltage Detection

- Programmable Soft-Start Function

- Programmable Oscillator Frequency

- Over Temperature Protection

### **APPLICATIONS**

- Network Cards

- Power Supply Modules

### **DESCRIPTION**

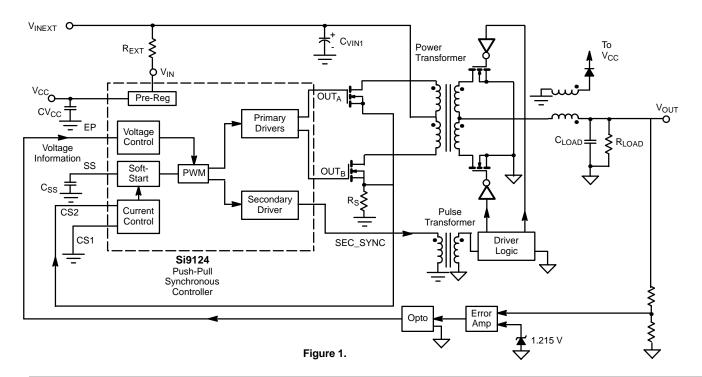

Si9124 is a dedicated push-pull controller IC ideally suited to fixed telecom dc-dc converter applications where high efficiency is required at low output voltages (e.g. <3.3 V). Designed to operate within the voltage range of 12-72 V and withstand 100 V, 100 ms transients, the IC is capable of controlling and directly driving both primary side MOSFET switches of a push-pull circuit.

High conversion efficiency is achieved by use of synchronous rectifying MOSFET transistors in the secondary. Due to the

very low on-resistance of the secondary MOSFETs, a significant increase in the efficiency can be achieved as compared with conventional Schottky diodes for today's low output voltages. On-chip control of the dead time delays between the primary and secondary signals keep efficiencies high and prevents accidental destruction of the power transformer or wasted energy from self timed approaches. Such a system can achieve conversion efficiencies well in excess of 90%.

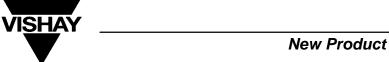

### **FUNCTIONAL BLOCK DIAGRAM**

Document Number: 72099 S-03638—Rev. B, 20-Mar-03

### **DESCRIPTION (CONTINUED)**

Si9124 has advanced current monitoring circuitry to permit the user to set the maximum current in the primary circuit. Such a feature acts as protection against output shorts. Upon sensing an overload condition, the converter is shut off for a period of time and then soft-start cycle is re-initiated, achieving hiccup mode operation. Current sensing is by means of a sense resistor on the primary device. An integrated over-temperature shutdown circuit also protects the system.

The 100-V depletion mode MOSFET integrated pre-regulator

circuit permits direct operation from input voltage with only one series resistor during startup. The pre-regulator automatically disconnects from the input supply when the output voltage is established by means of a feedback winding from the filter inductor.

Si9124 is available in <u>TSSOP-16</u> pin package. In order to satisfy the stringent ambient temperature requirements, Si9124 is rated to handle the industrial temperature range of –40 to 85°C.

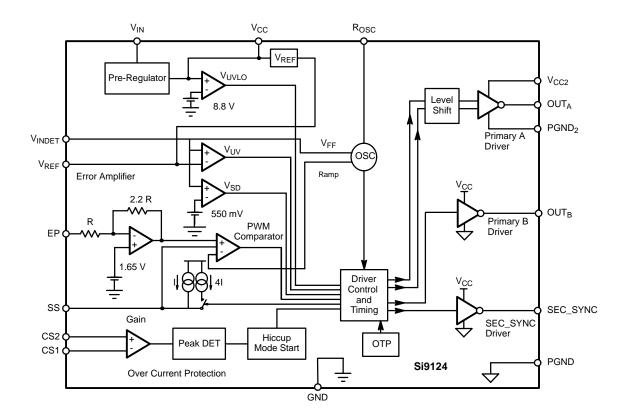

### **DETAILED BLOCK DIAGRAM**

Figure 2.

## Vishay Siliconix

### ABSOLUTE MAXIMUM RATINGS (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>IN</sub> (Continuous)                                         | HV Pre-Regulator Input Current (continuous) 5 mA                      |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|

| V <sub>IN</sub> (100 ms)                                             | Storage Temperature65 to 150°C                                        |

| V <sub>CC</sub>                                                      | Operating Junction Temperature                                        |

| V <sub>CC2</sub>                                                     | TSSOP-16 (T <sub>A</sub> = 25°C)                                      |

| V <sub>REF</sub> , R <sub>OSC</sub> 0.3 V to V <sub>CC</sub> + 0.3 V | Thermal Impedance ( $\Theta_{JA}$ )                                   |

| Logic Inputs0.3 V to V <sub>CC</sub> + 0.3 V                         | TSSOP-16 <sup>b</sup>                                                 |

| Analog Inputs                                                        | Notes a. Device mounted on JEDEC compliant 1S2P (4 layer) test board. |

| SEC_SYNC Drive Current                                               | b. Derate -10 mW/°C above 25°C.                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING RANGE (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>IN</sub>                                                                                         | C <sub>SS</sub>                              |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------|

| $C_{VIN1}  \   C_{VIN2}  \dots  100  \mu \text{F/ESR} \leq 100  \text{m} \Omega$ and 0.1 $\mu \text{F}$ | $C_{REF}$                                    |

| V <sub>CC</sub> Operating                                                                               | $C_{BOOST}$                                  |

| CV <sub>CC</sub>                                                                                        | $C_{LOAD}$                                   |

| f <sub>OSC</sub>                                                                                        | Analog Inputs                                |

| $R_{OSC}$                                                                                               | Digital Inputs 0 to V <sub>CC</sub>          |

| R <sub>EXT</sub>                                                                                        | Reference Voltage Output Current 0 to 2.5 mA |

| SPECIFICATIONS <sup>a</sup>      |                    |                                                                                                                                                                                                               |                       |       |      |      |

|----------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|------|

|                                  | Symbol             | Test Conditions Unless Specified $CS1 = CS2 = 0 \text{ V, } f_{NOM} = 500 \text{ kHz, } V_{IN} = 48 \text{ V} \\ V_{INDET} = 4.8 \text{ V; } 10 \text{ V} \leq V_{CC} \leq 13.2 \text{ V, } V_{CC2} = V_{CC}$ | Limits<br>-40 to 85°C |       |      |      |

| Parameter                        |                    |                                                                                                                                                                                                               | Minb                  | Typc  | Maxb | Unit |

| Reference (3.3 V)                |                    |                                                                                                                                                                                                               | •                     | •     | •    |      |

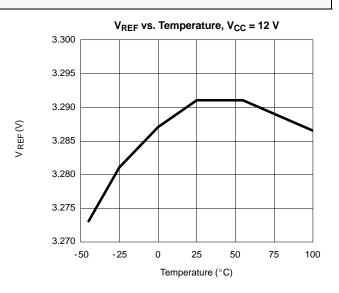

| Output Voltage                   | $V_{REF}$          | V <sub>CC</sub> = 12 V, 25°C Load = 0 mA                                                                                                                                                                      | 3.2                   | 3.3   | 3.4  | V    |

| Short Circuit Current            | I <sub>SREF</sub>  | V <sub>REF</sub> = 0 V                                                                                                                                                                                        |                       |       | -50  | mA   |

| Load Regulation                  | dVr/dlr            | I <sub>REF</sub> = 0 to -2.5 mA                                                                                                                                                                               |                       | -30   | -75  | mV   |

| Power Supply Rejection           | PSRR               | @ 100Hz                                                                                                                                                                                                       |                       | 60    |      | dB   |

| Oscillator                       |                    |                                                                                                                                                                                                               | *                     |       |      | •    |

| Accuracy (1% R <sub>OSC</sub> )  |                    | $R_{OSC} = 30 \text{ k}\Omega, f_{NOM} = 500 \text{ kHz}$                                                                                                                                                     | -20                   |       | 20   | %    |

| Max Frequency                    | F <sub>MAX</sub>   | R <sub>OSC</sub> = 24 kΩ                                                                                                                                                                                      |                       | 600   |      | kHz  |

| Error Amplifier                  | - 1                |                                                                                                                                                                                                               |                       |       | •    | ı    |

| Input Bias Current               | I <sub>BIAS</sub>  | V <sub>EP</sub> = 0 V                                                                                                                                                                                         | -40                   |       | -15  | μΑ   |

| Gain                             | A <sub>V</sub>     |                                                                                                                                                                                                               |                       | -2.2  |      | V/V  |

| Bandwidth                        | BW                 |                                                                                                                                                                                                               |                       | 5     |      | MHz  |

| Power Supply Rejection           | PSRR               | @ 100Hz                                                                                                                                                                                                       |                       | 60    |      | dB   |

| Slew Rate                        | SR                 |                                                                                                                                                                                                               |                       | 0.5   |      | V/μs |

| <b>Current Sense Amplifier</b>   |                    |                                                                                                                                                                                                               | •                     | •     | •    |      |

| Input Voltage CM Range           | $V_{CM}$           | V <sub>CS1</sub> - GND, V <sub>CS2</sub> - GND                                                                                                                                                                |                       | ± 150 |      | mV   |

| Input Amplifier Gain             | A <sub>VOL</sub>   |                                                                                                                                                                                                               |                       | 17.5  |      | dB   |

| Input Amplifier Bandwidth        | BW                 |                                                                                                                                                                                                               |                       | 5     |      | MHz  |

| Input Amplifier Offset Voltage   | Vos                |                                                                                                                                                                                                               |                       | ±5    |      |      |

| V <sub>CC</sub> Hiccup Threshold | V <sub>THCUP</sub> | Increase CS2 Until SS Hiccups                                                                                                                                                                                 |                       | 150   |      | mV   |

| Hysteresis                       |                    | Decrease CS2 Until SS Clamps                                                                                                                                                                                  |                       | -50   |      |      |

### **New Product**

|                                                             |                      | Test Conditions Unless Specified $CS1 = CS2 = 0 \text{ V, } f_{NOM} = 500 \text{ kHz, } V_{IN} = 48 \text{ V}$ $V_{INDET} = 4.8 \text{ V; } 10 \text{ V} \leq V_{CC} \leq 13.2 \text{ V, } V_{CC2} = V_{CC}$ |          | Limits<br>-40 to 85°C |      |                  |      |

|-------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|------|------------------|------|

| Parameter                                                   | Symbol               |                                                                                                                                                                                                              |          | Minb                  | Турс | Max <sup>b</sup> | Unit |

| PWM Operation                                               | •                    |                                                                                                                                                                                                              | •        |                       | •    | •                |      |

| Duta Carles                                                 | D <sub>MAX</sub>     | , south                                                                                                                                                                                                      | P = 0 V  | 90                    | 92   | 95               | 0/   |

| Duty Cycle <sup>e</sup>                                     | D <sub>MIN</sub>     | $f_{OSC} = 500 \text{ kHz}$                                                                                                                                                                                  | = 1.85 V |                       | < 15 |                  | %    |

| Pre-Regulator                                               |                      |                                                                                                                                                                                                              |          |                       |      |                  |      |

| Input Voltage (Continuous)                                  | V <sub>IN</sub>      | I <sub>IN</sub> = 10 μA                                                                                                                                                                                      |          |                       |      | 72               | V    |

| Input Leakage Current                                       | I <sub>LKG</sub>     | $V_{IN}$ = 72 V, $V_{CC}$ > $V_{REG}$                                                                                                                                                                        |          |                       |      | 10               |      |

|                                                             | I <sub>REG1</sub>    | $V_{IN}$ = 72 V, $V_{INDET}$ < $V_{SD}$                                                                                                                                                                      |          |                       | 86   | 200              | μΑ   |

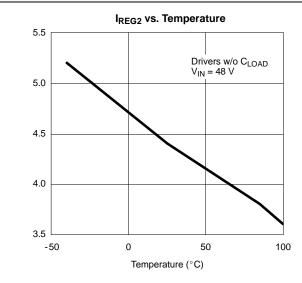

| Regulator Bias Current                                      | I <sub>REG2</sub>    | V <sub>IN</sub> = 72 V, V <sub>INDET</sub> > V <sub>REF</sub>                                                                                                                                                |          |                       | 4.5  | 7.5              |      |

| Pre-Regulator Drive Capacility                              | I <sub>START</sub>   | $V_{CC} < V_{REG}$                                                                                                                                                                                           |          | 20                    | 1    | 1                | mA   |

|                                                             | . v                  | V SV                                                                                                                                                                                                         |          | 7.4                   | 9.1  | 10.4             |      |

| V <sub>CC</sub> Pre-Regulator Turn Off<br>Threshold Voltage | V <sub>REG1</sub>    | $V_{INDET} > V_{REF}$ $T_A$                                                                                                                                                                                  | = 25°C   | 8.5                   | 9.1  | 9.7              |      |

| Threshold voltage                                           | V <sub>REG2</sub>    | V <sub>INDET</sub> = 0 V                                                                                                                                                                                     |          |                       | 9.2  |                  | V    |

| Undervoltage Lockout <sup>d</sup>                           | V <sub>UVLO</sub>    | $V_{CC}$ Rising $T_A = 25^{\circ}C$                                                                                                                                                                          |          | 7.15                  | 8.6  | 9.8              | ]    |

| Officervollage Lockout*                                     | VUVLO                |                                                                                                                                                                                                              | = 25°C   | 8.1                   | 8.6  | 9.3              |      |

| V <sub>UVLO</sub> Hysteresis                                | V <sub>UVLOHYS</sub> |                                                                                                                                                                                                              |          |                       | 0.5  |                  |      |

| Soft-Start                                                  |                      |                                                                                                                                                                                                              |          |                       |      |                  |      |

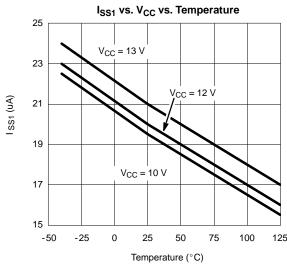

| Soft-Start Current Output                                   | I <sub>SS1</sub>     | $0 < V_{SS} < 2 V_{be}$                                                                                                                                                                                      |          | 12                    | 20   | 28               | μА   |

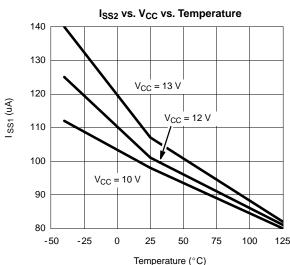

| Soit-Start Current Output                                   | I <sub>SS2</sub>     | $2 V_{be} < V_{SS} < 4.8 V$                                                                                                                                                                                  |          | 60                    | 100  | 200              | μΑ   |

| Soft-Start Completion Voltage                               | V <sub>SS_COMP</sub> | Normal Operation                                                                                                                                                                                             |          | 7.35                  | 8.1  | 8.85             | V    |

| Shutdown                                                    |                      |                                                                                                                                                                                                              |          |                       |      |                  |      |

| V <sub>INDET</sub> Shutdown FN                              | V <sub>SD</sub>      | V <sub>INDET</sub> Rising                                                                                                                                                                                    |          | 350                   | 550  | 720              |      |

| V <sub>INDET</sub> Hysteresis                               |                      | V <sub>INDET</sub>                                                                                                                                                                                           |          |                       | 200  |                  | mV   |

| V <sub>INDET</sub> Input Threshold V                        | oltages              |                                                                                                                                                                                                              | <u> </u> |                       | •    | •                |      |

| V <sub>INDET</sub> - V <sub>IN</sub> Under Voltage          | V <sub>UV</sub>      | V <sub>INDET</sub> Rising                                                                                                                                                                                    |          | 3.13                  | 3.3  | 3.46             |      |

| V <sub>INDET</sub> Hysteresis                               |                      | VINDET                                                                                                                                                                                                       |          |                       | 0.3  |                  | V    |

| Over Temperature Protec                                     | tion                 | 1                                                                                                                                                                                                            |          |                       | 1    | 1                |      |

| Activating Temperature                                      |                      | T <sub>J</sub> Increasing                                                                                                                                                                                    |          |                       | 160  |                  |      |

| De-Activating Temperature                                   |                      | T <sub>J</sub> Decreasing                                                                                                                                                                                    |          |                       | 130  |                  | °C   |

| Converter Supply Curren                                     | t (V <sub>CC</sub> ) | 1                                                                                                                                                                                                            | I        |                       | 1    | 1                |      |

| Shutdown                                                    | I <sub>CC1</sub>     | Shutdown, V <sub>INDET</sub> = 0 V                                                                                                                                                                           |          | 50                    | 140  | 350              | μΑ   |

| Switching Disabled                                          | I <sub>CC2</sub>     | V <sub>INDET</sub> < V <sub>REF</sub>                                                                                                                                                                        |          | 1.8                   | 2.8  | 3.8              | •    |

| Switching w/o Load <sup>f</sup>                             | I <sub>CC3</sub>     | $V_{\text{INDET}} > V_{\text{REF}}, f_{\text{NOM}} = 500 \text{ kHz}$                                                                                                                                        |          | 3.0                   | 4.4  | 6.8              |      |

| Switching with C <sub>LOAD</sub>                            | I <sub>CC4</sub>     | V <sub>CC</sub> = 12 V, OUT <sub>A</sub> = OUT <sub>B</sub> = 3 nF, C <sub>SEC_SYNC</sub>                                                                                                                    | = 0.3 nF |                       | 15.2 |                  | mA   |

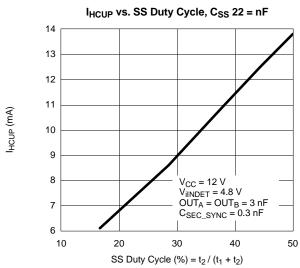

| V <sub>CC</sub> Hiccup Current                              | I <sub>HCUP</sub>    | CS2 - CS1 = 200 mV, C <sub>OUTA</sub> = C <sub>OUTB</sub> = 3<br>C <sub>SEC_SYNC</sub> = 0.3 nF                                                                                                              | 3 nF     |                       | 4.3  |                  |      |

## Vishay Siliconix

| SPECIFICATIONS <sup>a</sup> |                     |                                                                                                                       |                        |         |                            |      |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------|---------|----------------------------|------|

|                             |                     | Test Conditions Unless Specified CS1 = CS2 = 0 V, f <sub>NOM</sub> = 500 kHz, V <sub>IN</sub> = 48 V                  | Limits<br>-40 to 85°C  |         |                            |      |

| Parameter                   | Symbol              | $V_{\text{INDET}} = 4.8 \text{ V}; 10 \text{ V} \le V_{\text{CC}} \le 13.2 \text{ V}, V_{\text{CC2}} = V_{\text{CC}}$ | Minb                   | Турс    | Maxb                       | Unit |

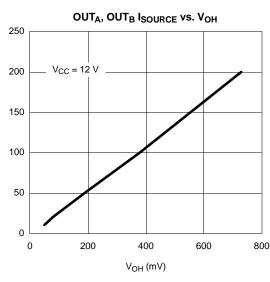

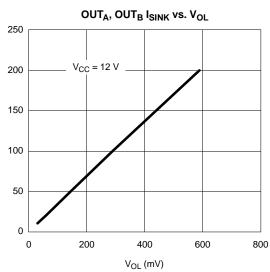

| Output A Primary Drive      | er                  |                                                                                                                       | l.                     | ,       | JI.                        | I.   |

| Output High Voltage         | V <sub>OH</sub>     | Sourcing 10 mA                                                                                                        | V <sub>CC2</sub> - 0.3 |         |                            | v    |

| Output Low Voltage          | V <sub>OL</sub>     | Sinking 10 mA                                                                                                         |                        |         | PGND <sub>2</sub><br>+ 0.3 |      |

| V <sub>CC2</sub> Current    | I <sub>CC5</sub>    |                                                                                                                       | 0.1                    | 1.55    | 1.1                        | mA   |

| Peak Output Source          | I <sub>SOURCE</sub> | V <sub>CC2</sub> = 12 V, PGND <sub>2</sub> = 0 V                                                                      |                        | -1.0    | -0.75                      |      |

| Peak Output Sink            | I <sub>SINK</sub>   |                                                                                                                       | 0.75                   | 1.0     |                            | Α    |

| Rise Time                   | t <sub>r</sub>      | T 07:00 0 0 5 W 10 W 00 00W                                                                                           |                        | 18      | 28                         |      |

| Fall Time                   | t <sub>f</sub>      | $T_A = 25$ °C, $C_{OUTA} = 3$ nF, $V_{CC} = 12$ V, $20 - 80$ %                                                        |                        | 22      | 28                         | ns   |

| Output B Primary Drive      | er                  |                                                                                                                       | •                      | ·       | •                          | I    |

| Output High Voltage         | V <sub>OH</sub>     | Sourcing 10 mA                                                                                                        | V <sub>CC</sub> - 0.3  |         |                            | V    |

| Output Low Voltage          | V <sub>OL</sub>     | Sinking 10 mA                                                                                                         |                        |         | 0.3                        | 1    |

| Peak Output Source          | I <sub>SOURCE</sub> |                                                                                                                       |                        | -1.0    | -0.75                      |      |

| Peak Output Sink            | I <sub>SINK</sub>   | V <sub>CC</sub> = 12 V, PGND = 0 V                                                                                    | 0.75                   | 1.0     |                            | Α    |

| Rise Time                   | t <sub>r</sub>      |                                                                                                                       |                        | 19      | 28                         |      |

| Fall Time                   | t <sub>f</sub>      | $T_A = 25$ °C, $C_{OUTB} = 3$ nF, $V_{CC} = 12$ V, 20 - 80%                                                           |                        | 24      | 28                         | ns   |

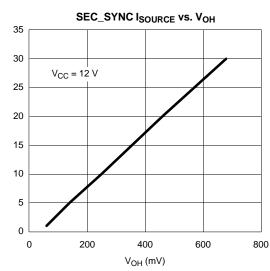

| Secondary_Synchrono         | us Driver           |                                                                                                                       |                        | I       |                            | I    |

| Output High Voltage         | V <sub>OH</sub>     | Sourcing 10 mA                                                                                                        | V <sub>CC</sub> - 0.4  |         |                            | V    |

| Output Low Voltage          | V <sub>OL</sub>     | Sinking 10 mA                                                                                                         |                        |         | 0.4                        |      |

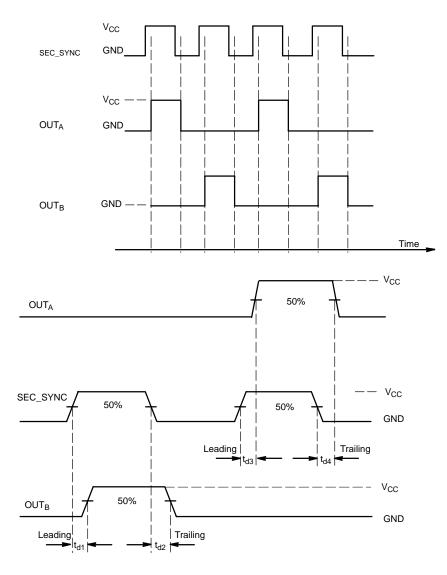

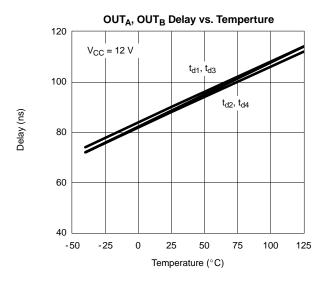

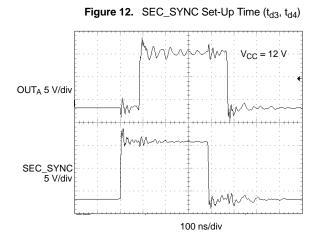

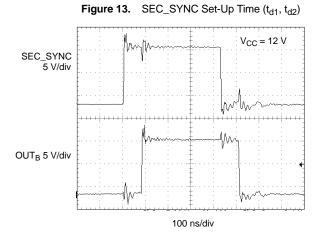

| Landing Edge Delays         | t <sub>d1</sub>     | T 0500 V 40 V 1 40 V 0-2 Figure 0                                                                                     |                        | 80 110  | 110                        | ns   |

| Leading Edge Delays         | t <sub>d3</sub>     | T <sub>A</sub> = 25°C, V <sub>CC</sub> = 12 V, L <sub>X</sub> = 48 V, See <u>Figure 3</u>                             |                        | 80      | 110                        |      |

| Tarilla a Edua Dalassa      | t <sub>d2</sub>     | C <sub>OUTA</sub> = C <sub>OUTB</sub> = 3nF, C <sub>SEC_SYNC</sub> = 0.3 nF                                           |                        | 80      | 110                        |      |

| Trailing Edge Delays        | t <sub>d4</sub>     |                                                                                                                       |                        | 80      | 110                        |      |

| Peak Output Source          | I <sub>SOURCE</sub> | V 40V                                                                                                                 |                        | -100    |                            | 1 .  |

| Peak Output Sink            | I <sub>SINK</sub>   | V <sub>CC</sub> = 12 V                                                                                                |                        | 100     |                            | mA   |

| Rise Time                   | t <sub>r</sub>      |                                                                                                                       |                        | 16      | 28                         |      |

| Fall Time                   | t <sub>f</sub>      | $T_A = 25^{\circ}\text{C}, C_{\text{SEC\_SYNC}} = 0.3 \text{ nF}, V_{\text{CC}} = 12 \text{ V}, 20 - 80\%$            |                        | 17      | 28                         | ns   |

| Voltage Mode                | •                   |                                                                                                                       |                        |         |                            | •    |

| F                           | t <sub>d1A</sub>    | Input to A-side switch off                                                                                            |                        | < 200   |                            | ns   |

| Error Amplifier             | t <sub>d2B</sub>    | Input to B-side switch off                                                                                            |                        | < 200   |                            |      |

| Current Mode                |                     |                                                                                                                       |                        |         |                            |      |

| Current Amplifier           | t <sub>d3A</sub>    | Input to A-side switch off                                                                                            |                        | < 200   |                            | ne   |

|                             | t <sub>d4B</sub>    | Input to B-side switch off                                                                                            |                        | <200 ns |                            |      |

- a. b.

- Refer to PROCESS OPTION FLOWCHART for additional information.

The algebraic convention whereby the most negative value is a minimum and the most positive a maximum (-40° to 85°C).

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing and are measured at V<sub>CC</sub> = 12 V unless otherwise noted.

V<sub>UVLO</sub> tracks V<sub>REG1</sub> by a diode drop.

Measured on OUT<sub>A</sub> or OUT<sub>B</sub> outputs.

Note total supply current drawn is I<sub>CC3</sub> plus I<sub>CC5</sub>.

- c. d. e. f.

### **TIMING DIAGRAMS FOR MOS DRIVERS**

Figure 3.

Soft-Start, Hiccup Mode Operation

### **PIN CONFIGURATION**

#### Si9124DQ (TSSOP-16) $V_{\text{CC2}}$ $V_{\text{IN}}$ 16 $\mathsf{OUT}_\mathsf{A}$ $V_{\text{CC}}$ 2 15 $\mathsf{V}_{\mathsf{REF}}$ 3 PGND<sub>2</sub> 14 GND $\mathsf{OUT}_\mathsf{B}$ 4 13 $\mathsf{R}_{\mathsf{OSC}}$ 5 12 **PGND** SEC\_SYNC ΕP 6 11 SS $\mathsf{V}_{\mathsf{INDET}}$ 7 10 CS1 CS2 8 9

Top View

| ORDERING INFORMATION |                   |               |  |

|----------------------|-------------------|---------------|--|

| Part Number          | Temperature Range | Package       |  |

| Si9124DQ-T1          | -40 to 85°C       | Tape and Reel |  |

| Si9124DQ             | -40 to 65 C       | Bulk          |  |

| PIN DESCRIPTION |                    |                                                                                                                                                                                                         |  |

|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Number      | Name               | Function                                                                                                                                                                                                |  |

| 1               | V <sub>IN</sub>    | Input supply voltage for the start-up circuit.                                                                                                                                                          |  |

| 2               | V <sub>CC</sub>    | Supply voltage for internal circuitry                                                                                                                                                                   |  |

| 3               | $V_{REF}$          | 3.3-V reference, decoupled with 1-µF capacitor                                                                                                                                                          |  |

| 4               | GND                | Analog Ground                                                                                                                                                                                           |  |

| 5               | R <sub>OSC</sub>   | External resistor connection to oscillator                                                                                                                                                              |  |

| 6               | EP                 | Voltage control input                                                                                                                                                                                   |  |

| 7               | V <sub>INDET</sub> | V <sub>IN</sub> under voltage detect and shutdown function input. Shuts down or disables switching when V <sub>INDET</sub> falls below preset threshold voltages and provides the feed forward voltage. |  |

| 8               | CS1                | Current limit amplifier negative input                                                                                                                                                                  |  |

| 9               | CS2                | Current limit amplifier positive input                                                                                                                                                                  |  |

| 10              | SS                 | Soft-Start control - external capacitor connection                                                                                                                                                      |  |

| 11              | SEC_SYNC           | Secondary side timing signal                                                                                                                                                                            |  |

| 12              | PGND               | A driver power ground.                                                                                                                                                                                  |  |

| 13              | OUTB               | B gate drive signal – primary                                                                                                                                                                           |  |

| 14              | PGND <sub>2</sub>  | B driver power ground                                                                                                                                                                                   |  |

| 15              | OUT <sub>A</sub>   | A gate drive signal – primary                                                                                                                                                                           |  |

| 16              | V <sub>CC2</sub>   | V <sub>CC2</sub> connect to V <sub>CC</sub>                                                                                                                                                             |  |

### **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 5.

### **DETAILED OPERATION**

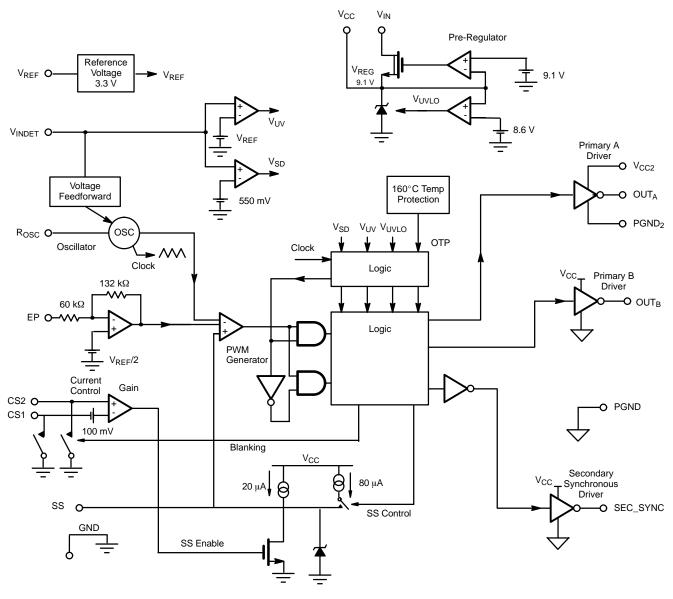

### Start-Up

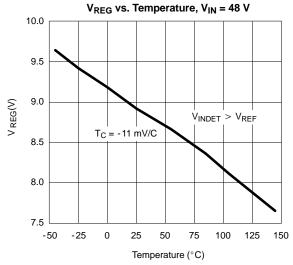

A detailed Functional Block Diagram is shown in Figure 5 with additional detail of the pre-regulator shown in Figure 6. The pre-regulator circuit acts as a linear regulator to provide  $V_{CC}$  directly from the  $V_{INEXT}$  supply until the  $V_{CC}$  supply voltage between 10 V to 13.2 V can be sustained from an auxiliary winding from the secondary of the power inductor.

When  $V_{\rm INEXT}$  rises above 0 V (see Figure 6), the internal pre-regulator begins charging the external capacitor on  $V_{\rm CC}$ . The charging current is limited to typically 40 mA by the internal DMOS device. When Vcc exceeds the UVLO voltage of 8.8 V, a soft-start cycle of the controller is initiated to provide power to the secondary. Once switching commences, the internal gate drivers for the primary side switching transistors and the drive current into the secondary synchronization driver draw additional current from the  $V_{\rm CC}$  capacitor and pre-regulator.

The pre-regulator will remain on until V $_{CC}$  equals V $_{REG}$  but between V $_{UVLO}$  and V $_{REG}$ , excessive current may result in V $_{CC}$  falling below V $_{UVLO}$  and stopping soft start operation. This situation is avoided by the hysteresis between V $_{REG}$  and V $_{UVLO}$  and correct sizing of the V $_{CC}$  capacitor, bootstrap capacitor, the soft-start capacitor, the primary MOSFET gate driving charge, and load on the SEC\_SYNC output. The value of the V $_{CC}$  capacitor should be chosen to be capable of maintaining soft start operation with V $_{CC}$  above V $_{UVLO}$  until the V $_{CC}$  current can be supplied from the external circuit (e.g. via an auxiliary winding on the secondary inductor).

Figure 6. High-Voltage Pre-Regulator Circuit

The feedback voltage from the output of the auxiliary winding must sustain  $V_{CC}$  above  $V_{REG}$  to fully disconnect the pre-regulator, isolating  $V_{CC}$  from  $V_{INEXT}$ .  $V_{CC}$  is then maintained above  $V_{REG}$  for the duration of operation. In the

event of an over voltage condition on  $V_{CC}$ , an internal voltage clamp turns on at 14.5 V to shunt excessive current to GND. In systems where operation is directly from a 12 V supply,  $V_{INEXT}$  and  $V_{CC}$  can be connected to the 12 V bus.

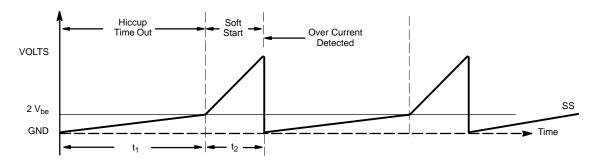

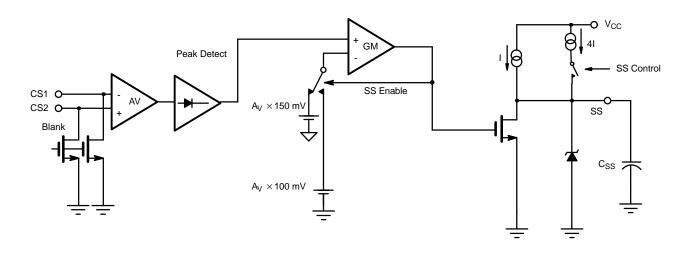

The soft-start circuit is designed for the dc-dc converter to start up in an orderly manner and reduce component stress. Soft start is achieved by ramping the maximum achievable duty cycle during the soft start time. The duty cycle is increased from zero to the final value at the rate set by the an external capacitor, C<sub>SS</sub> as shown in Figure 7. The hiccup time is set by an internal 20 µA current source charging C<sub>SS</sub> from 0 V to 2 V<sub>be</sub>, at which point switching begins. Then a 100 μA charging current is applied to CSS to charge from 2 Vbe to the final value controlling the duty cycle as it rises. In the event of UVLO, shutdown or over current, the SS pin will be held low (<1 V) disabling driver switching. A longer soft-start time may be needed for highly capacitive loads and high peak-output current applications. In the event of an over current condition being detected, the soft-start pin will be pulled low and the cycle will start again performing a hiccup as shown in Figure 4. The hiccup off-time, t<sub>1</sub>, is given by:

$$t_1 \approx C_{SS} \times \frac{1.2 \text{ V}}{20 \text{ µA}}$$

**New Product**

The soft-start time t<sub>2</sub> is can be estimated as:

$$t_2 \approx \frac{\left(C_{SS} \times V_{OUT} \times n\right)}{\left(K \times 100 \,\mu\text{A}\right)}$$

where  $V_{OUT}$  is the output of the converter, and n is the turns ratio of the primary to each secondary winding, and K is the ratio of the resistive divider from  $V_{INEXT}$  to  $V_{INDET}$  (typically 10/1).

Figure 7. Current-Sense and Soft-Start Circuit Block Diagram

### **New Product**

Care should be taken to control the operating time using the internal preregulator to prevent excessive power dissipation in the IC. The use of an external dropping resistor connected in series with the  $V_{IN}$  pin to drop the voltage during start up is recommended. The value of  $R_{EXT}$  is selected to drop the input voltage to the IC under worst case conditions thereby dissipating power in the resistor, instead of the IC. If the supply output is shorted and the auxiliary winding does not provide the  $V_{CC}$  current, then continuous soft start cycles will occur. The average power in the IC during start-up where the hiccup operation would be performed continuously is given by:

$$Power (IC) = V_{IN} \times \frac{\left[t_1 I_{CC2} + t_2 \left(I_{CC4} + I_{CC5} + I_{SEC\_SYNC}\right)\right]}{\left(t_1 + t_2\right)}$$

$$Power\left(R_{EXT}\right) = V_{ID} \times \frac{\left[t_1 \, I_{CC2} + t_2\!\!\left(I_{CC4} + I_{CC5} + I_{SEC\_SYNC}\right)\right]}{\left(t_1 + t_2\right)}$$

where

$$V_{ID} = (V_{INEXT} - V_{IN})$$

where  $I_{CC2}$  is the non-switching supply current,  $I_{CC4}$  and  $I_{CC5}$  are the supply current while switching, and  $I_{SEC\_SYNC}$  is the average current out of the SEC\_SYNC pin, and  $t_1$  and  $t_2$  are defined in Figure 4.

After the feedback voltage from the secondary overrides the internal pre-regulator, no current flows through  $R_{\text{EXT}}$ . An example of the feedback circuitry is shown in Figure 15.

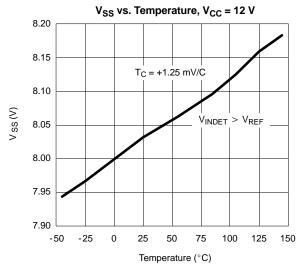

The SS pin has a predictable +1.25-mV/°C temperature coefficient and can be used to continuously monitor the junction temperature of the IC for a given power dissipation.

### Reference

The reference voltage of Si9124 is set at 3.3 V. The reference voltage should be de-coupled externally with a 0.1  $\mu F$  capacitor. The  $V_{REF}$  voltage is 0 V in shutdown mode and has 50-mA source capability.

### **Voltage Mode PWM Operation**

Under normal load conditions, the IC operates in voltage mode and generates a fixed frequency pulse-width modulated signal to the drivers. Duty cycle is controlled over a wide range to maintain the output voltage under line and load variation. Voltage feed-forward is also included to improve line regulation and transient response. In the push-pull topology requiring isolation between output and input, the reference voltage and error amplifier must be supplied externally, usually on the secondary side.

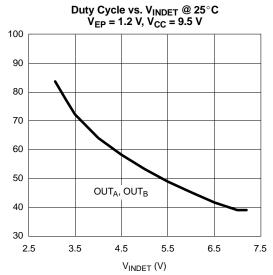

The error information is usually passed to the power controller through an opto-coupling device for isolation. The error information enters the IC via pin EP and where 0 V results in the maximum duty cycle, whilst 2 V represents minimum duty cycle. The EP error signal is gained up by -2.2X via an inverting amplifier and compared against the internal ramp

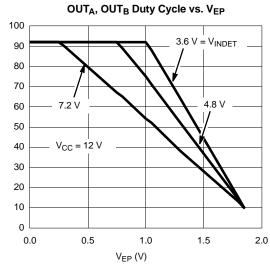

generator. The relationship between Duty Cycle and  $V_{EP}$  is shown in the Typical Characteristic section, Duty Cycle vs.  $V_{EP}$  at 25  $^{\circ}$ C, page 12.

Voltage feed-forward is implemented by taking the attenuated  $V_{\rm INEXT}$  signal at  $V_{\rm INDET}$  to directly modulate he duty cycle. This relationship is shown in the Typical Characteristic section, Duty Cycle vs.  $V_{\rm INDET}$  page 12. The response time to line transients is very short since the PWM duty cycle is charged directly without having to go through the error amplifier feedback loop. At start-up, i.e., once  $V_{CC}$  is greater than  $V_{\rm UVLO}$ , switching is initiated under soft-start control which increases maximum attainable switch on-time linearly over the soft-start period. Start-up from a  $V_{\rm INDET}$  power down, over-temperature, or over current is also initiated under soft-start control.

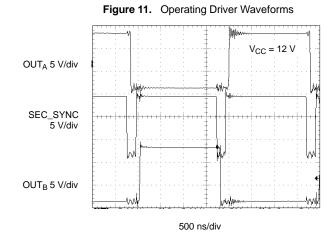

## Push-Pull and Synchronous Rectification Timing Sequence

The PWM signal generated within the IC controls the  $OUT_A$  and  $OUT_B$  drivers on alternate cycles. A period of inactivity always results after initiation of the soft-start cycle until the soft-start voltage reaches approximately 2  $V_{be}$  and PWM generated switching begins. The timing and coordination of the drives to the primary and secondary stages is very important and the relationships are shown in Figure 3. It is essential to avoid the situation where both of the secondary MOSFETs are on when either the  $OUT_A$  or  $OUT_B$  switches are active. In this situation the transformer would effectively be presented with a short across the output. To avoid this a timing signal is made available which is ahead of the primary drive outputs by 80 ns.

### **Primary MOSFET Drivers**

The drive voltage for the primary MOSFETs is provided directly from the  $V_{CC}$  and  $V_{CC2}$  supply. The switch gate drive signals  $OUT_A$  and  $OUT_B$  are shown in Figure 3. The drive currents for the primary side MOSFETs is supplied from the  $V_{CC}$  and  $V_{CC2}$  supply and can influence start up conditions.

### **Secondary Synchronization Driver**

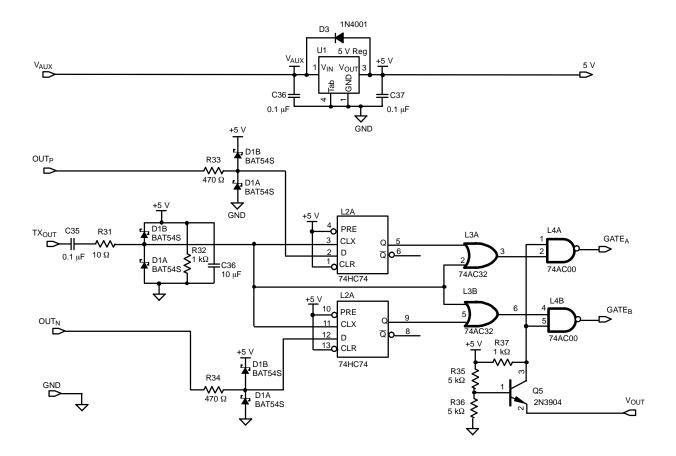

The secondary side MOSFETs are driven by the SEC\_SYNC output via a pulse transformer and gate driver circuits. The time relationships are shown in Figure 3. Logic circuitry on the secondary side is required to align the synchronous rectifier gate drive with the primary drive. The current supplied to the pulse transformer is drawn from  $\mbox{\sc V}_{\mbox{\sc CC}}$ .

#### Oscillator

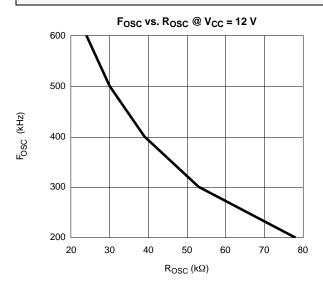

The oscillator is designed to operate at a frequencies up to 500 kHz. The 500-kHz operating frequency allows the converter to minimize the inductor and capacitor size, improving the power density of the converter. The oscillator and therefore the switching frequency is programmable by a resistor on the  $R_{OSC}$  pin. The relationship is shown in the Typical Characteristics,  $F_{OSC}$  vs.  $R_{OSC}$ .

## Vishay Siliconix

### **Hiccup Operation**

Current limiting is achieved by monitoring the differential voltage between CS1 and CS2 pins which are connected across a primary sense resistor. Once the differential voltage exceeds the 150-mV trigger point, Hiccup operation is started. The soft-start voltage on the SS pin is pulled to ground and switching stops until the SS pin charges up to 2  $V_{be}$  whereupon a duty cycle limited soft start is initiated. The upper and lower switching points of the current limit have 50 mV of hysteresis.

### **VINEXT Voltage Monitor – VINDET**

The Si9124 provides a means of sensing the voltage on  $V_{\text{INEXT}}$  to control the operating mode and provides the feed-forward control voltage to the PWM controller. This is

achieved by choosing an appropriate resistive tap between  $V_{\mbox{\scriptsize INEXT}}$  and ground.

When the  $V_{INDET}$  voltage is greater than 720 mV but less than  $V_{REF}$  and  $V_{CC}$  is greater than  $V_{UVLO}$ , all internal circuitry is enabled, but switching is stopped.

$V_{\mbox{\footnotesize{INDET}}}$  also provides the input to the voltage feed-forward function by adjusting the amplitude of the PWM ramp to the PWM comparator.

#### **Shutdown Mode**

If  $V_{INDET}$  pin is forced below 470 mV the device will enter SHUTDOWN mode. This powers down all unnecessary functions of the controller, ensures that the primary switches are off and results in a low level current demand of 150  $\mu$ A from the  $V_{INEXT}$  or  $V_{CC}$  supplies.

### **TYPICAL CHARACTERISTICS**

### **New Product**

Duty Cycle (%)

Duty Cycle %

### TYPICAL CHARACTERISTICS

IREG2 (mA)

### TYPICAL CHARACTERISTICS

**New Product**

Iccs + Iccs (mA)

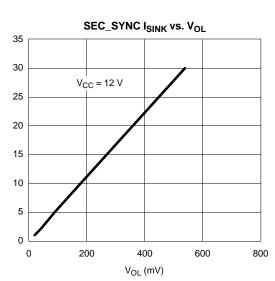

ISINK (mA)

ISINK (mA)

SOURCE (mA)

### **TYPICAL WAVEFORMS**

Figure 8. Over Current Hiccup (CS2 = 200 mV)  $OUT_{A} 20 \text{ V/div}$   $OUT_{B} 20 \text{ V/div}$  CS2 100 mV/div SS 1 V/div CSS = 22 nF  $200 \text{ } \mu\text{s/div}$

Figure 10. Pre-Regulator Start-Up

Δ 0 s @: 360μs

ViNEXT

VCC

Ch1 10.0 V 10.0 V M2.00mis Ch1 5 5.8 V

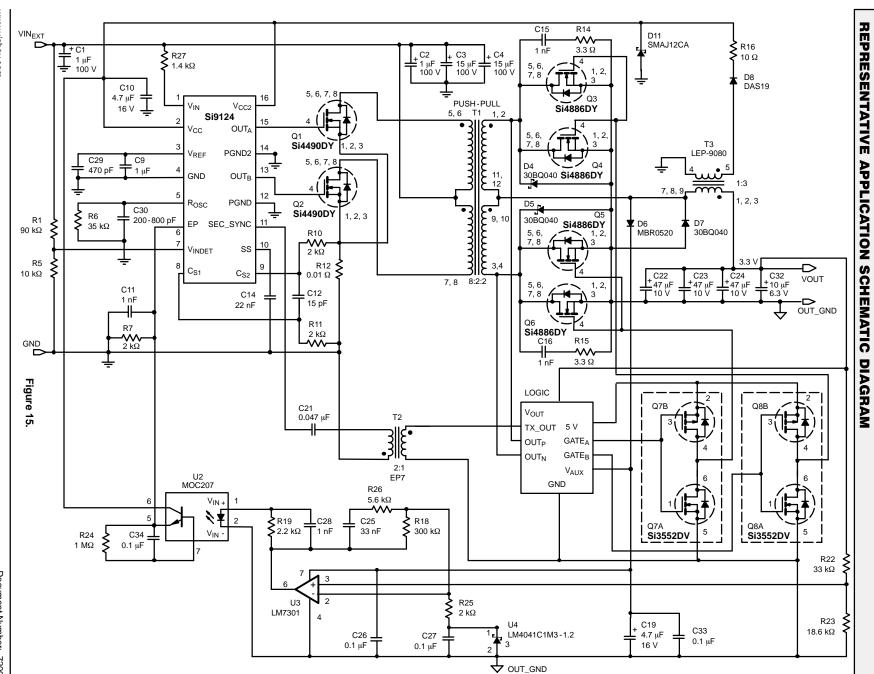

### LOGIC REPRESENTATIVE APPLICATION SCHEMATIC

Figure 14.