#### **Features**

- 10-bit Resolution

- 1.5 Gsps Sampling Rate

- Selectable 1:2 or 1:4 Demultiplexed Output

- 500 mVpp Differential 100 $\Omega$  or Single-ended 50 $\Omega$  Analog Input

- 100 $\Omega$  Differential or Single-ended 50 $\Omega$  Clock input

- LVDS Output Compatibility

- Functions:

- ADC Gain Adjust

- Sampling Delay Adjust

- 1:4 Demultiplexed Simultaneous or Staggered Digital Outputs

- Data Ready Output with Asynchronous Reset

- Out-of-range Output Bit (11th Bit)

- Power Consumption: 6.5W

- Power Supplies: -5V, -2.2V, 3.3V and V<sub>PLUSD</sub> Output Power Supply

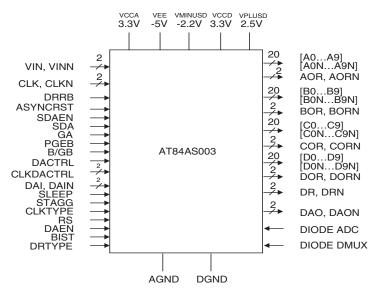

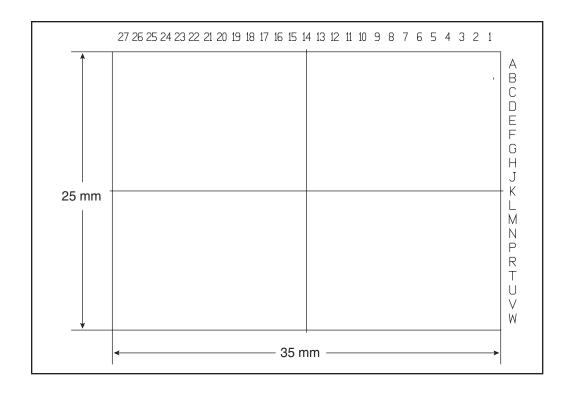

- Package

- Cavity Down EBGA 317 (Enhanced Ball Grid Array)

- 25 x 35 mm Overall Dimensions

#### **Performances**

- · 3 GHz Full-power Analog Input Bandwidth

- ±0.4 dB Gain Flatness from DC up to 1.5 GHz

- Single-tone Performance at Fs = 1.5 Gsps, Full Nyquist Zone

- ENOB = 8.0 Effective Bits, F<sub>IN</sub> = 750 MHz

- SNR = 52 dB, SFDR = -60 dBFS,  $F_{IN}$  = 750 MHz

- Dual-tone Performance (IMD3) at Fs = 1.5 Gsps (-7 dBFS each tone)

- Fin1 = 745 MHz. Fin2 = 755 MHz: IMD3 = -60 dBFS

- Fin1 = 1244 MHz, Fin2 = 1255 MHz: IMD3 = -60 dBFS

# **Screening**

- Temperature Range:

- $T_C > 0$ °C;  $T_J < 90$ °C (Commercial "C" Grade)

- T<sub>C</sub> > -20°C; T<sub>J</sub> < 110°C (Industrial "V" Grade)

# **Applications**

- Direct RF Down Conversion

- Ultra Wide Band Satellite Receivers

- Radars and Countermeasures

- · High-speed Acquisition Systems

- High Energy Physics

- Automatic Test Equipment

# **Description**

The AT84AS003 combines a 10-bit 1.5 Gsps analog-to-digital converter with a 1:4 DMUX, designed for accurate digitization of broadband signals.

It features 8.0 Effective Number of Bits (ENOB) and -60 dBFS Spurious Free Dynamic Range (SFDR) at 1.5 Gsps over the full first Nyquist zone.

10-bit 1.5 Gsps ADC With 1:4 DMUX

AT84AS003

**Summary**

5403AS-BDC-10/04

This is a summary document. A complete document is not available at this time. For more information, please contact your local Atmel sales office.

The 1:4 demultiplexed digital outputs are LVDS logic compatible, allowing easy interfacing with standard FPGAs or DSPs .The AT84AS003 operates at up to 1.5 Gsps, without additional tuning of the synchronization between the ADC and DMUX.

The AT84AS003 comes in a  $25 \times 35$  mm EBGA317 package. This package has the same TCE as FR4 boards, offering excellent reliability when subjected to large thermal variations.

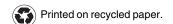

Figure 1. Block Diagram

# Functional Description

The AT84AS003 is a 10-bit 1.5 Gsps ADC combined with a high-speed demultiplexer (DMUX) used to lower the LVDS output bit stream (10-bit data and one out-of range bit) by a factor of 2 or 4.

The ADC works in fully differential mode from the analog input to the digital outputs. It provides an on-chip  $100\Omega$  differential termination for the clock input. The analog input is 500 mVpp on a  $100\Omega$  differential input impedance.  $50\Omega$  reverse terminations are required for the analog input. They should be placed as close as possible to the EBGA package input pins (2 mm maximum). The output clock and the output data are LVDS compatible ( $100\Omega$  differentially terminated).

The AT84AS003 ADC features two asynchronous resets:

- DRRB, which ensures that the first digitized data corresponds to the first acquisition

- ASYNCRST, which initializes the DMUX

The gain control pin GA is used to finely adjust the ADC gain to a unity gain.

The control pin B/GB is provided to select either a binary or gray data output format.

A Sampling Delay Adjust function (SDA, activated via the SDAEN signal) may be used to fine-tune the ADC aperture delay by approximately 120 ps around its nominal value. This function is useful when interleaving multiple ADCs.

The control pin B/GB is provided to select either a binary or Gray data output format.

A tunable delay cell (controlled via CLKDACTRL) is integrated between the ADC and the DMUX on the clock path to fine-tune the data according to the clock alignment at the interface between the ADC and the DMUX. This delay can be tuned from -250 to 250 ps around a default center value, featuring a 500 ps typical tuning range. No tuning should be necessary for operating frequencies up to 1.5 Gsps.

An extra stand-alone delay cell is also provided. It is controlled via analog DACTRL control input and activated via DAEN. The tuning range is typically 500 ps.

A pattern generator (PGEB) is integrated in the ADC block for debugging purposes or acquisition setup. Similarly, a Built-in Self Test (BIST) is provided for quick debug of the DMUX block.

The demultiplexer ratio can be selected using RS (1:2 or 1:4 ratio).

Two modes for the output clock (via DRTYPE) are selectable:

- DR mode: only the output clock's rising egde is active, the output clock rate is the same as the output data rate

- DR/2 mode: both the output clock's rising and falling edges are active, the output clock rate is half the output data rate

The AT84AS003's data is output in two different modes:

- Staggered: even and odd bits are output with half a data period delay

- Simultaneous: even and odd bits are output at the same time

A sleep mode is provided to lower the power consumption of the DMUX block.

Die junction temperature monitoring is also provided to facilitate management of the junction temperature, by sensing the voltage drop across two diodes implemented on the ADC and DMUX respectively, close to the chip's hot point.

The AT84AS003 is delivered in an Enhanced Ball Grid Array (EBGA). Its TCE, which is similar to that of the FR4 material, makes it highly suitable for applications exposed to large thermal variations.

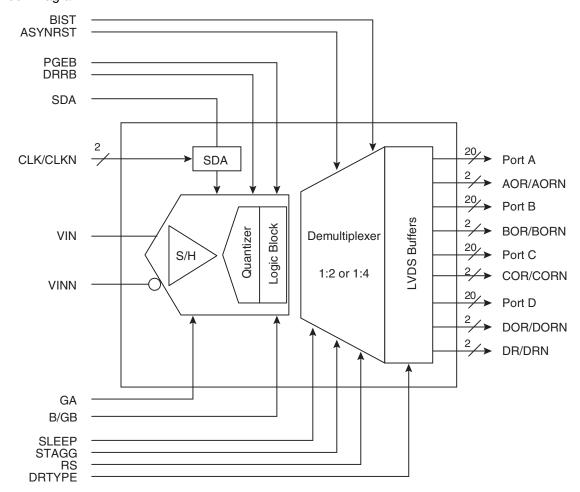

Table 1. Description of Functions

| Name                | Function                     | Name       | Function                                             |  |

|---------------------|------------------------------|------------|------------------------------------------------------|--|

| V <sub>CCA</sub>    | Analog 3.3VV power supply    | DOR, DORN  | Additional output bit port D                         |  |

| V <sub>CCD</sub>    | Digital 3.3V power supply    | RS         | DMUX ratio selection signal                          |  |

| V <sub>EE</sub>     | Analog -5V power supply      | CLKDACTRL  | Control signal for clock delay cell                  |  |

| V <sub>MINUSD</sub> | Digital -2.2V power supply   | DACTRL     | Control signal for standalone delay cell             |  |

| V <sub>PLUSD</sub>  | Output 2.5 power supply      | DAEN       | Enable signal for standalone delay cell              |  |

| AGND                | Analog ground                | DAI, DAIN  | Input signals for standalone delay cell              |  |

| DGND                | Digital ground               | DAO, DAON  | Output signals for standalone delay cell             |  |

| CLK, CLKN           | Input clock signals          | GA         | ADC gain adjust                                      |  |

| VIN, VINN           | Analog input data            | SDA        | ADC sampling delay adjust                            |  |

| DRRB                | ADC reset                    | SDAEN      | ADC SDA enable                                       |  |

| ASYNCRST            | DMUX asynchronous reset      | PGEB       | ADC pattern generator                                |  |

| DR/DRN              | Output clock signals         | B/GB       | Binary or gray output code selection                 |  |

| A0A9<br>A0NA9N      | Output data port A           | SLEEP      | Sleep mode selection signal                          |  |

| AOR, AORN           | Additional output bit port A | STAGG      | Staggered mode selection for data outputs            |  |

| B0B9<br>B0NB9N      | Output data port B           | CLKTYPE    | Input clock type selection signal                    |  |

| BOR, BORN           | Additional output bit port B | DRTYPE     | Output clock type selection signal                   |  |

| C0C9<br>C0NC9N      | Output data port C           | BIST       | Built-in self test                                   |  |

| COR, CORN           | Additional output bit port C | DIODE ADC  | Diode for die junction temperature monitoring (ADC)  |  |

| D0D9<br>D0ND9N      | Output data port D           | DIODE DMUX | Diode for die junction temperature monitoring (DMUX) |  |

Figure 2. Device Pinout

# **Package Information**

Figure 3. EBGA 317 Package Outline (Bottom View)

# **Ordering Information**

| Part Number    | Package  | Temperature Range                                                | Screening | Comments                                                             |

|----------------|----------|------------------------------------------------------------------|-----------|----------------------------------------------------------------------|

| AT84XAS003TP   | EBGA 317 | Ambient                                                          | Prototype | Prototype version<br>Please contact your<br>local Atmel sales office |

| AT84AS003CTP   | EBGA 317 | Commercial "C"<br>T <sub>C</sub> > 0°C; T <sub>J</sub> < 90°C    | Standard  |                                                                      |

| AT84AS003VTP   | EBGA 317 | Industrial "V"<br>T <sub>C</sub> > -20°C; T <sub>J</sub> < 110°C | Standard  |                                                                      |

| AT84AS003TP-EB | EBGA 317 | Ambient                                                          | Prototype | Evaluation kit                                                       |

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

# ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Chevenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

@ Atmel Corporation 2004. All rights reserved. Atmel® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.