**User's Manual**

# NEC

# V850E/IA2

# **32-Bit Single-Chip Microcontrollers**

Hardware

μPD703114 μPD703114(A) μPD70F3114 μPD70F3114(A)

Document No. U15195EJ5V0UD00 (5th edition) Date Published August 2005 N CP(K)

© NEC Electronics Corporation 2001 Printed in Japan [MEMO]

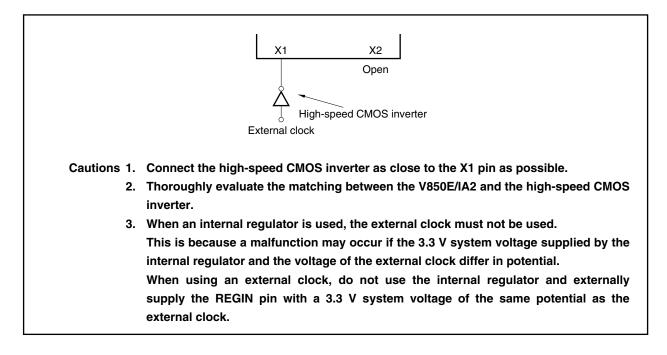

# **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

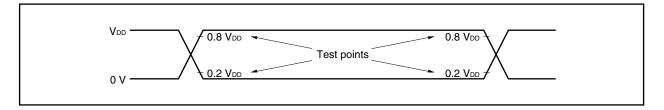

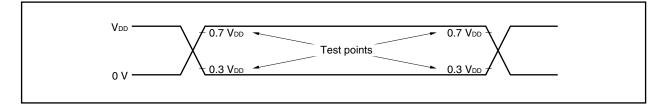

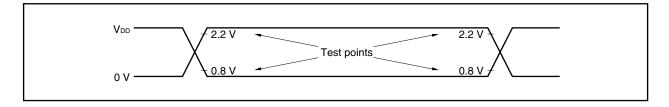

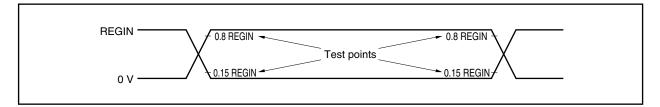

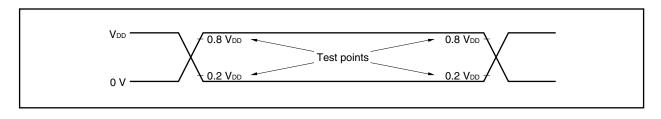

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

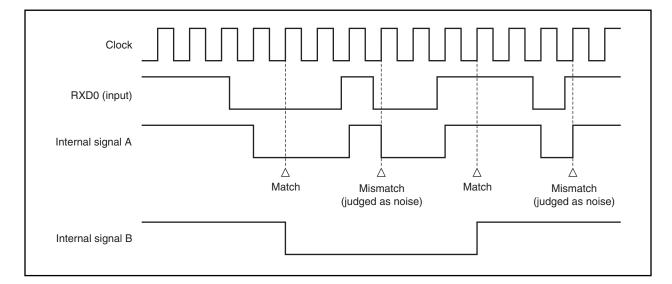

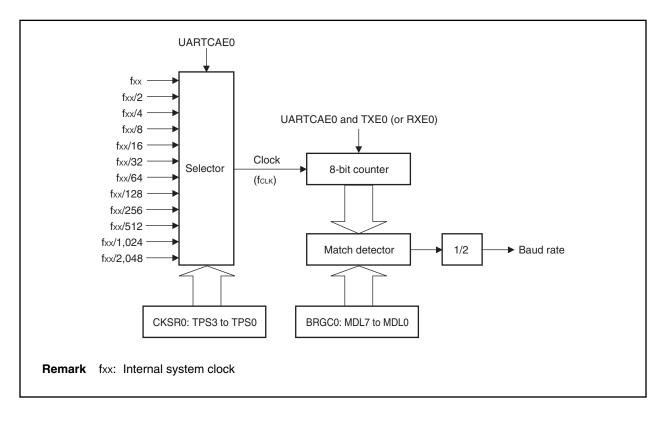

# (2) HANDLING OF UNUSED INPUT PINS

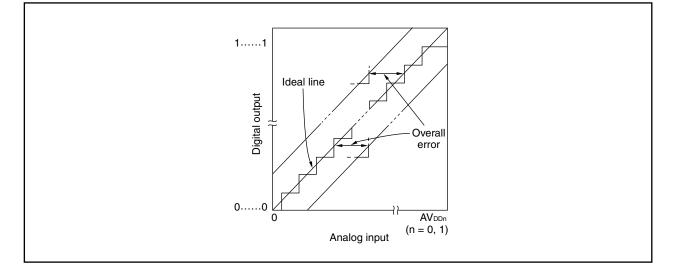

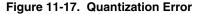

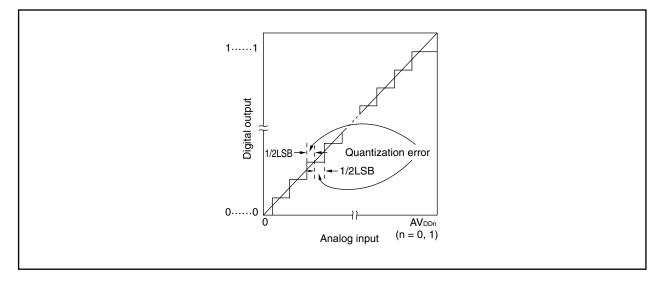

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

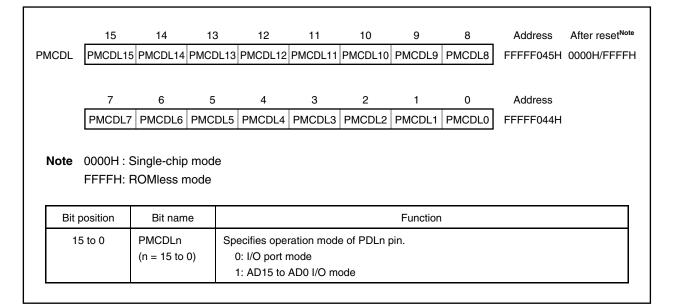

# **③** PRECAUTION AGAINST ESD

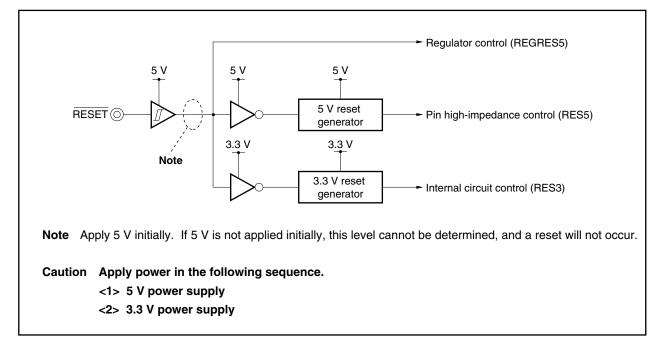

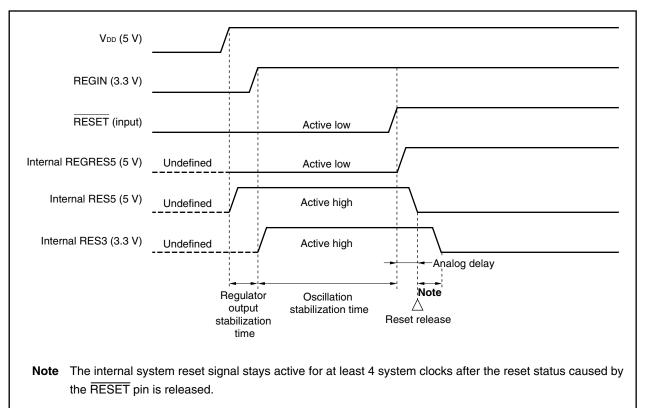

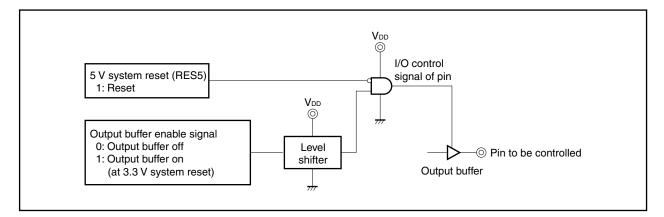

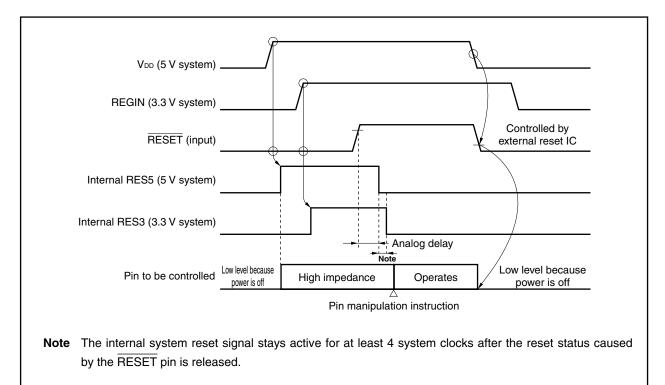

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **(6)** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of March, 2005. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

# [GLOBAL SUPPORT] http://www.necel.com/en/support/support.html

| NEC Electronics America, Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782 | <b>NEC Electronics (Europe) GmbH</b><br>Duesseldorf, Germany<br>Tel: 0211-65030 | <b>NEC Electronics Hong Kong Ltd.</b><br>Hong Kong<br>Tel: 2886-9318 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                      | <ul> <li>Sucursal en España</li> </ul>                                          | NEC Electronics Hong Kong Ltd.                                       |

|                                                                                                      | Madrid, Spain                                                                   | Seoul Branch                                                         |

|                                                                                                      | Tel: 091-504 27 87                                                              | Seoul, Korea                                                         |

|                                                                                                      |                                                                                 | Tel: 02-558-3737                                                     |

|                                                                                                      | <ul> <li>Succursale Française</li> </ul>                                        |                                                                      |

|                                                                                                      | Vélizy-Villacoublay, France                                                     | NEC Electronics Shanghai Ltd.                                        |

|                                                                                                      | Tel: 01-30-67 58 00                                                             | Shanghai, P.R. China                                                 |

|                                                                                                      | <ul> <li>Filiale Italiana</li> </ul>                                            | Tel: 021-5888-5400                                                   |

|                                                                                                      |                                                                                 |                                                                      |

|                                                                                                      | Milano, Italy                                                                   | NEC Electronics Taiwan Ltd.                                          |

|                                                                                                      | Tel: 02-66 75 41                                                                | Taipei, Taiwan                                                       |

|                                                                                                      |                                                                                 | Tel: 02-2719-2377                                                    |

|                                                                                                      | <ul> <li>Branch The Netherlands</li> </ul>                                      |                                                                      |

|                                                                                                      | Eindhoven, The Netherlands                                                      | NEC Electropies Singapore Bto 1 td                                   |

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 6253-8311

• United Kingdom Branch Milton Keynes, UK Tel: 01908-691-133

Tel: 040-2654010

• Tyskland Filial Taeby, Sweden Tel: 08-63 87 200

J05.6

# PREFACE

| Readers                 | This manual is intended for users who wish to understand the functions of the V850E/IA2 and design application systems using it. The target products are as follows.                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | <ul> <li>Standard products: μPD703114, 70F3114</li> <li>Special grade products: μPD703114(A), 70F3114(A)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Purpose                 | This manual is intended to give users an understanding of the hardware functions of the V850E/IA2 shown in the <b>Organization</b> below.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Organization            | This manual is divided into two parts: Hardware (this manual) and Architecture (V850E1 Architecture User's Manual).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | HardwareArchitecture• Pin functions• Data type• CPU function• Register set• On-chip peripheral functions• Instruction format and instruction set• Flash memory programming• Interrupts and exceptions• Electrical specifications• Pipeline operation                                                                                                                                                                                                                                                                                                |

| How to Read This Manual | It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | <ul> <li>Cautions 1. The application examples in this manual apply to "standard" quality grade products for general electronic systems. When using an example in this manual for an application that requires a "special" quality grade product, thoroughly evaluate the component and circuit to be actually used to see if they satisfy the special quality grade.</li> <li>2. When using this manual as a manual for a special grade product, read the part numbers as follows.<br/>µPD703114 → 703114(A)<br/>µPD70F3114 → 70F3114(A)</li> </ul> |

|                         | <ul> <li>To find the details of a register where the name is known</li> <li>→ Refer to APPENDIX B REGISTER INDEX.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | <ul> <li>To understand the details of an instruction function</li> <li>→ Refer to the V850E1 Architecture User's Manual.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | <ul> <li>To know details of the electrical specifications of the V850E/IA2</li> <li>→ Refer to CHAPTER 16 ELECTRICAL SPECIFICATIONS.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | <ul> <li>To understand the overall f</li> <li>→ Read this manual accord</li> </ul>                                                                         |                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|             | reserved word in the dev                                                                                                                                   | ose number is in angle brackets (<>) is defined as a vice file.<br>nat of each register describes 0 or 1, other values are         |

|             | The mark $\star$ shows major re                                                                                                                            | vised points.                                                                                                                      |

| Conventions | Data significance:<br>Active low representation:<br>Memory map address:<br><b>Note</b> :<br><b>Caution</b> :<br><b>Remark</b> :<br>Numeric representation: | Higher digits on the left and lower digits on the right                                                                            |

|             | Prefix indicating power of 2 (                                                                                                                             | address space, memory capacity):<br>K (kilo): $2^{10} = 1,024$<br>M (mega): $2^{20} = 1,024^{2}$<br>G (giga): $2^{30} = 1,024^{3}$ |

|             | Data type:                                                                                                                                                 | Word 32 bits<br>Halfword 16 bits<br>Byte 8 bits                                                                                    |

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Documents related to V850E/IA2

| Document Name                                                                                               | Document No. |

|-------------------------------------------------------------------------------------------------------------|--------------|

| V850E1 Architecture User's Manual                                                                           | U14559E      |

| V850E/IA2 Hardware User's Manual                                                                            | This manual  |

| V850E/IA1, V850E/IA2 AC Motor Inverter Control Using Vector<br>Operation Application Note                   | U14868E      |

| Inverter Control by V850 Series 120° Excitation Method Control by Zero-<br>Cross Detection Application Note | U17209E      |

| Inverter Control by V850 Series Vector Control by Encoder Application<br>Note                               | U17324E      |

| Inverter Control by V850 Series Vector Control by Hole Sensor<br>Application Note                           | U17338E      |

# Documents related to development tools (user's manuals)

| Document Name                                  | Document No.                                       |         |

|------------------------------------------------|----------------------------------------------------|---------|

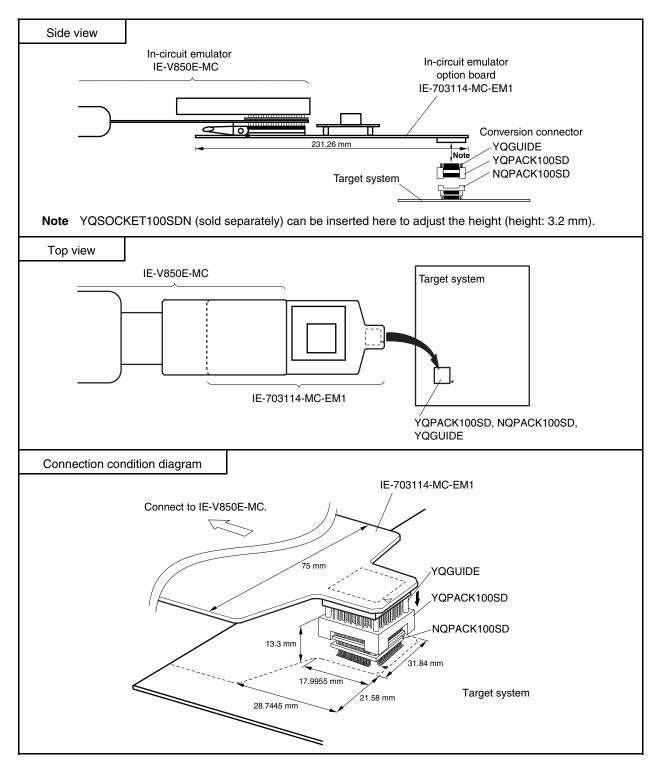

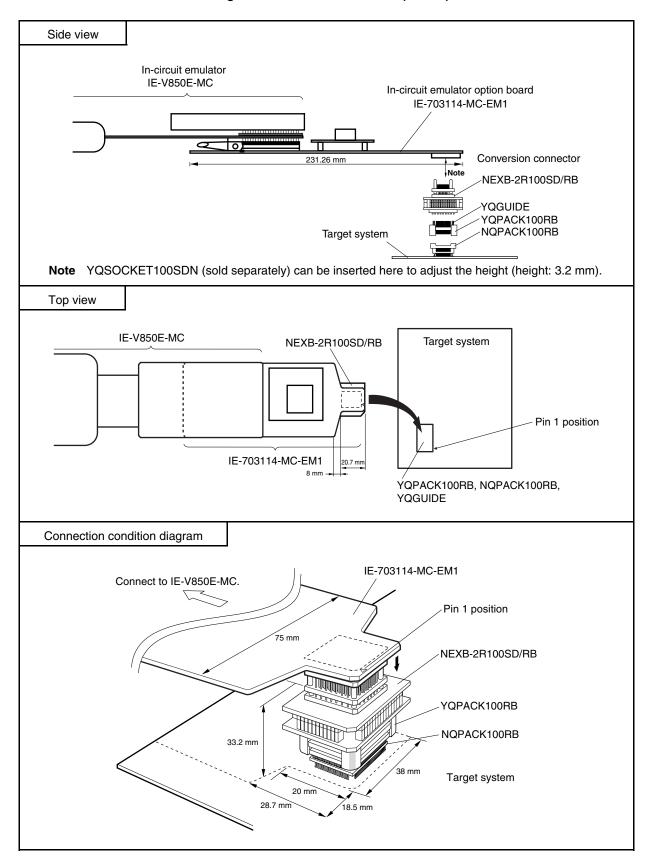

| IE-V850E-MC, IE-V850E-MC-A (In-circuit em      | U14487E                                            |         |

| IE-703114-MC-EM1 (In-circuit emulator optio    | n board)                                           | U16533E |

| CA850 (Ver. 3.00) (C compiler package)         | Operation                                          | U17293E |

|                                                | C Language                                         | U17291E |

|                                                | Assembly Language                                  | U17292E |

|                                                | Link Directives                                    | U17294E |

| PM+ (Ver. 6.00) (Project manager)              |                                                    | U17178E |

| ID850 (Ver. 3.00) (Integrated debugger)        | Operation                                          | U17358E |

| TW850 (Ver. 2.00) (Performance analysis tur    | ing tool)                                          | U17241E |

| SM850 (Ver. 2.50) (System simulator) Operation |                                                    | U16218E |

| SM850 (Ver. 2.00 or later) (System simulator)  | External Part User Open<br>Interface Specification | U14873E |

| SM+ (System simulator)                         | Operation                                          | U17246E |

|                                                | User Open Interface                                | U17247E |

| RX850 (Ver. 3.13 or later) (Real-time OS)      | Basics                                             | U13430E |

|                                                | Installation                                       | U13410E |

|                                                | Technical                                          | U13431E |

| RX850 Pro (Ver. 3.15) (Real-time OS)           | Basics                                             | U13773E |

|                                                | Installation                                       | U13774E |

|                                                | Technical                                          | U13772E |

| RD850 (Ver. 3.01) (Task debugger)              | U13737E                                            |         |

| RD850 Pro (Ver. 3.01) (Task debugger)          | U13916E                                            |         |

| AZ850 (Ver. 3.10) (System performance anal     | U14410E                                            |         |

| PG-FP4 Flash memory programmer                 |                                                    | U15260E |

# CONTENTS

| СНАРТЕ | R 1 INTRODUCTION                                                                                        | 17 |

|--------|---------------------------------------------------------------------------------------------------------|----|

| 1.1    | Outline                                                                                                 |    |

| 1.2    | Features                                                                                                |    |

| 1.3    | Applications                                                                                            | 21 |

| 1.4    | Ordering Information                                                                                    | 21 |

| 1.5    | Pin Configuration (Top View)                                                                            | 22 |

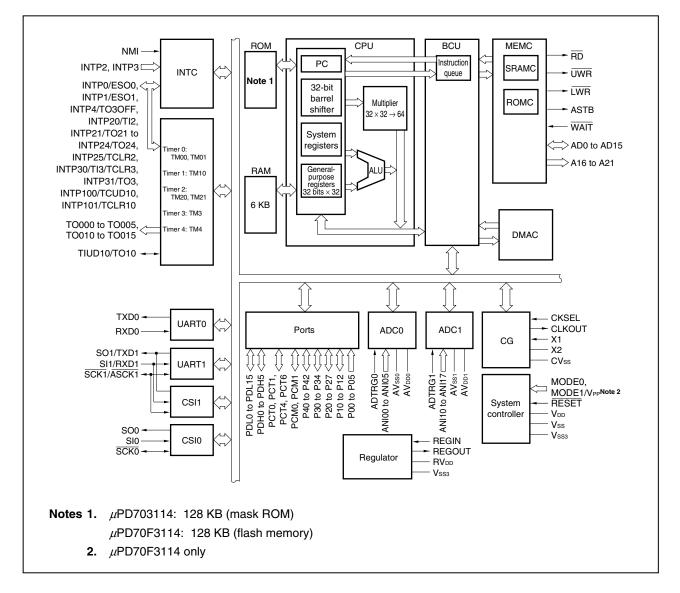

| 1.6    | Configuration of Function Block                                                                         | 25 |

|        | 1.6.1 Internal block diagram                                                                            | 25 |

|        | 1.6.2 Internal units                                                                                    | 26 |

| СНАРТЕ | R 2 PIN FUNCTIONS                                                                                       | 28 |

| 2.1    | List of Pin Functions                                                                                   | 28 |

| 2.2    | Pin Status                                                                                              | 33 |

| 2.3    | Description of Pin Functions                                                                            | 34 |

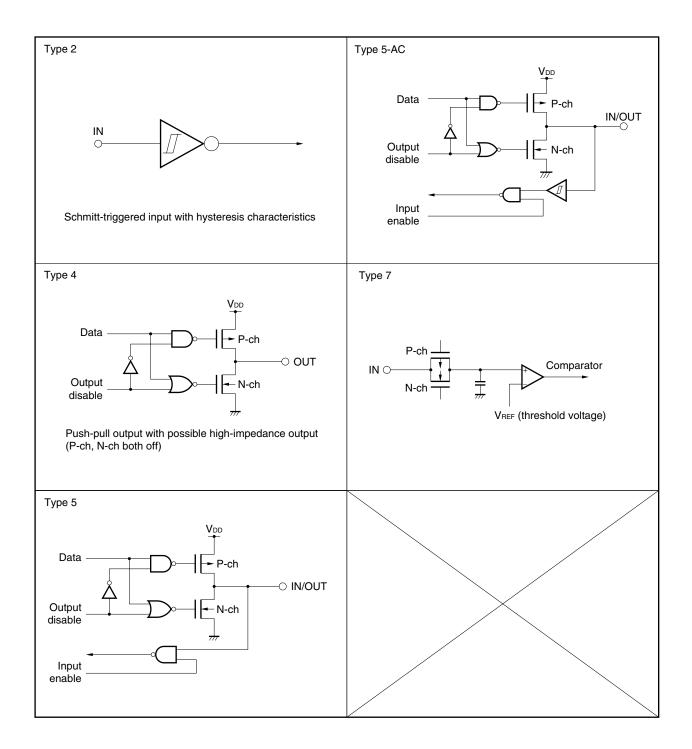

| 2.4    | Types of Pin I/O Circuits and Connection of Unused Pins                                                 | 43 |

| 2.5    | Pin I/O Circuits                                                                                        | 45 |

|        |                                                                                                         | 40 |

|        | R 3 CPU FUNCTION                                                                                        |    |

| 3.1    | Features                                                                                                |    |

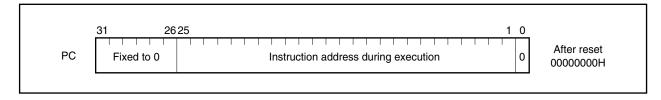

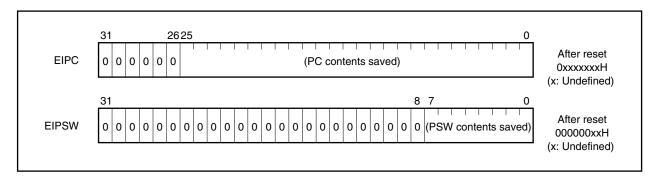

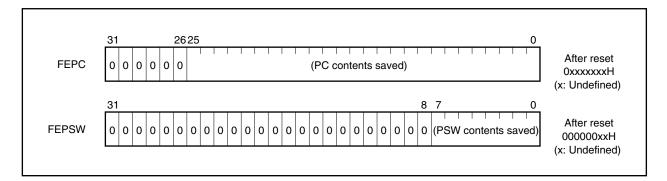

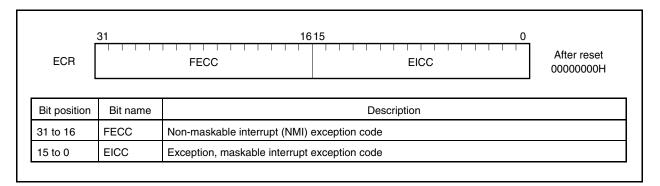

| 3.2    | CPU Register Set                                                                                        |    |

|        | 3.2.1 Program register set                                                                              |    |

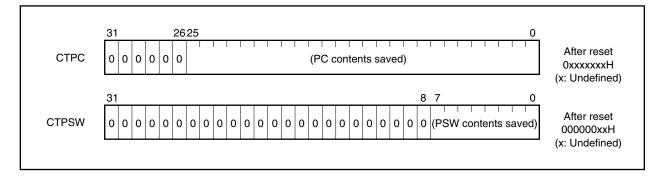

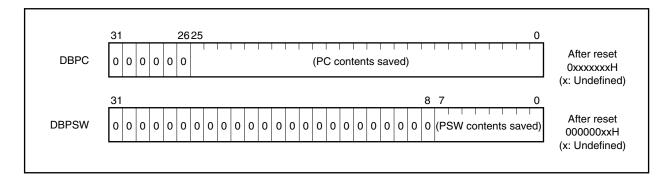

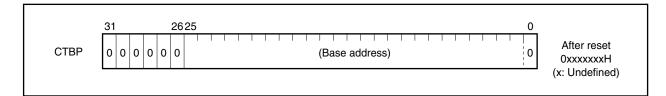

|        | 3.2.2 System register set                                                                               |    |

| 3.3    | Operation Modes                                                                                         |    |

|        | 3.3.1 Operation modes                                                                                   |    |

|        | 3.3.2 Operation mode specification                                                                      |    |

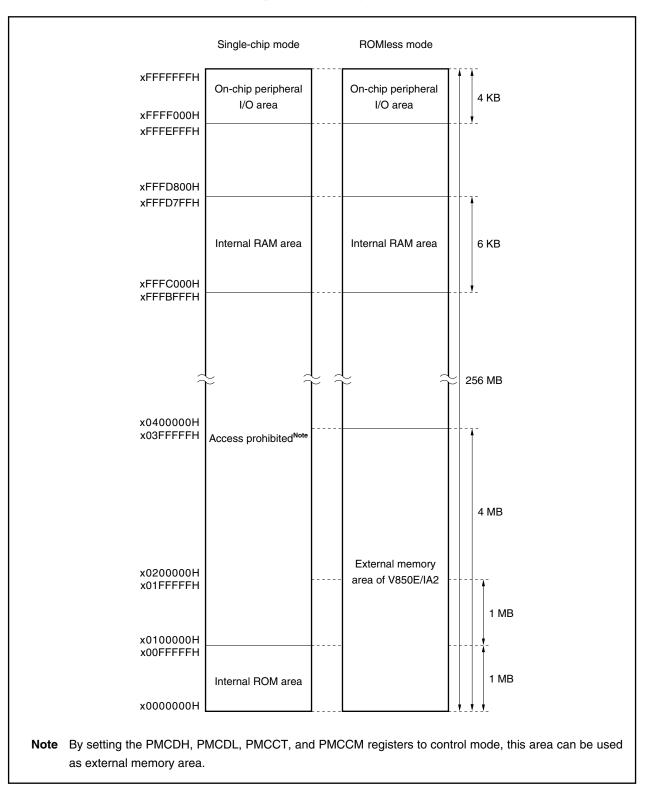

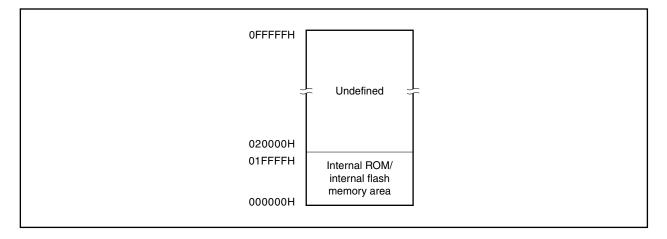

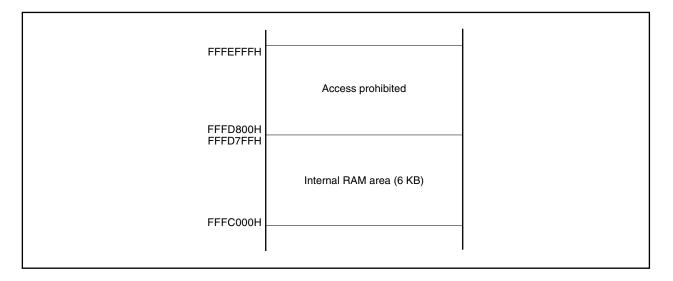

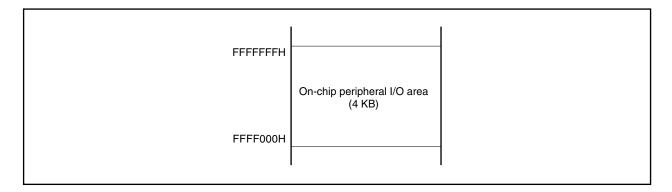

| 3.4    | Address Space                                                                                           |    |

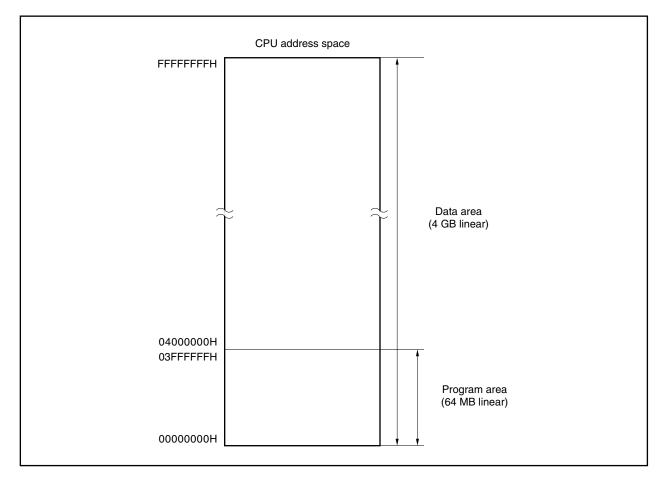

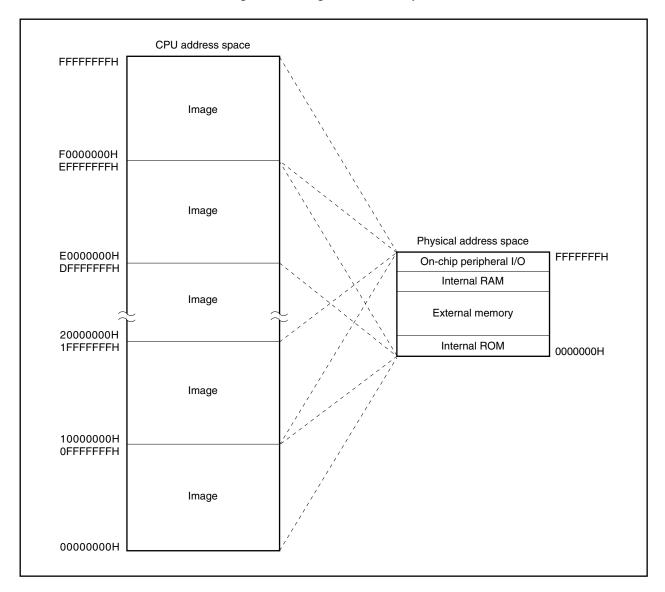

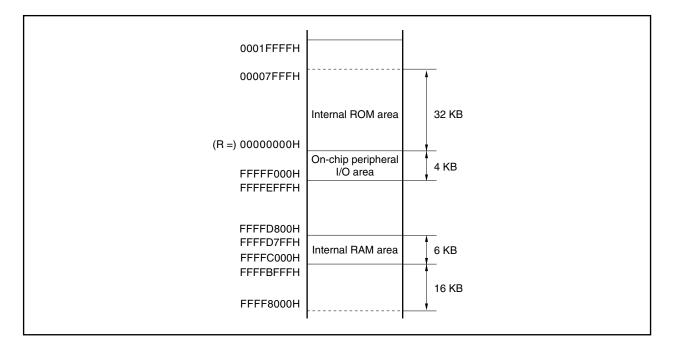

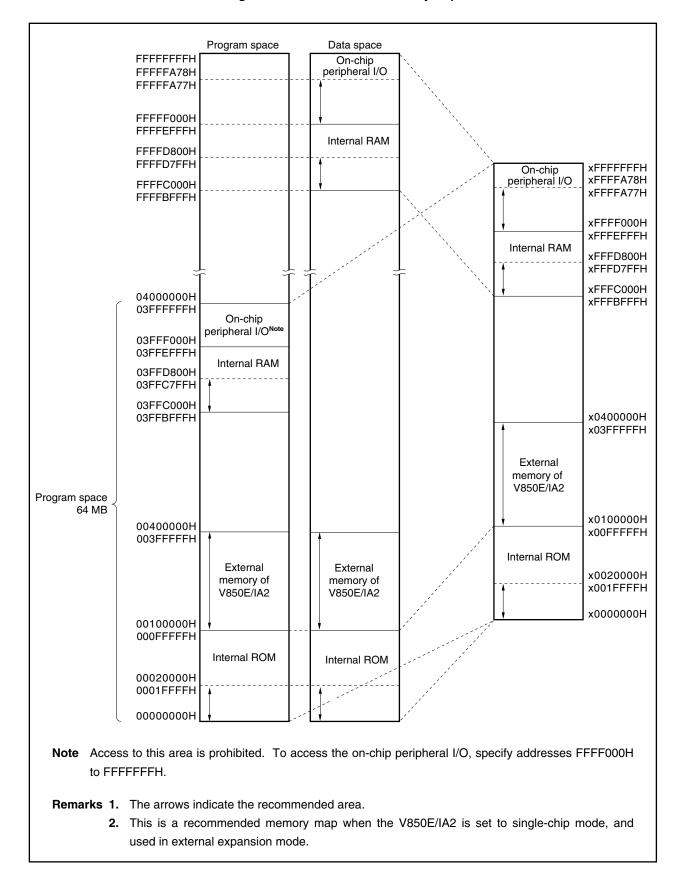

|        | 3.4.1 CPU address space                                                                                 |    |

|        | 3.4.2 Image                                                                                             |    |

|        | 3.4.3 Wrap-around of CPU address space                                                                  |    |

|        | 3.4.4 Memory map                                                                                        |    |

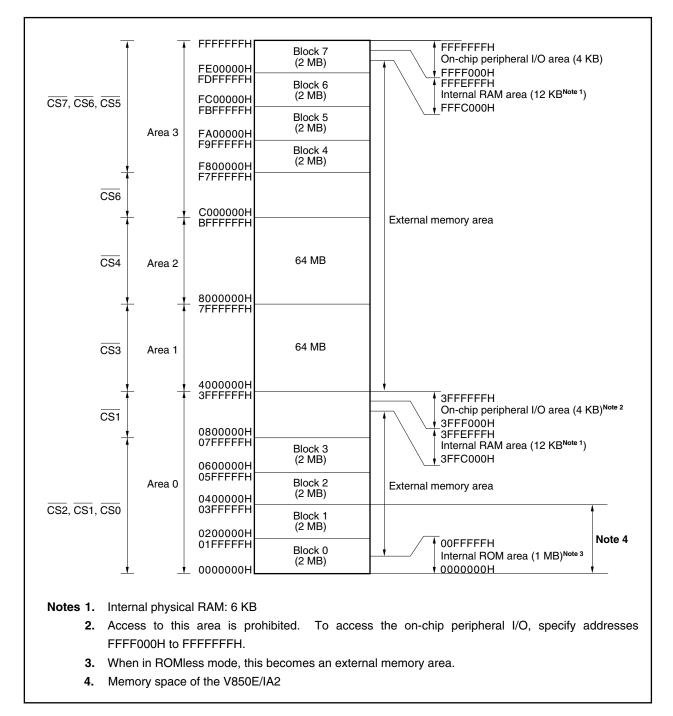

|        | 3.4.5 Area                                                                                              | •  |

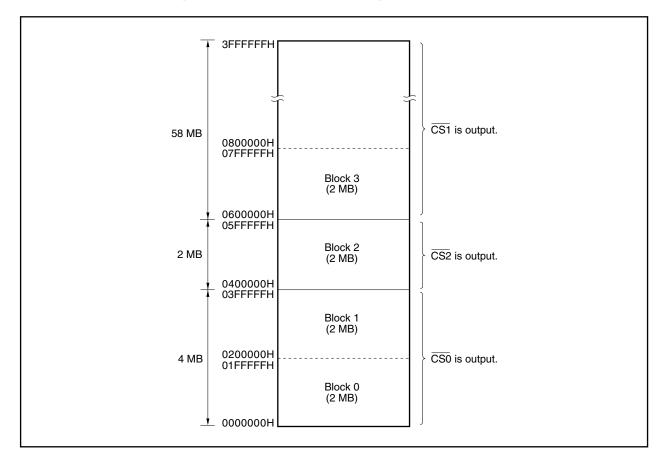

|        | 3.4.6 External memory expansion                                                                         |    |

|        | <ul><li>3.4.7 Recommended use of address space</li><li>3.4.8 On-chip peripheral I/O registers</li></ul> |    |

|        | 3.4.8 On-cnip peripheral i/O registers                                                                  |    |

|        | 3.4.9 Specific registers                                                                                |    |

|        | 3.4.11 Cautions                                                                                         |    |

|        |                                                                                                         |    |

| CHAPTE | R 4 BUS CONTROL FUNCTION                                                                                | 80 |

| 4.1    | Features                                                                                                | 80 |

| 4.2    | Bus Control Pins                                                                                        | 80 |

|        | 4.2.1 Pin status during internal ROM, internal RAM, and on-chip peripheral I/O access                   | 80 |

| 4.3    | Memory Block Function                                                                                   | 81 |

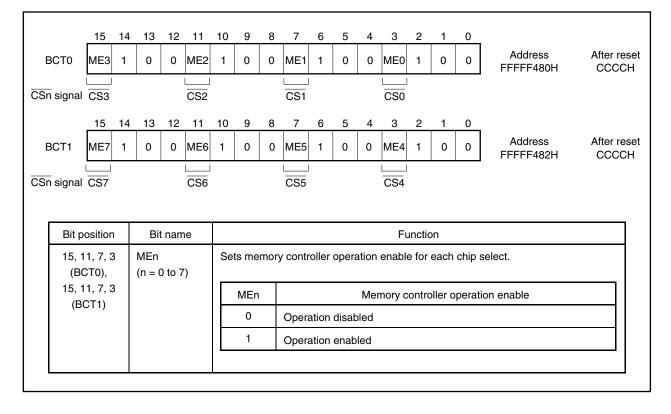

|              | 4.3.1  | Chip select control function                                 |     |

|--------------|--------|--------------------------------------------------------------|-----|

| 4.4          | Bus C  | Cycle Type Control Function                                  |     |

| 4.5          | Bus A  | Access                                                       |     |

|              | 4.5.1  | Number of access clocks                                      |     |

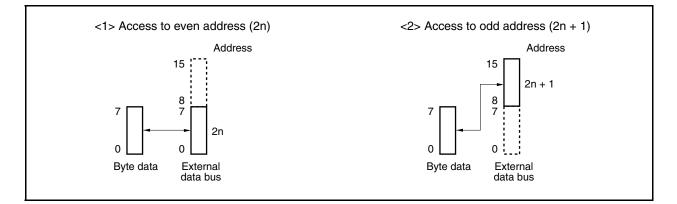

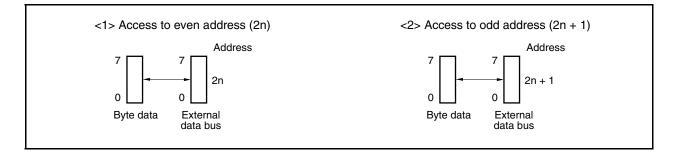

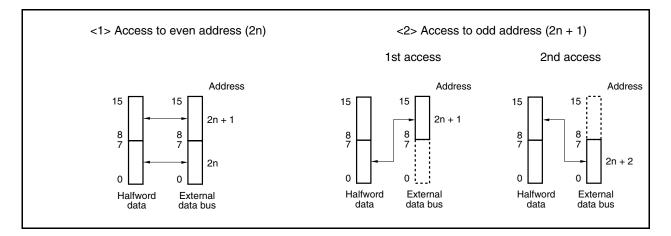

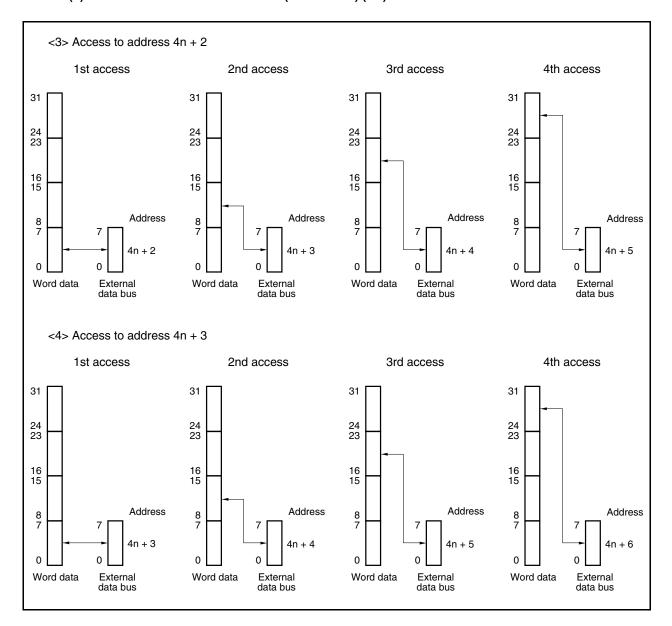

|              | 4.5.2  | Bus sizing function                                          |     |

|              | 4.5.3  | Bus width                                                    |     |

| 4.6          | Wait F | Function                                                     |     |

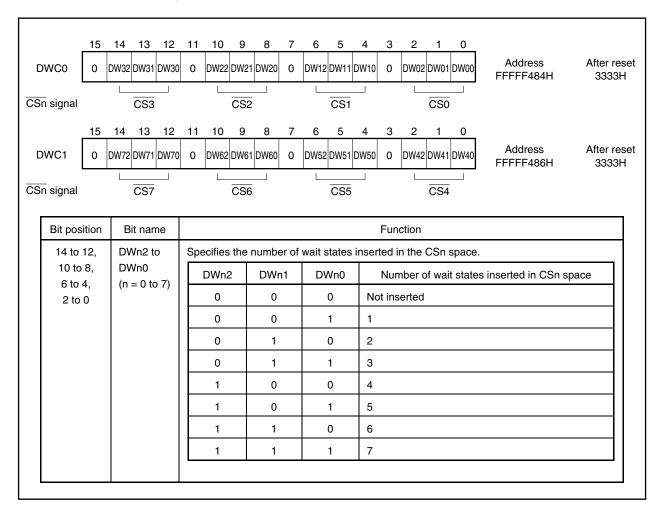

|              | 4.6.1  | Programmable wait function                                   |     |

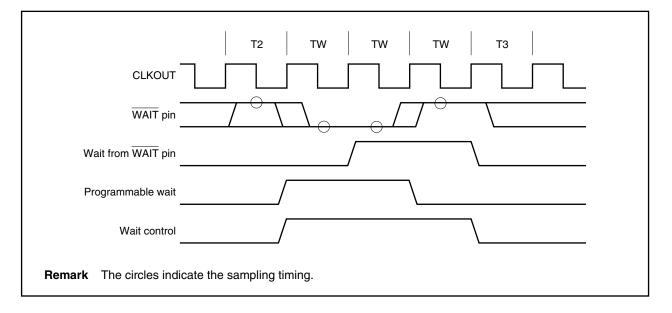

|              | 4.6.2  | External wait function                                       |     |

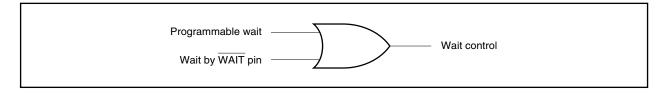

|              | 4.6.3  | Relationship between programmable wait and external wait     |     |

| 4.7          | Idle S | tate Insertion Function                                      |     |

| 4.8          | Bus P  | Priority Order                                               |     |

| 4.9          | Boun   | dary Operation Conditions                                    |     |

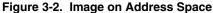

|              | 4.9.1  | Program space                                                |     |

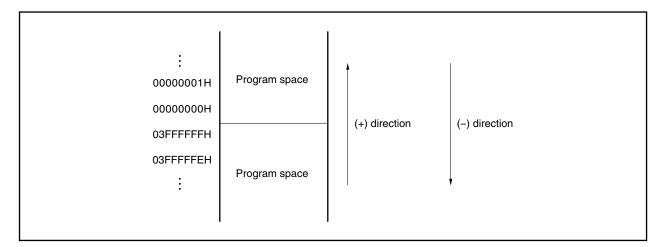

|              | 4.9.2  | Data space                                                   |     |

|              |        |                                                              |     |

| CHAPTE       | R 5 N  | IEMORY ACCESS CONTROL FUNCTION                               | 100 |

| 5.1          | SRAM   | I, External ROM, External I/O Interface                      | 100 |

|              | 5.1.1  | Features                                                     | 100 |

|              | 5.1.2  | SRAM, external ROM, external I/O access                      | 101 |

|              |        |                                                              |     |

| CHAPTE       | R 6 D  | OMA FUNCTIONS (DMA CONTROLLER)                               | 105 |

| 6.1          | Featu  | res                                                          | 105 |

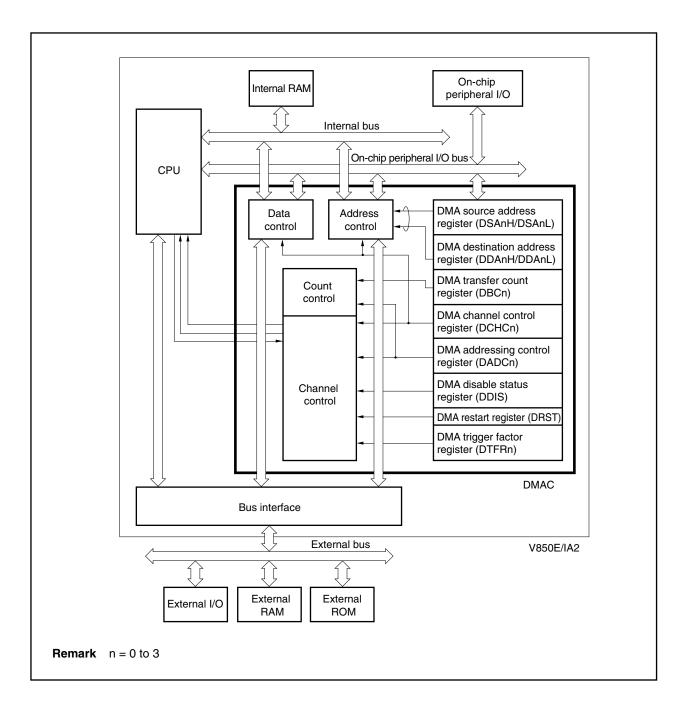

| 6.2          | Config | guration                                                     |     |

| 6.3          | Contr  | ol Registers                                                 | 107 |

|              | 6.3.1  | DMA source address registers 0 to 3 (DSA0 to DSA3)           | 107 |

|              | 6.3.2  | DMA destination address registers 0 to 3 (DDA0 to DDA3)      | 109 |

|              | 6.3.3  | DMA transfer count registers 0 to 3 (DBC0 to DBC3)           | 111 |

|              | 6.3.4  | DMA addressing control registers 0 to 3 (DADC0 to DADC3)     | 112 |

|              | 6.3.5  | DMA channel control registers 0 to 3 (DCHC0 to DCHC3)        | 114 |

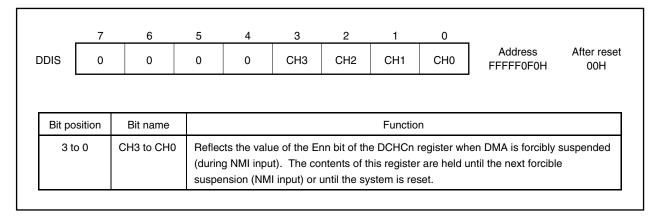

|              | 6.3.6  | DMA disable status register (DDIS)                           | 116 |

|              | 6.3.7  | DMA restart register (DRST)                                  | 116 |

|              | 6.3.8  | DMA trigger factor registers 0 to 3 (DTFR0 to DTFR3)         |     |

| 6.4          | Trans  | fer Modes                                                    |     |

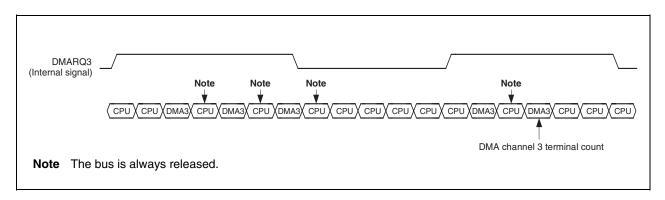

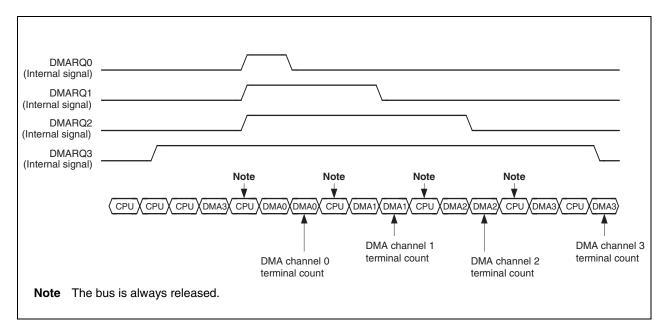

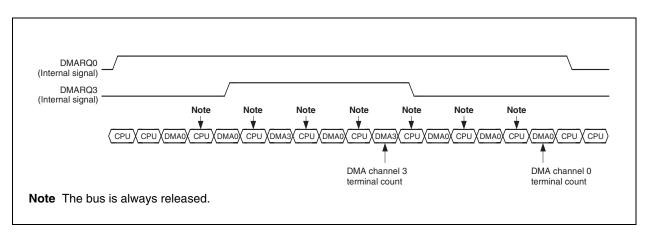

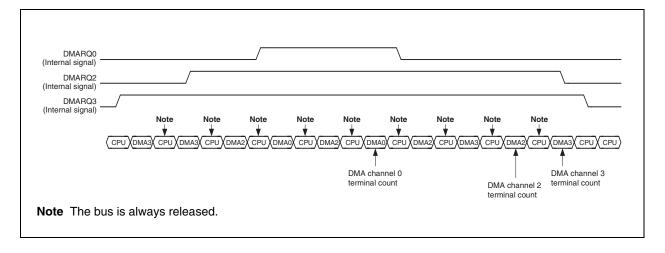

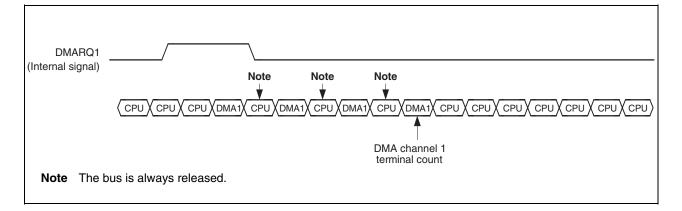

|              | 6.4.1  | Single transfer mode                                         | 120 |

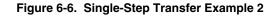

|              | 6.4.2  | Single-step transfer mode                                    |     |

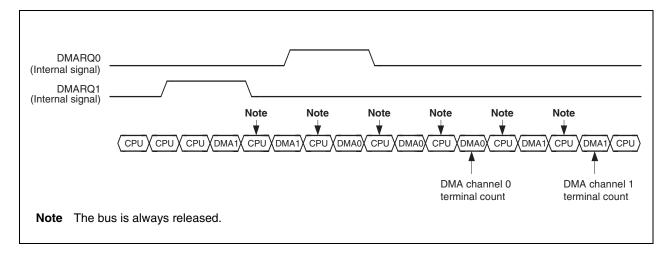

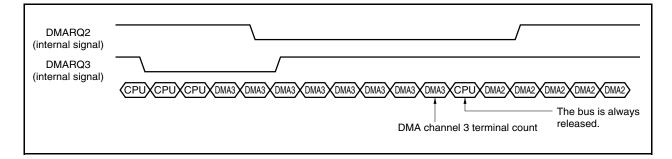

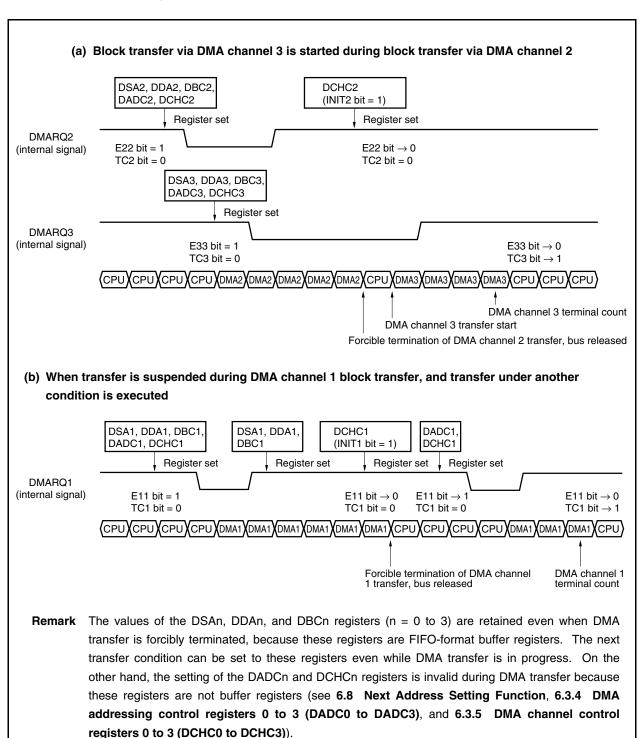

|              | 6.4.3  | Block transfer mode                                          |     |

| 6.5          |        | fer Types                                                    |     |

|              | 6.5.1  | Two-cycle transfer                                           |     |

| 6.6          |        | fer Target                                                   |     |

|              | 6.6.1  | Transfer type and transfer target                            |     |

| ~ 7          | 6.6.2  | External bus cycles during DMA transfer (two-cycle transfer) |     |

| 6.7          |        | Channel Priorities                                           |     |

| 6.8          |        | Address Setting Function                                     |     |

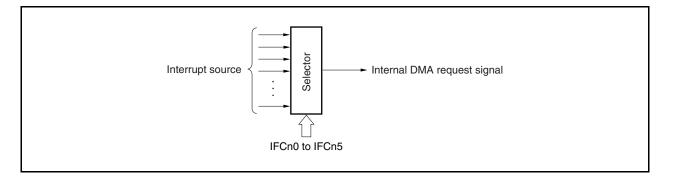

| 6.9<br>6 10  |        | Transfer Start Factors                                       |     |

| 6.10<br>6.11 |        | ble Suspension<br>Transfer End                               |     |

| 0.11         |        | 110113151 EIIU                                               |     |

| 6.12   | Forcible Termination                                        | 129 |

|--------|-------------------------------------------------------------|-----|

|        | 6.12.1 Restrictions on forcible termination of DMA transfer | 130 |

| 6.13   | Time Required for DMA Transfer                              | 131 |

| 6.14   | Cautions                                                    | 132 |

|        |                                                             |     |

| CHAPTE | ER 7 INTERRUPT/EXCEPTION PROCESSING FUNCTION                | 134 |

| 7.1    | Features                                                    | 134 |

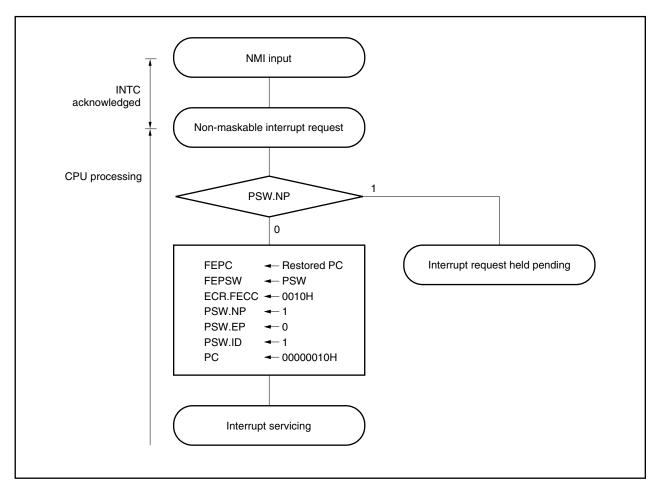

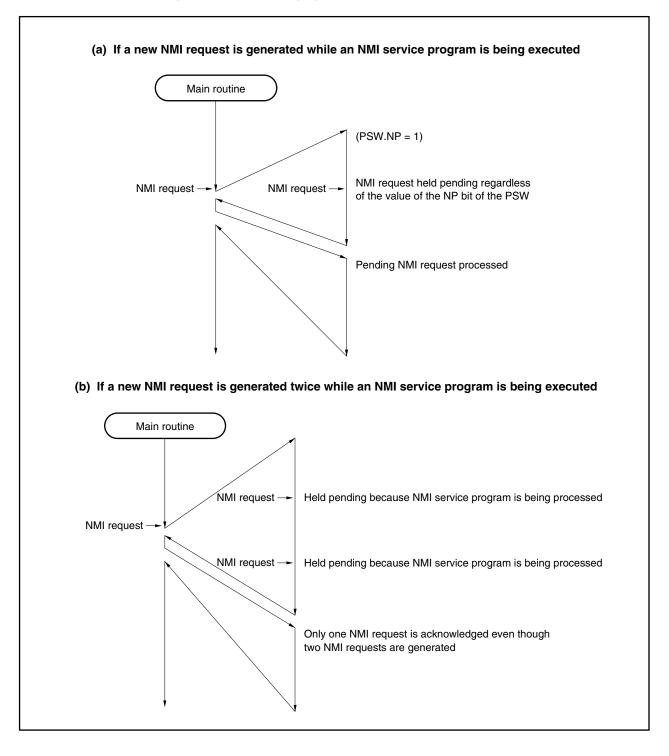

| 7.2    | Non-Maskable Interrupt                                      | 138 |

|        | 7.2.1 Operation                                             |     |

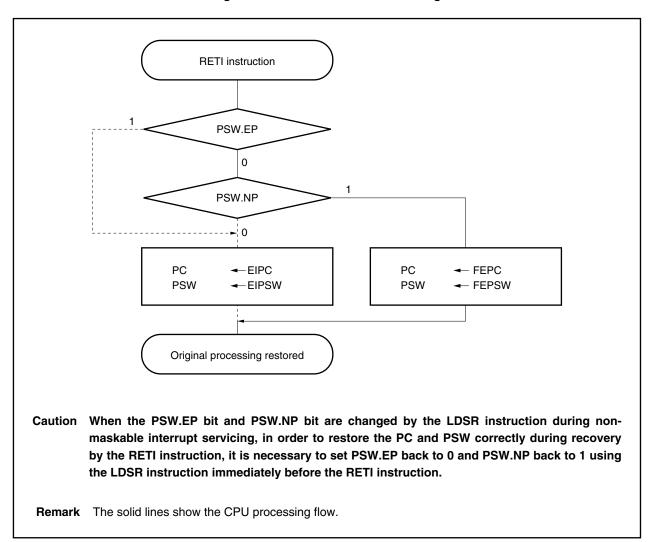

|        | 7.2.2 Restore                                               | 141 |

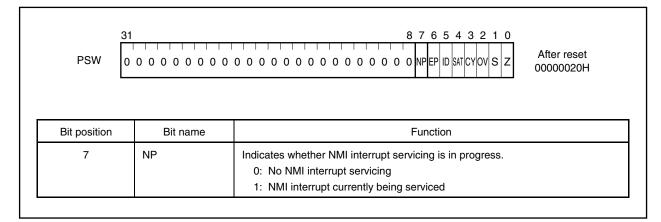

|        | 7.2.3 Non-maskable interrupt status flag (NP)               | 142 |

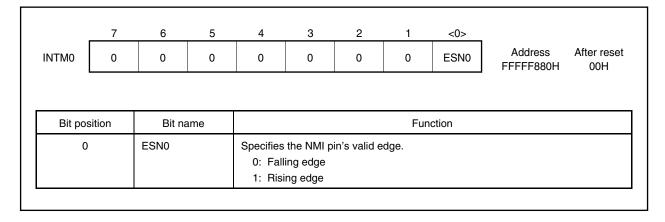

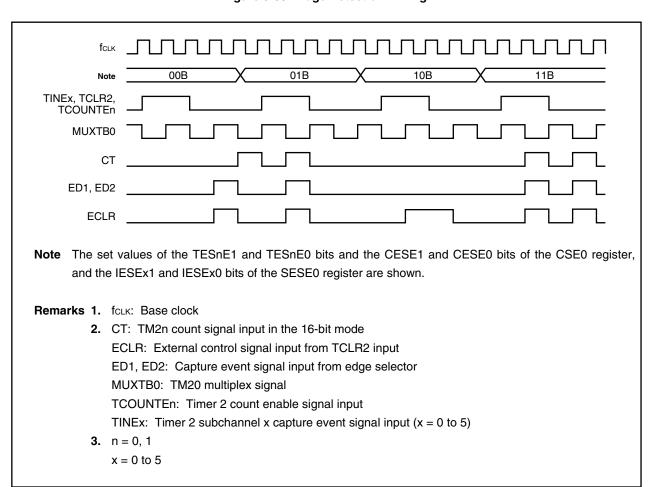

|        | 7.2.4 Edge detection function                               | 142 |

| 7.3    | Maskable Interrupts                                         | 143 |

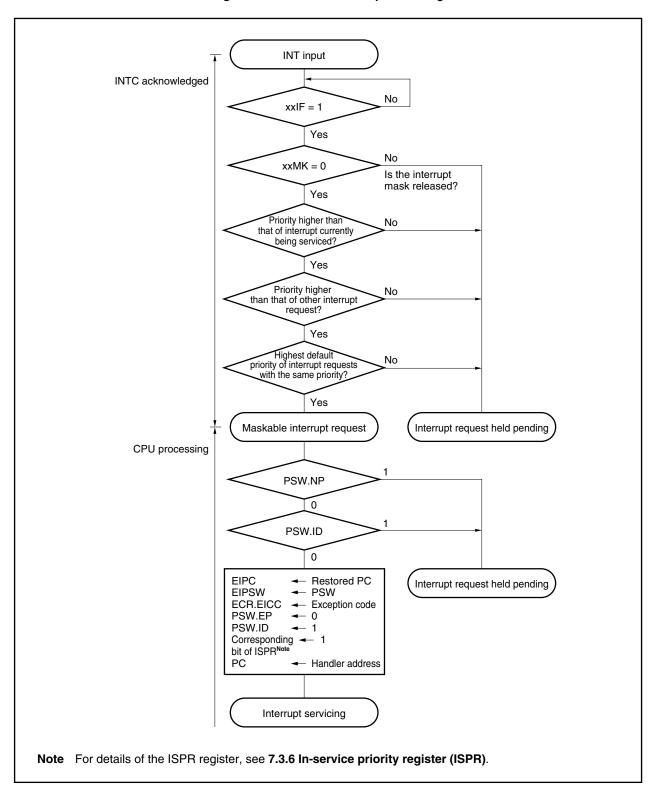

|        | 7.3.1 Operation                                             | 143 |

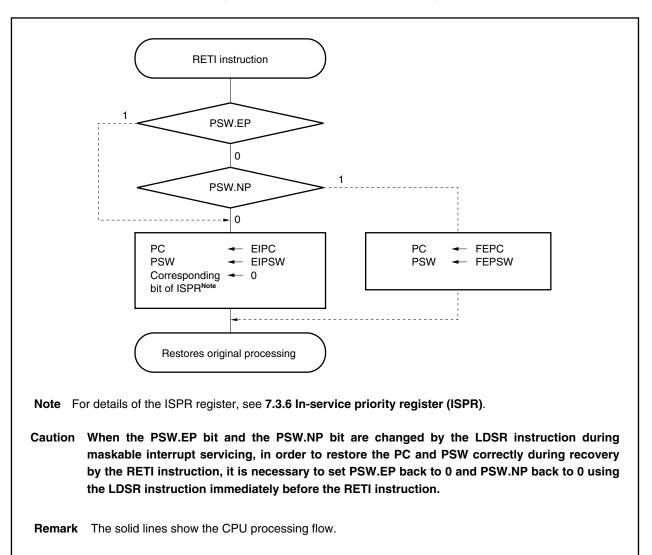

|        | 7.3.2 Restore                                               | 145 |

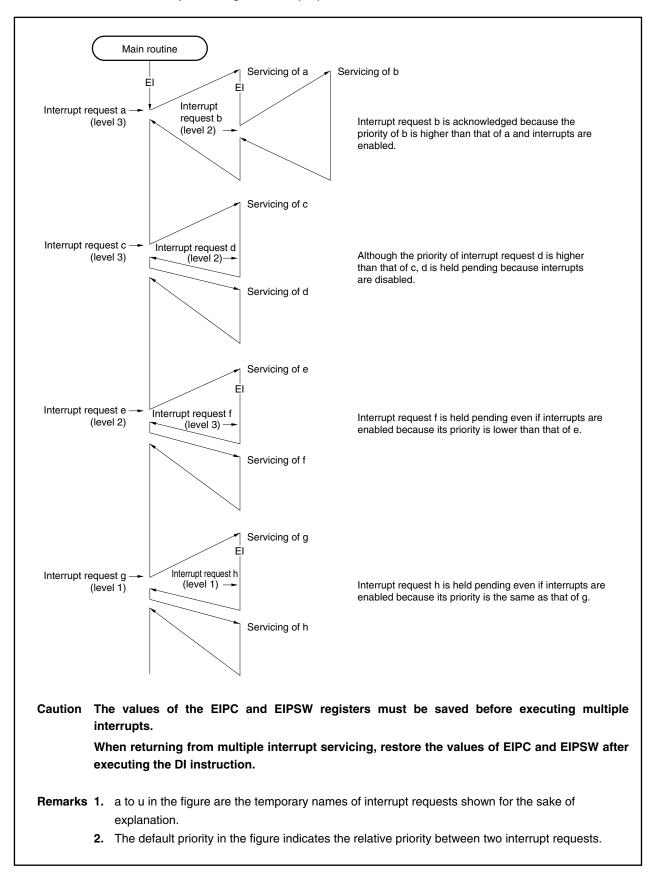

|        | 7.3.3 Priorities of maskable interrupts                     | 146 |

|        | 7.3.4 Interrupt control register (xxICn)                    | 150 |

|        | 7.3.5 Interrupt mask registers 0 to 3 (IMR0 to IMR3)        | 153 |

|        | 7.3.6 In-service priority register (ISPR)                   | 154 |

|        | 7.3.7 Maskable interrupt status flag (ID)                   | 155 |

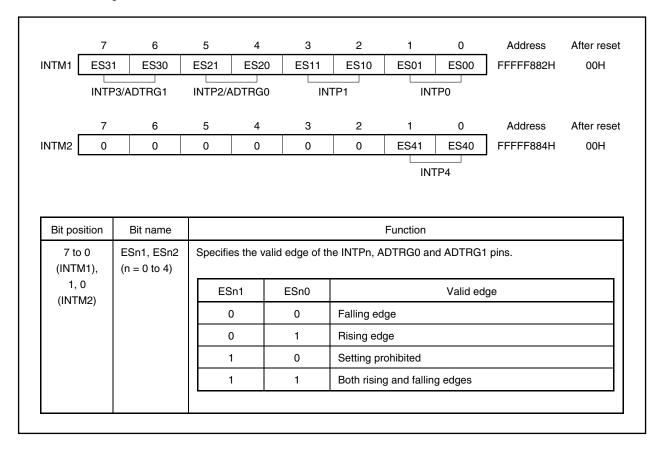

|        | 7.3.8 Interrupt trigger mode selection                      | 155 |

| 7.4    | Software Exception                                          | 163 |

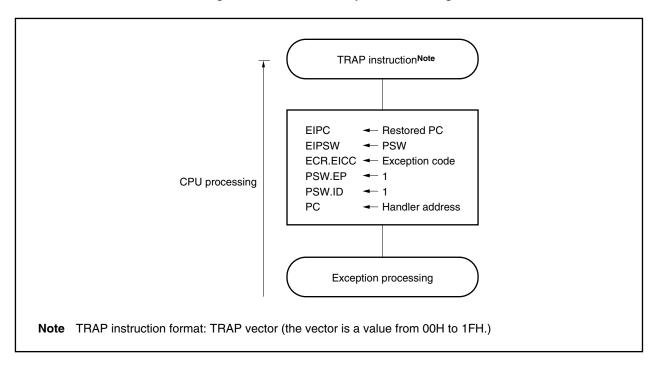

|        | 7.4.1 Operation                                             |     |

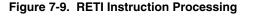

|        | 7.4.2 Restore                                               | 164 |

|        | 7.4.3 Exception status flag (EP)                            |     |

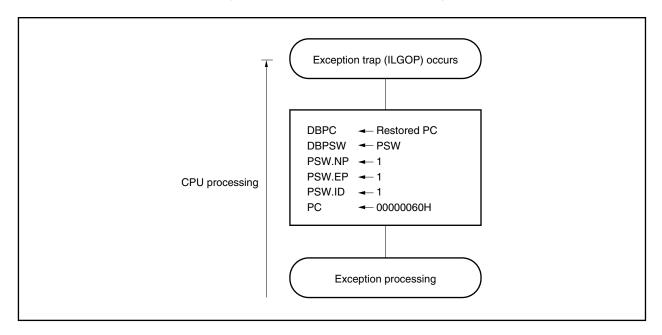

| 7.5    | Exception Trap                                              | 166 |

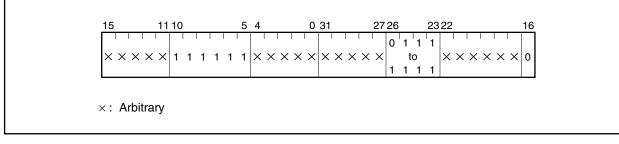

|        | 7.5.1 Illegal opcode definition                             |     |

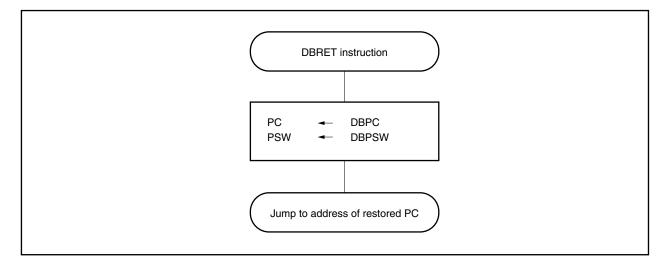

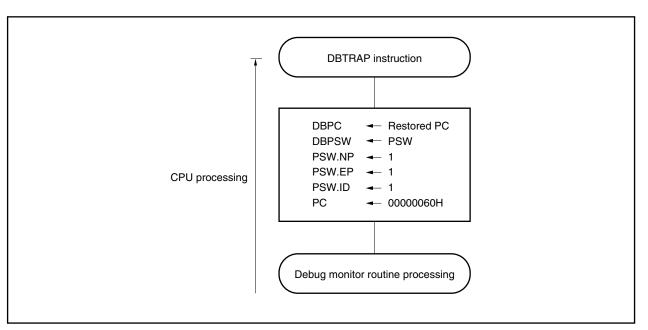

|        | 7.5.2 Debug trap                                            |     |

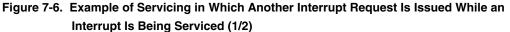

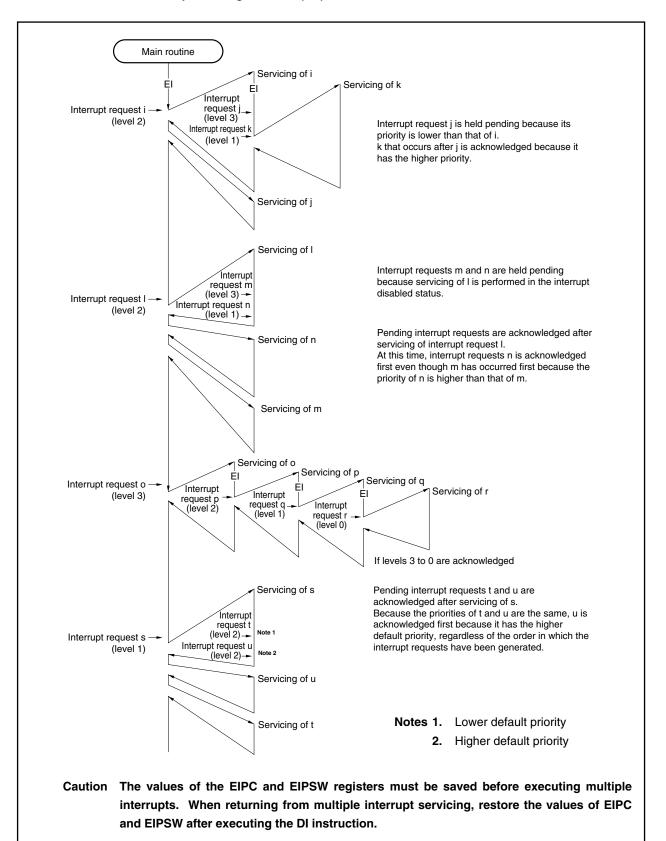

| 7.6    | Multiple Interrupt Servicing Control                        | 170 |

| 7.7    | Interrupt Response Time                                     | 172 |

| 7.8    | Periods in Which CPU Does Not Acknowledge Interrupts        | 173 |

|        |                                                             |     |

| CHAPTE | ER 8 CLOCK GENERATION FUNCTION                              | 174 |

| 8.1    | Features                                                    | 174 |

| 8.2    | Configuration                                               | 174 |

| 8.3    | Input Clock Selection                                       | 175 |

|        | 8.3.1 Direct mode                                           |     |

|        | 8.3.2 PLL mode                                              |     |

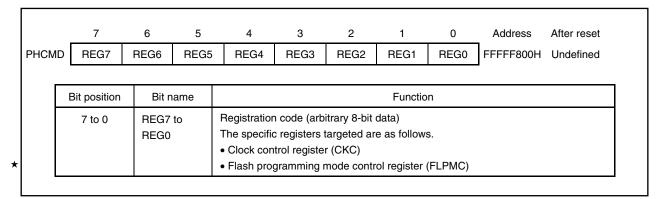

|        | 8.3.3 Peripheral command register (PHCMD)                   |     |

|        | 8.3.4 Clock control register (CKC)                          |     |

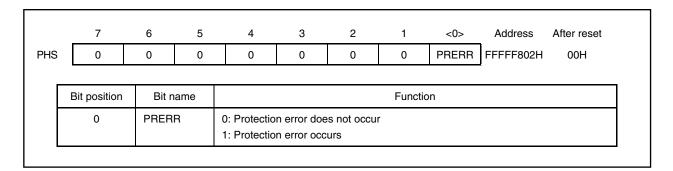

|        | 8.3.5 Peripheral status register (PHS)                      |     |

| 8.4    | PLL Lockup                                                  |     |

| 8.5    | Power Save Control                                          |     |

|        | 8.5.1 Overview                                              |     |

|        | 8.5.2 Control registers                                     |     |

|        | 8.5.3 HALT mode                                             |     |

|        | 8.5.4 IDLE mode                                             |     |

|        |                                                             |     |

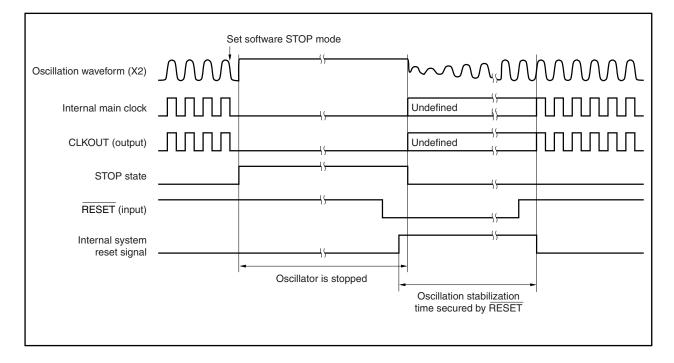

|       | 8.5.5          | Software STOP mode                                    | 191 |

|-------|----------------|-------------------------------------------------------|-----|

| 8.6   | Secur          | ing Oscillation Stabilization Time                    |     |

|       | 8.6.1          | Oscillation stabilization time security specification | 193 |

|       | 8.6.2          | Time base counter (TBC)                               | 194 |

|       |                |                                                       |     |

| CHAPT | ER 9 T         | IMER/COUNTER FUNCTION                                 | 195 |

| 9.1   | Timer          | 0                                                     |     |

|       | 9.1.1          | Features (timer 0)                                    | 195 |

|       | 9.1.2          | Function overview (timer 0)                           | 196 |

|       | 9.1.3          | Functions added to V850E/IA2                          | 197 |

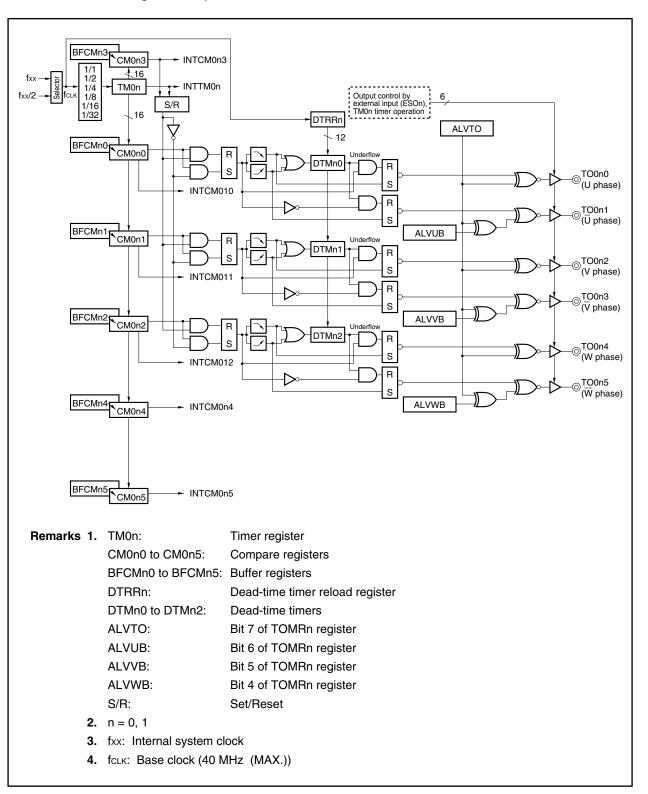

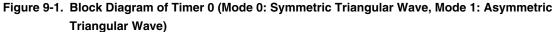

|       | 9.1.4          | Basic configuration                                   | 198 |

|       | 9.1.5          | Control registers                                     | 205 |

|       | 9.1.6          | Operation                                             | 229 |

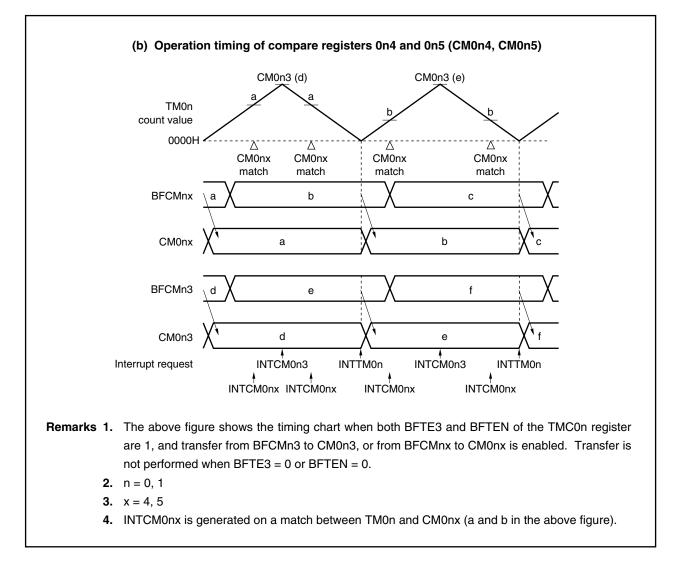

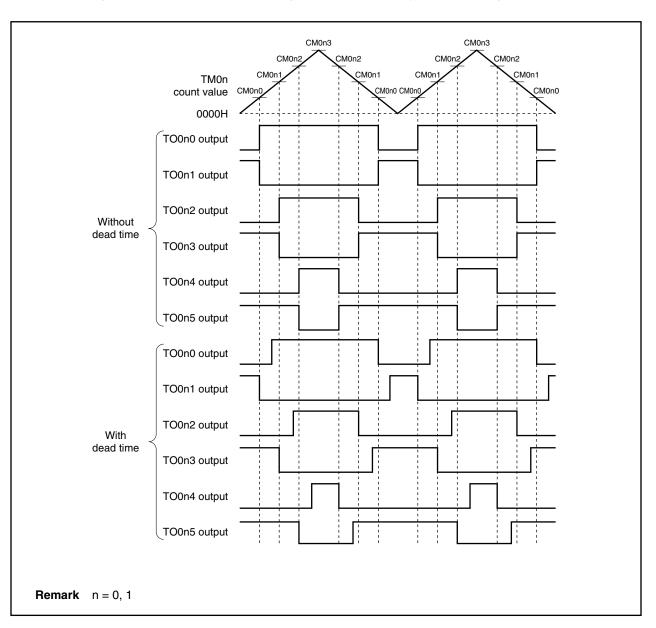

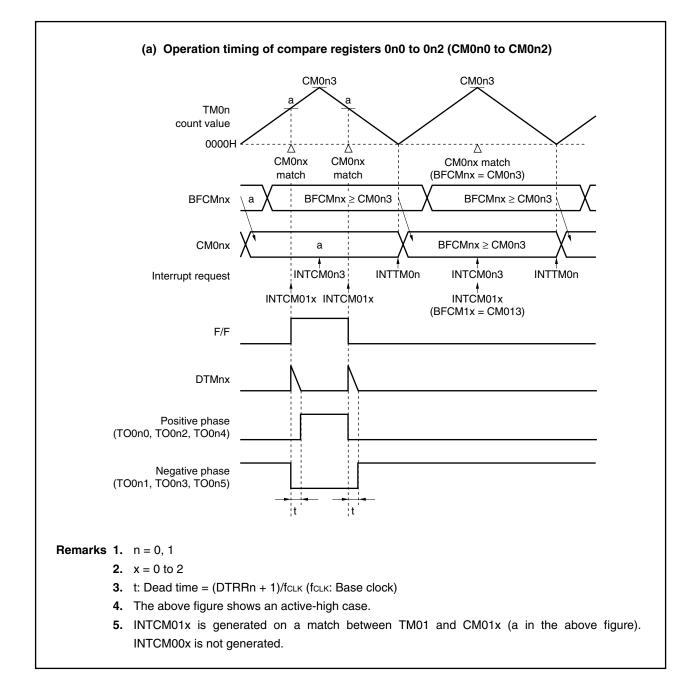

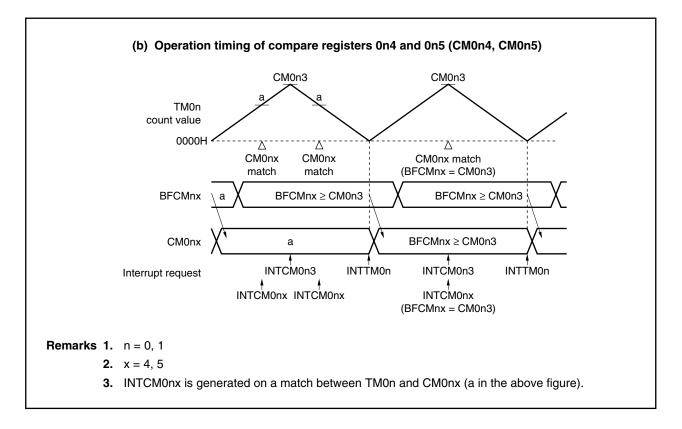

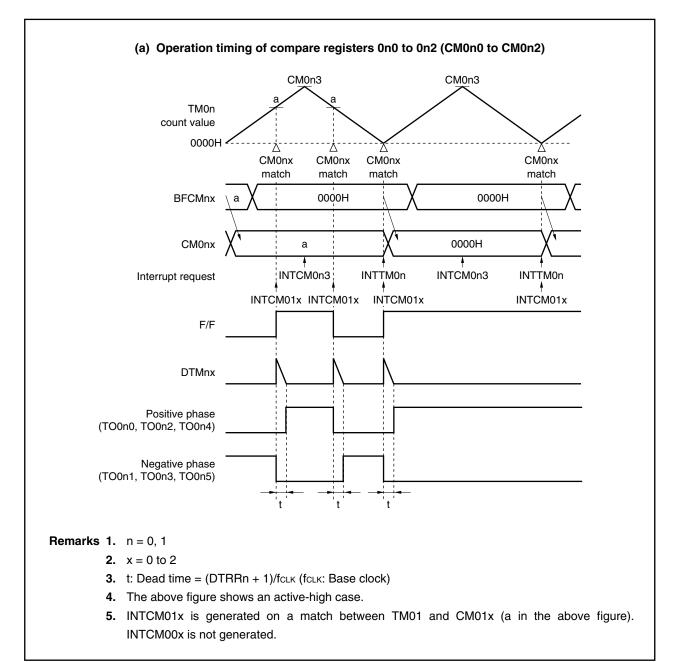

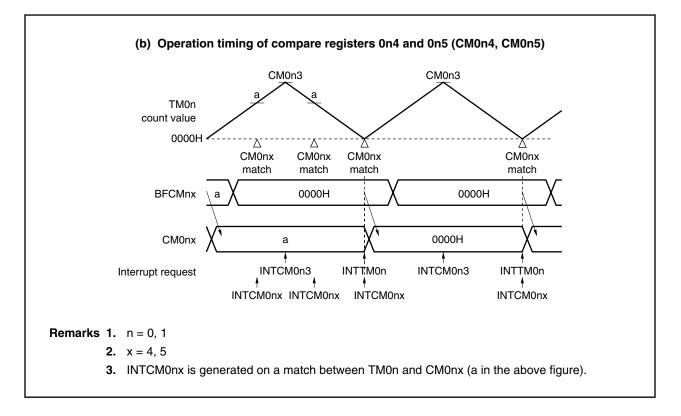

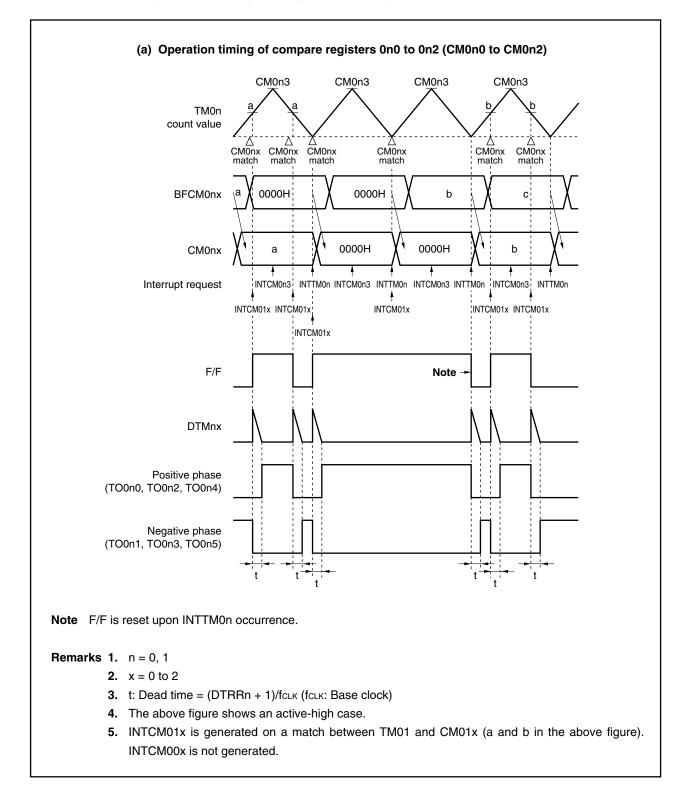

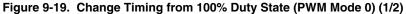

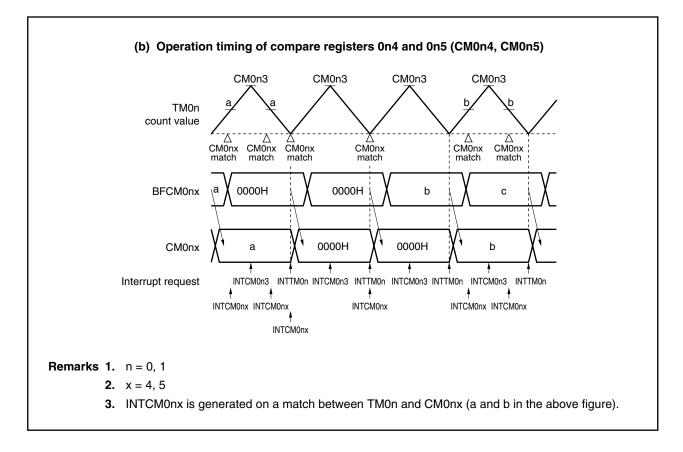

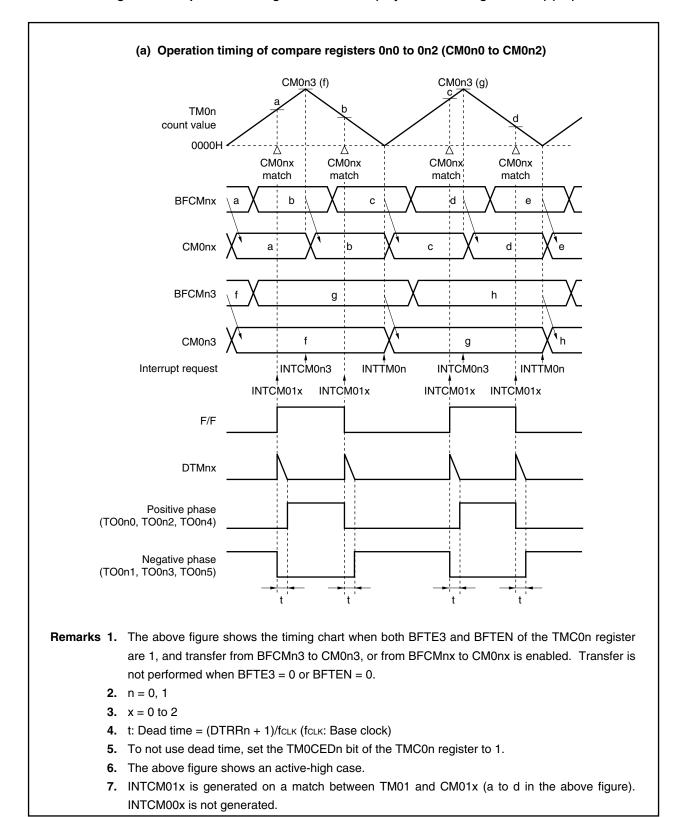

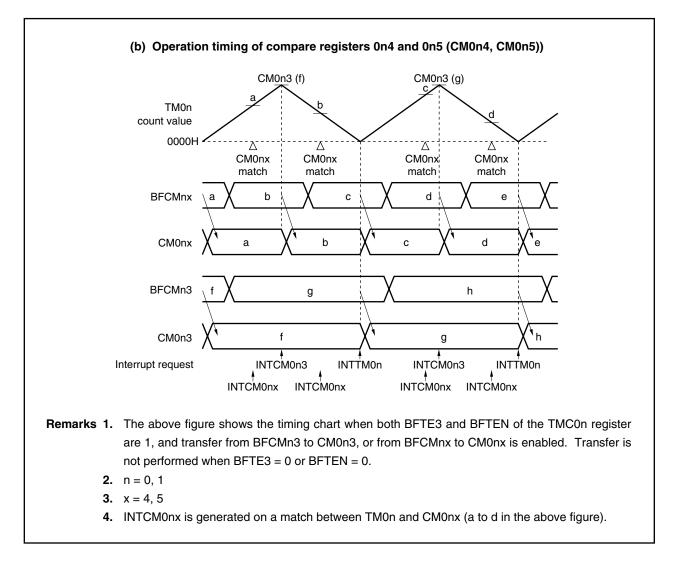

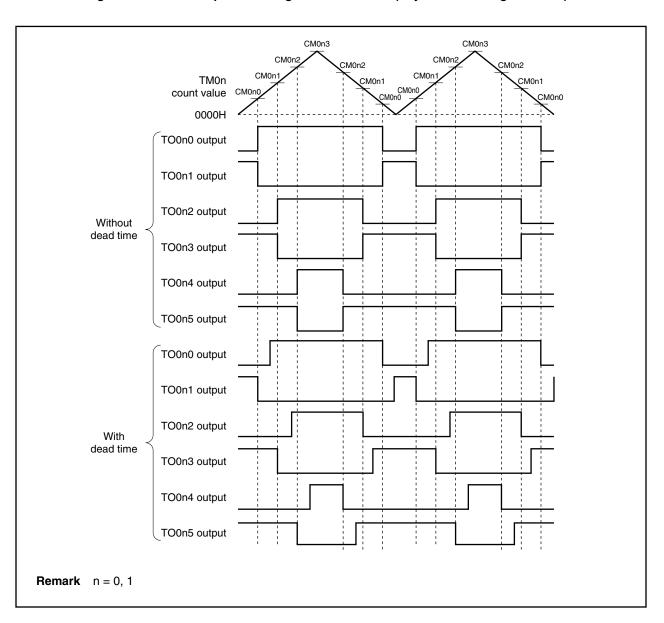

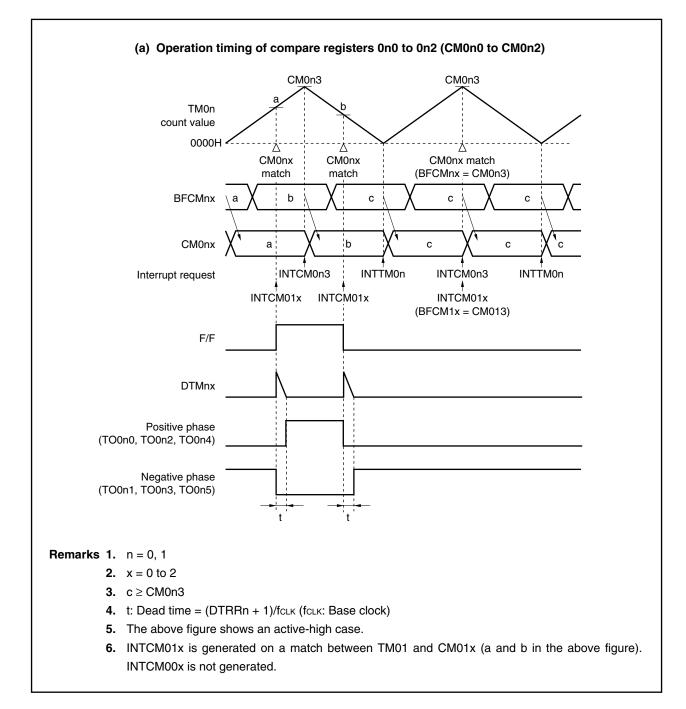

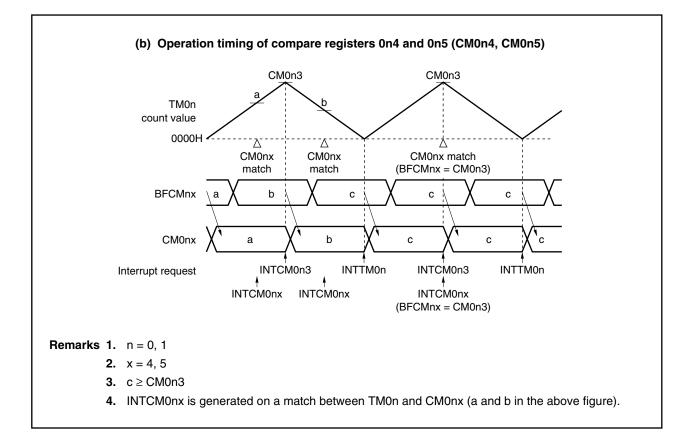

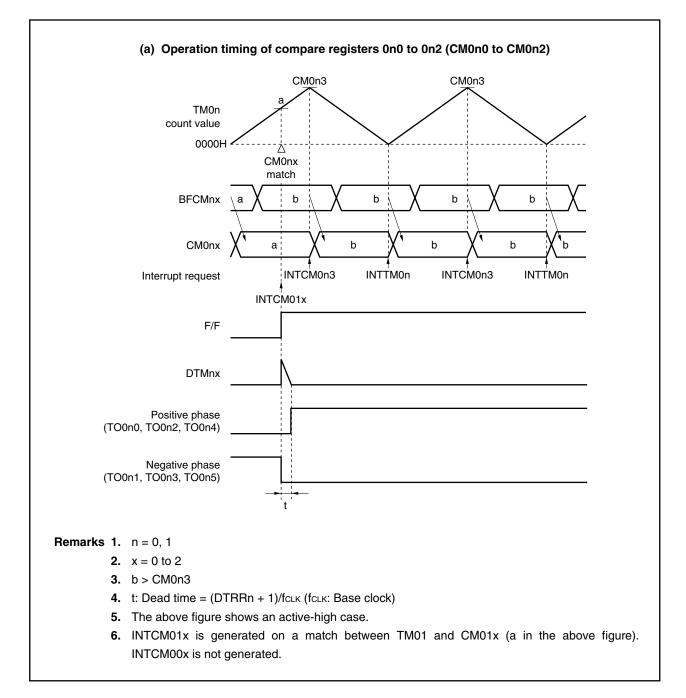

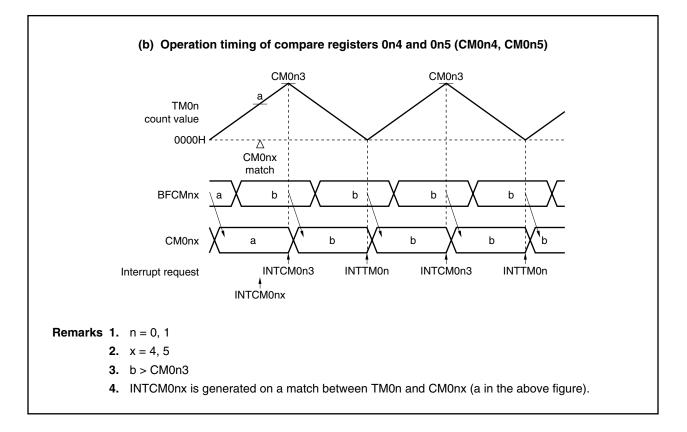

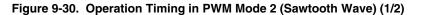

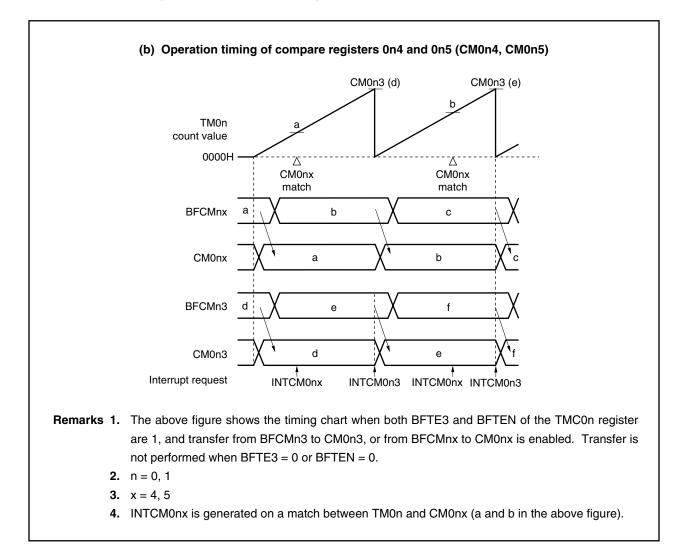

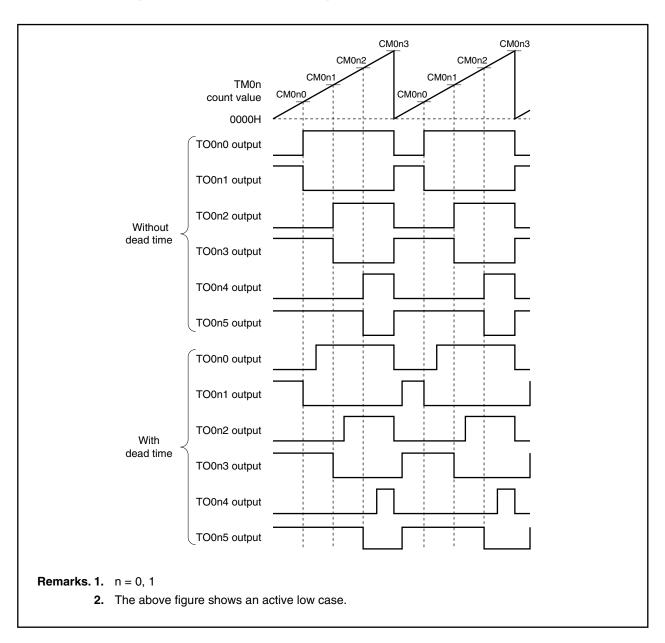

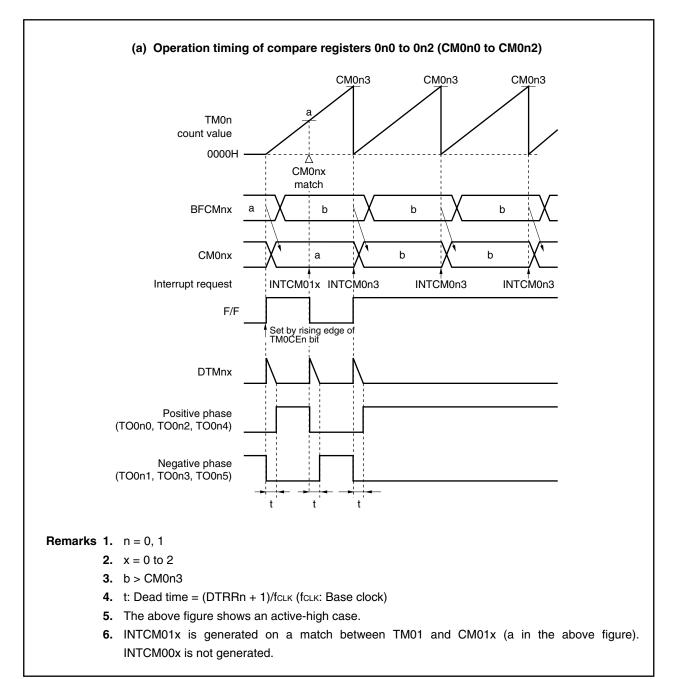

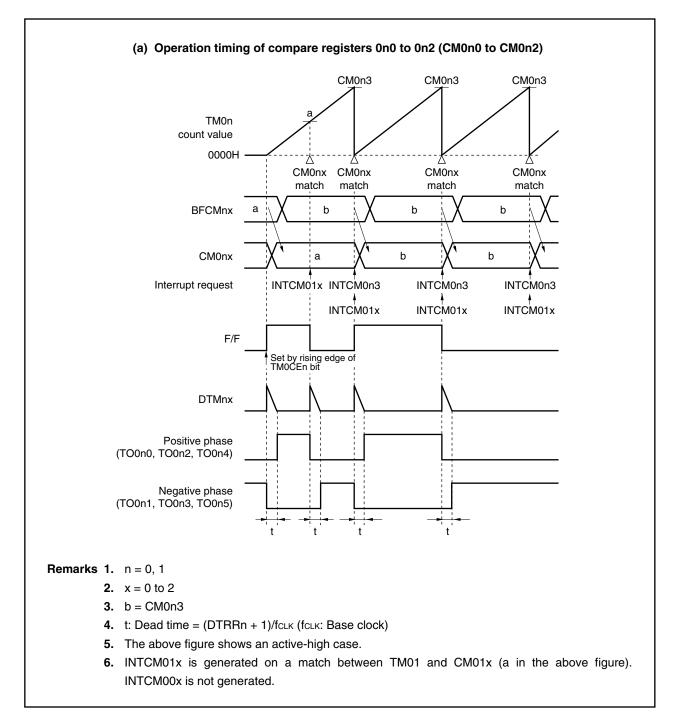

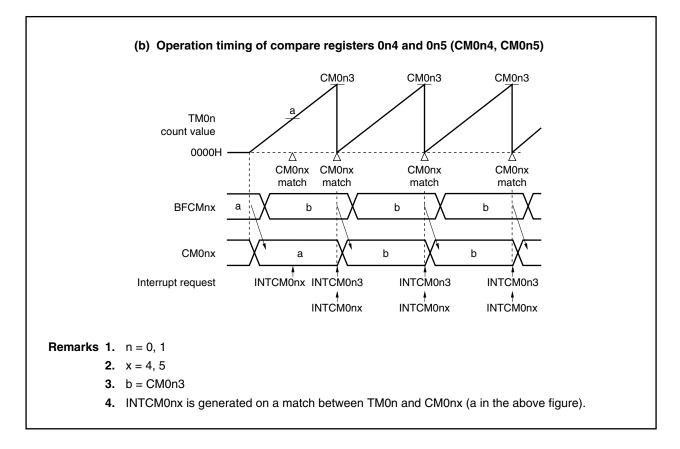

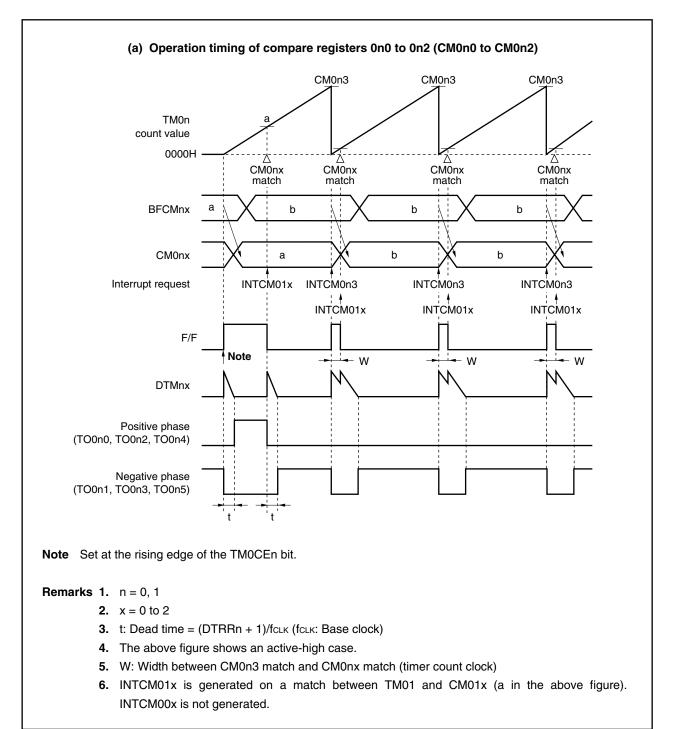

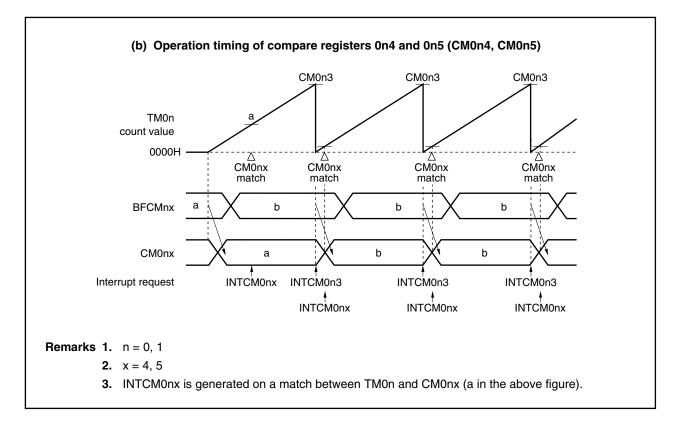

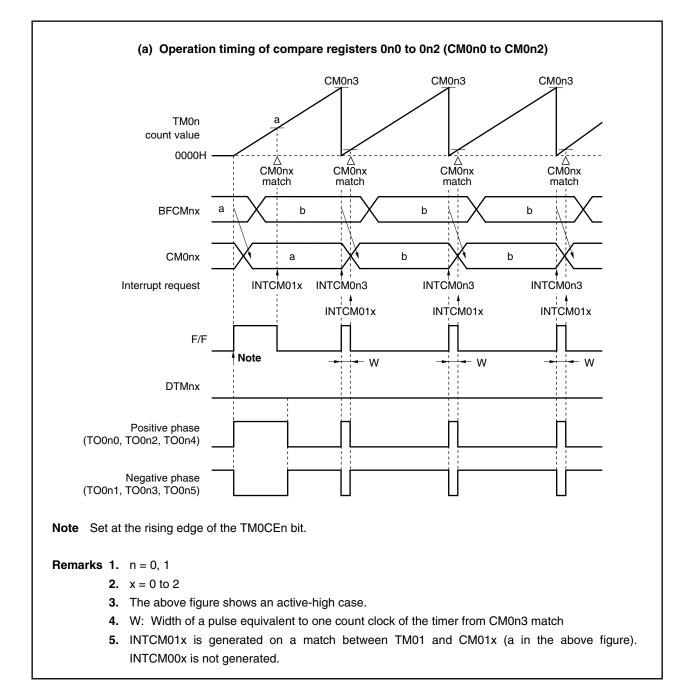

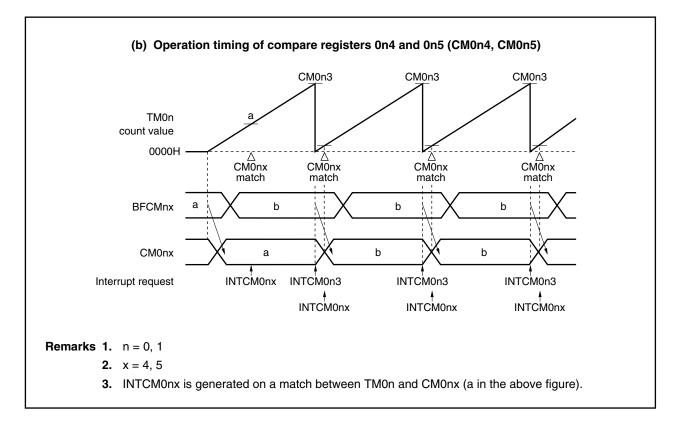

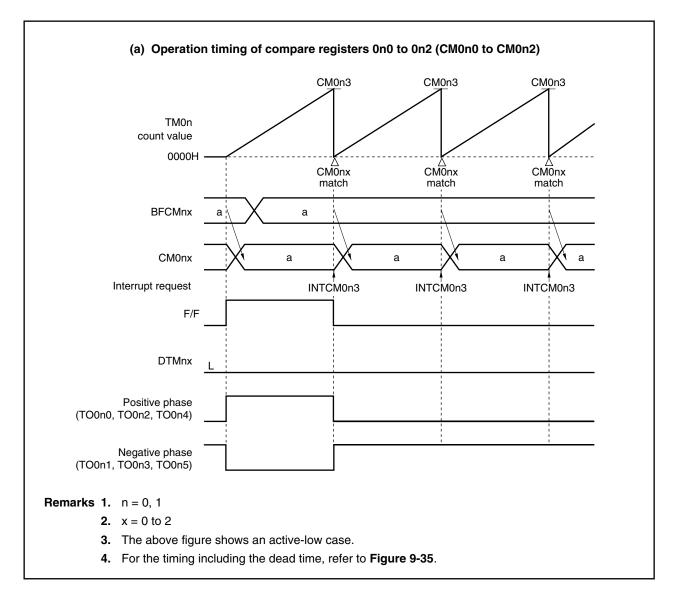

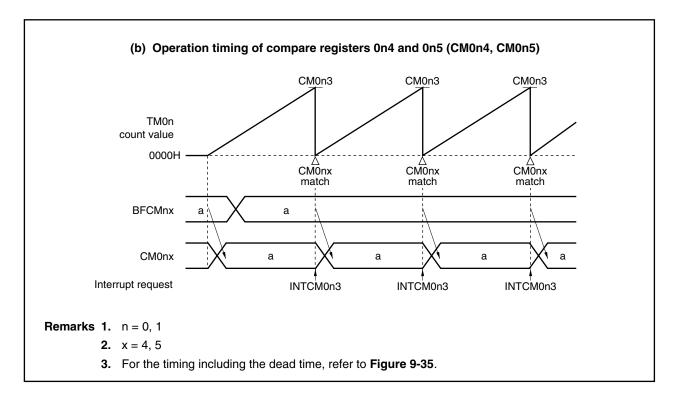

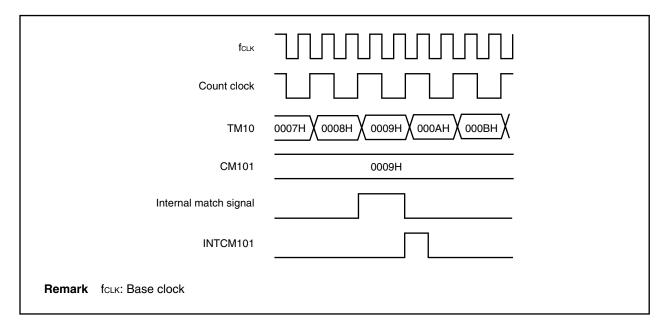

|       | 9.1.7          | Operation timing                                      |     |

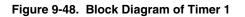

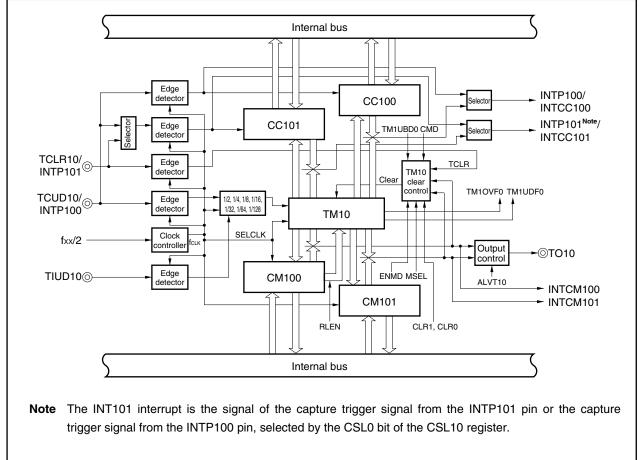

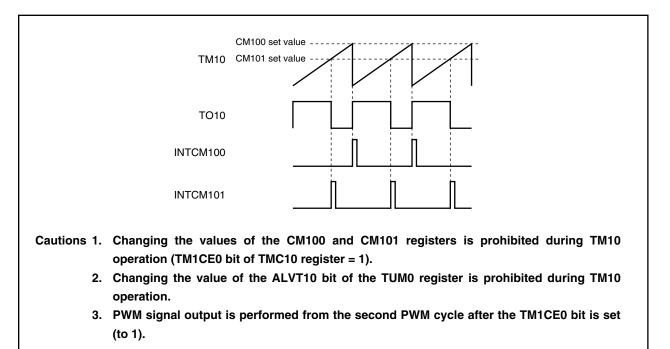

| 9.2   | Timer          | 1                                                     |     |

|       | 9.2.1          | Features (timer 1)                                    |     |

|       | 9.2.2          | Function overview (timer 1)                           |     |

|       | 9.2.3          | Basic configuration                                   |     |

|       | 9.2.4          | Control registers                                     |     |

|       | 9.2.5          | Operation                                             |     |

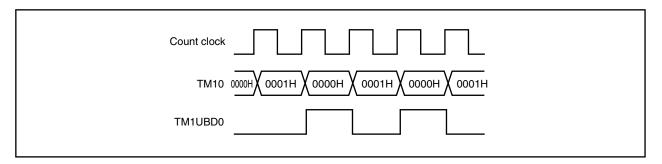

|       | 9.2.6          | Supplementary description of internal operation       |     |

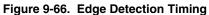

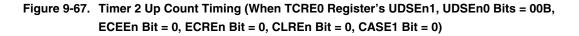

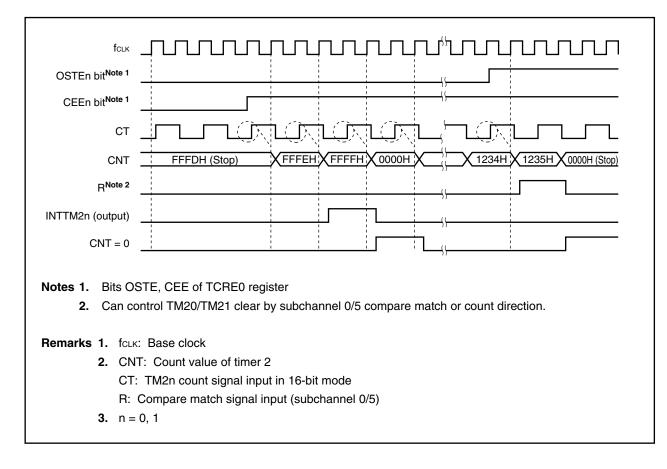

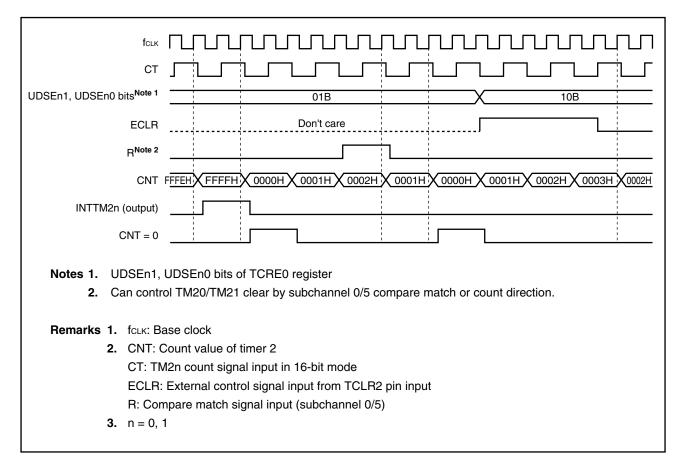

| 9.3   |                | 2                                                     |     |

|       | 9.3.1          | Features (timer 2)                                    |     |

|       | 9.3.2          | Function overview (timer 2)                           |     |

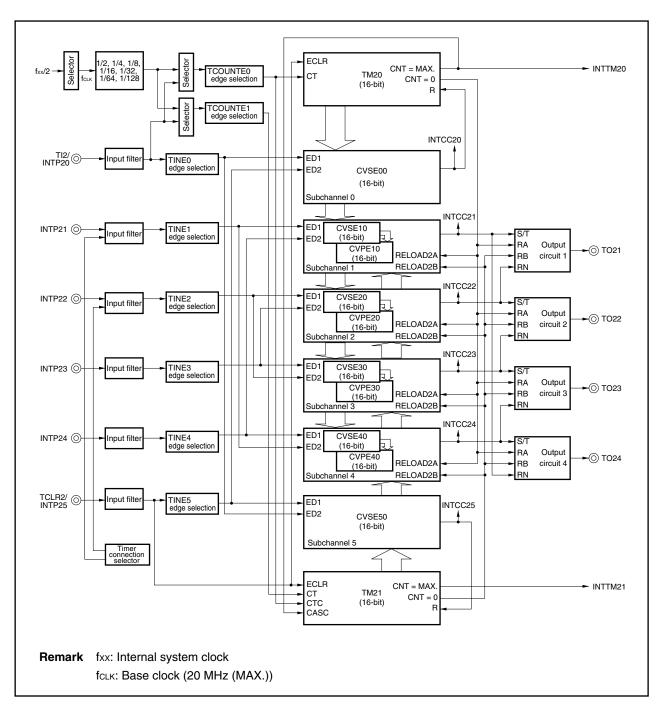

|       | 9.3.3          | Basic configuration                                   |     |

|       | 9.3.4          | Control registers                                     |     |

|       | 9.3.5          | Operation                                             |     |

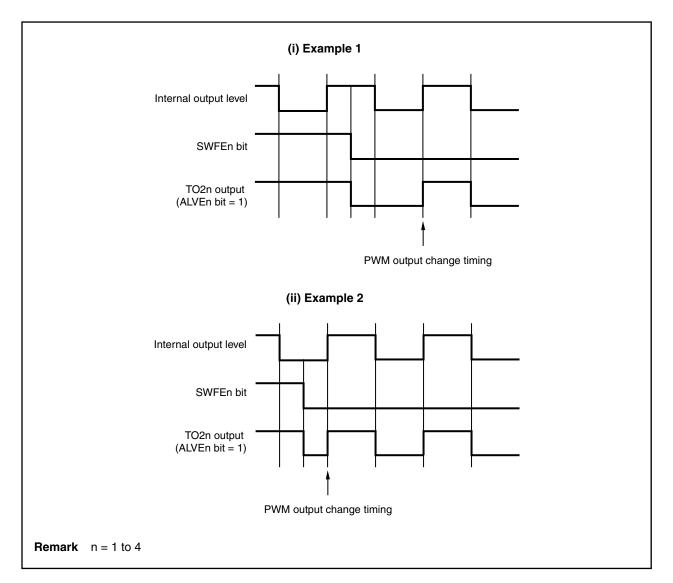

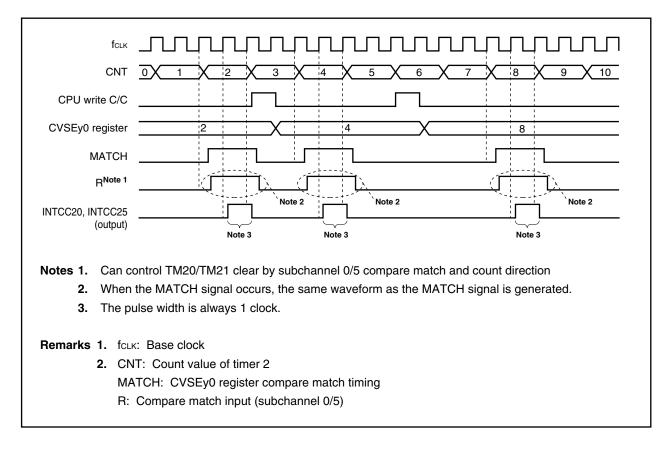

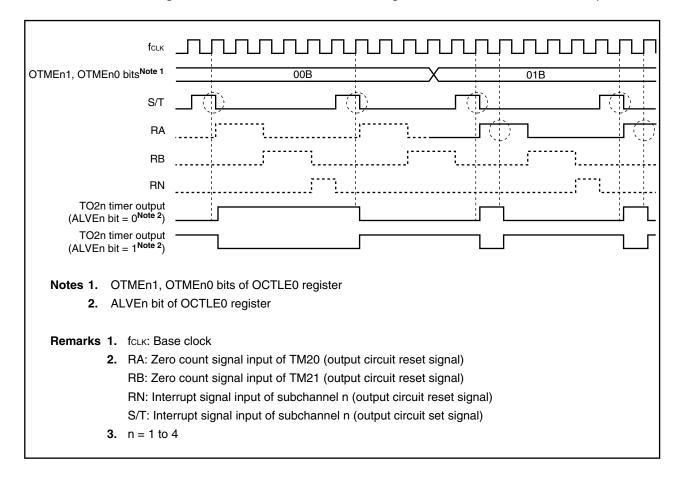

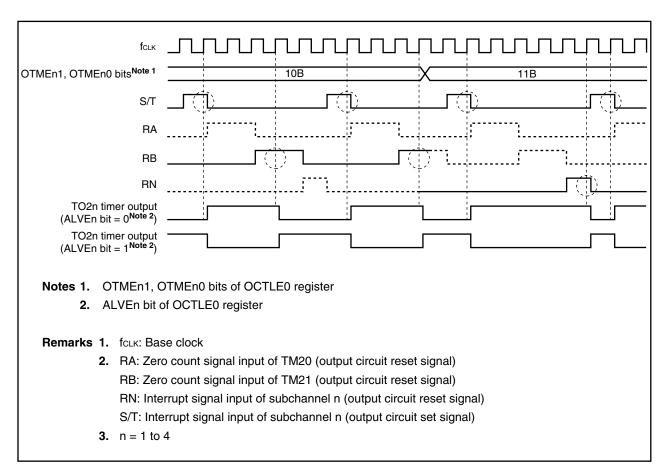

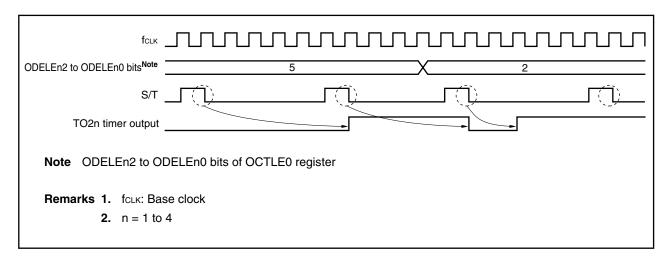

|       | 9.3.6          | PWM output operation in timer 2 compare mode          |     |

| 9.4   |                | 3                                                     |     |

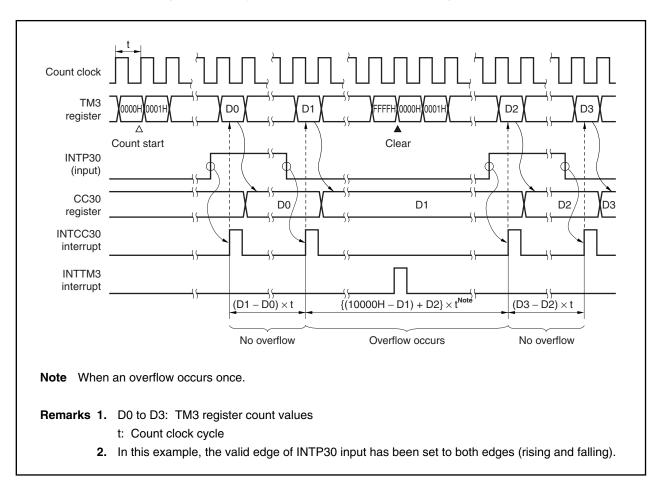

|       | 9.4.1          | Features (timer 3)                                    |     |

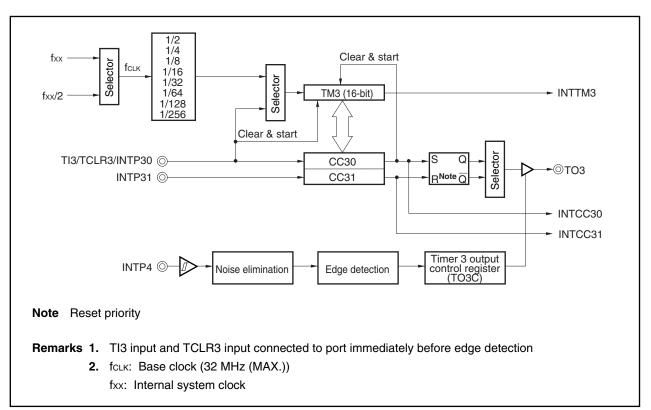

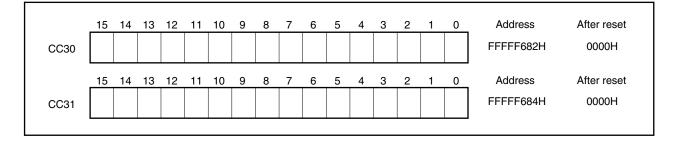

|       | 9.4.2          | Function overview (timer 3)                           |     |

|       | 9.4.3          | Function added to V850E/IA2                           |     |

|       | 9.4.4          | Basic configuration                                   |     |

|       | 9.4.5          | Control registers                                     |     |

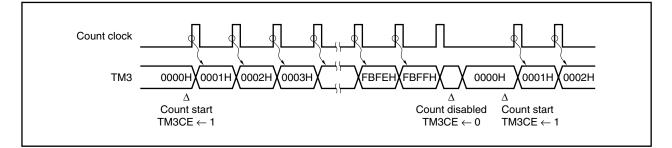

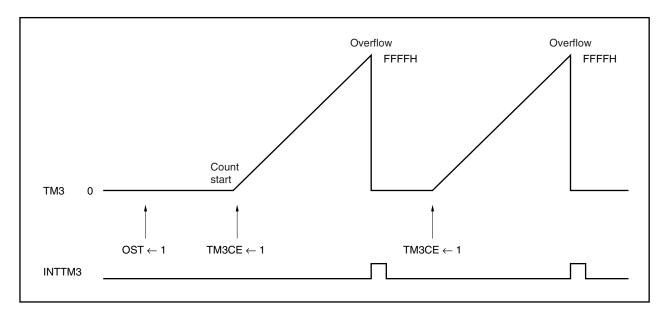

|       | 9.4.6          | Operation                                             |     |

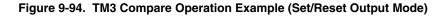

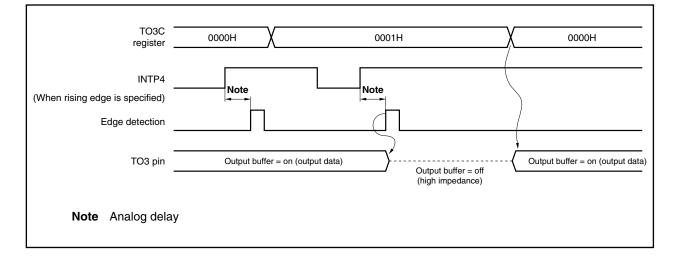

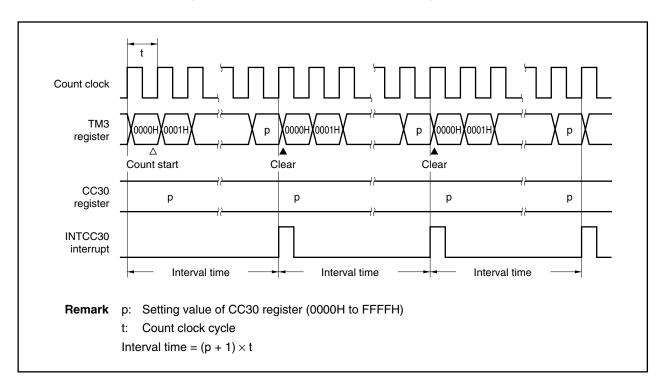

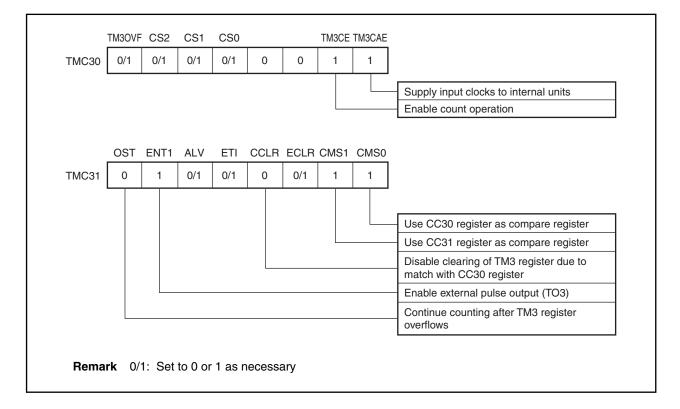

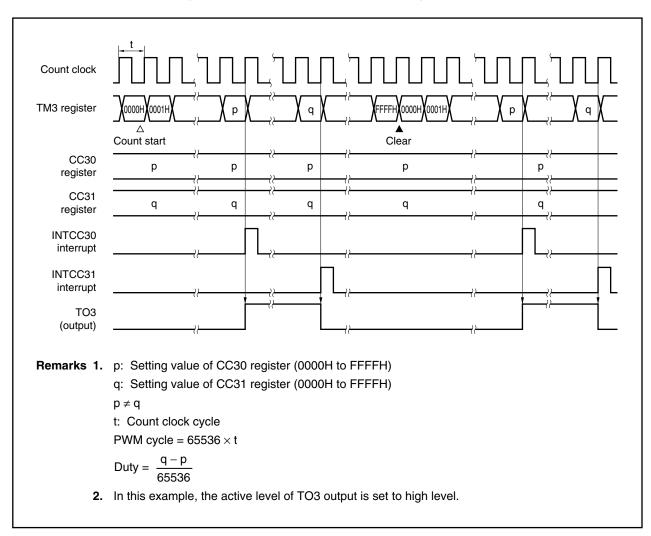

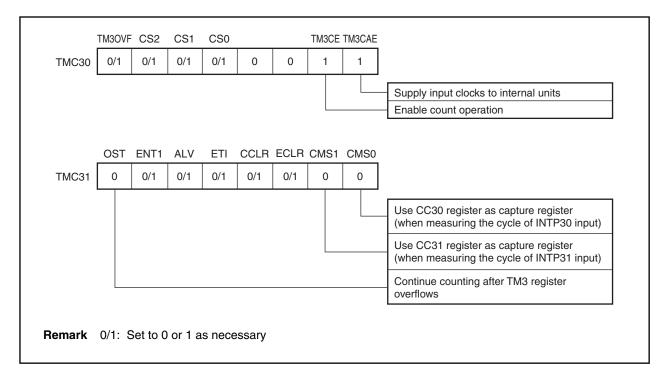

|       | 9.4.7          | Application examples                                  |     |

| 0.5   | 9.4.8          | Cautions                                              |     |

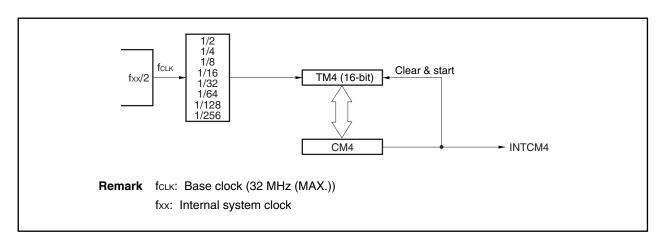

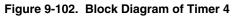

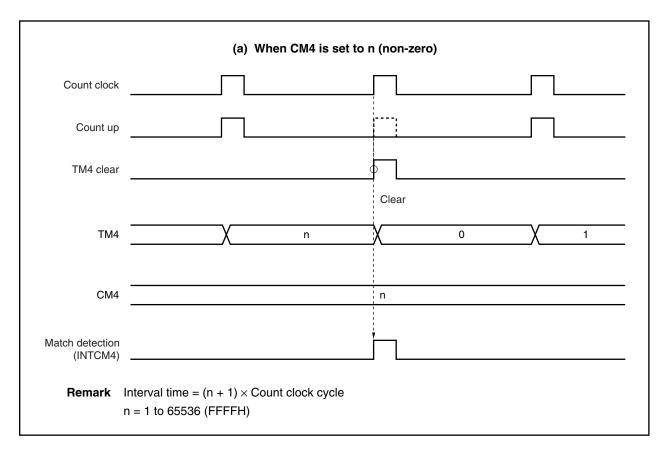

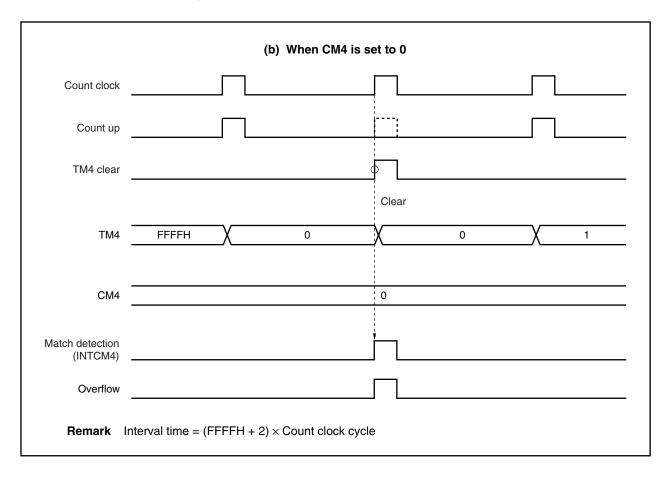

| 9.5   |                | 4                                                     |     |

|       | 9.5.1          | Features (timer 4)                                    |     |

|       | 9.5.2          | Function overview (timer 4)                           |     |

|       | 9.5.3          | Basic configuration                                   |     |

|       | 9.5.4<br>0.5.5 | Control register                                      |     |

|       | 9.5.5          | Operation                                             |     |

|       | 9.5.6          | Application example                                   |     |

| 9.6   | 9.5.7<br>Timor | Cautions Connection Function                          |     |

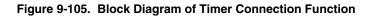

| 9.0   | 9.6.1          |                                                       |     |

|       |                | Overview                                              |     |

|       | 9.6.2          | Control register                                      |     |

| CHAPTE | R 10             | SERIAL INTERFACE FUNCTION                                     | 406 |

|--------|------------------|---------------------------------------------------------------|-----|

| 10.1   | Featur           | res                                                           |     |

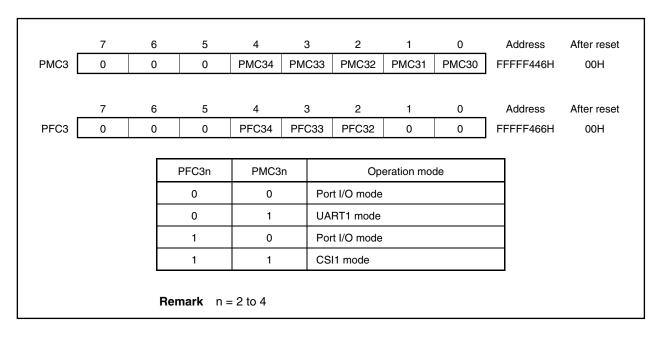

|        | 10.1.1           | Selecting UART1 or CSI1 mode                                  |     |

| 10.2   | Async            | chronous Serial Interface 0 (UART0)                           |     |

|        | 10.2.1           | Features                                                      |     |

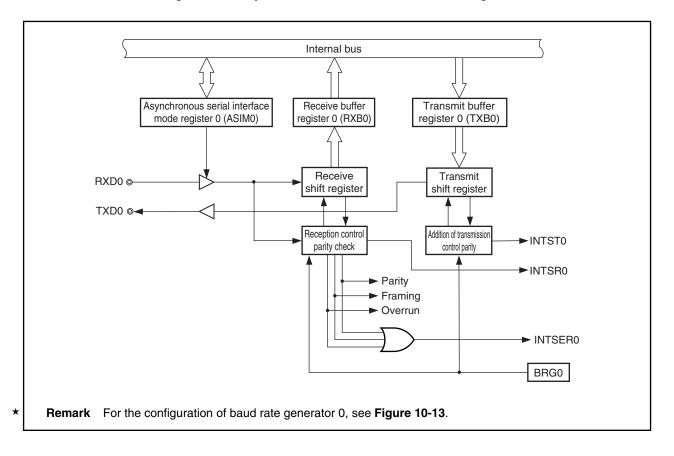

|        | 10.2.2           | Configuration                                                 |     |

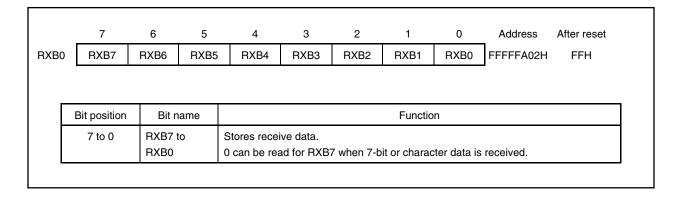

|        | 10.2.3           | Control registers                                             |     |

|        | 10.2.4           | Interrupt requests                                            |     |

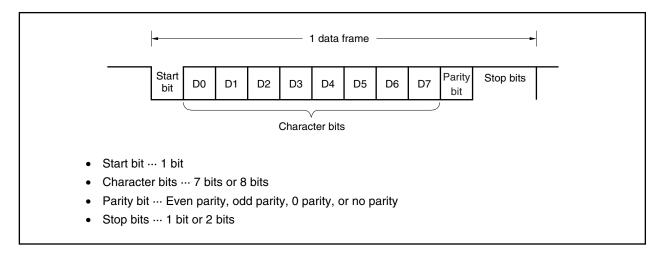

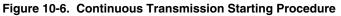

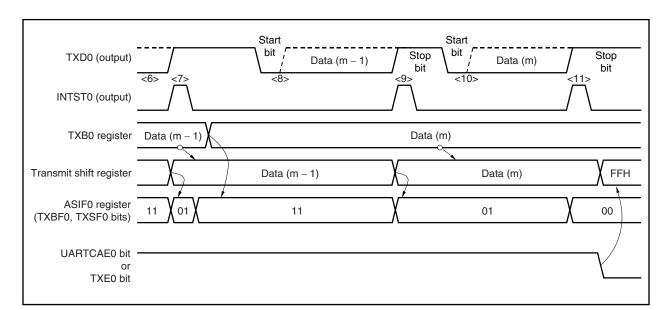

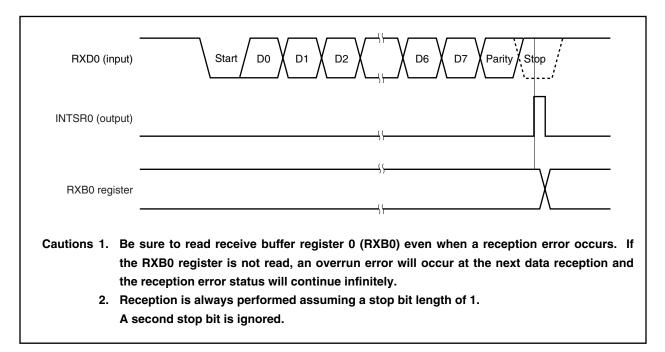

|        | 10.2.5           | Operation                                                     |     |

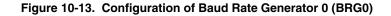

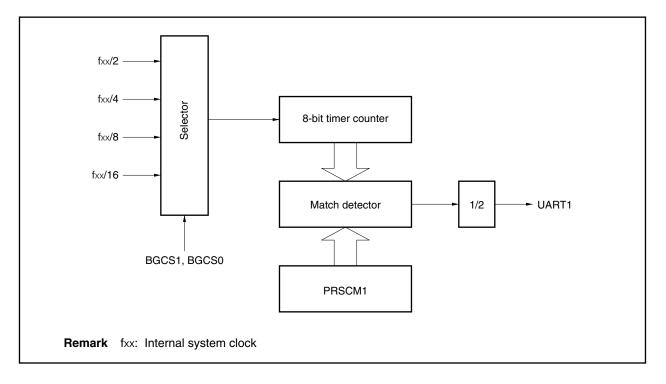

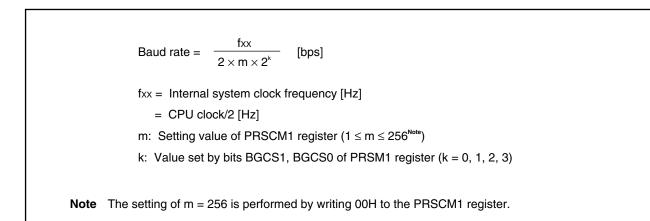

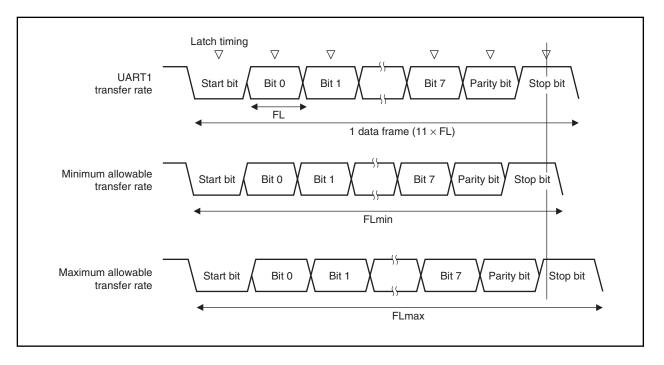

|        | 10.2.6           | Dedicated baud rate generator 0 (BRG0)                        |     |

|        | 10.2.7           | Cautions                                                      |     |

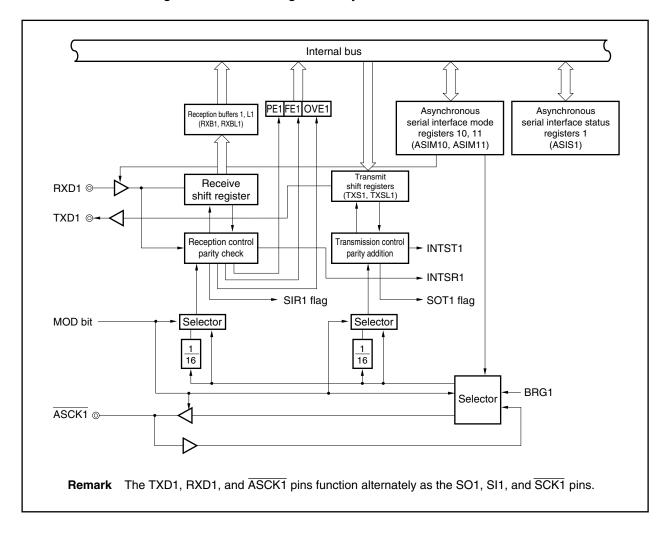

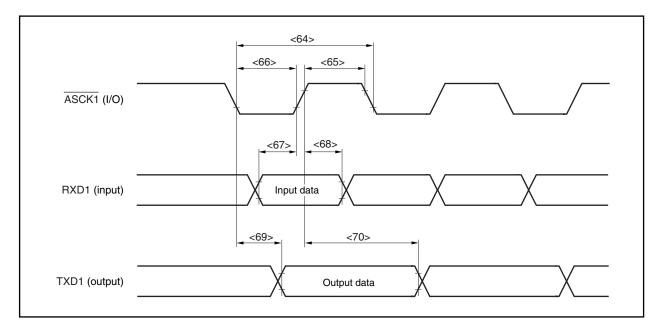

| 10.3   | Async            | hronous Serial Interface 1 (UART1)                            | 439 |

|        | 10.3.1           | Features                                                      |     |

|        | 10.3.2           | Configuration                                                 |     |

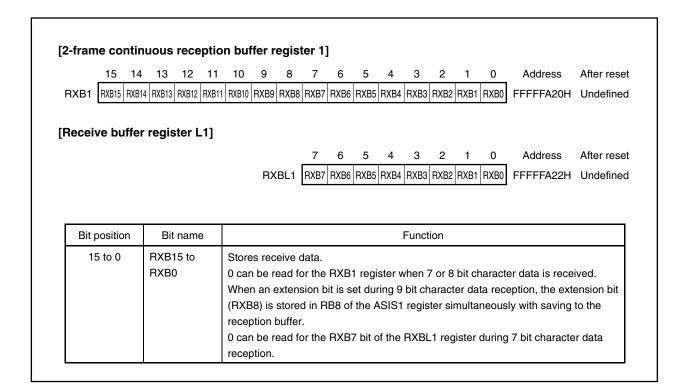

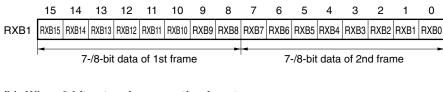

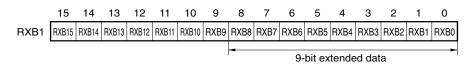

|        | 10.3.3           | Control registers                                             |     |

|        | 10.3.4           | Interrupt requests                                            | 451 |

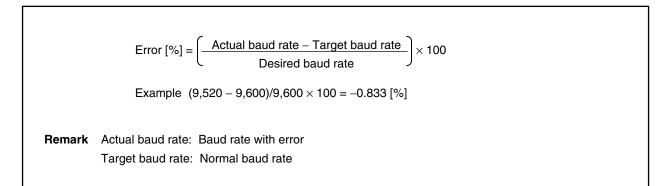

|        | 10.3.5           | Operation                                                     |     |

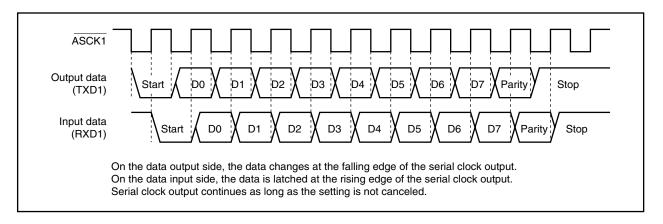

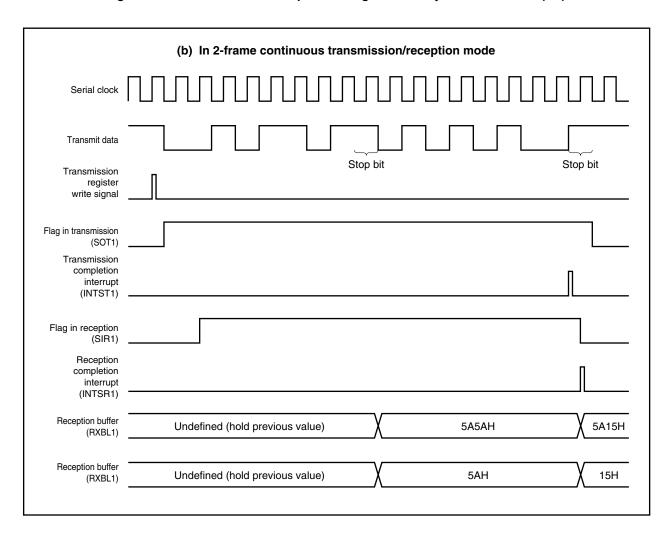

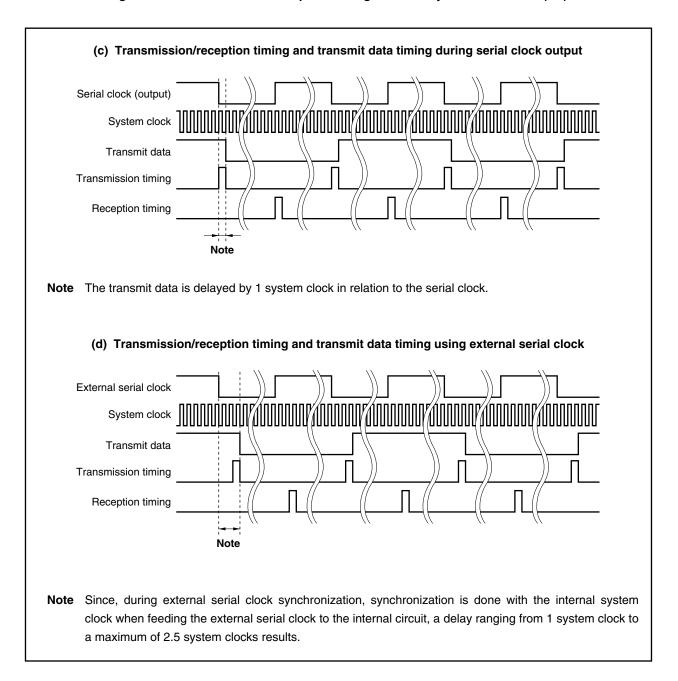

|        | 10.3.6           | Synchronous mode                                              |     |

|        | 10.3.7           | Dedicated baud rate generator 1 (BRG1)                        |     |

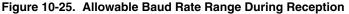

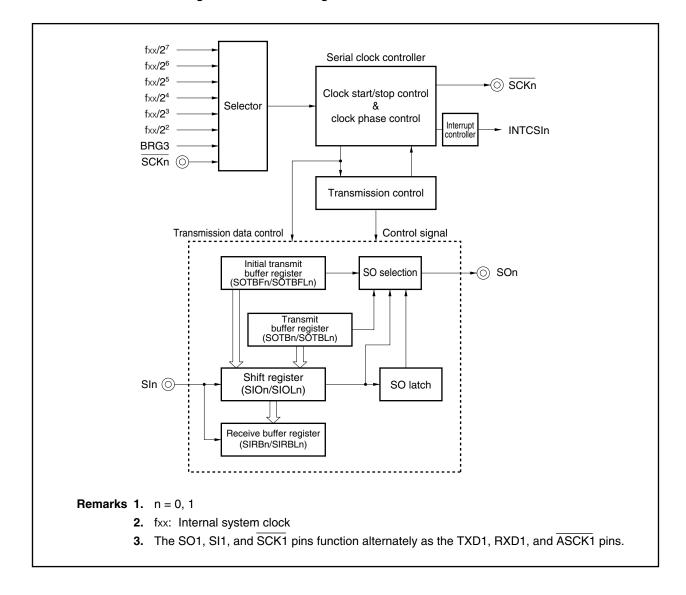

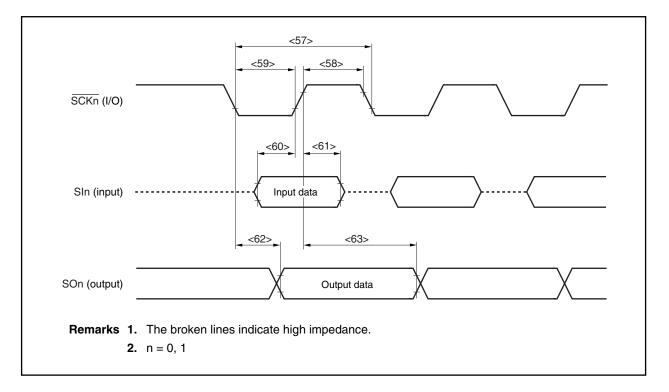

| 10.4   | Clocke           | ed Serial Interfaces 0, 1 (CSI0, CSI1)                        |     |

|        | 10.4.1           | Features                                                      | 474 |

|        | 10.4.2           | Configuration                                                 |     |

|        | 10.4.3           | Control registers                                             |     |

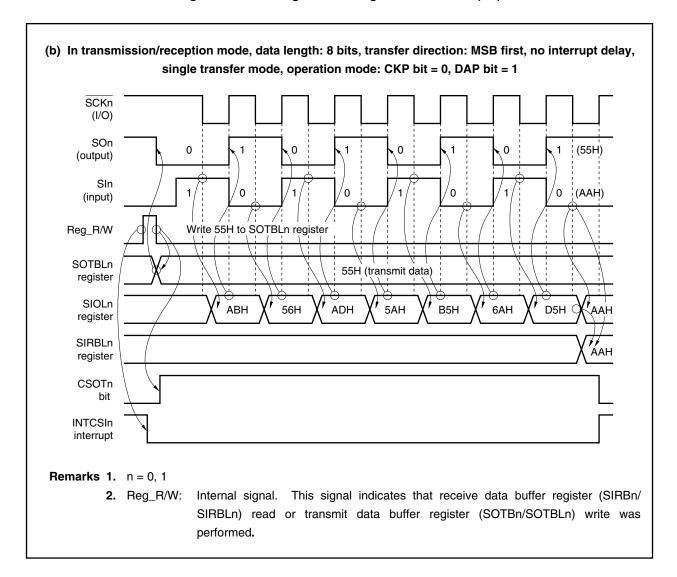

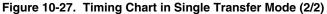

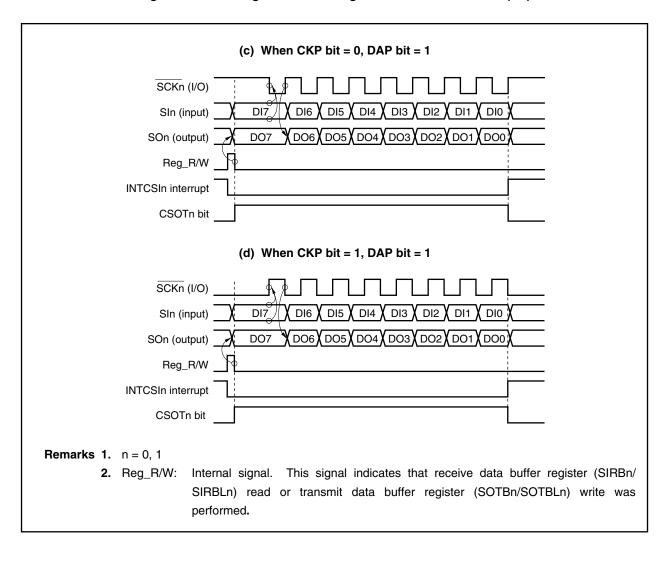

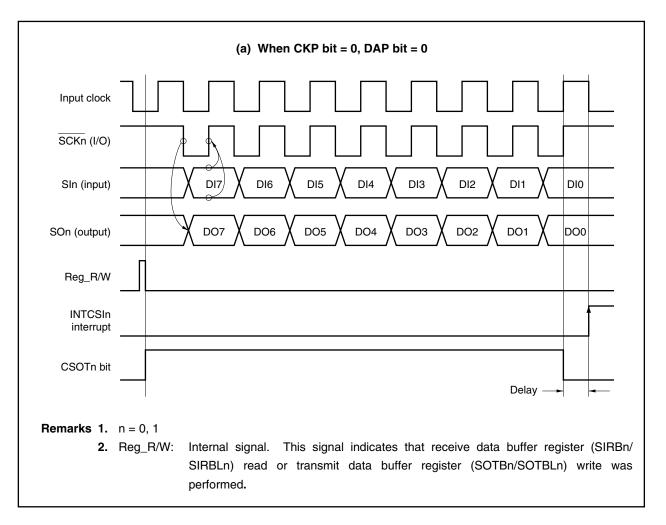

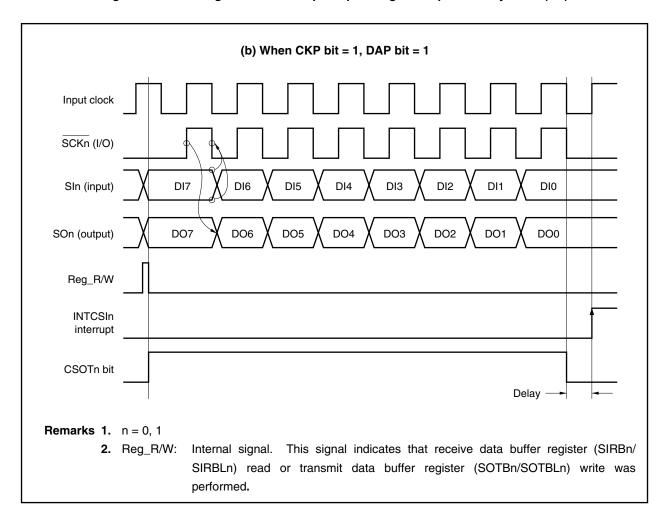

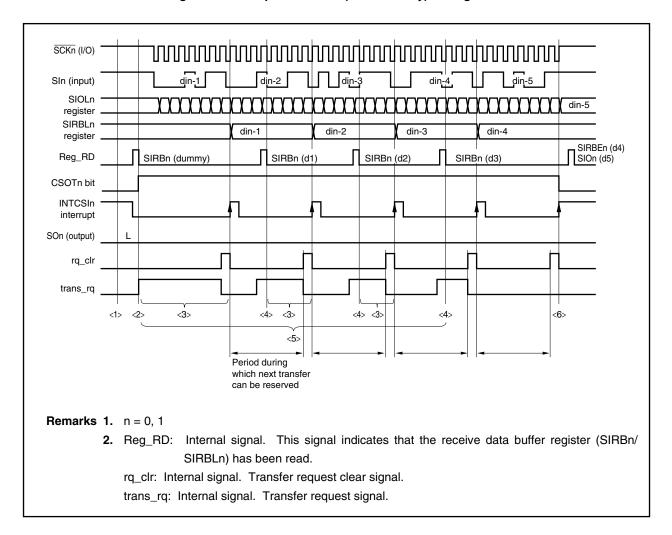

|        | 10.4.4           | Operation                                                     |     |

|        | 10.4.5           | Output pins                                                   |     |

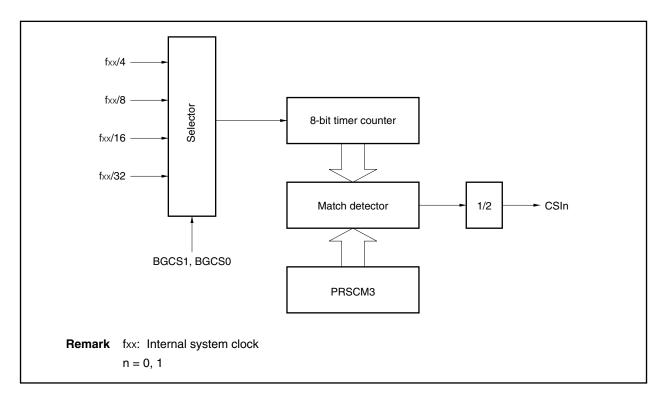

|        | 10.4.6           | Dedicated baud rate generator 3 (BRG3)                        |     |

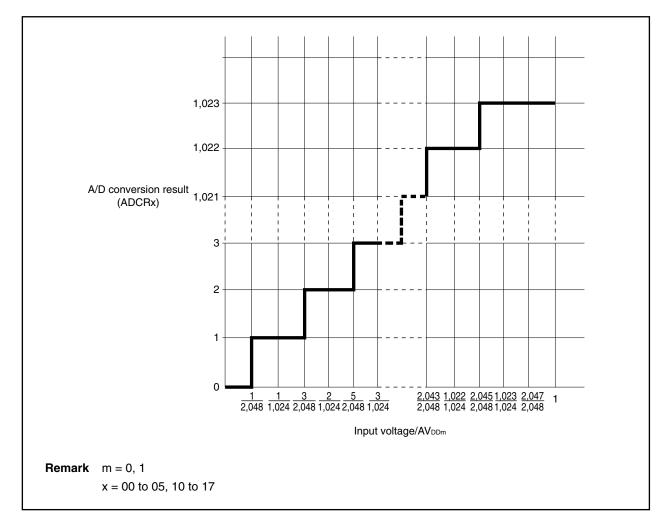

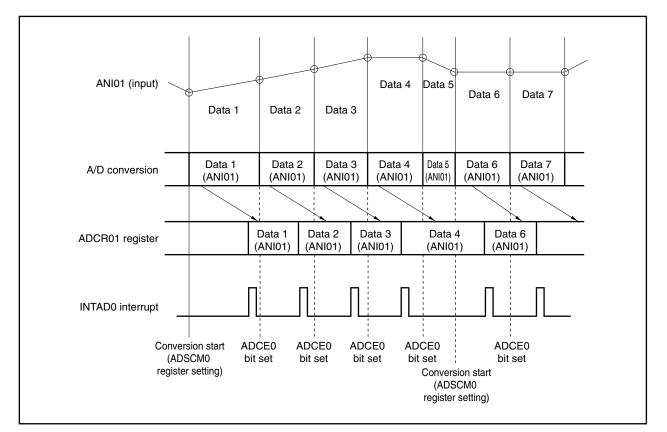

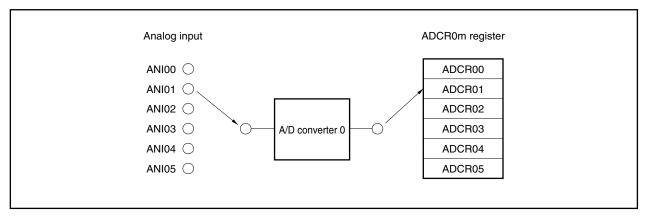

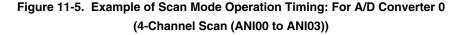

| СНАРТЕ | R 11             | A/D CONVERTER                                                 | 512 |

|        |                  | res                                                           |     |

| 11.1   |                  |                                                               | -   |

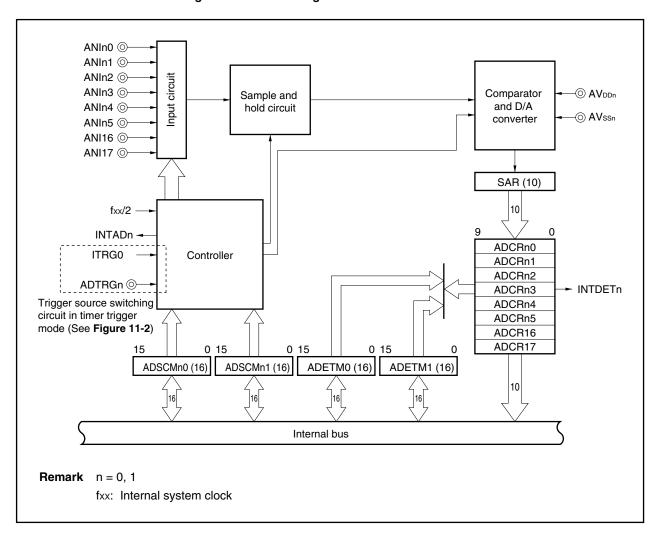

| 11.2   | -                | guration                                                      |     |

|        |                  | ions Added to V850E/IA2                                       |     |

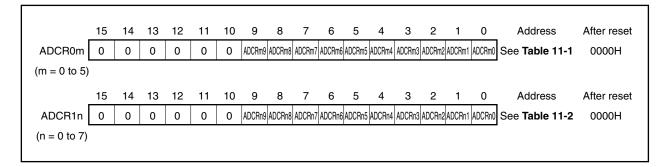

| 11.4   |                  | ol Registers                                                  |     |

| 11.5   |                  | upt Requests                                                  |     |

| 11.6   |                  | onverter Operation                                            |     |

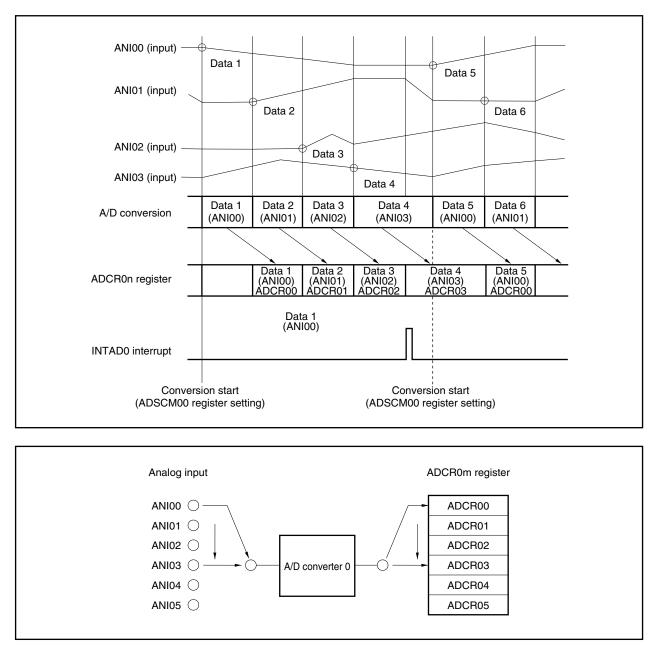

|        | 11.6.1<br>11.6.2 | A/D converter basic operation                                 |     |

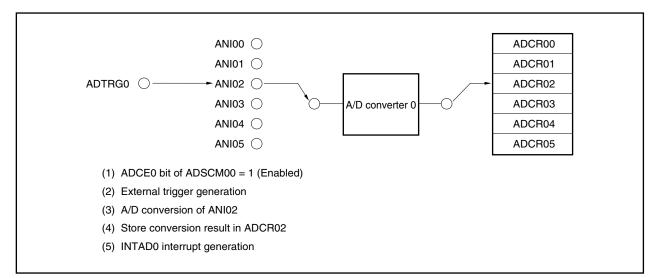

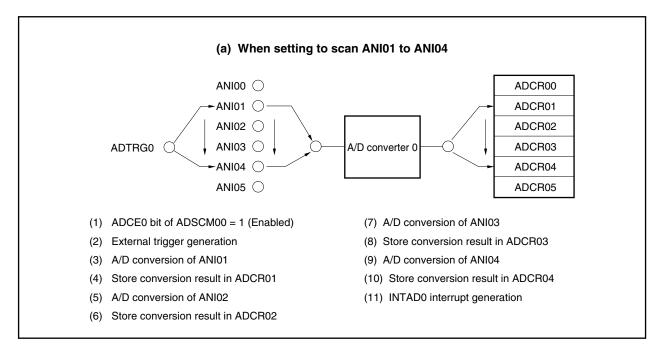

| 11.7   |                  | Operation modes and trigger modes<br>tion in A/D Trigger Mode |     |

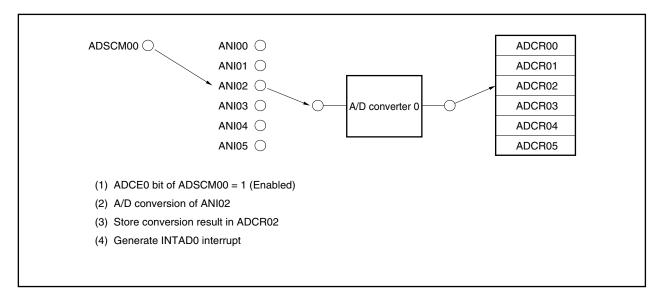

| 11.7   | 11.7.1           | Operation in select mode                                      |     |

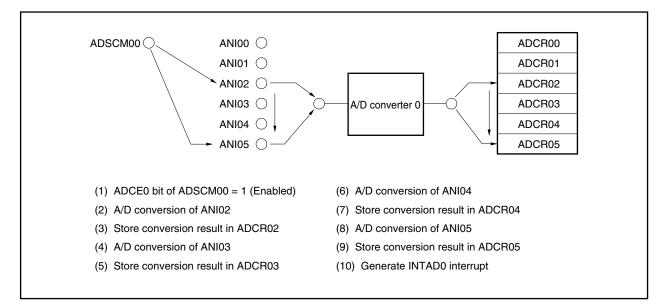

|        | 11.7.1           | Operation in scan mode                                        |     |

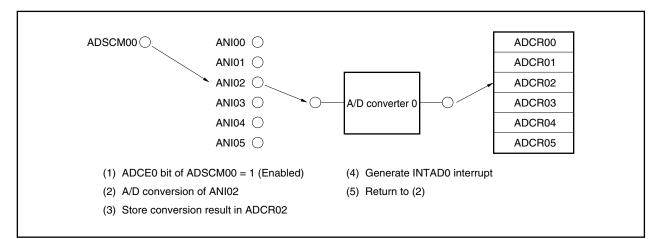

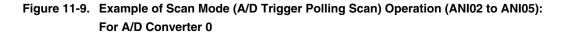

| 11.8   |                  | tion in A/D Trigger Polling Mode                              |     |

| 11.0   | 11.8.1           | Operation in select mode                                      |     |

|        | 11.8.2           | Operation in scan mode                                        |     |

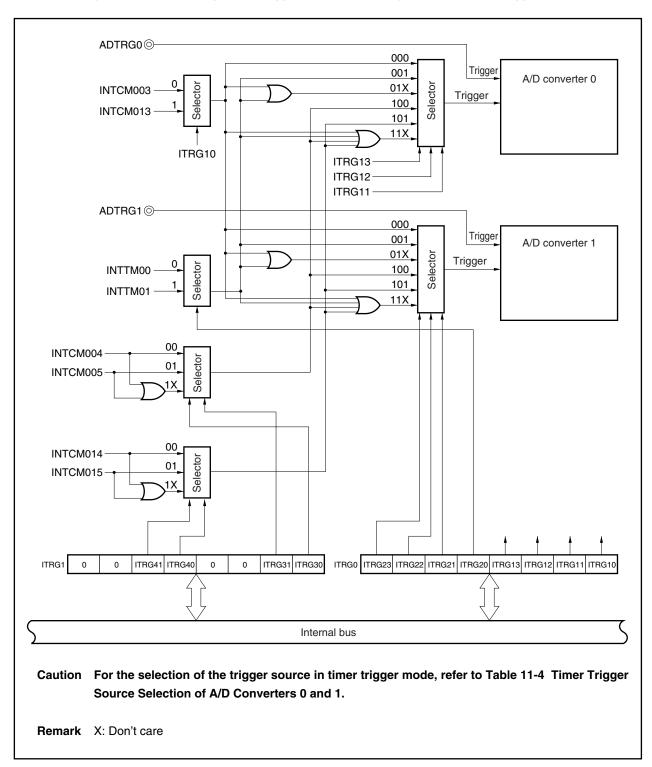

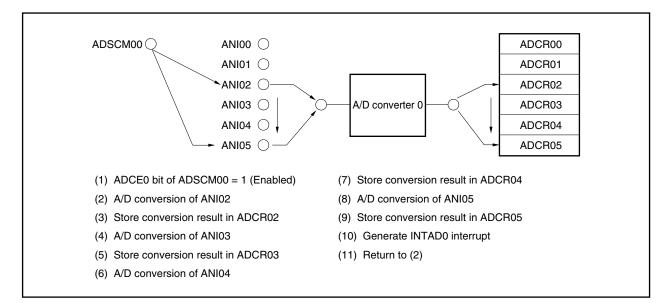

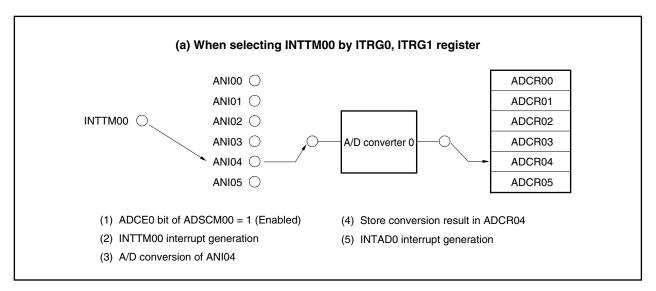

| 11.9   | -                | tion in Timer Trigger Mode                                    |     |

| 11.5   | 11.9.1           | Operation in select mode                                      |     |

|        | 11.9.2           | Operation in scan mode                                        |     |

| 11.10  | -                | tion in External Trigger Mode                                 |     |

|        | -                | Operation in select mode                                      |     |

|        |                  |                                                               |     |

|        | 11.10.2   | Operation in scan mode                                | 540 |

|--------|-----------|-------------------------------------------------------|-----|

| 11.11  | Operat    | ion Cautions                                          |     |

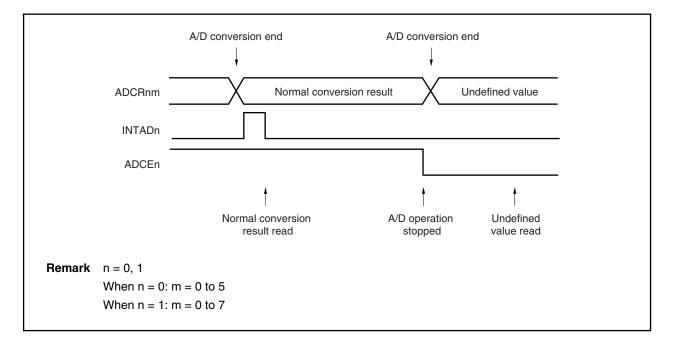

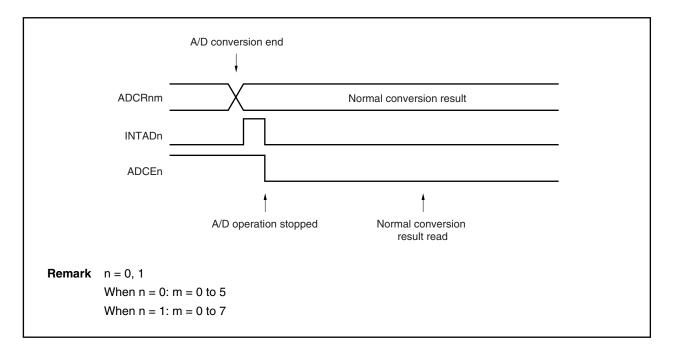

|        | 11.11.1   | Stopping A/D conversion operation                     | 541 |

|        | 11.11.2   | Trigger input during A/D conversion operation         | 541 |

|        | 11.11.3   | External or timer trigger interval                    | 541 |

|        | 11.11.4   | Operation in standby modes                            | 541 |

|        | 11.11.5   | Compare match interrupt in timer trigger mode         | 541 |

|        | 11.11.6   | Timing that makes the A/D conversion result undefined | 542 |

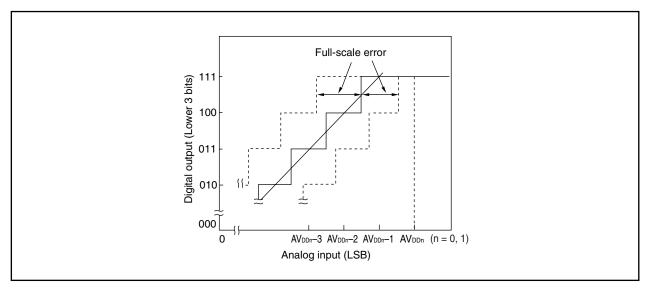

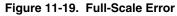

| 11.12  | How to    | Read A/D Converter Characteristics Table              |     |

| СНАРТЕ | R 12 F    | PORT FUNCTIONS                                        |     |

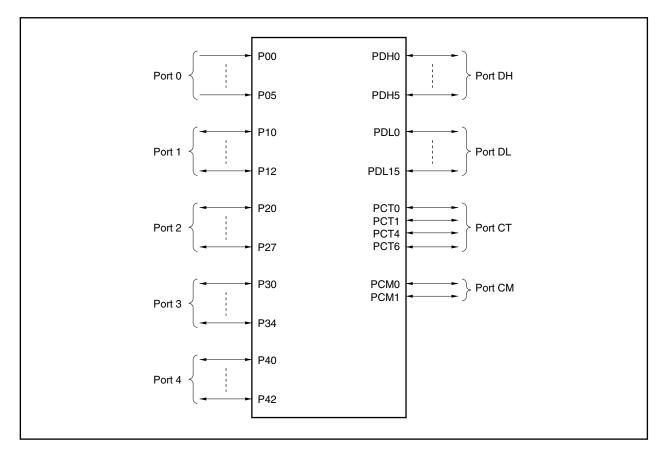

| 12.1   | Feature   | es                                                    |     |

| 12.2   |           | Configuration of Ports                                |     |

| 12.3   | Pin Fu    | nctions of Each Port                                  |     |

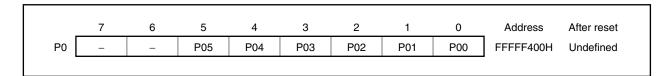

|        | 12.3.1    | Port 0                                                | 563 |

|        | 12.3.2    | Port 1                                                | 564 |

|        | 12.3.3    | Port 2                                                | 566 |

|        | 12.3.4    | Port 3                                                | 568 |

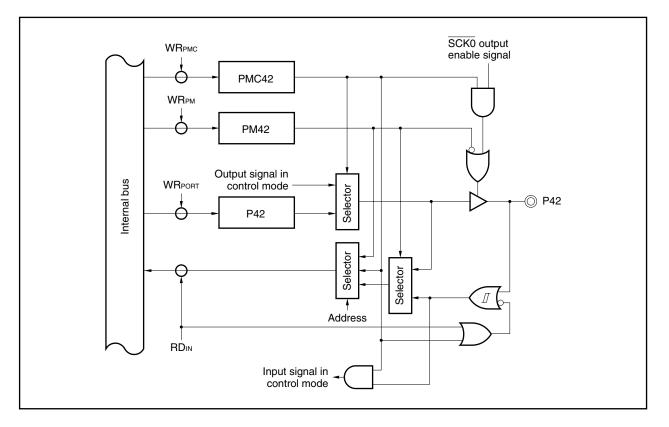

|        | 12.3.5    | Port 4                                                | 570 |

|        | 12.3.6    | Port DH                                               | 572 |

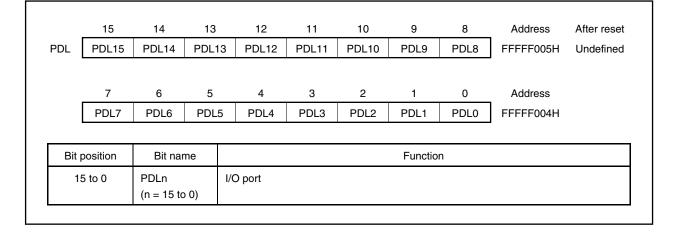

|        | 12.3.7    | Port DL                                               | 574 |

|        | 12.3.8    | Port CT                                               | 576 |

|        | 12.3.9    | Port CM                                               | 578 |

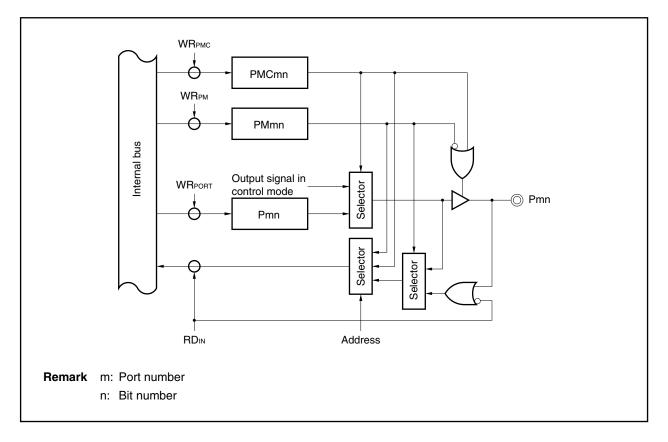

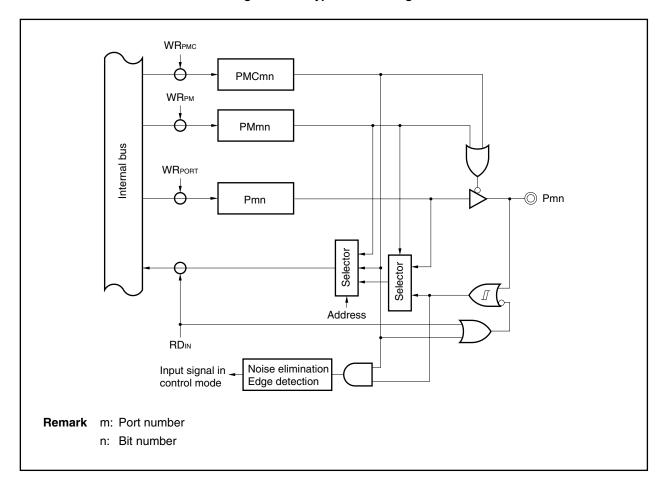

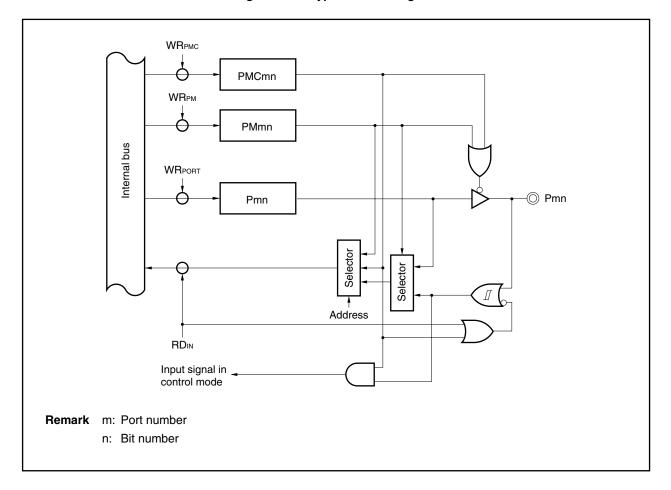

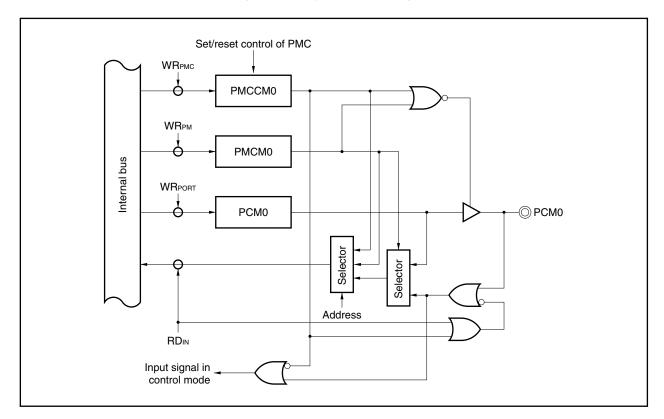

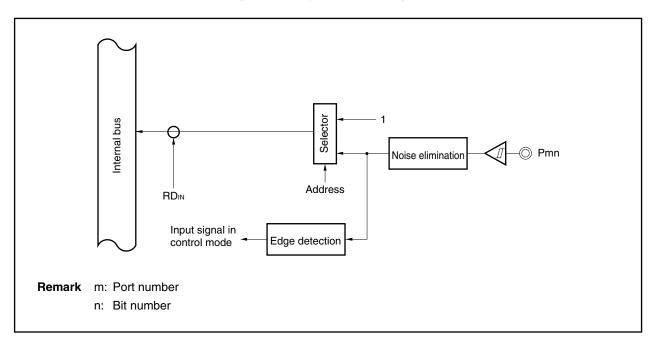

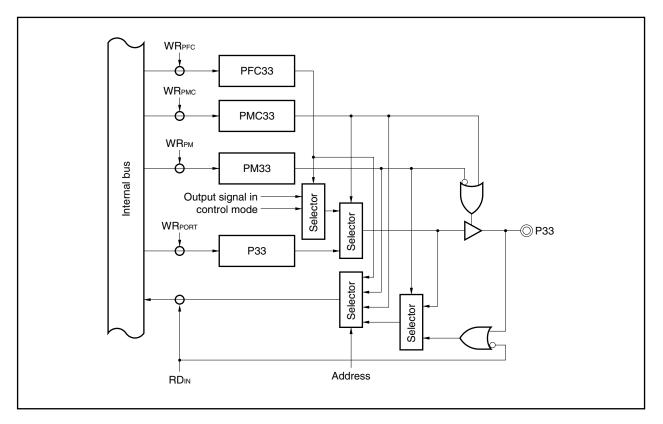

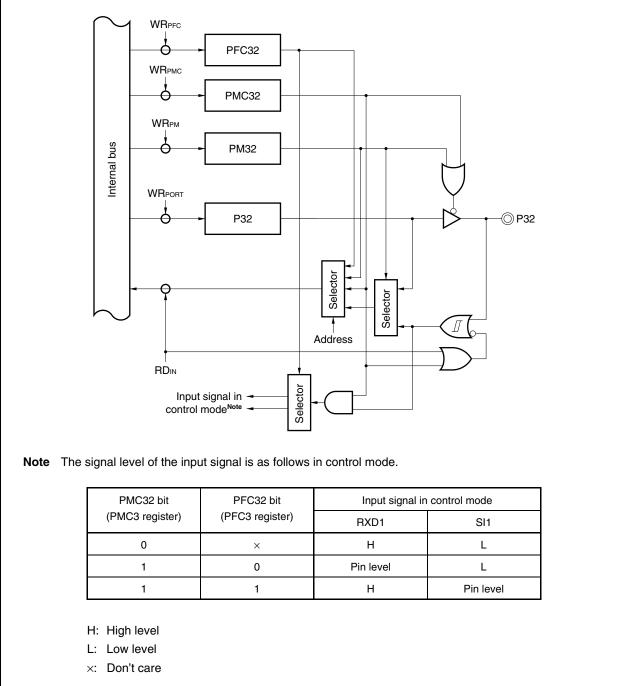

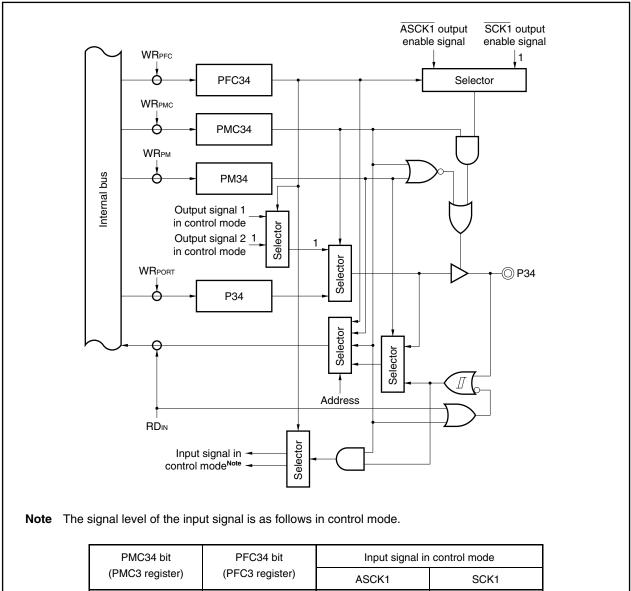

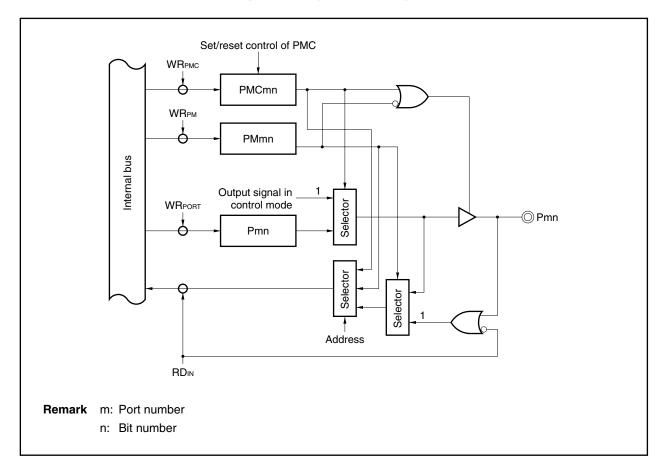

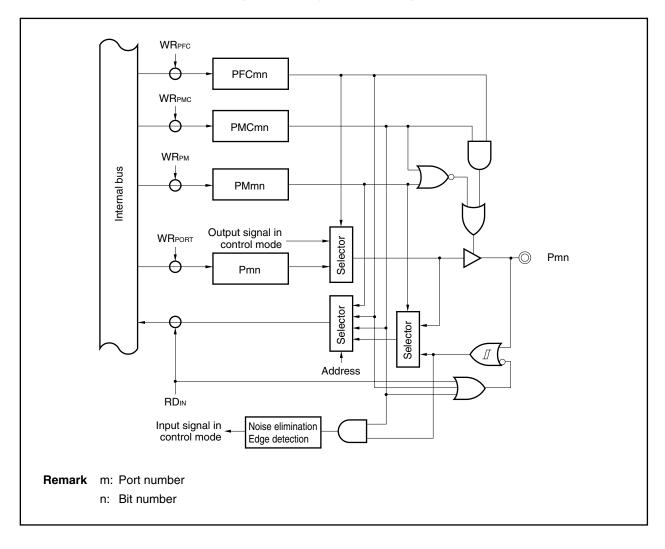

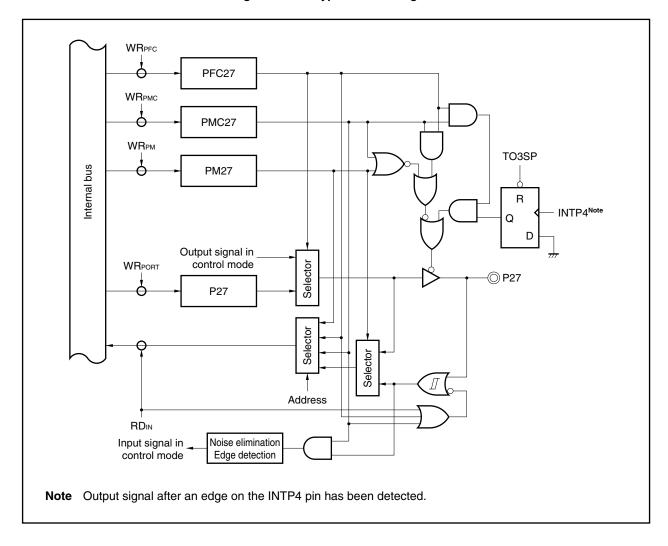

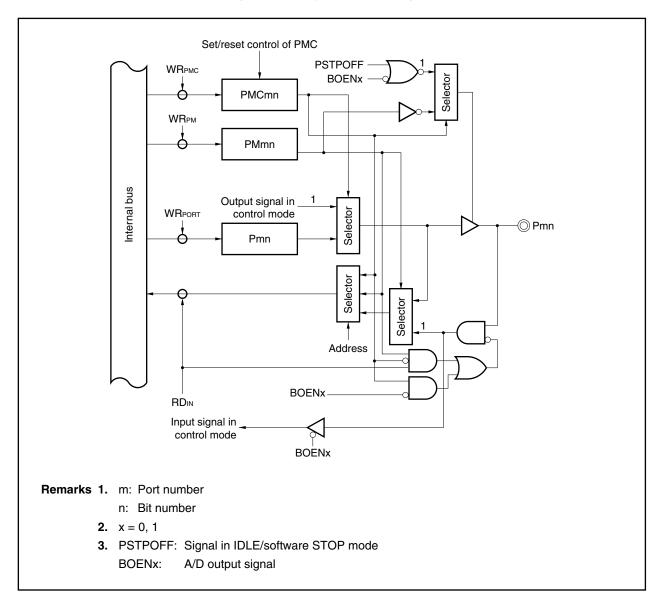

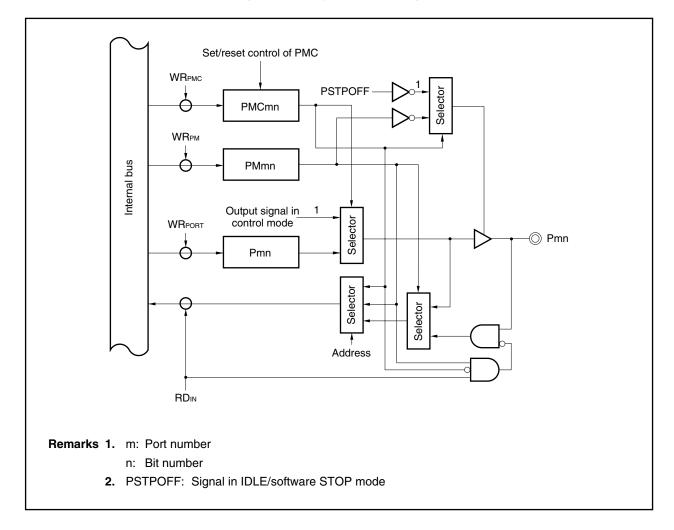

| 12.4   | Operat    | ion of Port Function                                  | 580 |

|        | 12.4.1    | Writing to I/O port                                   | 580 |

|        | 12.4.2    | Reading from I/O port                                 | 580 |

|        | 12.4.3    | Output status of alternate function in control mode   |     |

| 12.5   | Noise I   | Eliminator                                            | 581 |

|        | 12.5.1    | Interrupt pins                                        | 581 |

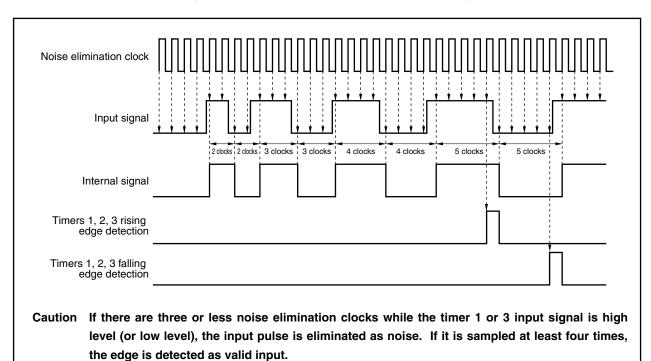

|        | 12.5.2    | Timer 10, timer 3 input pins                          | 581 |

|        | 12.5.3    | Timer 2 input pins                                    | 585 |

| 12.6   |           | IS                                                    |     |

|        | 12.6.1    | Hysteresis characteristics                            | 588 |

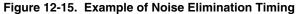

| СНАРТЕ | R 13 F    | RESET FUNCTION                                        | 589 |

| 13.1   | Feature   | es                                                    |     |

| 13.2   | Pin Fu    | nctions                                               |     |

| 13.3   | Initializ | zation                                                |     |

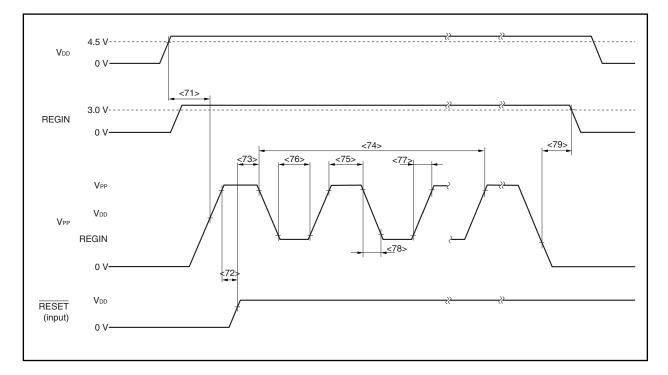

| СНАРТЕ | R 14 F    | REGULATOR                                             | 599 |

| 14.1   | Featur    | es                                                    | 599 |

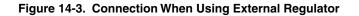

| 14.2   |           | onal Outline                                          |     |

| 14.3   |           | ction Example                                         |     |

|        |           | I Register                                            |     |

| 15.1 F | eatures                                                | 6              |

|--------|--------------------------------------------------------|----------------|

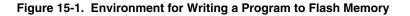

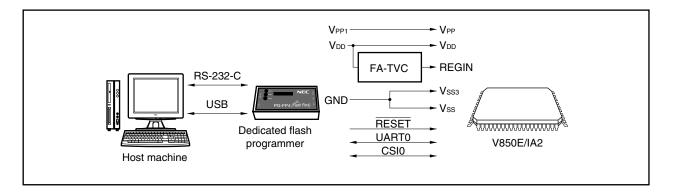

|        | /riting Using Flash Programmer                         |                |

|        | rogramming Environment                                 |                |

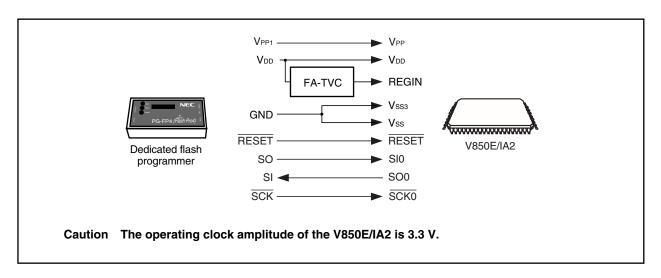

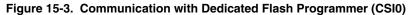

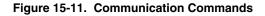

|        | communication Mode                                     |                |

|        | in Connection                                          |                |

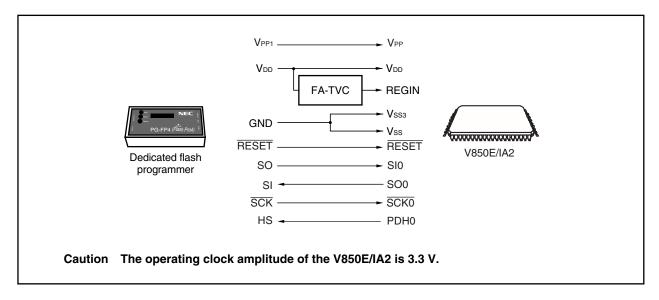

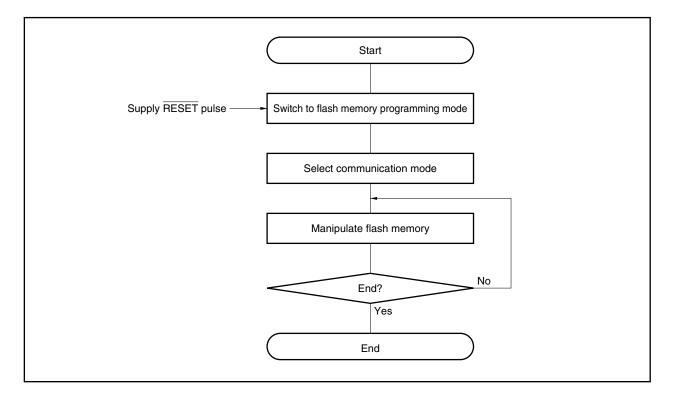

|        | 5.5.1 MODE1/VPP pin                                    |                |

|        | 5.5.2 Serial interface pin                             |                |

|        | 5.5.3 RESET pin                                        |                |

|        | 5.5.4 NMI pin                                          |                |

| 1/     | 5.5.5 MODE0, MODE1 pins                                |                |

| 1/     | 5.5.6 Port pins                                        |                |

| 1/     | 5.5.7 Other signal pins                                |                |

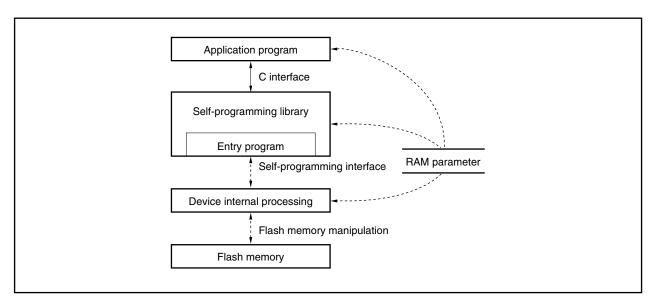

| 1/     | 5.5.8 Power supply                                     |                |

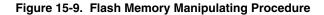

| 15.6 P | rogramming Method                                      |                |

| 1/     | 5.6.1 Flash memory control                             | 6              |

| 1/     | 5.6.2 Flash memory programming mode                    | 6              |

| 1/     | 5.6.3 Selection of communication mode                  | 6              |

| 1/     | 5.6.4 Communication commands                           | 6              |

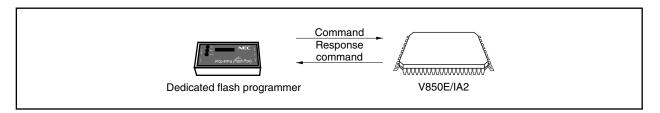

| 15.7 F | lash Memory Programming by Self-Programming            | 6 <sup>.</sup> |

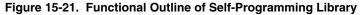

| 1/     | 5.7.1 Outline of self-programming                      | 6              |

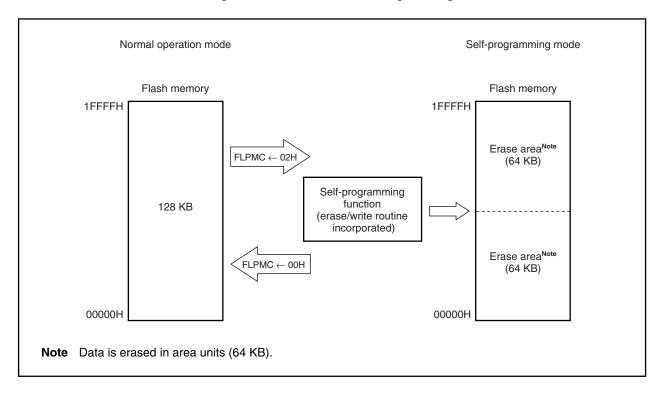

| 1/     | 5.7.2 Self-programming function                        | 6              |

| 1/     | 5.7.3 Outline of self-programming interface            | 6              |

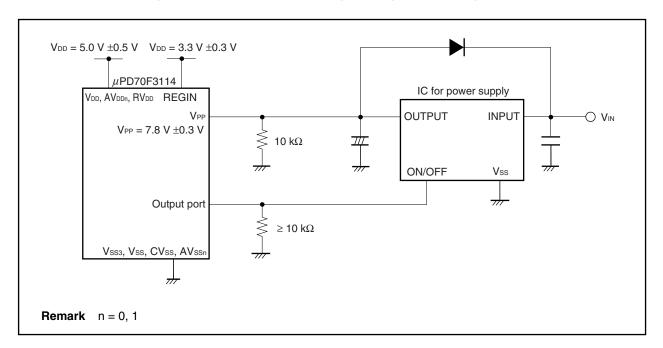

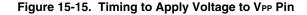

| 1/     | 5.7.4 Hardware environment                             | 6              |

| 1/     | 5.7.5 Software environment                             | 6              |

| 1/     | 5.7.6 Self-programming function number                 | 6              |

| 1/     | 5.7.7 Calling parameters                               | 6              |

| 1      | 5.7.8 Contents of RAM parameters                       | 6              |

| 1/     | 5.7.9 Errors during self-programming                   | 6              |

| 1      | 5.7.10 Flash information                               | 6              |

| 1      | 5.7.11 Area number                                     | 6              |

| 1      | 5.7.12 Flash programming mode control register (FLPMC) | 6              |

| 1      | 5.7.13 Calling device internal processing              | 6              |

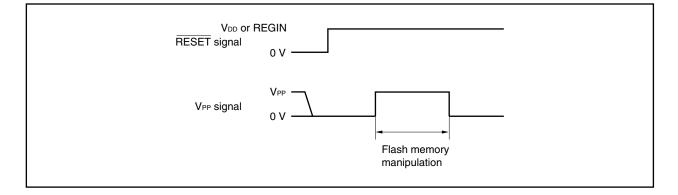

| 1      | 5.7.14 Erasing flash memory flow                       | 6              |

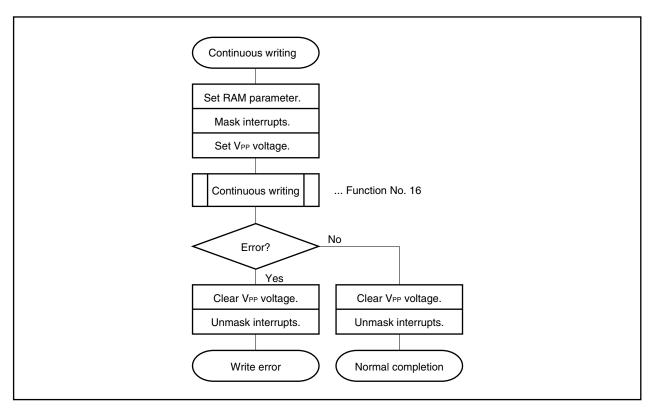

| 1      | 5.7.15 Continuous writing flow                         | 6              |

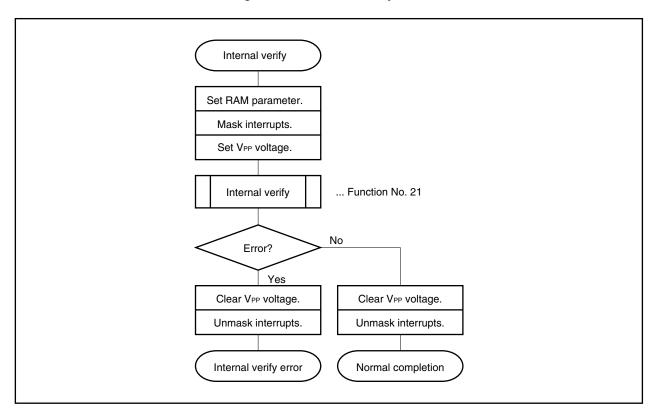

| 1      | 5.7.16 Internal verify flow                            | 6              |

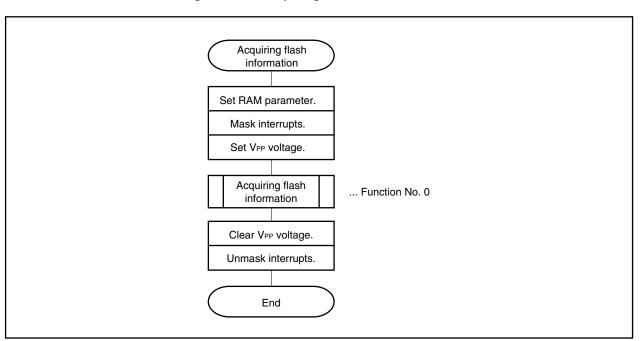

| 1      | 5.7.17 Acquiring flash information flow                | 6              |

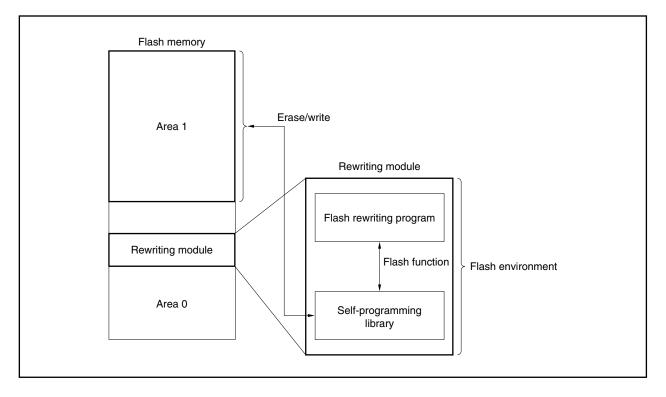

| 1      | 5.7.18 Self-programming library                        | 6              |

| 15.8 H | ow to Distinguish Flash Memory and Mask ROM Versions   | 6              |

| APTER  | 16 ELECTRICAL SPECIFICATIONS                           | 6              |

|        | ormal Operation Mode                                   |                |

| 16.1 N | •                                                      | -              |

|        | lash Memory Programming Mode                           |                |

$\star$

$\star$

$\star$

| CHAPTER 18 RECOMMENDED SOLDERING CONDITIONS | 662 |

|---------------------------------------------|-----|

| APPENDIX A NOTES ON TARGET SYSTEM DESIGN    | 664 |

| APPENDIX B REGISTER INDEX                   | 666 |

| APPENDIX C INSTRUCTION SET LIST             | 675 |

| C.1 Conventions                             | 675 |

| C.2 Instruction Set (Alphabetical Order)    |     |

| APPENDIX D REVISION HISTORY                 | 684 |

| D.1 Major Revisions in This Edition         | 684 |

| D.2 Revision History up to Previous Edition |     |

#### **CHAPTER 1 INTRODUCTION**

The V850E/IA2 is a product in NEC Electronics' V850 Series of single-chip microcontrollers. This chapter provides an overview of the V850E/IA2.

#### 1.1 Outline

The V850E/IA2 is a 32-bit single-chip microcontroller that uses high-speed operations to realize high-precision inverter control of motors. It uses the V850E1 CPU of the V850 Series and has on-chip peripheral functions such as ROM, RAM, a bus interface, a DMA controller, timers including a 3-phase sine-wave PWM timer for motors, serial interfaces, and A/D converters.

# (1) V850E1 CPU

The V850E1 CPU supports a RISC instruction set in which the instruction execution speed is increased greatly through the use of basic instructions that execute one instruction per clock, and an optimized pipeline. Moreover, it supports multiply instructions using a 32-bit hardware multiplier, saturated product-sum operation instructions, and bit manipulation instructions as optimum instructions for digital servo control applications.

Object code efficiency is increased in the C compiler by using 2-byte-length basic instructions and instructions corresponding to high-level languages, which promote a compact program.

Furthermore, since the interrupt response time, including processing by the on-chip interrupt controller, is also fast, this CPU is ideal for advanced real-time control.

#### (2) External bus interface function

A bus configuration consisting of a multiplexed address bus (22 bits) and data bus (8 bits or 16 bits selectable) suitable for compact system design is used as the external bus interface. SRAM and ROM memories can be connected.

In the DMA controller, transfer is started using software and transfers between external memories can be made concurrent with internal CPU operations or data transfers. Real-time control such as motor control or communication control can also be realized simultaneously due to high-speed, high-performance CPU instruction execution.

#### (3) On-chip flash memory ( $\mu$ PD70F3114)

The on-chip flash memory version ( $\mu$ PD70F3114), which has a quickly accessible flash memory on-chip, can shorten system development time since it is possible to rewrite a program with the V850E/IA2 mounted in an application system. Moreover, it can greatly improve maintainability after a system is shipped.

#### (4) Complete middleware, development environment

The V850E/IA2 can execute JPEG, JBIG, MH/MR/MMR and other middleware at high speeds. Moreover, since middleware for realizing speech recognition, voice synthesis, and other processing also is provided, multimedia systems can be realized easily.

A development environment that integrates an optimized C compiler, debugger, in-circuit emulator, simulator, and system performance analyzer is also provided.

Table 1-1 lists the differences between the V850E/IA1 and V850E/IA2. Table 1-2 lists the differences between the V850E/IA1 and V850E/IA2 register setting values.

| Item                        |                  | V850E/IA1                                                                      | V850E/IA2                                                                      |

|-----------------------------|------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Maximum operating frequency |                  | 50 MHz <sup>Note</sup>                                                         | 40 MHz                                                                         |

| Internal ROM Mask ROM       |                  | μPD703116: 256 KB                                                              | μPD703114: 128 KB                                                              |

|                             | Flash memory     | μPD70F3116: 256 KB                                                             | μPD70F3114: 128 KB                                                             |

| Internal RAM                |                  | 10 KB                                                                          | 6 KB                                                                           |

| Timer                       | Timer 00, 01     | Provided                                                                       | Buffer register, compare register, and compare match interrupt added           |

|                             | Timer 10, 11     | Provided                                                                       | Timer 10: Provided, Timer 11: Not provided                                     |

|                             | Timer 20, 21     | Provided                                                                       | Provided                                                                       |

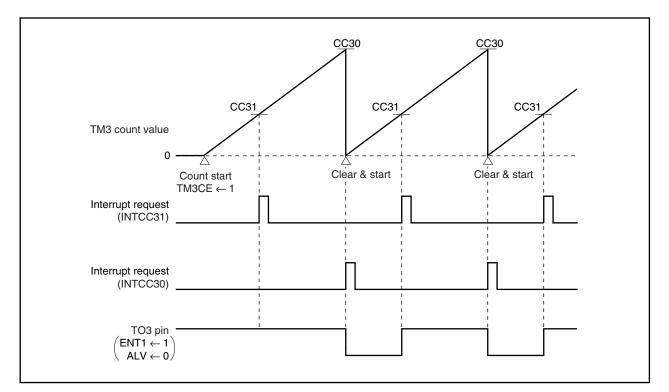

|                             | Timer 3          | Provided                                                                       | TO3 output buffer off function added by INTP4 input                            |

|                             | Timer 4          | Provided                                                                       | Provided                                                                       |

| Serial interface            | UART0            | Provided                                                                       | Provided                                                                       |

|                             | UART1            | Provided                                                                       | Provided (pins multiplexed with CSI1)                                          |

| UART2                       |                  | Provided                                                                       | Not provided                                                                   |

| CSIO                        |                  | Provided                                                                       | Provided                                                                       |

| CSI1                        |                  | Provided                                                                       | Provided (pins multiplexed with UART1)                                         |

|                             | FCAN             | Provided                                                                       | Not provided                                                                   |

| Debug support function      | NBD              | Provided                                                                       | Not provided                                                                   |

| A/D converter               | Analog input     | Total of two circuits: 16 ch<br>A/D converter 0: 8 ch<br>A/D converter 1: 8 ch | Total of two circuits: 14 ch<br>A/D converter 0: 6 ch<br>A/D converter 1: 8 ch |

|                             | AVDD, AVREF pins | Independent pins                                                               | Alternate-function pins                                                        |

| Supply voltage              |                  | V <sub>DD3</sub> = 3.3 V ±0.3 V<br>V <sub>DD5</sub> = 5.0 V ±0.5 V             | $V_{DD} = RV_{DD} = 5.0 \text{ V} \pm 0.5 \text{ V}$<br>Internal regulator     |

| Package                     |                  | 144-pin plastic LQFP                                                           | 100-pin plastic LQFP<br>100-pin plastic QFP                                    |

#### Table 1-1. Differences Between V850E/IA1 and V850E/IA2

\* Note The maximum operating frequency of the in-circuit emulator is 40 MHz. A frequency of 50 MHz can be supported by upgrading the in-circuit emulator, so contact an NEC Electronics sales representative or distributor.

**Remark** For details, refer to the user's manual of each product.

| Register Name                                    | V850E/IA1  | V850E/IA2               |

|--------------------------------------------------|------------|-------------------------|

| System wait control register (VSWC)              | 12H        | 02H                     |

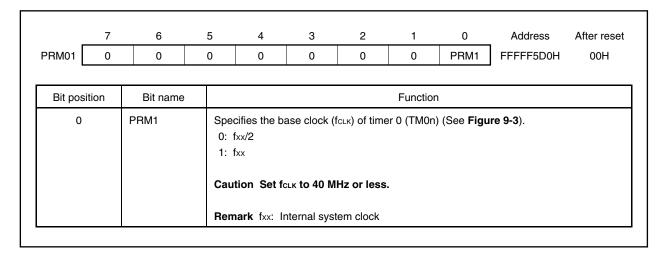

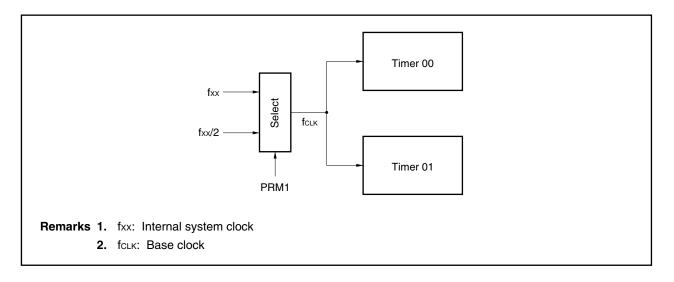

| Timer 1/timer 2 clock selection register (PRM02) | 00H or 01H | 01H (initial value 00H) |

# Table 1-2. Differences Between V850E/IA1 and V850E/IA2 Register Setting Values

Remark For details, refer to the user's manual of each product.

# 1.2 Features

★ O Number of instructions 80

O Minimum instruction execution time

25 ns (@ internal 40 MHz operation)

O General-purpose registers 32 bits  $\times$  32 registers

| O Instruction set        | V850E1 (NB85E) CPU<br>Signed multiplication (32 bits $\times$ 32 bits $\rightarrow$ 64 bits): 1 or 2 clocks<br>Saturated operation instructions (with overflow/underflow detection function)<br>32-bit shift instruction: 1 clock<br>Bit manipulation instructions<br>Long/short format load/store instructions<br>Signed load instructions |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O Memory space           | 4 MB linear address space (shared by program and data)<br>Memory block division function: 2 MB/block<br>Programmable wait function<br>Idle state insertion function                                                                                                                                                                         |

| O External bus interface | 16-bit data bus (address/data multiplexed)<br>16-/8-bit bus sizing function<br>External wait function                                                                                                                                                                                                                                       |

### O Internal memory

| Part Number | Internal ROM          | Internal RAM |

|-------------|-----------------------|--------------|

| μPD703114   | 128 KB (mask ROM)     | 6 KB         |

| μPD70F3114  | 128 KB (flash memory) | 6 KB         |

O Interrupts/exceptions External interrupts: 16 (including NMI) Internal interrupts: 42 sources Exceptions: 1 source 8 levels of priority can be specified

| O DMA controller         | 4-channel configuration<br>Transfer unit:<br>Maximum transfer count:<br>Transfer type:<br>Transfer modes:<br>Transfer subjects:<br>Transfer requests:<br>Next address setting fund | 2-cycle transfer<br>Single transfer, single-step transfer, block transfer<br>Memory $\leftrightarrow$ Memory, Memory $\leftrightarrow$ I/O, I/O $\leftrightarrow$ I/O<br>On-chip peripheral I/O, software                                                               |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O I/O lines              | Input ports: 6<br>I/O ports: 47                                                                                                                                                    |                                                                                                                                                                                                                                                                         |

| O Timer/counter function | 16-bit up/down counter/ti<br>General-purpose 16-bit t                                                                                                                              | sine wave PWM inverter control: 2 channels<br>imer for 2-phase encoder input: 1 channel<br>imer/counter: 2 channels<br>imer/event counter: 1 channel<br>hannel                                                                                                          |

| O Serial interface       | Clocked serial interface (                                                                                                                                                         | vo channels are used for both CSI and UART and therefore                                                                                                                                                                                                                |

| O A/D converter          | 10-bit resolution A/D con                                                                                                                                                          | werter: 6 channels + 8 channels (2 units)                                                                                                                                                                                                                               |

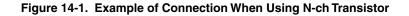

| O Regulator              | not necessary. A 5 V sir<br>N-ch transistor (2SD195                                                                                                                                | e for the internal CPU and one for the peripheral interface, are<br>ngle-power-supply system can be configured by connecting an<br>50 (VL standard product, surface mount type) or 2SD1581<br>commended). If a 3.3 V power supply is available, it can be<br>REGIN pin. |

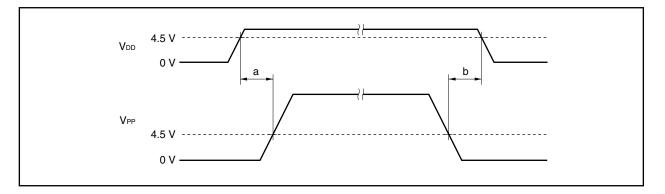

| O Clock generator        | Multiplication function (×<br>Divide-by-2 function usin                                                                                                                            | 1, ×2.5, ×5, ×10) using PLL clock synthesizer $_{\rm N}$ g external clock input                                                                                                                                                                                         |

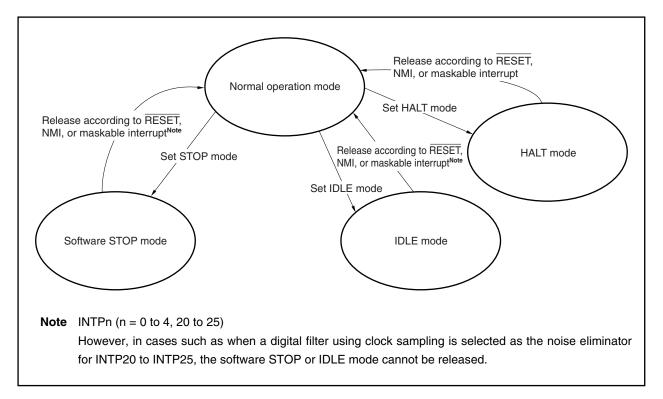

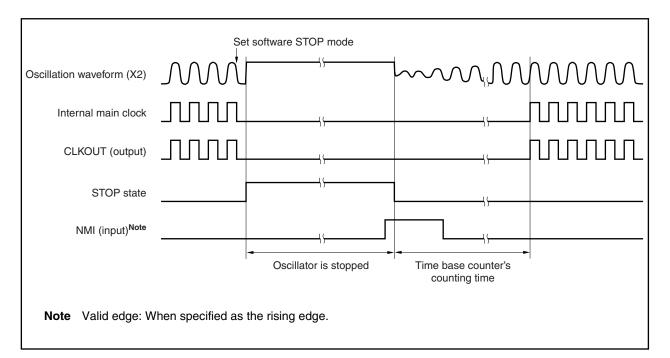

| O Power-saving function  | HALT, IDLE, and softwar                                                                                                                                                            | re STOP modes                                                                                                                                                                                                                                                           |

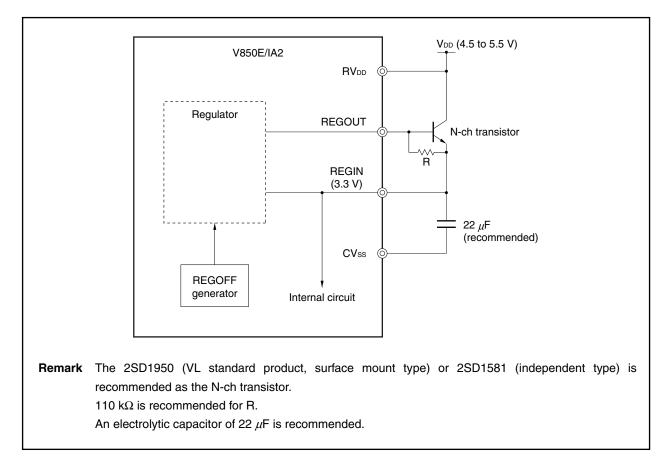

| O Package                | 100-pin plastic LQFP (fin<br>100-pin plastic QFP (14 :                                                                                                                             |                                                                                                                                                                                                                                                                         |

| O CMOS technology        | Fully static circuits                                                                                                                                                              |                                                                                                                                                                                                                                                                         |

# 1.3 Applications

• *μ*PD703114, 70F3114: Consumer equipment (inverter air conditioners) Industrial equipment (motor control, general-purpose inverters) • μPD703114(A), 70F3114(A): Automobile applications (electrical power steering)

# 1.4 Ordering Information

|   | Part Number              | Package                                           | Quality Grade |

|---|--------------------------|---------------------------------------------------|---------------|

|   | μPD703114GC-×××-8EU      | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Standard      |

| * | μPD703114GC-×××-8EU-A    | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Standard      |

|   | μPD703114GC(A)-×××-8EU   | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Special       |

| * | μPD703114GC(A)-×××-8EU-A | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Special       |

|   | μPD703114GF-×××-3BA      | 100-pin plastic QFP (14 $	imes$ 20)               | Standard      |

| * | μPD703114GF-×××-3BA-A    | 100-pin plastic QFP (14 $	imes$ 20)               | Standard      |

|   | μPD70F3114GC-8EU         | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Standard      |

| * | μPD70F3114GC-8EU-A       | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Standard      |

|   | μPD70F3114GC(A)-8EU      | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Special       |

| * | μPD70F3114GC(A)-8EU-A    | 100-pin plastic LQFP (fine pitch) (14 $	imes$ 14) | Special       |

|   | μPD70F3114GF-3BA         | 100-pin plastic QFP (14 $	imes$ 20)               | Standard      |

| * | μPD70F3114GF-3BA-A       | 100-pin plastic QFP (14 $	imes$ 20)               | Standard      |

Remarks 1. XXX indicates ROM code suffix.

\*

2. Products with -A at the end of the part number are lead-free products.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Electronics Corporation to know the specification of the quality grade on the device and its recommended applications.

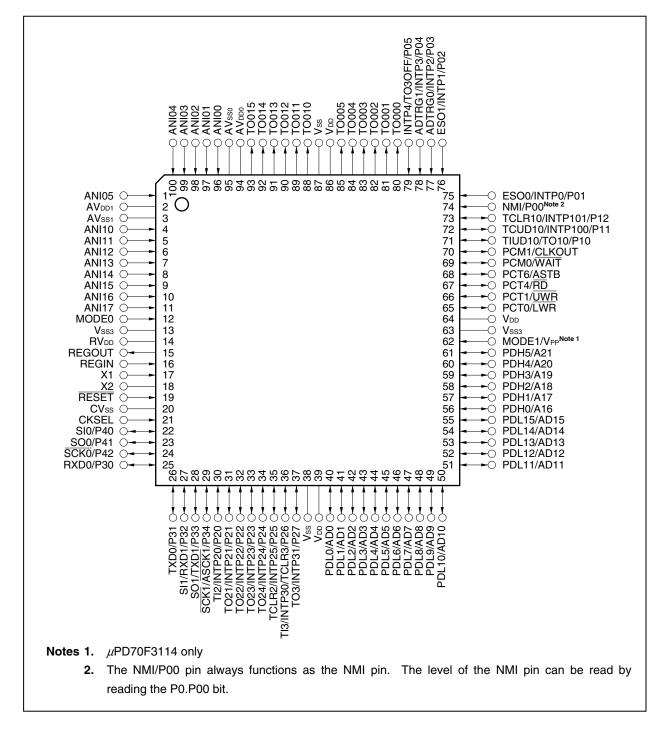

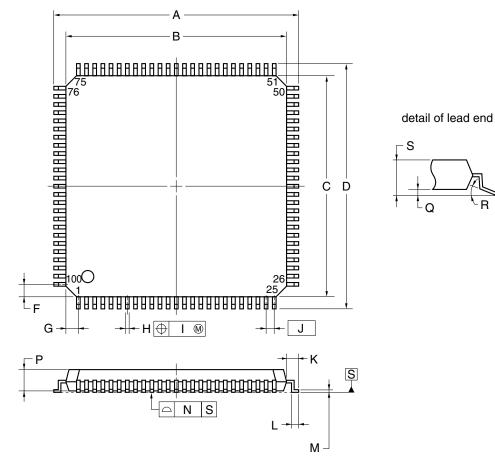

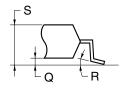

# 1.5 Pin Configuration (Top View)

• 100-pin plastic LQFP (fine pitch) (14 × 14)

|   | μPD703114GC-×××-8EU    | μPD70F3114GC-8EU    |

|---|------------------------|---------------------|

| * | μPD703114GC-×××-8EU-A  | μPD70F3114GC-8EU-A  |

|   | μPD703114GC(A)-×××-8EU | μPD70F3114GC(A)-8EU |

|   |                        |                     |

μPD703114GC(A)-×××-8EU-A μPD70F3114GC(A)-8EU-A

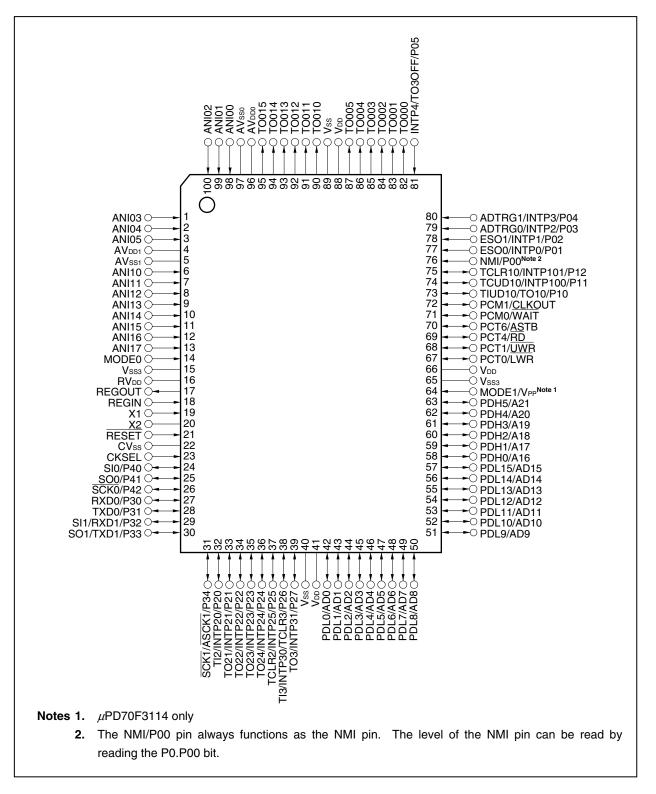

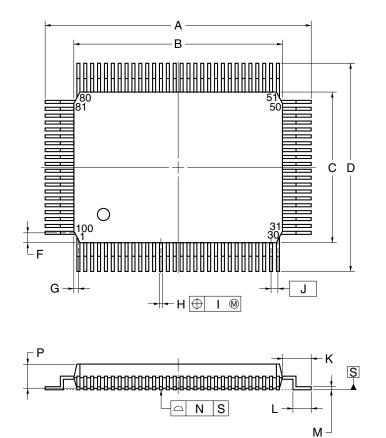

# • 100-pin plastic QFP (14 × 20)

\*

| μPD703114GF-×××-3BA   | μPD70F3114GF-3BA   |

|-----------------------|--------------------|

| μPD703114GF-×××-3BA-A | μPD70F3114GF-3BA-A |

# **Pin Identification**

| A16 to A21:       | Address bus                           | PDH0 to PDH5:      | Port DH                   |

|-------------------|---------------------------------------|--------------------|---------------------------|

| AD0 to AD15:      | Address/data bus                      | PDL0 to PLD15:     | Port DL                   |

| ADTRG0, ADTRG1:   | A/D trigger input                     | RD:                | Read strobe               |

| ANI00 to ANI05,   |                                       | RESET:             | Reset                     |

| ANI10 to ANI17:   | Analog input                          | REGIN:             | Regulator input           |

| ASCK1:            | Asynchronous serial clock             | REGOUT:            | Regulator output          |

| ASTB:             | Address strobe                        | RVDD:              | Regulator power supply    |

| AVDD0, AVDD1:     | Analog power supply                   | RXD0, RXD1:        | Receive data              |

| AVsso, AVss1:     | Analog ground                         | SCK0, SCK1:        | Serial clock              |

| CKSEL:            | Clock generator operating mode select | SI0, SI1:          | Serial input              |

| CLKOUT:           | Clock output                          | SO0, SO1:          | Serial output             |

| CVss:             | Clock generator ground                | TCLR10, TCLR2,     |                           |

| ESO0, ESO1:       | Emergency shut off                    | TCLR3:             | Timer clear               |

| INTP0 to INTP4,   |                                       | TCUD10:            | Timer control pulse input |

| INTP100, INTP101, |                                       | TI2, TI3:          | Timer input               |

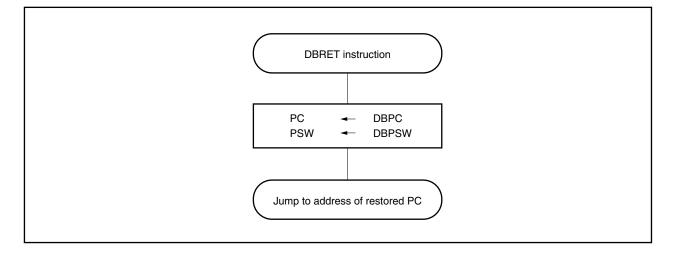

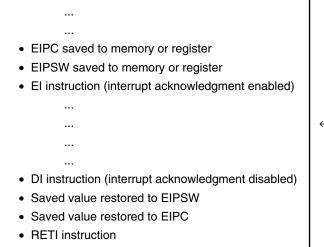

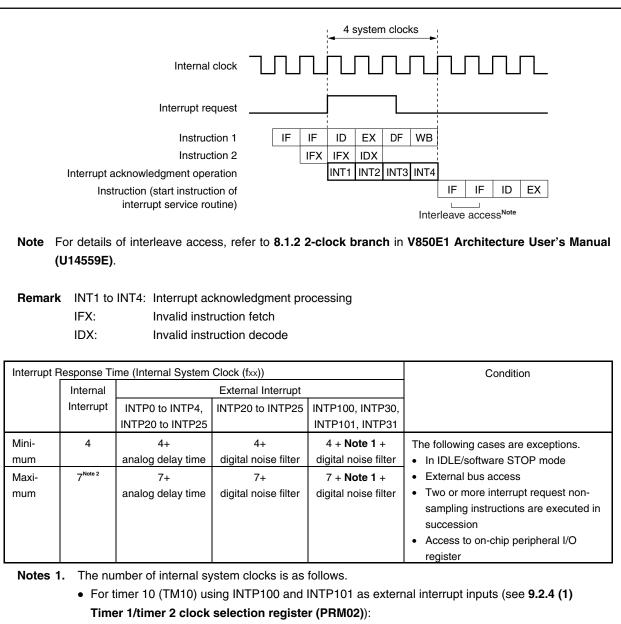

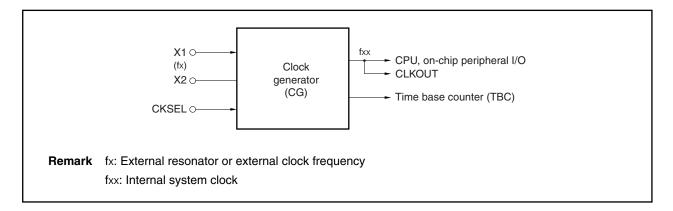

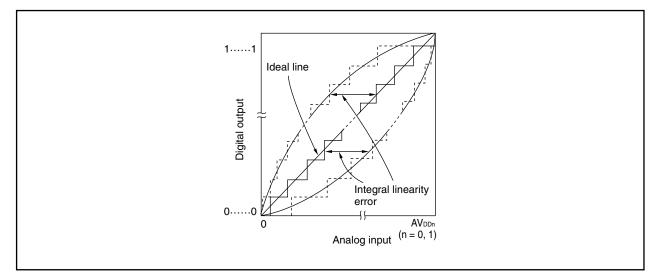

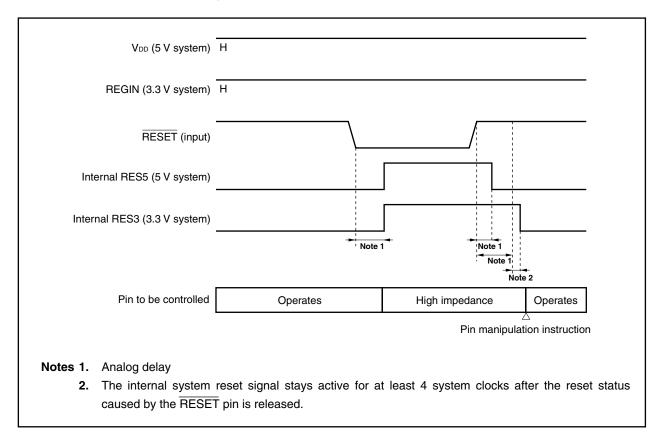

| INTP20 to INTP25, |                                       | TIUD10:            | Timer count pulse input   |