# 256K x 16 Static RAM

#### **Features**

- · Fast access times: 10, 12 ns

- Fast OE access times: 5, 6, and 7 ns

- Single +3.3V ±0.3V power supply

- Fully static—no clock or timing strobes necessary

- All inputs and outputs are TTL-compatible

- Three state outputs

- · Center power and ground pins for greater noise immunity

- Easy memory expansion with CE and OE options

- Automatic CE power-down

- · High-performance, low power consumption, CMOS double-poly, double-metal process

- · Packaged in 44-pin, 400-mil SOJ and 44-pin, 400-mil **TSOP**

#### **Functional Description**

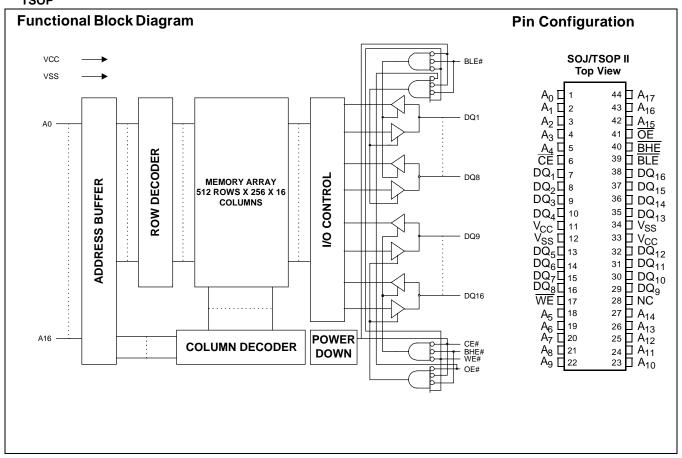

The CY7C1049AV33\GVT73512A8 is organized as a 262,144 x 16 SRAM using a four-transistor memory cell with a high-performance, silicon gate, low-power CMOS process. Cypress SRAMs are fabricated using double-layer polysilicon, double-layer metal technology.

This device offers center power and ground pins for improved performance and noise immunity. Static design eliminates the need for external clocks or timing strobes. For increased system flexibility and eliminating bus contention problems, this device offers Chip Enable (CE), separate Byte Enable controls (BLE and BHE) and Output Enable (OE) with this organization.

The device offers a low-power standby mode when chip is not selected. This allows system designers to meet low standby power requirements.

#### **Selection Guide**

|                                   |                                |  | CY7C1049AV33-10/<br>GVT73512A8-10 | CY7C1049AV33-12/<br>GVT73512A8-12 |

|-----------------------------------|--------------------------------|--|-----------------------------------|-----------------------------------|

| Maximum Access Time (ns)          |                                |  | 10                                | 12                                |

| Maximum Operating Current (mA)    | Maximum Operating Current (mA) |  |                                   | 210                               |

| Maximum CMOS Standby Current (mA) | Com'l/Ind'l                    |  | 10                                | 10                                |

|                                   | Com'l L                        |  | 3.0                               | 3.0                               |

#### **Truth Table**

| Mode                                                 | CE | WE | OE | BLE | BHE | DQ <sub>1</sub> -D <sub>8</sub> | DQ <sub>9</sub> -D <sub>16</sub> | POWER   |

|------------------------------------------------------|----|----|----|-----|-----|---------------------------------|----------------------------------|---------|

| Low Byte Read (DQ <sub>1</sub> -DQ <sub>8</sub> )    | L  | Н  | L  | L   | Н   | Q                               | High-Z                           | Active  |

| High Byte Read (DQ <sub>9</sub> –DQ <sub>16</sub> )  | L  | Н  | L  | Н   | L   | High-Z                          | Q                                | Active  |

| Word Read (DQ <sub>1</sub> -DQ <sub>16</sub> )       | L  | Н  | L  | L   | L   | Q                               | Q                                | Active  |

| Low Byte Write (DQ <sub>1</sub> -DQ <sub>8</sub> )   | L  | L  | X  | L   | Н   | D                               | High-Z                           | Active  |

| High Byte Write (DQ <sub>9</sub> -DQ <sub>16</sub> ) | L  | L  | Х  | Н   | L   | High-Z                          | D                                | Active  |

| Word Write (DQ <sub>1</sub> –DQ <sub>16</sub> )      | L  | L  | Х  | L   | L   | D                               | D                                | Active  |

| Output Disable                                       | L  | X  | X  | Н   | Н   | High-Z                          | High-Z                           | Active  |

|                                                      | L  | Н  | Н  | Х   | Х   | High-Z                          | High-Z                           | Active  |

| Standby                                              | Н  | X  | Х  | X   | X   | High-Z                          | High-Z                           | Standby |

## **Pin Descriptions**

| SOJ & TSOP<br>Pin Numbers                                         | Pin Name                          | Туре             | Description                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------|-----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4, 5, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 42, 43, 44 | A <sub>0</sub> -A <sub>17</sub>   | Input            | Addresses Inputs: These inputs determine which cell is addressed.                                                                                                                                                                                                                                                                |

| 17                                                                | WE                                | Input            | Write Enable: This input determines if the cycle is a READ or WRITE cycle. WE is LOW for a WRITE cycle and HIGH for a READ cycle.                                                                                                                                                                                                |

| 6                                                                 | CE                                | Input            | Chip Enable: This active LOW input is used to enable the device. When $\overline{\text{CE}}$ is LOW, the chip is selected. When $\overline{\text{CE}}$ is HIGH, the chip is disabled and automatically goes into standby power mode.                                                                                             |

| 39, 40                                                            | BLE, BHE                          | Input            | Byte Enable: These active LOW inputs allow individual bytes to be written or read. When $\overline{BLE}$ is LOW, the data is written to or read from the lower byte (DQ <sub>1</sub> –DQ <sub>8</sub> ). When $\overline{BHE}$ is LOW, the data is written to or read from the higher byte (DQ <sub>9</sub> –DQ <sub>16</sub> ). |

| 41                                                                | ŌĒ                                | Input            | Output Enable: This active LOW input enables the output drivers.                                                                                                                                                                                                                                                                 |

| 7, 8, 9, 10, 13, 14,<br>15, 16, 29, 30, 31, 32,<br>35, 36, 37, 38 | DQ <sub>1</sub> -DQ <sub>16</sub> | Input/<br>Output | SRAM Data I/O: Data inputs and data outputs. Lower byte is $\rm DQ_{1}-\rm DQ_{8}$ and upper byte is $\rm DQ_{9}-\rm DQ_{16}.$                                                                                                                                                                                                   |

| 11, 33                                                            | V <sub>CC</sub>                   | Supply           | Power Supply: 3.3V ±0.3V%.                                                                                                                                                                                                                                                                                                       |

| 12, 34                                                            | V <sub>SS</sub>                   | Supply           | Ground.                                                                                                                                                                                                                                                                                                                          |

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> . | –0.5V to +4.6V                |

|-----------------------------------------------------------------|-------------------------------|

| V <sub>IN</sub>                                                 | 0.5V to V <sub>CC</sub> +0.5V |

| Storage Temperature (plastic)                                   | 55°C to +125°                 |

| Junction Temperature                                            | +125°                         |

| AI - 4 |  |

|--------|--|

|        |  |

|        |  |

<sup>1.</sup>  $T_A$  is the "Instant On" case temperature.

| Power Dissipation1.0             | )W |

|----------------------------------|----|

| Short Circuit Output Current50 r | nΑ |

## **Operating Range**

| Range      | Ambient<br>Temperature <sup>[1]</sup> | v <sub>cc</sub> |

|------------|---------------------------------------|-----------------|

| Commercial | 0°C to +70°C                          | $3.3V\pm0.3V$   |

| Industrial | –40°C to +85°C                        |                 |

### **Electrical Characteristics** Over the Operating Range

| Parameter       | Description                                    | Conditions                                                  | Min. | Max.                 | Unit |

|-----------------|------------------------------------------------|-------------------------------------------------------------|------|----------------------|------|

| V <sub>IH</sub> | Input High (Logic 1) Voltage <sup>[2, 3]</sup> |                                                             | 2.2  | V <sub>CC</sub> +0.5 | V    |

| V <sub>II</sub> | Input Low (Logic 0) Voltage <sup>[2, 3]</sup>  |                                                             | -0.5 | 0.8                  | V    |

| IL <sub>I</sub> | Input Leakage Current                          | $0V \le V_{IN} \le V_{CC}$                                  | -5   | 5                    | μΑ   |

| ILO             | Output Leakage Current                         | Output(s) disabled, 0V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> | -5   | 5                    | μΑ   |

| V <sub>OH</sub> | Output High Voltage <sup>[2]</sup>             | $I_{OH} = -4.0 \text{ mA}$                                  | 2.4  |                      | V    |

| V <sub>OL</sub> | Output Low Voltage <sup>[2]</sup>              | I <sub>OL</sub> = 8.0 mA                                    |      | 0.4                  | V    |

| V <sub>CC</sub> | Supply Voltage <sup>[2]</sup>                  |                                                             | 3.0  | 3.6                  | V    |

| Parameter        | Description                          | Conditions                                                                                              | Power | Тур. | -10 | -12 | Unit |

|------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-----|-----|------|

| I <sub>CC</sub>  | Power Supply                         | Device selected; $\overline{CE} \le V_{IL}$ ; $V_{CC} = Max.$ ;                                         | std.  | 90   | 240 | 210 | mA   |

|                  | Current: Operating <sup>[4, 5]</sup> | f = f <sub>MAX</sub> ; outputs open                                                                     | low   |      | 240 | 210 |      |

| I <sub>SB1</sub> | TTL Standby <sup>[5]</sup>           | $\overline{CE} \ge V_{IH}$ ; $V_{CC} = Max.$ ; $f = f_{MAX}$                                            | std.  | 25   | 70  | 60  | mA   |

|                  |                                      |                                                                                                         | low   |      | 70  | 60  |      |

| I <sub>SB2</sub> | CMOS Standby <sup>[5]</sup>          | $\overline{\text{CE1}} \ge V_{\text{CC}} - 0.2; V_{\text{CC}} = \text{Max.};$                           | std.  | 0.1  | 10  | 10  | mA   |

|                  |                                      | all other inputs $\leq$ V <sub>SS</sub> + 0.2 or $\geq$ V <sub>CC</sub> - 0.2; all inputs static; f = 0 | low   |      | 3.0 | 3.0 |      |

### Capacitance<sup>[6]</sup>

| Parameter        | Description                   | Test Conditions                    | Max. | Unit |

|------------------|-------------------------------|------------------------------------|------|------|

| C <sub>I</sub>   | Input Capacitance             | $T_A = 25^{\circ}C$ , $f = 1$ MHz, | 6    | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance (DQ) | V <sub>CC</sub> = 3.3V             | 8    | pF   |

- 2. All voltages referenced to  $V_{\rm SS}$  (GND).

- Overshoot:  $V_{IH} \le +6.0V$  for  $t \le t_{RC}$  /2. Undershoot:  $V_{IL} \le -2.0V$  for  $t \le t_{RC}$  /2  $I_{CC}$  is given with no output current.  $I_{CC}$  increases with greater output loading and faster cycle times. Typical values are measured at 3.3V, 25°C, and 20 ns cycle time. This parameter is sampled.

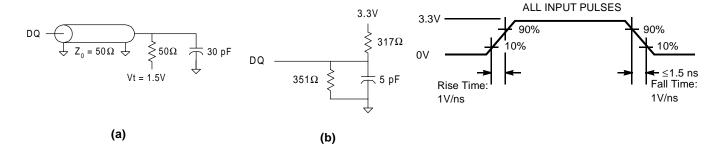

#### **AC Test Loads and Waveforms**

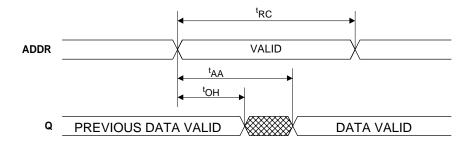

# Switching Characteristics<sup>[5]</sup> Over the Operating Range

|                   |                                                       |      | AV33-10/<br>56A16-10 | 7C1041<br>GVT732 |      |      |

|-------------------|-------------------------------------------------------|------|----------------------|------------------|------|------|

| Parameter         | Description                                           | Min. | Max.                 | Min.             | Max. | Unit |

| READ CYCLE        |                                                       | •    |                      |                  |      |      |

| t <sub>RC</sub>   | READ Cycle Time                                       | 10   |                      | 12               |      | ns   |

| t <sub>AA</sub>   | Address Access Time                                   |      | 10                   |                  | 102  | ns   |

| t <sub>ACE</sub>  | Chip Enable Access Time                               |      | 10                   |                  | 12   | ns   |

| t <sub>OH</sub>   | Output Hold from Address Change                       | 3    |                      | 3                |      | ns   |

| t <sub>LZCE</sub> | Chip Enable to Output in Low-Z <sup>[6, 7]</sup>      | 3    |                      | 3                |      | ns   |

| t <sub>HZCE</sub> | Chip Disable to Output in High-Z <sup>[6, 7, 8]</sup> |      | 5                    |                  | 6    | ns   |

| t <sub>AOE</sub>  | Output Enable Access Time                             |      | 5                    |                  | 6    | ns   |

| t <sub>LZOE</sub> | Output Enable to Output in Low-Z                      | 0    |                      | 0                |      | ns   |

| t <sub>HZOE</sub> | Output Enable to Output in High-Z <sup>[6, 8]</sup>   |      | 5                    |                  | 6    | ns   |

| t <sub>ABE</sub>  | Byte Enable Access Time                               |      | 5                    |                  | 6    | ns   |

| t <sub>LZBE</sub> | Byte Enable to Output in Low-Z <sup>[6, 7]</sup>      | 0    |                      | 0                |      | ns   |

| t <sub>HZBE</sub> | Byte Disable to Output in High-Z <sup>[6, 7, 8]</sup> |      | 5                    |                  | 6    | ns   |

| t <sub>PU</sub>   | Chip Enable to Power-up Time <sup>[6]</sup>           | 0    |                      | 0                |      | ns   |

| t <sub>PD</sub>   | Chip Disable to Power-down Time <sup>[6]</sup>        |      | 10                   |                  | 12   | ns   |

| WRITE CYCLE       |                                                       | •    | 1                    | •                |      | •    |

| t <sub>WC</sub>   | WRITE Cycle Time                                      | 10   |                      | 12               |      | ns   |

| t <sub>CW</sub>   | Chip Enable to End of Write                           | 8    |                      | 8                |      | ns   |

| t <sub>AW</sub>   | Address Valid to End of Write, with OE HIGH           | 8    |                      | 8                |      | ns   |

| t <sub>AS</sub>   | Address Set-up Time                                   | 0    |                      | 0                |      | ns   |

| t <sub>AH</sub>   | Address Hold from End of Write                        | 0    |                      | 0                |      | ns   |

| t <sub>WP2</sub>  | WRITE Pulse Width                                     | 10   |                      | 10               |      | ns   |

| t <sub>WP1</sub>  | WRITE Pulse Width, with OE HIGH                       | 8    |                      | 8                |      | ns   |

| t <sub>DS</sub>   | Data Set-up Time                                      | 5    |                      | 6                |      | ns   |

| t <sub>DH</sub>   | Data Hold Time                                        | 0    |                      | 0                |      | ns   |

| t <sub>LZWE</sub> | Write Disable to Output in Low-Z <sup>[6, 7]</sup>    | 3    |                      | 4                |      | ns   |

| t <sub>HZWE</sub> | Write Enable to Output in High-Z <sup>[6, 7, 8]</sup> |      | 5                    |                  | 6    | ns   |

| t <sub>BW</sub>   | Byte Enable to End of Write                           | 8    |                      | 8                |      | ns   |

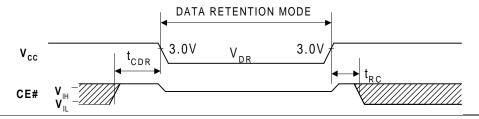

### Data Retention Characteristics Over the Operating Range (For L version only)

| Parameter                         | Description                          | Conditions                                                                                              |               | Min.            | Тур. | Max. | Unit |

|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|---------------|-----------------|------|------|------|

| V <sub>DR</sub>                   | V <sub>CC</sub> for Data Retention   |                                                                                                         |               | 2.0             |      |      | V    |

| I <sub>CCDR</sub> <sup>[9]</sup>  | Data Retention Current               | $\overline{CE} \ge V_{CC} - 0.2V;$                                                                      | $V_{CC} = 2V$ |                 | 0.2  | 1.6  | mA   |

|                                   |                                      | all other inputs $\leq$ V <sub>SS</sub> + 0.2 or $\geq$ V <sub>CC</sub> - 0.2; all inputs static; f = 0 | $V_{CC} = 3V$ |                 | 0.3  | 2.4  | mA   |

| t <sub>CDR</sub> <sup>[6]</sup>   | Chip Deselect to Data Retention Time |                                                                                                         |               | 0               |      |      | ns   |

| t <sub>R</sub> <sup>[6, 10]</sup> | Operation Recovery Time              |                                                                                                         |               | t <sub>RC</sub> |      |      | ns   |

- At any given temperature and voltage condition, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> and t<sub>HZWE</sub> is less than t<sub>LZWE</sub>.

Output loading is specified with C<sub>L</sub>=5 pF as in AC Test Loads. Transition is measured ±500mV from steady state voltage.

Capacitance derating applies to capacitance different from the load capacitance shown in AC Test Loads.

t<sub>RC</sub> = Read Cycle Time.

## Low V<sub>CC</sub> Data Retention Waveform

### **Switching Waveforms**

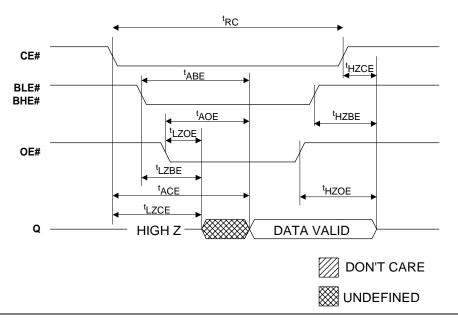

Read Cycle No. 1<sup>[11, 12]</sup>

Read Cycle No.  $2^{[7, 11, 13, 14]}$

#### Notes:

- WE is HIGH for read cycle.

Device is continuously selected. Chip Enable and Output Enables are held in their active state.

Address valid prior to or coincident with latest occurring chip enable.

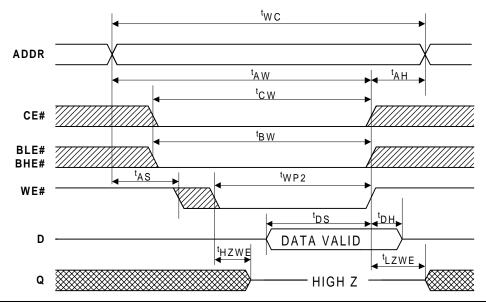

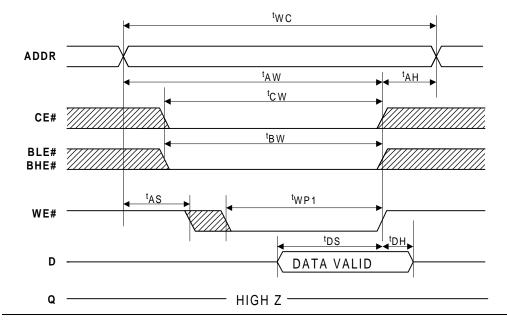

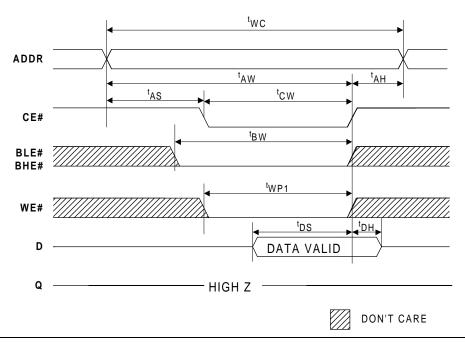

Chip Enable and Write Enable can initiate and terminate a write cycle.

# Switching Waveforms (continued)

# Write Cycle No. 1 ( $\overline{\text{WE}}$ Controlled with $\overline{\text{OE}}$ Active LOW)[9, 7, 14]

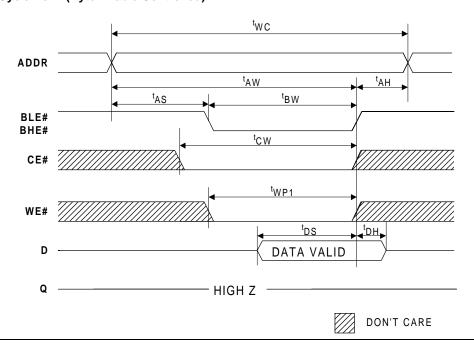

# Write Cycle No. 2 (WE Controlled with OE Inactive HIGH)[9, 14]

# Switching Waveforms (continued)

# Write Cycle No. 3 ( $\overline{\text{CE}}$ Controlled)<sup>[9, 14]</sup>

# Write Cycle No. 4 (Byte Enable Controlled)[9, 14]

# **Ordering Information**

| Speed<br>(ns) | Ordering Code      | Package<br>Name | Package Type                 | Operating<br>Range |

|---------------|--------------------|-----------------|------------------------------|--------------------|

| 10            | CY7C1041AV33-10VC  | V36             | 36-Lead (400-Mil) Molded SOJ | Commercial         |

|               | GVT73256A16J-10C   |                 |                              |                    |

|               | CY7C1041AV33-10ZC  | Z44             | 44-Pin TSOP II               |                    |

|               | GVT73256A16TS-10C  |                 |                              |                    |

|               | CY7C1041AV33L-10VC | V36             | 36-Lead (400-Mil) Molded SOJ |                    |

|               | GVT73256A16J-10LC  |                 |                              |                    |

|               | CY7C1041AV33L-10ZC | Z44             | 44-Pin TSOP II               |                    |

|               | GVT73256A16TS-10LC |                 |                              |                    |

| 12            | CY7C1041AV33-12VC  | V36             | 36-Lead (400-Mil) Molded SOJ | Commercial         |

|               | GVT73256A16J-12C   |                 |                              |                    |

|               | CY7C1041AV33-12ZC  | Z44             | 44-Pin TSOP II               |                    |

|               | GVT73256A16TS-12C  |                 |                              |                    |

|               | CY7C1041AV33L-12VC | V36             | 36-Lead (400-Mil) Molded SOJ |                    |

|               | GVT73256A16J-12LC  |                 |                              |                    |

|               | CY7C1041AV33L-12ZC | Z44             | 44-Pin TSOP II               |                    |

|               | GVT73256A16TS-12LC |                 |                              |                    |

Document #: 38-00997-\*\*

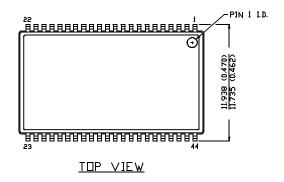

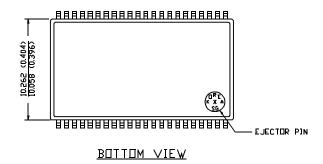

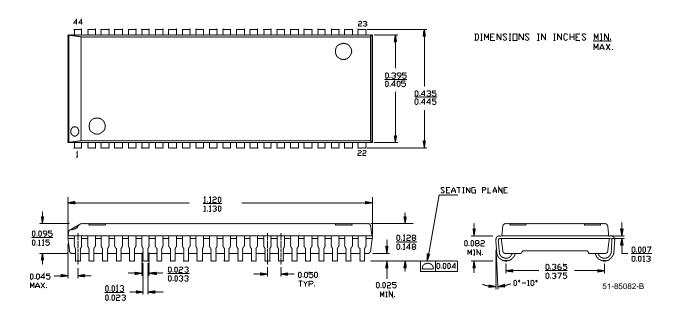

# **Package Diagrams**

#### 44-Lead (400-Mil) Molded SOJ V34

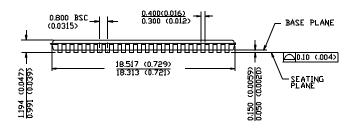

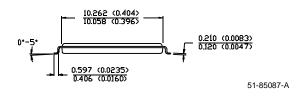

#### Package Diagrams (continued)

#### 44-Pin TSOP II Z44

DIMENSION IN MM (INCH)

MAX

MIN.