L64111 MPEG Audio Decoder Technical Manual

September 1993

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications

First Edition MD72-000101-99 A

using production parts.

This document applies to revision B of the L64111 MPEG Audio Decoder and to all subsequent versions unless otherwise indicated in a subsequent edition or an update to this edition of the document.

Publications are stocked at the address given below. Requests should be addressed to:

LSI Logic Corporation Literature Distribution, M/S D-102 1551 McCarthy Boulevard Milpitas, CA 95035 Fax: 408.433.8989

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

© 1993 LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# **Preface**

This book is the primary reference and technical manual for the L64111 MPEG Audio Decoder. It contains a complete functional description for the L64111 and includes complete physical and electrical specifications for the L64111.

#### **Audience**

This book assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the L64111 for possible use in a system

- Engineers who are designing the L64111 into a system

## Organization

This book has the following chapters:

- Chapter 1, Introduction, describes the general characteristics and capabilities of the L64111 and provides an introduction to relevant MPEG concepts.

- Chapter 2, Audio Decoder Functional Overview, describes L64111 interfaces and discusses the chip's internal architecture and functions.

- Chapter 3, Audio Decoder Signal Descriptions, details the operation of each L64111 interface signal.

- Chapter 4, Registers, describes the L64111 registers and their usage.

- Chapter 5, Specifications, lists the electrical and mechanical characteristics of the product.

- Chapter 6, Applications, presents the designs of several applications.

## Related Publications

ISO/IEC JTC 1/SC 29 Coded Representation of Picture, Audio and Multimedia/Hypermedia Information: MPEG CD 11172 Part 1 - Systems, Part 2 - Video, and Part 3 - Audio.

# Conventions Used in this Manual

The following signal naming conventions are used throughout this manual:

- A level-significant signal that is true or valid when the signal is LOW always has an overbar ( ) over its name.

- An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has an overbar ( ) over its name.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by the subscripted "2" following the number—for example, 1101<sub>2</sub>.

The first time a word or phrase is defined in this manual, it is italicized.

# **Contents**

| Chapter 1 | Intro | 1-1                                      |     |

|-----------|-------|------------------------------------------|-----|

| •         | 1.1   | L64111 Features                          | 1-2 |

|           | 1.2   | MPEG Overview                            | 1-3 |

|           | 1.3   | MPEG Audio Encoding                      | 1-4 |

|           | 1.4   | Transmission of MPEG Data                | 1-5 |

|           |       | L64111 MPEG Data Input                   | 1-5 |

|           |       | ISO System Streams                       | 1-6 |

|           |       | MPEG Packets                             | 1-6 |

| Chapter 2 | Aud   | io Decoder Functional Overview           | 2-1 |

|           | 2.1   | L64111 Features                          | 2-2 |

|           |       | Data Input                               | 2-2 |

|           |       | Control and Processing                   | 2-2 |

|           |       | Output                                   | 2-3 |

|           |       | Error Handling                           | 2-3 |

|           |       | Synchronization                          | 2-3 |

|           | 2.2   | L64111 Internal Organization             | 2-3 |

|           |       | Controller Interface and Input Data FIFO | 2-5 |

|           |       | Pre-parser                               | 2-5 |

|           |       | Decoder                                  | 2-6 |

|           |       | DRAM Controller                          | 2-6 |

|           |       | Play Director                            | 2-6 |

|           |       | PCM Serial Converter                     | 2-6 |

|           |       | Output Multiplexer                       | 2-6 |

|           | 2.3   | Decoding Details                         | 2-6 |

|           | 2.4   | Rate Control and Clock Granularity       | 2-8 |

| Chapter 3 | Aud   | lio Decoder Signal Descriptions          | 3-1 |

|           | 3.1   | Digital Audio Data Serial Inputs         | 3-2 |

|           | 3.2 | DRAM Interface                          | 3-3  |

|-----------|-----|-----------------------------------------|------|

|           | 3.3 | Controller Interface                    | 3-4  |

|           | 3.4 | FIFO Status Indicators                  | 3-5  |

|           | 3.5 | Other Control Signals                   | 3-6  |

|           | 3.6 | PCM Audio Outputs                       | 3-8  |

| Chapter 4 | Reg | isters                                  | 4-1  |

|           | 4.1 | Register Operation and Summary          | 4-2  |

|           | 4.2 | Data Register                           | 4-3  |

|           | 4.3 | Control Registers                       | 4-4  |

|           |     | Control Register 1                      | 4-4  |

|           |     | Control Register 2                      | 4-6  |

|           |     | Control Register 3                      | 4-8  |

|           | 4.4 | Interrupt Registers                     | 4-9  |

|           |     | Interrupt Mask and Status Register 1    | 4-9  |

|           |     | Interrupt Mask and Status Register 2    | 4-10 |

|           | 4.5 | Timer Countdown and Offset Registers    | 4-12 |

|           |     | Timer Countdown Register (TCR)          | 4-12 |

|           |     | Timer Offset Register High (TORH)       | 4-13 |

|           |     | Timer Offset Register Low (TORL)        | 4-13 |

|           | 4.6 | Parametric Data Word Registers          | 4-13 |

|           |     | Parametric Data Word Register 1         | 4-14 |

|           |     | Parametric Data Word Register 2         | 4-15 |

|           |     | Parametric Data Word Register 3         | 4-16 |

|           | 4.7 | Presentation Time Stamp (PTS) Registers | 4-17 |

|           | 4.8 | Ancillary/User Data FIFO                | 4-17 |

|           | 4.9 | Channel Buffer Registers                | 4-18 |

|           |     | Channel Buffer Status Counter           | 4-18 |

|           |     | Channel Buffer Write Counter            | 4-18 |

|           |     | Channel Buffer Read Counter             | 4-19 |

| Chapter 5 | Spe | cifications                             | 5-1  |

|           | 5.1 | Electrical Characteristics              | 5-2  |

|           | 5.2 | AC Timing                               | 5-5  |

|           | 5.3 | Pinouts                                 | 5-9  |

|           | 5.4 | Mechanical Specifications               | 5-10 |

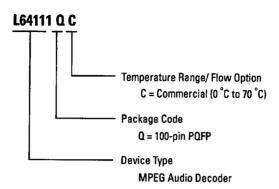

|           | 5.5 | Ordering Information                    | 5 12 |

| Chapter 6  | Арр | 6-1                                        |      |

|------------|-----|--------------------------------------------|------|

| •          | 6.1 | External Controller Operation              | 6-1  |

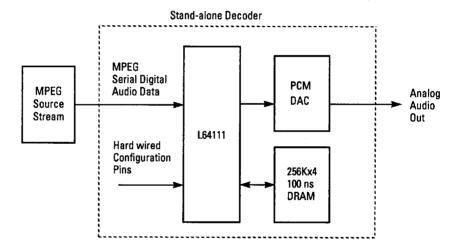

|            | 6.2 | Stand-alone Operation                      | 6-4  |

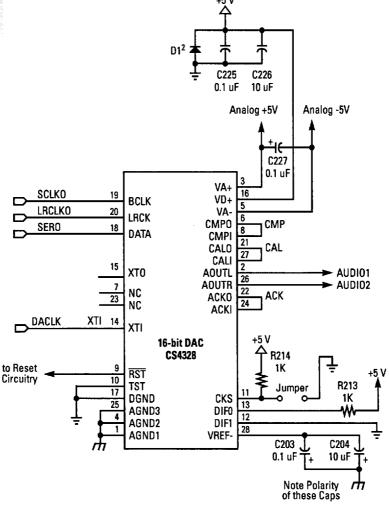

|            | 6.3 | DAC Interfacing                            | 6-5  |

|            |     | Calculating the Output Sample Rate         | 6-7  |

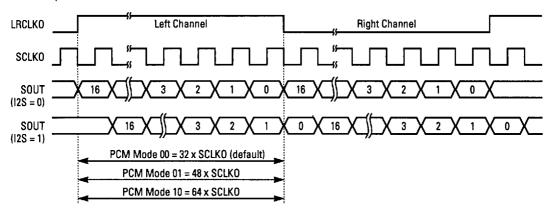

|            |     | Setting the PCM Output Mode                | 6-9  |

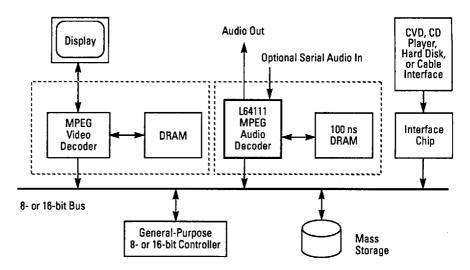

|            | 6.4 | Audio/Video Application                    | 6-10 |

|            |     | Synchronization Using Timecodes            | 6-10 |

|            |     | Input Buffering Considerations             | 6-11 |

|            |     | Cue and Review                             | 6-12 |

| Appendix A | Cus | tomer Feedback                             | A-1  |

| Figures    | 1.1 | L64111 Interface Signals                   | 1-2  |

|            | 1.2 | Audio Encoding Process (Simplified)        | 1-5  |

|            | 1.3 | ISO System Stream                          | 1-6  |

|            | 1.4 | MPEG Audio Packet Structure                | 1-7  |

|            | 2.1 | L64111 Internal Architecture               | 2-4  |

|            | 2.2 | Input Data FIFO                            | 2-5  |

|            | 2.3 | Decoder Audio Stream Processing Flow Chart | 2-7  |

|            | 3.1 | L64111 Logic Symbol                        | 3-2  |

|            | 3.2 | Input Data FIFO and Flags                  | 3-6  |

|            | 3.3 | Use of STARTI and STARTO Signals           | 3-8  |

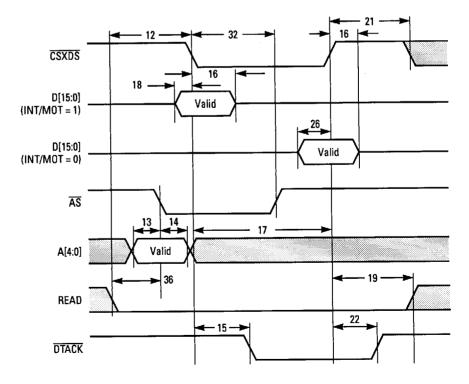

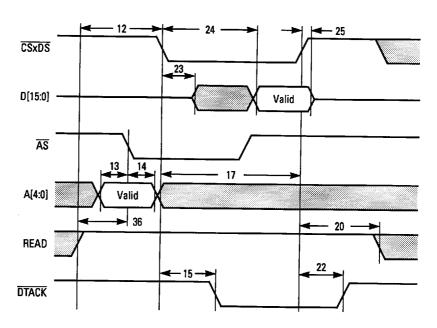

|            | 5.1 | Channel Buffer Write Cycle                 | 5-6  |

|            | 5.2 | Channel Buffer Read Cycle                  | 5-7  |

|            | 5.3 | Controller Interface Write Cycle           | 5-7  |

|            | 5.4 | Controller Interface Read Cycle            | 5-8  |

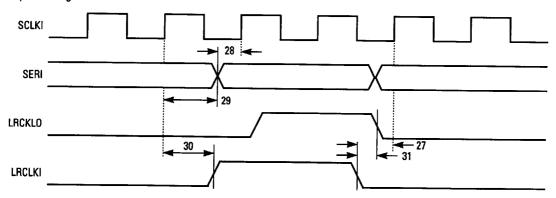

|            | 5.5 | Input Timing                               | 5-8  |

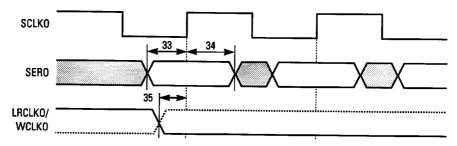

|            | 5.6 | Serial PCM Data Out Timing                 | 5-8  |

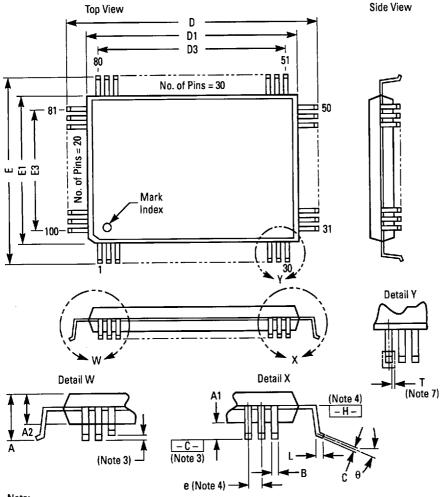

|            | 5.7 | 100-pin PQFP Mechanical Dimensions         | 5-11 |

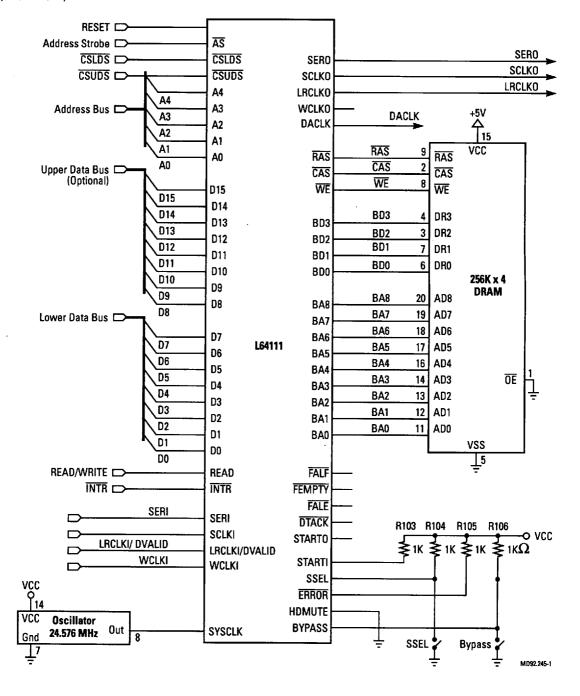

|            | 6.1 | Application Using External Controller      | 6-2  |

|            | 6.2 | Stand-alone Operation                      | 6-4  |

|            | 6.3 | PCM Output Modes                           | 6-9  |

|            | 6.4 | Audio/Video Application Elements           | 6-10 |

# ■ 5304804 0011519 365 ■LLC

| Tables | 1.1 | Audio Frame Header Structure                              | 1-7  |

|--------|-----|-----------------------------------------------------------|------|

|        | 4.1 | L64111 Registers                                          | 4-3  |

|        | 5.1 | Absolute Maximum Ratings                                  | 5-2  |

|        | 5.2 | Recommended Operating Conditions                          | 5-2  |

|        | 5.3 | Capacitance                                               | 5-2  |

|        | 5.4 | DC Characteristics                                        | 5-3  |

|        | 5.5 | Pin Description Summary                                   | 5-4  |

|        | 5.6 | AC Characteristics                                        | 5-5  |

|        | 5.7 | 100-pin PQFP Pinout by Pin Number                         | 5-9  |

|        | 5.8 | 100-pin PQFP Pinout by Pin Name                           | 5-10 |

|        | 6.1 | Hardwiring Values Using Input Pins                        | 6-5  |

|        | 6.2 | Recommended Operating Frequencies Using Oversampling DACs | 6-6  |

■ 5304804 0011520 087 ■■LLC

# Chapter 1 Introduction

Chapter 1 introduces the LSI Logic L64111 MPEG Audio Decoder and presents an introduction to MPEG technology. The L64111 is a single chip handling all aspects of the MPEG audio decoding process.

This chapter contains four sections:

- Section 1.1, L64111 Features

- Section 1.2, MPEG Overview

- Section 1.3, MPEG Audio Encoding

- Section 1.4, Transmission of MPEG Data

# 1.1 L64111 Features

The L64111 MPEG Audio Decoder is a single LSI component combining an ISO 11172 MPEG system stream decoder and an MPEG audio decoder.

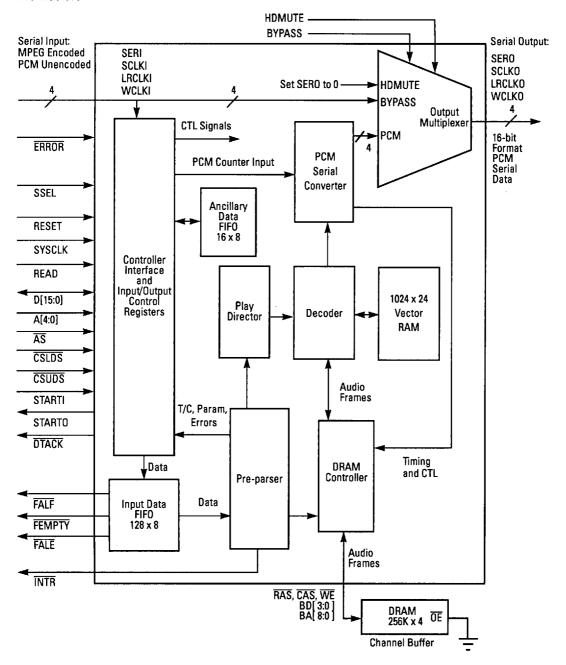

Figure 1.1 is a block diagram of the L64111. The L64111 can accept either serial or parallel digital MPEG audio data. The L64111 contains an internal DRAM controller, which interfaces with external DRAM to provide memory for a Channel Buffer.

The L64111 can be used in stand-alone and controller-based applications, such as digital cable decoders, CD players, digital VCRs, digital direct-broadcast satellite decoders, laser disk players, CD ROM players, and workstations.

Figure 1.1 L64111 Interface Signals

The key features of the L64111 are:

- complies with ISO CD 11172-1 and CD 11172-3 specifications for decoding of MPEG 90/265 Layers I and II audio bitstreams

- receives and handles MPEG ISO System Stream pack

- handles MPEG audio stream (audio frame) packet

- handles up to 15 Mbit/s (sustained rate) bitstream parsing

- decodes/reconstructs MPEG-1 audio stream Layers I and II in real-time

- supports data rates up to 192 Kbit/s monaural and 384 Kbit/s stereo/dual channel

- MUSICAM compatible at selected bitrates

- operates with or without an external system microcontroller

- handles 8- or 16-bit data through the external controller interface

- simple interface to external Channel Buffer using a single 256K x 4

100 ns fast page mode DRAM

- supports more than one second of delay for audio/video synchronization

- includes registers for cue and review control and output data rate control

# 1.2 MPEG Overview

The ISO/IEC Motion Pictures Expert Group (MPEG) first proposed the JTC1/SC2/WG11 standard for coding of moving pictures and associated audio for use with digital storage media in 1990. Though a full discussion of MPEG is beyond the scope of this document, this section summarizes concepts common to both MPEG audio and video applications.

MPEG is a standard for the representation of compressed audio and video signals. It allows for:

- Data interchange between compatible systems

- Standardized decoding methodologies

Given an *elementary stream* of data (for audio data, this is called an *audio stream*), an MPEG encoder first digitally compresses and codes the data. The MPEG algorithm offers a choice of levels of complexity and performance for this process. (See Section 1.3, "MPEG Audio Encoding," for more information.)

To prepare a stream of compressed audio data for transmission, it is formatted into *audio frames*. Each audio frame contains audio data, error-correction data, and optional user-defined *ancillary data*. The audio frames are then sent in *packets* grouped within *packs* in an ISO MPEG System Stream. (See Section 1.4, "Transmission of MPEG Data," for more information.)

The packs in system streams may contain a mix of audio packets and video packets for one or more channels. Packs may contain packets from separate elementary streams. Thus, MPEG can easily support multiple

Introduction 1-3

channels of program material, and a decoder given access to a system stream may access large numbers of channels.

On the receiving end, MPEG audio decoding involves:

- identifying and removing a channel's audio frames from the audio packets in the System Stream

- managing the temporary storage of frames

- applying appropriate algorithms for decoding the audio frames

- merging decoded audio frames back into continuous audio

- limiting the effect of transmission errors

The LSI Logic L64111 MPEG Audio Decoder is a single-chip solution that performs all MPEG-1 Audio Layer I and II decoding operations in real time. The L64111 produces decoded audio data in industry-standard Pulse Code Modulation (PCM) serial format, allowing the use of commodity parts (PCM DACs) for audio output.

The following two sections discuss the two major parts of MPEG audio processing in more detail.

# 1.3 MPEG Audio Encoding

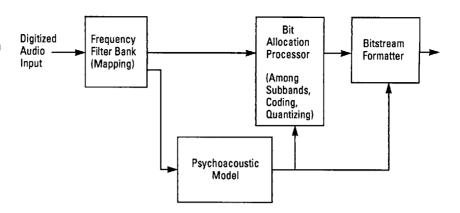

MPEG audio encoding is intended to efficiently represent a digitized audio stream by removing redundant information. Because different applications have different performance goals, MPEG uses different encoding techniques. These techniques, called *Layers*, provide different trade-offs between compression and signal quality. The MPEG algorithm uses the two following processes for removing redundant audio information:

- Coding and quantization

- Psychoacoustic modelling

Coding and quantization are techniques that are applied to data that has been mapped into the frequency domain and filtered into subbands.

Psychoacoustic modeling is a technique that determines the best allocation of data within the available data channel bandwidth based on human perception.

The general structure of an MPEG encoder is shown in Figure 1.2.

Figure 1.2 Audio Encoding Process (Simplified)

# 1.4 Transmission of MPEG Data

This section discusses formatting and transmission of MPEG-encoded data.

Once audio data has been coded, it may be stored or transmitted digitally. MPEG provides a framework for use of packet-oriented transmission of compressed data. In particular, ISO CD 11172 defines formats for digital data streams for both video and audio. The ISO System Stream format is designed to accommodate both audio packets and video packets within the same framework for transmission.

An ISO System Stream contains data in a specified sequential format. The data may be physically delivered in parallel form or serial form. The following discusses how the L64111 decoder accepts and handles data streams at the physical and the logical level.

# L64111 MPEG Data Input

The L64111 provides the following formats for MPEG data:

- Parallel input through a microcontroller interface

- Serial input through a dedicated serial link

**Parallel Data Input.** In order to be compatible with computer and storage media applications, the L64111 accepts parallel data through its Controller Interface. For more details on the Controller Interface, refer to the discussions in Chapters 2 and 3.

**Serial Data Input.** In order to be compatible with data transmission applications, the L64111 has a dedicated serial link interface to handle coded data, which is typically provided in bit-serial fashion.

Introduction 1-5

# ISO System Streams

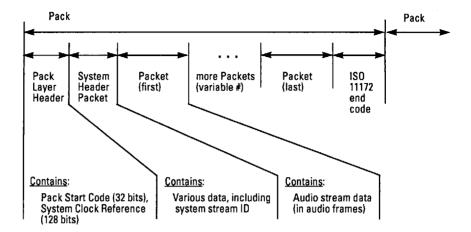

This subsection discusses MPEG system syntax. The highest level MPEG syntax is the ISO System Stream. The System Stream is composed of a sequence of packs, as shown in Figure 1.3.

Figure 1.3 ISO System Stream

An MPEG pack is composed of a pack layer header, a system header packet, a sequence of packets, and ends with an ISO 11172 end code. The pack layer header contains a pack start code used for synchronization purposes, and a system clock value. The system header packet contains a variety of housekeeping data and in particular contains a system stream ID used to differentiate multiple system streams. A sequence of one or more packets contains either encoded audio or encoded video stream data. The ISO 11172 end code is the final element in an MPEG pack.

For detailed definition of pack headers, refer to the ISO CD 11172-1 system stream descriptions. The following section describes MPEG packets in more detail.

#### MPEG Packets

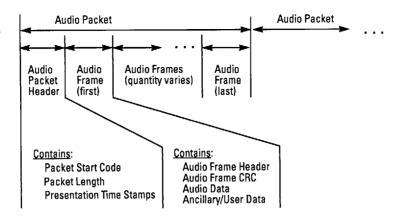

Any one MPEG packet carries either audio or video data, but not both simultaneously. An MPEG Audio Packet contains an audio packet header and one or more Audio Frames. Figure 1.4 shows the packet structure.

Figure 1.4 MPEG Audio Packet Structure

Audio Packet Header. An audio packet header contains the following:

#### Packet Start Code

Identifies this as an audio packet. The Packet Start Code also contains a five-bit audio stream identifier that may be read by the user to identify the audio channel.

# Packet Length

Indicates the number of bytes remaining in the audio packet

■ Presentation Time Stamps (PTS)

These time stamps (PTS) are optional. The L64111 makes the PTS data available to the user through registers.

**Audio Frame**. An Audio Frame contains a slice of the audio data stream together with some supplementary data. Audio frames have the following elements:

#### Audio Frame Header

Table 1.1 shows the audio frame header structure:

Table 1.1 Audio Frame Header Structure

| Size    | Purpose                                                                                         |  |  |  |

|---------|-------------------------------------------------------------------------------------------------|--|--|--|

| 12 bits | Has a fixed value of 0xFFF. The decoder uses the sync word to synchronize with the data stream. |  |  |  |

| 1 bit   | The decoder uses the ID to identify whether the data is MPEG coded or not.                      |  |  |  |

| 2 bits  | Defines whether data is encoded as Layer I, II, or III.                                         |  |  |  |

| 1 bit   | A CRC is included in the data stream.                                                           |  |  |  |

| 4 bits  | Defines an index into a table defining the bit rate.                                            |  |  |  |

|         | 12 bits 1 bit 2 bits 1 bit                                                                      |  |  |  |

(Sheet 1 of 2)

Introduction 1-7

## Table 1.1 (Continued) Audio Frame Header Structure

| Data Field            | Size   | Purpose                                                                                 |

|-----------------------|--------|-----------------------------------------------------------------------------------------|

| Sampling Frequency ID | 2 bits | Identifies the sampling frequency.                                                      |

| Padding Bit           | 1 bit  | Adds additional bytes to an audio frame to match the sample rate to the bit rate.       |

| Private Bit           | 1 bit  | User definable spare bit.                                                               |

| Channel Mode          | 2 bits | Identifies whether the channel data is stereo, joint stereo, dual channel, or monaural. |

| Mode Extension        | 2 bits | Used only in joint stereo mode. Indicates joint stereo subbands.                        |

| Copyright             | 1 bit  | Flags whether the data stream contains copyrighted material.                            |

| Original/Home         | 1 bit  | Indicates whether this data stream is an original or a copy.                            |

| Emphasis              | 2 bits | Indicates the type of de-emphasis to be used.                                           |

| (Sheet 2 of 2)        |        |                                                                                         |

## Audio Frame Cyclic Redundancy Code (CRC)

This field contains a 16-bit checksum, which can be used to detect errors in the audio frame header.

#### Audio Data

The L64111 uses the audio data to reconstruct the sampled audio data. Its format is beyond the scope of this document. The data structures for Layer I dual channel/stereo, intensity stereo, and for the more complex Layer II audio data fields are described in Sections 2.4.1.5 and 2.4.1.6 of the ISO CD 11172-3.

## Ancillary Data

The final field in an audio frame contains user-defined data (ancillary data).

# Chapter 2 Audio Decoder Functional Overview

Chapter 2 describes the features, major internal architecture, and general internal operation of the L64111 MPEG Audio Decoder. Additional application-specific material is given in Chapter 6, "Applications."

- Section 2.1, L64111 Features

- Section 2.2, L64111 Internal Organization

- Section 2.3, Decoding Details

- Section 2.4, Rate Control and Clock Granularity

## 2.1 L64111 Features

The L64111 can be used in environments ranging from stand-alone to controller-based, as well as in a workstation or embedded application. Applications for the L64111 include digital cable decoders, CD players, digital VCRs, digital direct-broadcast satellite decoders, laser disk players, CD ROM players, and multimedia workstations.

## Data Input

The L64111 decoder can accept MPEG coded data in serial or parallel form. In Bypass mode, the L64111 routes input data unprocessed to the output. The L64111 can accept parallel data in either 8-bit or 16-bit form from a system controller.

# Control and Processing

The L64111 parses ISO Systems Streams and also accepts Audio Streams.

The decoder can parse system bitstreams at rates up to 15 Mbits/second (depending on system clock speed), store and catalog audio frames in its external channel buffer, and provide presentation time stamp information for audio-video synchronization.

#### Control

The L64111 may be used either as a stand-alone processor or with a system controller (microcontroller or microprocessor). The controller interface supports 8- or 16-bit data transfers. The L64111 obtains decoding information directly from the data stream. A controller may supply optional parameters for decoder synchronization, error correction, and frequency selection. When operating stand-alone, the L64111 uses default parameters.

# **Channel Buffer Capability**

The L64111 requires an external channel buffer for temporary storage of audio frames that have been removed from the stream. The L64111's internal DRAM controller requires just one external component: a 256K x 4 fast page mode DRAM. The channel buffer can handle at least one second of data, which facilitates audio-video synchronization or other delay compensation.

# **Audio-Video Synchronization**

Synchronization of audio and video streams requires that an external system controller monitor the video and audio presentation time stamps. The decoder delays audio frames (stores them in the buffer) until the controller determines that the correct presentation time has been reached. At this point the controller commands the L64111 to start decoding from data in the channel buffer. Using the 256K x 4 Channel Buffer, the decoder can compensate for at least one second of delay between audio and video data.

# **Processing**

The L64111 completely integrates and automates the process of decoding Layer I or Layer II streams.

## Output

The L64111 provides a 16-bit PCM output by means of a multiplexed serial output bus compatible with commodity PCM serial D to A converters (DACs). A bypass command allows four-wire PCM serial audio data to be passed directly from serial input to serial output with only a multiplexer delay.

# **Error Handling**

The L64111 provides the ability to conceal errors in data. When this function is enabled, two choices of response to error are provided:

(1) repeat of last error-free audio frame, or (2) muting.

# Synchronization

A multipass synchronization mechanism minimizes frame synchronization errors. With this technique, successive valid syncs must be acquired before synchronization is established.

# 2.2 L64111 Internal Organization

When initialized, the L64111 synchronizes itself by monitoring the data stream and locating an audio frame in the data stream. When MPEG data is input, the chip strips away all unneeded information, retaining only the audio and control data. The audio and control data is then partially expanded and stored in a channel buffer. When the appropriate control signals are seen, this stored data is played; that is, decompression is performed and the data is output in PCM format.

Figure 2.1 shows the L64111's internal architecture. The functions of the main elements are discussed after the figure.

Figure 2.1 L64111 Internal Architecture

# Controller Interface and Input Data FIFO

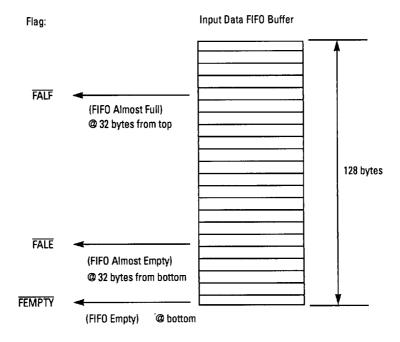

Data enters the L64111 in parallel through the Controller Interface, or in serial through the serial port. The data is first synchronized to the system clock (SYSCLK), then sent to the Input Data FIFO. The FIFO buffers the data and supplies it to the Pre-parser. Various flags signal the extent to which the buffer is full or empty. The flags are made available for flow control. The input FIFO is not part of the channel buffer, and its flags do not reflect the state of the channel buffer.

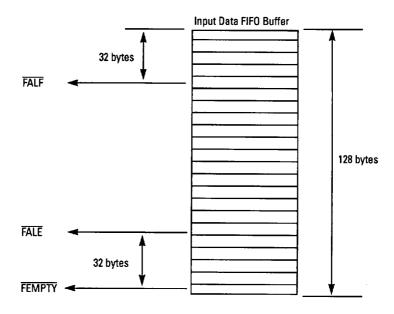

Figure 2.2 Input Data FIFO

# Pre-parser

The Pre-parser performs stream parsing. For ISO System Stream parsing and synchronization, the Pre-parser detects the pack start code or system header start code and uses one of these to synchronize to the ISO stream.

The Pre-parser then looks for packet header information and attempts packet identification. It identifies audio frame information and discards all else. Next, it calculates the CRC and separates the header information from the audio data and sends the audio data to the channel buffer.

## Decoder

The decoder receives data from the Channel Buffer and fully decodes the data using the MPEG algorithm. The reconstructed data is then sent into the PCM Serial Converter.

### **DRAM Controller**

The DRAM Controller handles the read/write and refresh activities of the external Channel Buffer DRAM. The Channel Buffer stores blocks of partially decoded audio data prior to their reconstruction in the decoder.

# **Play Director**

The Play Director maintains a list of the frames in the Channel Buffer. It also holds certain header information required to complete the decoding operation of each frame. The frames are normally accessed as a circular buffer. It is possible to skip or replay frames (cue and review) while they are in the Play Director. The Play Director is also used in error concealment.

# PCM Serial Converter

The 16-bit reconstructed stereo pair is output in a PCM format compatible with most serial D to A converters. Various modes are supported.

# Output Multiplexer

The Output Multiplexer controls routing of serial data signals. It can be program-controlled or hardwired to select one of the following three outputs:

- SERO set to zero

- Unprocessed input data (passed through unchanged)

- PCM format output of decoder

In Bypass Mode, the L64111 passes all four PCM inputs unaltered to the output. All signals retain their temporal alignment.

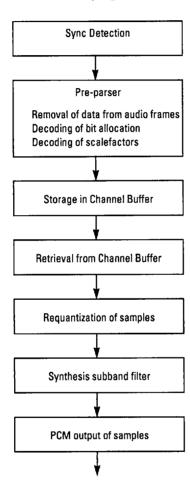

# 2.3 Decoding Details

The decoder can operate with bit rates up to 384 Kbits/second stereo or dual channel with sampling frequencies of 32 KHz, 44.1 KHz, or 48 KHz. Once the decoder has started decoding, it takes data from the Channel Buffer. The decoder uses a two-pass system, as described in the following paragraphs.

In the first pass, the decoder parses the bitstream, separating out the sync, header information, allocations, and scalefactors, performs the CRC check, and removes ancillary data.

In the second pass, the decoder provides degrouping, inverse quantization, scaling, and subband synthesis. By performing two passes, the decoder can mask errors by repeating the same frame, and the two-pass approach allows identifying false audio syncs.

Figure 2.3 Decoder Audio Stream Processing Flow Chart

# 2.4 Rate Control and Clock Granularity

Rate control is the ability of the decoder to deliver a continuous PCM output correctly timed while the input is coming in bursts. The rate control mechanism has two parts.

The first part is the Input Data FIFO. Part of this FIFO compensates for the variations in processing time for different parts of the Pre-parser. The rest of this FIFO allows data burst rates up to 7.5 Mbytes/second (60 Mbits/second) for a length of 128 bytes, until the Pre-parser processes this data at its 15 Mbit/second rate. These rates are valid for SYSCLK of 30 MHz.

The second channel rate control is the Channel Buffer. This buffer is filled at a 15 Mbit/second rate and is emptied at the PCM output sample rate.

There is a mechanism which allows the output sample rate to be accurately derived from the device clock. It is also possible to periodically correct the output sample rate for timebase drift between the encoder and the decoder in systems where they do not share a common clock.

# Chapter 3 Audio Decoder Signal Descriptions

Chapter 3 describes all L64111 interface signals. These descriptions are useful for hardware designers who are interfacing the L64111 with other devices.

This chapter contains the following sections:

- Section 3.1, Digital Audio Data Serial Inputs

- Section 3.2, DRAM Interface

- Section 3.3, Controller Interface

- Section 3.4, FIFO Status Indicators

- Section 3.5, Other Control Signals

- Section 3.6, PCM Audio Outputs

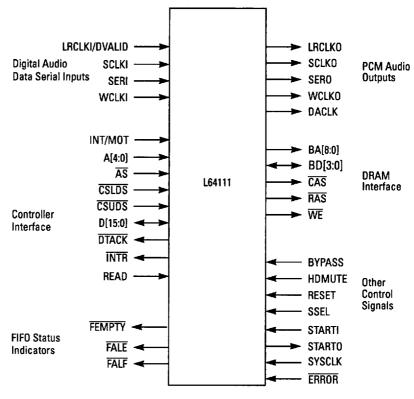

Figure 3.1 is the logic symbol for the L64111.

Figure 3.1 L64111 Logic Symbol

# 3.1 Digital Audio Data Serial Inputs

The Digital Audio serial inputs can accept MPEG or PCM serial data. The L64111 uses the serial data input when either the SSEL pin and/or the SER/PAR register bit is HIGH, or if the device is in Bypass mode. Otherwise, data on these inputs is ignored.

#### LRCLKI/DVALID

# Data Valid Input

When Bypass mode is inactive, this signal acts as DVALID. When DVALID is asserted by an external device, data on SERI is valid and is clocked into the L64111 on the next rising edge of SCLKI, which allows easy demultiplexing of multiple independent streams of serial data, or masking data (parity bits, for example) which is not part of the MPEG stream.

When the L64111 is in Bypass mode, this signal acts as LRCLKI. LRCLKI does not affect the data on SERI. During bypass, LRCLKI

is connected to LRCLKO through a multiplexer. A HIGH indicates that the SERI input contains left channel data; a LOW indicates that SERI contains right channel data. The data rate on this input is usually SCLKI/16.

## SCLKI Serial Clock In Input

The L64111 samples SERI, DVALID, and ERROR on the rising edge of SCLKI. SCLKI can be asynchronous to SYSCLK up to a maximum frequency determined by device characterization, but it can never be more than twice the frequency of SYSCLK. The clock does not need to be periodic.

In Bypass mode, SCLKI is connected to SCLKO through a multiplexer.

## SERI Serial Data In Input

Data on the Serial Data In pin is latched on the rising edge of SCLKI in the cycles where DVALID is HIGH. Serial Data In may be from either an MPEG system stream or an MPEG audio stream

In Bypass mode, SERI is connected to SCLKO through a multiplexer.

Input

## WCLKI Word Clock In

WCLKI is an optional PCM input and is not used internally by the L64111.

In Bypass mode, WCLKI is connected to WCLKO through a multiplexer.

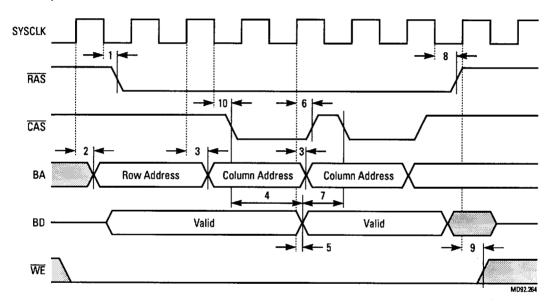

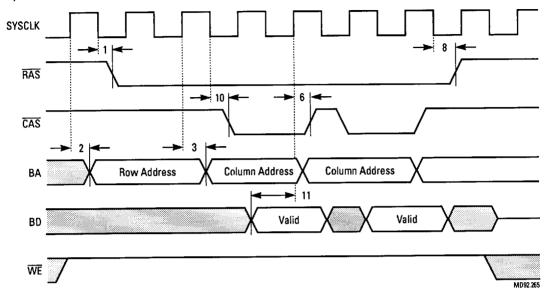

# 3.2 DRAM Interface

The L64111 interfaces directly to DRAM, which is used for a Channel Buffer. The DRAM is required for the L64111 to operate properly.

# BA[8:0] Buffer Address Outp

BA[8:0] are multiplexed address lines to the Channel Buffer DRAMs. When the L64111 asserts  $\overline{RAS}$ , BA[8:0] contain the row address. When the L64111 asserts  $\overline{CAS}$ , BA[8:0] contain the column address. The L64111 contains address line drivers so that no external components are required to drive the DRAM.

# BD[3:0] Buffer Data Bidirectional

BD[3:0] are bidirectional data lines between the L64111 and the Channel Buffer DRAM.

$\overline{\mathbf{WE}}$

CAS Column Address Strobe Output

CAS is the DRAM column address strobe. When asserted LOW, CAS indicates that BA[8:0] contain the column address.

RAS

Row Address Strobe

RAS is the DRAM row address strobe. When asserted LOW, RAS

indicates that BA[8:0] contain the row address.

Write Enable

Output

The L64111 asserts WE LOW to write data into the Channel Buffer

DRAM. The L64111 reads data from the Channel Buffer DRAM

when both RAS and CAS are LOW with WE HIGH.

# 3.3 Controller Interface

This section describes the signals for the controller interface.

A[4:0] Address Bus Input

A[4:0] are address lines that provide access to the L64111 internal registers. Refer to Table 4.1 on page 4-3 for a listing of the registers and their respective addresses.

AS

Address Strobe

When AS is asserted LOW, the L64111 latches the address on A[4:0].

AS may be tied to CSLDS if no AS signal is available from the system controller.

CSLDS Chip Select and Lower Data Strobe Input

CSLDS is the active-LOW chip select and data strobe for the least significant eight bits of the data bus (low byte).

CSUDS

Chip Select and Upper Data Strobe

CSUDS is the chip select and data strobe for the most significant eight bits of the data bus (high byte). When using 16-bit data on D[15:0], this strobe must always occur simultaneously with, or be preceded by, CSLDS. If operating with an eight-bit controller, this pin should be tied HIGH.

D[15:0] Data Bus

D[15:0] are bidirectional data bits. D[15:8] are the high byte; D[7:0] are the low byte. When operating in eight-bit mode only the low byte is used. Refer to Section 4.2, "Data Register," on page 4-3 for more information.

DTACK

Data Acknowledge

DTACK is the active-LOW data acknowledge signal to the external controller. It is asserted for at least one cycle for every transaction

over the controller interface, and remains LOW until the end of the transaction and after both CSUDS and CSLDS have been deasserted. Note that the L64111 still asserts DTACK on a write even if the Input Data FIFO is full and the write has resulted in an overflow.

#### INT/MOT Interface Mode Select

Input

When Interface Mode Select is tied HIGH, the L64111 latches data on the falling edge of READ during write cycles. When tied LOW, it latches data on the rising edge of READ during write cycles. This pin should not be toggled during normal operation.

#### **INTR**

System Interrupt

Output

The L64111 asserts INTR LOW to flag an interrupt. INTR is an open drain output and requires a 1 Kohm pullup resistor to VCC. Pulling up INTR allows multiple interrupts to be wire-ORed.

#### READ Read

Input

The system controller asserts READ (HIGH) when reading from the L64111 and deasserts READ (LOW) when writing to the L64111. The system controller must assert AS and CSLDS during both read and write operations to the L64111.

# 3.4 FIFO Status **Indicators**

The FIFO status flags operate in both serial and parallel input modes. The input FIFO and the channel buffer are unrelated, so these flags do not reflect the state of the channel buffer.

#### **FALE**

FIFO Almost Empty Flag

Output

The L64111 asserts FALE LOW to indicate that the L64111's internal 128-byte Input Data FIFO is almost empty—there are only 32 bytes of data left in the buffer (see Figure 3.2). It is not an error to let the FIFO empty completely.

#### FALE

FIFO Almost Full Flag

Output

The L64111 asserts FALF LOW to indicate that the L64111's internal 128-byte Input Data FIFO is almost full—there are only 32 unused bytes left in the buffer (see Figure 3.2). It is an error to let the FIFO overflow.

FEMPTY FIFO Empty Flag

Output

The L64111 asserts FEMPTY LOW to indicate that the L64111's internal 128-byte Input Data FIFO is empty and new data should be provided to the FIFO (see Figure 3.2). It is *not* an error to let the FIFO empty completely.

Figure 3.2 Input Data FIFO and Flags

# 3.5 Other Control Signals

This section describes the remaining L64111 control signals.

# BYPASS Decoder Bypass

## Input

If BYPASS is set to one, all serial inputs (SERI, SCLKI, DVALID, and WCLKI) are routed directly to their respective outputs (SERO, SCLKO, LRCLKO, and WCLKO) with hard mute still functional. Note that there is no buffering of PCM input data in the channel buffer. In Bypass mode, the L64111 does not process data from the serial data input.

If BYPASS is set to zero, the L64111 processes the data from the serial input.

Bypass mode can also be selected by writing to the BYPASS bit in Control Register 1, in which case the BYPASS pin should be tied LOW.

#### ERROR

#### **Error Indication**

#### Input

A LOW on the Error Indication pin indicates that the data on SERI has an error. Error Indication is used by the L64111 to conceal errors in the stream. A LOW on this pin also forces the L64111 to search for the next sync code as soon as it is released. ERROR can be connected to an error correction chip in the channel that is capable of flagging an uncorrectable error. The error indication is propagated internally along with the data.

#### **HDMUTE Hard Mute**

Input

When HDMUTE is asserted HIGH, the L64111 forces the PCM output to zeros.

Mute operation can also be selected by writing to the SOFT\_MUTE bit in Control Register 2, in which case the HDMUTE pin may be tied LOW.

#### RESET Reset

Input

The L64111 resets after RESET has been asserted HIGH for two clock cycles. RESET can be tied permanently LOW if the system controller software has been set up to assert the SOFT\_RST bit in Control Register 1 through the controller interface.

#### SSEL Serial Select

Input

The SSEL input selects the L64111's source of data. If SSEL is HIGH, the decoder accepts the serial data entering through input pins SERI, SCLKI, and DVALID. If SSEL is LOW, the decoder accepts data in parallel format from the Controller Interface data lines.

Serial selection can also be done by writing to the SER/PAR bit in Control Register 1, in which case this pin may be tied LOW.

#### STARTI

Start In

Input

When Start In is asserted HIGH, the L64111 begins to decode the data in its Channel Buffer. The L64111 may also be started by writing to the STARTI bit in Control Register 1, in which case this pin may be tied HIGH.

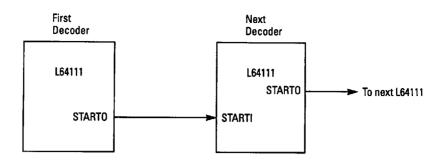

#### STARTO Start Out

Output

The STARTO pin is provided for designs having multiple MPEG audio decoders that must be synchronized. When using more than a single L64111, connect STARTO of the first device to STARTI of the second device, as illustrated in Figure 3.3. STARTO is asserted HIGH when device begins decoding stored frames from the channel buffer.

#### SYSCLK System Clock

Input

System Clock is a 50% duty cycle clock which is at least 384 times the maximum L64111 output sample frequency. System Clock should have crystal accuracy for best audio quality.

Figure 3.3 Use of STARTI and STARTO Signals

# 3.6 **PCM Audio Outputs**

The functions of the PCM Audio Output pins may be programmed to support a variety of common D to A converters.

#### DACLK **DAC Clock Out**

Output

DACLK is a clock which is half the frequency of SYSCLK. DACLK can be used to clock certain oversampling DACs.

## LRCLKO Left/Right Channel Indicator Out

Output

LRCLKO indicates whether the current data output on SERO is left channel (LRCLKO = HIGH) or right channel (LRCLKO = LOW) information. In Bypass mode, the LRCLKO pin is a reflection of DVALID.

#### **SCLKO** Serial Bit Clock Out

Output

SCLKO is the bit clock for the serial data on SERO. In Bypass mode this pin is a reflection of SCLKI.

#### Serial Data Out SERO

Output

A serial 16 bit word, sign extended with MSB first, for each of the left and right channels, synchronized to SCLKO. The actual format may be programmed through the system interface. In Bypass mode this pin is a reflection of SERI.

#### WCLKO **Word Clock Out**

Output

Transitions from HIGH to LOW on both edges of LRCLK. This signal is synchronized to SCLKO. In bypass mode, the WCLKO pin is a reflection of WCLKI.

# Chapter 4 Registers

Chapter 4 discusses the L64111's internal registers. These registers configure and control the operation of the L64111, and monitor the operating status of the L64111. This chapter contains the following sections:

- Section 4.1, Register Operation and Summary

- Section 4.2, Data Register

- Section 4.3, Control Registers

- Section 4.4, Interrupt Registers

- Section 4.5, Timer Countdown and Offset Registers

- Section 4.6, Parametric Data Word Registers

- Section 4.7, Presentation Time Stamp (PTS) Registers

- Section 4.8, Ancillary/User Data FIFO

- Section 4.9, Channel Buffer Registers

# 4.1 Register Operation and Summary

The L64111 can operate either as a stand-alone device or in applications that use a system controller. In stand-alone operation, the L64111 operates according to the register field default values except as noted later.

Operating the L64111 with a system controller allows the full range of operating capabilities. A system controller provides register values and interrupt processing control. A system controller is typically used when it is necessary to synchronize audio and video decoders, or provide operating parameter value flexibility. A system controller can also convert ancillary data in the audio stream to text for visual display.

Table 4.1 lists the L64111's registers. Note that registers designated as read-only must not be written, because the write capability of certain registers may be reserved for use only with test parameters.

Table 4.1 L64111 Registers

| Address<br>A[4:0] | Register Name                   | Description                                                                       | Read / Write<br>Capability |  |

|-------------------|---------------------------------|-----------------------------------------------------------------------------------|----------------------------|--|

| 0                 | Data                            | Data input                                                                        | Write-only                 |  |

| 1                 | Control Register 1              | Configuration                                                                     | Read / Write               |  |

| 2                 | Control Register 2              | Configuration                                                                     | Read / Write               |  |

| 3                 | Control Register 3              | Configuration                                                                     | Read / Write               |  |

| 4                 | Interrupt and Status Register 1 | Contains status of interrupt sources; allows enabling/disabling interrupt sources | Read / Write               |  |

| 5                 | Interrupt and Status Register 2 | Contains status of interrupt sources; allows enabling/disabling interrupt sources | Read / Write               |  |

| 6                 | Timer Countdown Register (TCR)  | Reference Value for Clock Divider                                                 | Read / Write               |  |

| 7                 | Timer Offset Register H (TORH)  | High Byte of Timer                                                                | Read / Write               |  |

| 8                 | Timer Offset Register L (TORL)  | Low Byte of Timer                                                                 | Read / Write               |  |

| 9                 | Parametric Data Word 1          | Audio Frame Header Information                                                    | Read-only                  |  |

| 10                | Parametric Data Word 2          | Audio Frame Header Information                                                    | Read-only                  |  |

| 11                | Parametric Data Word 3          | Audio Frame Header Information                                                    | Read-only                  |  |

| 12                | Presentation Time Stamp 1       | PTS lowest byte                                                                   | Read-only                  |  |

| 13                | Presentation Time Stamp 2       | PTS data                                                                          | Read-only                  |  |

| 14                | Presentation Time Stamp 3       | PTS data                                                                          | Read-only                  |  |

| 15                | Presentation Time Stamp 4       | PTS data                                                                          | Read-only                  |  |

| 16                | Presentation Time Stamp 5       | PTS highest byte                                                                  | Read-only                  |  |

| 17                | Ancillary/User Data FIFO        | Used for access to output of FIFO                                                 | Read-only                  |  |

| 18                | Channel Buffer Status Counter   | Channel Buffer Storage Capacity                                                   | Read-only                  |  |

| 19                | Channel Buffer Write Counter    | Pointer to the next write                                                         | Read / Write               |  |

| 20                | Channel Buffer Read Counter     | Pointer to the next read                                                          | Read / Write               |  |

| 21-31             | Reserved                        |                                                                                   |                            |  |

# 4.2 Data Register

The L64111 has one Data Register. The Data Register is connected to Controller Interface pins D[15:0]. The L64111 transfers parallel MPEG data through this register.

# Address $A[4:0] = 00000_2$

| 15       | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7           | 6   | 5         | 4         | 3         | 2         | 1     | 0  |

|----------|-----|-----|-----|-----|-----|----|----|-------------|-----|-----------|-----------|-----------|-----------|-------|----|

| D15      | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7          | D6  | D5        | D4        | D3        | D2        | D1    | D0 |

| <u> </u> |     |     | l   |     |     |    | L  | $\subseteq$ |     |           | L         | 1         | L         |       |    |

|          |     |     |     |     |     |    |    |             | Lov | v byte us | sed for r | egister a | ccess a   | nd    |    |

|          |     |     |     |     |     |    |    |             | for | MPEG d    | ata in ei | aht-bit a | arallel f | ormat |    |

MPEG data can also be written by the controller to this register in 16-bit parallel format

Data

Data

[15:0]

The Data Register is write-only. The usable width of this register is either 8 or 16 bits, depending on the setting for the width of the Controller Interface data path, which is controlled by bit 4 (SEL\_16/8\_BIT) of Control Register 2.

When eight-bit I/O is selected, the Data Register accepts the lowest eight data bits D[7:0] from the Controller Interface data pins; the highest eight bits are ignored. Eight-bit width mode is automatically selected on reset.

When the L64111 is set for 16-bit I/O, all Controller Interface data bits D[15:0] are accepted. 16-bit I/O is useful for increased performance with controllers capable of transferring 16 bits of data at a time.

# 4.3 Control Registers

The Control registers are located at addresses 1 through 3. These registers set up and configure the L64111 and monitor its operating status.

Control Register 1 Control Register 1 is an eight-bit register accessed through data bits D[7:0].

Address  $A[4:0] = 00001_2$

| 7                    | 6       | 5      | 4        | 3        | 2       | 1        | 0      |

|----------------------|---------|--------|----------|----------|---------|----------|--------|

| ANC DATA<br>FIFO RST | SER/PAR | BYPASS | RESERVED | RESERVED | BUF_RST | SOFT_RST | STARTI |

#### ANC DATA FIFO RST

#### **Ancillary Data FIFO Reset**

7

When this bit is set to one, the L64111 clears/empties the Ancillary Data FIFO on the next clock cycle. The bit must then be set back to zero to enable the FIFO. The default for this bit upon system reset is zero (FIFO enabled).

#### SER/PAR Serial/Parallel Input Select

6

When SER/PAR is one, the L64111 uses the SERI input as the source of MPEG data. When this bit is zero, the L64111 selects MPEG data from the Controller Interface data bus D[15:0] when A[4:0] = 00000<sub>2</sub>. The L64111 uses the OR of this bit and the SSEL pin to select the Serial or Parallel mode. This means that if the SSEL pin is high the device will always be in Serial input mode. The L64111 uses the value of the logical OR of this bit and the SSEL pin to determine if the mode is Parallel or Serial. The default value of this bit is zero (parallel mode).

#### BYPASS

**Bypass Mode**

5

The BYPASS bit determines whether the L64111 operates in MPEG mode (BYPASS = 0) or Bypass mode (BYPASS = 1). The L64111 uses the logical OR of this bit and the BYPASS pin to determine if the Bypass mode is selected. If the BYPASS pin is high, the device will always be in Bypass mode. The default value of this bit is zero (not bypassed).

#### RESERVED

Reserved

[4:3]

Set the RESERVED bits to zero to maintain compatibility with future L64111 revisions.

#### BUF\_RST

**Buffer Reset**

2

When this bit is set to one, the Channel Buffer is emptied on the next clock cycle. The L64111 does not reset this bit to zero after emptying the Channel Buffer. The default value for this bit upon system reset is zero. Note that the L64111 empties the Channel Buffer when RESET is asserted or SOFT\_RST is set to one.

#### SOFT\_RST

#### **Soft System Reset**

1

Setting this bit to one causes the L64111 to reset itself on the next clock cycle. After resetting itself, the L64111 sets this bit to zero. The default value for this bit upon system reset is zero. The value used by the L64111 to determine reset is the logical OR of the RESET pin and the SOFT\_RESET bit.

Registers 4-5

#### **STARTI**

#### **Decoder Start**

When this bit is one, the decoder functional block starts on the next clock cycle. If the Channel Buffer is empty, the decoder does not start until the Channel Buffer has received data. If this bit and the STARTI input pin are both HIGH, the decoder is enabled, and starts to play. When this bit is zero, the decoder is reset on the next cycle. The default value for this bit upon system reset is the state of the STARTI pin.

## **Control Register 2**

Control Register 2 is an eight-bit register accessed through Controller Interface data bits D[7:0]. It is used to set up and control various functions as described in following paragraphs.

Address  $A[4:0] = 00010_2$

| <br>7  | 6   | 5         | 4            | 3          | 2   | 1      | 0   |

|--------|-----|-----------|--------------|------------|-----|--------|-----|

| MUTE[1 | :0] | SOFT_MUTE | SEL_16/8_BIT | AUDIO ONLY | I2S | РСМ МО | DDE |

## MUTE[1:0]

#### Mute Control

[7:6]

This field determines the decoder's response to errors. An error occurs if any of the following conditions are detected: CRC errors, grammar errors in input data, or assertion of the ERROR input pin. The Play Director uses these two bits as follows:

#### MUTE[1:0] Description

|    | <u>-                                      </u>                     |

|----|--------------------------------------------------------------------|

| 00 | Errors are ignored                                                 |

| 01 | On error, PCM output is muted                                      |

| 10 | On error, the error is concealed by replaying the last valid frame |

| 11 | Reserved. Do not use this value.                                   |

The default value for this field upon system reset is  $00_2$ .

#### **SOFT\_MUTE** Software Controlled Mute

5

When this bit is set to one, the L64111 forces the PCM output to zero, which mutes the output. Hard mute operation is controlled by the logical OR of the SOFT\_MUTE bit and the HDMUTE pin. The default value for this bit upon system reset is zero. When read, the value of SOFT\_MUTE is the logical OR of the SOFT\_MUTE bit and the HDMUTE pin.

## SEL\_16/8\_BIT Data Width Select

When this bit is one, the L64111 accepts 16-bit wide data on D[15:0]. When this bit is zero, the L64111 accepts 8-bit wide data on D[7:0] and ignores data bits D[15:8]. The L64111 only uses the 16-bit format for MPEG data; all control registers are eight bits wide. The default value for this bit upon system reset is zero.

## **AUDIO ONLY Audio Only**

3

4

When this bit is one, the L64111 assumes that the input data stream is an MPEG audio stream. When this bit is zero, the L64111 assumes that input data is an ISO System Stream requiring full system processing to retrieve MPEG audio frames. Upon system reset, the value of this bit is set to the value of address line A4, which allows mode selection for stand-alone operation.

## I2S I2S Protocol

2

When this bit is one, the L64111 produces an I2S compatible protocol on the PCM output by delaying the data bit one SCLK cycle with respect to LRCLK. When this bit is zero, the PCM output is in standard mode.

#### **PCM MODE**

## **PCM Output Mode**

[1:0]

These bits modify the PCM output in accordance with the table shown below. In each of the three PCM modes, the data is bit serial MSB first with sign extended. See the subsection entitled "Setting the PCM Output Mode" in Chapter 6 for more information.

| 1 0111 1110 22 [210] |          |

|----------------------|----------|

| 00                   | 32 fs    |

| 01                   | 64 fs    |

| 10                   | 48 fs    |

| 11                   | Reserved |

## Control Register 3

Control Register 3 is an eight-bit register accessed through Controller Interface data bits D[7:0] that selects an audio channel from the incoming data stream

Address  $A[4:0] = 00011_2$

| 7                      | 6    | 5    | 4 | 3     | 2            | 1      | 0 |

|------------------------|------|------|---|-------|--------------|--------|---|

| AUDIO_STREAM_ID_IGNORE | RESE | RVED |   | AUDIO | _STREAM_IDEN | TIFIER |   |

#### AUDIO\_STREAM\_ID\_IGNORE

## Ignore Audio Stream Identifier

7 When this bit is one, the L64111 responds to all audio streams and ignores the AUDIO\_STREAM\_IDENTIFIER value on bits [4:0]. When this bit is zero, the L64111 decodes only the audio streams with the audio ID value given in bits [4:0]. The default value of this bit upon system reset is one.

#### RESERVED Reserved

[6:5]

Set these bits to zero to maintain compatibility with future revisions.

## AUDIO\_STREAM\_IDENTIFIER

## **Audio Stream Identifier**

[4:0]

The MPEG stream contains a packet start code with a five-bit audio stream identifier. A system controller may write to this register field to program the L64111 to respond only to the specified audio stream. Upon switching streams, resynchronization takes place automatically. The time taken depends on the nature of the bitstream and the number of times the L64111 finds an emulated sync code before finding an actual sync code. Once an actual sync code is found, the L64111 synchronizes within three frames. These bits are ignored if operating with an audio stream only.

## 4.4 Interrupt Registers

Registers at addresses 4 and 5 provide monitoring and control of interrupts. The L64111 is capable of generating individually maskable interrupts in response to various internal events. An interrupt is enabled by writing a one to the location corresponding to a particular interrupt status bit. Writing a zero disables that interrupt. After a system reset, all interrupts are disabled.

When the system controller services an interrupt, it must read both registers because reading either of the registers deasserts the INTR output.

## Interrupt Mask and Status Register 1

Interrupt Mask and Status Register 1 are eight-bit registers accessed through Controller Interface bits D[7:0]. They monitor the L64111's current status. A write to this location writes to Interrupt Mask 1. A read from this location reads Status Register 1. The Status Register 1 fields are defined following the registers.

Interrupt Mask 1 (Write Only)

Address  $A[4:0] = 00100_2$

| 7 6                                |          | 5                                   | 4        | 3            | 2         | 0                  |

|------------------------------------|----------|-------------------------------------|----------|--------------|-----------|--------------------|

| ANC DATA VALID ANC DATA FIFO OV    |          | ANC DATA FIFO HFF                   | RESERVED | ERR BUF OVFL | R         | ESERVED            |

|                                    | Status F | Register 1 (Read                    | l Only)  |              | Address A | $A[4:0] = 00100_2$ |

| 7                                  | 6        | 5                                   | 4        | 3            | 2         | 0                  |

| ANC DATA VALID ANC DATA FIFO OVRFL |          | FL ANC DATA FIFO HFF 0 ERR BUF OVEL |          | ERR BUF OVFL |           | 0                  |

## ANC DATA VALID

## **Ancillary Data In FIFO is Valid**

7

When set to one, this bit indicates that the Ancillary Data FIFO contains valid data. This bit does not cause an interrupt unless the Ancillary Data FIFO was previously empty. This bit continues to reflect the status of the Ancillary Data FIFO after Status Register 1 has been read and also after the FIFO has been read. A zero in this bit indicates that the Ancillary Data FIFO contains no data. Bit 7 in Interrupt Mask 1 masks this bit.

#### ANC DATA FIFO OVRFL

#### **Ancillary Data In FIFO Overflowed**

6

When set to one, this bit indicates that the Ancillary Data FIFO contains valid data and the FIFO is full, resulting in overflow.

Registers

This bit causes a single interrupt when the FIFO starts to overflow and does not interrupt again until the FIFO has been read from and starts to overflow again. This bit continues to reflect the status of the Ancillary Data FIFO after Status Register 1 has been read. Bit 6 in Interrupt Mask 1 masks this bit.

#### ANC DATA FIFO HFF

## **Ancillary Data FIFO Half Full Flag**

5

When set to one, this bit indicates that the Ancillary Data FIFO is half full. Data may be lost if the FIFO is not read soon. This bit causes a single interrupt each time the FIFO passes over the half-full threshold in the high direction; another interrupt will not occur until the FIFO has been read, drops below, and then recrosses the half-full threshold. This bit continues to reflect the status of the Ancillary Data FIFO after Status Register 1 has been read. Bit 5 in Interrupt Mask 1 masks this bit.

#### RESERVED

#### Reserved

4, [2:0]

Set these bits to zero to maintain software compatibility with future revisions.

#### ERR BUFF OVFL

## **Channel Buffer Overflow Error**

3

When set to one, this bit indicates that the Channel Buffer has overflowed and data is being lost. Channel Buffer overflow is an error that results in missing samples in the PCM output. The effect may or may not be audible. Bit 3 in Interrupt Mask 1 masks this bit.

Interrupt Mask and Status Register 2 Interrupt Mask and Status Register 2 are eight-bit registers accessed through Controller Interface data bits D[7:0]. They monitor the L64111's current status. A write to this location writes to Interrupt Mask 2. A read from this location reads Status Register 2.

Interrupt Mask 2 (Write Only)

Address  $A[4:0] = 00101_2$

|          |        | <u> </u>      | 5        | 4        |                 | 2       | 1             | 0          |

|----------|--------|---------------|----------|----------|-----------------|---------|---------------|------------|

| SYNTAX E | RR DET | PTS AVAILABLE | SYNC AUD | SYNC SYS | FRAME DETECT IN | CRC ERR | NEW FRAME OUT | LAST FRAME |

Status Register 2 (Read Only)

Address  $A[4:0] = 00101_2$

| 7 | 6              | 5             | 4        | 3        | 2               | 1       | 0                        |

|---|----------------|---------------|----------|----------|-----------------|---------|--------------------------|

| 0 | SYNTAX ERR DET | PTS AVAILABLE | SYNC AUD | SYNC SYS | FRAME DETECT IN | CRC ERR | NEW FRAME OUT/LAST FRAME |

The Status Register 2 fields are defined below. Each field has a corresponding mask in the Interrupt Mask 2 Register.

0

0

This bit reads as a zero.

#### SYNTAX ERR DET

#### **Syntax Error Detected**

6

7

When set to one, this bit indicates that the L64111 has detected a syntax error in either the ISO System Stream or in the audio stream. Bit 7 in Interrupt Mask 2 masks this bit.

#### PTS AVAILABLE

## Presentation Time Stamp Available

5

When set to one, this bit indicates that the Presentation Time Stamp register contains a valid time stamp. The L64111 generates an interrupt only when this bit goes from zero to one. Bit 6 in Interrupt Mask 2 masks this bit.

## SYNC AUD Synchronized Audio

4

When set to one, this bit indicates that the L64111 is synchronized to the audio stream. The L64111 is considered synchronized after it has seen audio sync patterns in the correct location within three successive audio frames. The L64111 generates an interrupt when this bit goes from zero to one. Bit 5 in Interrupt Mask 2 masks this bit.

## SYNC SYS Synchronized System

3

When set to one, this bit indicates that the L64111 is synchronized to the system stream. The L64111 is considered synchronized after it has seen three consecutive system sync patterns in the correct location within the ISO System Stream. The L64111 generates an interrupt when this bit goes from zero to one. Bit 4 in Interrupt Mask 2 masks this bit.

#### FRAME DETECT IN

#### Frame Detect Input

2

When set to one, this bit indicates that a new frame is being processed. The parametric data word is valid and can be read for that frame. Bit 3 in Interrupt Mask 2 masks this bit.

#### CRC ERR

#### **CRC Error**

1

This bit is set to one when a CRC error has been detected. When an audio frame has a CRC error, the L64111 attaches its own internal flag to that frame's data and uses the flag to identify the frame as one having an error. Refer to the MUTE field description on page 4-6 for an example. Bit 2 in Interrupt Mask 2 masks this bit.

#### NEW FRAME OUT/LAST FRAME

## New Frame/Last Frame on Output

0

When set to one, this bit indicates that the L64111 has completed a frame and either the frame is being sent to the PCM output (New Frame Out) or there is only one frame in the channel buffer (Last Frame). The L64111 generates an interrupt when this bit goes from zero to one. Bit 1 in Interrupt Mask 2 masks the NEW FRAME OUT interrupt. Bit 0 in Interrupt Mask 2 masks the LAST FRAME interrupt.

## 4.5 Timer Countdown and Offset Registers

The following registers set the PCM Serial Output Clock (SCLKO) rate:

- Timer Countdown Register (TCR)

- Timer Offset Register High (TORH)

- Timer Offset Register Low (TORL)

The four-bit value in the TCR register is used as a terminal count. The 16-bit value formed from the TORH and TORL registers is used as the correction fraction, which is covered in more detail in Chapter 6.

Timer Countdown Register (TCR) The TCR register provides the Terminal Count value, which determines the SCLKO clock rate. SCLKO makes one transition for every n transitions of SYSCLK. The value of n must be loaded into TCR[3:0].

Address  $A[4:0] = 00110_2$

| 7 | 6    | 5    | 4 | 3 | 0  |

|---|------|------|---|---|----|

|   | RESE | RVED |   |   | CR |

Timer Offset Register High (TORH)

The TORH register stores the eight most significant bits of the 16-bit word that contains the fractional part of the PCM timer. Note that the decimal point is located just prior to bit seven of the TORH register. TORH and TORL together provide the fractional portion of the PCM timer. The TCR register provides the integer portion of the SCLKO rate.

Address  $A[4:0] = 00111_2$

| DEC PT | 7 | 6   | 5 | 4    | 3       | 2 | 1 | 0 |  |  |  |

|--------|---|-----|---|------|---------|---|---|---|--|--|--|

|        |   |     | - | TORH | I[15:8] |   |   |   |  |  |  |

|        |   | • • |   |      |         |   |   |   |  |  |  |

Timer Offset Register Low (TORL) The TORL register stores the least-significant fractional part of the PCM timer. TORL is accessed using Controller Interface bits D[7:0].

Address  $A[4:0] = 01000_2$

| 7 | 6 | 5 | 4   | 3       | 2 | 1 | 0 |

|---|---|---|-----|---------|---|---|---|

|   |   |   | TOR | IL[7:0] |   |   |   |

## 4.6 Parametric Data Word Registers

There are three eight-bit Parametric Data Word registers that contain the 20 header bits of the MPEG packet remaining after the 12-bit sync word 0xFFF has been stripped out. Each register can be read through Controller Interface data bits D[7:0]. The data in the Parametric Data Word registers is valid when the FRAME DETECT IN bit of Interrupt and Status Register 2 is set HIGH.

Note that the data must be read before the next frame overwrites it. The data remains valid for a minimum of seven milliseconds after the FRAME DETECT IN flag in Interrupt and Status Register 2 goes high. Reading the FRAME DETECT IN bit in the register again to determine if the data is still valid is not sufficient, since the FRAME DETECT IN bit goes HIGH only after the Parametric Data has been overwritten.

## Parametric Data Word Register 1

The Parametric Data Register 1 contains the audio frame header data parsed from the stream. For complete details, consult ISO CD 11172-3.

Address  $A[4:0] = 01001_2$

| 7  | 6    | 5       | 4              | 3 |                | 0 |

|----|------|---------|----------------|---|----------------|---|

| ID | Laye | r [1:0] | protection_bit |   | bit_rate_index |   |

#### ID **Coding Type ID**

The ID bit indicates the ID of the algorithm. A one indicates MPEG; a zero indicates non-MPEG.

#### Layer [1:0] Layer ID Number

[6:5]

The Layer field indicates the MPEG Layer used. The following table lists the encoding of the Layer field. The L64111 flags a syntax error if it sees Layer ID = 00 or 01.

| Layer ID | Layer     |

|----------|-----------|

| 11       | Layer I   |

| 10       | Layer II  |

| 01       | Layer III |

| 00       | Reserved  |

## protection\_bit Protection

This bit indicates whether CRC has been added to the audio bitstream. The L64111 can not detect CRC errors unless this bit is cleared to zero by the encoder.

## bit\_rate\_index Bit Rate Index

[3:0]

The bit\_rate\_index bit provides a pointer into a table indicating the bit rate. The table provides different values for a given pointer depending on the MPEG Layer. Illegal combinations of bit rate index, layer, and channel mode produce a syntax error on the L64111.

| Index | Layer 1 Bit<br>Rate | Layer 2 Bit<br>Rate |

|-------|---------------------|---------------------|

| 0000  | free format         | free format         |

| 0001  | 32                  | 32 🕇                |

| 0010  | 64                  | 48 🕇                |

| 0011  | 96                  | 56 🕇                |

| 0100  | 128                 | 64                  |

| 0101  | 160                 | 80 🕇                |

| 0110  | 192                 | 96                  |

| 0111  | 224                 | 112                 |

| 1000  | 256                 | 128                 |

| 1001  | 288                 | 160                 |

| 1010  | 320                 | 192                 |

| 1011  | 352                 | 224 ‡               |

| 1100  | 384                 | 256 ‡               |

| 1101  | 416                 | 320 ‡               |

| 1110  | 448                 | 384 ‡               |

| 1111  | reserved            | reserved            |

## Parametric Data Word Register 2

Parametric Data Register 2 contains additional audio frame header data parsed from the stream. For additional details, consult ISO CD 11172-3.

Address  $A[4:0] = 01010_2$

| 7                        | 6 | 5           | 4             | 3    | 2       | 11       | 0            |

|--------------------------|---|-------------|---------------|------|---------|----------|--------------|

| sampling_frequency [1:0] |   | padding_bit | extension_bit | mode | e [1:0] | mode_ext | ension [1:0] |

## sampling\_frequency [1:0]

## Sampling Frequency ID

[7:6]

This two-bit field indicates the sampling frequency as follows:

| sampling_<br>frequency | Frequency |

|------------------------|-----------|

| 00                     | 44.1 KHz  |

| 01                     | 48 KHz    |

| 10                     | 32 KHz    |

| 11                     | Reserved  |

<sup>1. †</sup> Mono (single channel) only. 2.‡ Stereo, intensity stereo, dual channel only.

mode [1:0]

padding\_bit Padding 5

For MPEG stream decoder internal use.

extension\_bit Extension

The value in this field is not used.

Channel Mode [3:2]

Indicates the channel mode as follows:

| Mode | Channel Mode Used                                |

|------|--------------------------------------------------|

| 00   | Stereo                                           |

| 01   | Joint stereo (intensity stereo and/or ms stereo) |

| 10   | Dual channel                                     |

| 11   | Single channel                                   |

#### mode\_extension [1:0]

#### **Mode Extension**

[1:0]

This field is used in joint stereo mode. In Layer I and II this field indicates which subbands are in intensity stereo. All other subbands are coded in stereo.

| Mode_Extension | Subbands                  |  |  |  |  |

|----------------|---------------------------|--|--|--|--|

| 00             | 4-31 in intensity stereo  |  |  |  |  |

| 01             | 8-31 in intensity stereo  |  |  |  |  |

| 10             | 12-31 in intensity stereo |  |  |  |  |

| 11             | 16-31 in intensity stereo |  |  |  |  |

Parametric Data Word Register 3 Parametric Data Register 3 contains additional audio frame header data parsed from the stream. For more details, consult ISO CD 11172-3.

Address  $A[4:0] = 01011_2$

| 7         | 6             | 5     | 4         | 3 |          | 0 |

|-----------|---------------|-------|-----------|---|----------|---|

| copyright | original/home | empha | sis [1:0] |   | Reserved |   |

copyright Copyright Flag

7

A one in this bit indicates that the data is copyrighted. A zero indicates that the coded bitstream is not copyright protected.

original/home Originator Copy

6

A one in this bit indicates that the bitstream contains original data. A zero indicates that the bitstream is a copy.

emphasis Emphasis

This field indicates the type of de-emphasis to be used:

[5:4]

| Emphasis | Type of De-emphasis to Use |

|----------|----------------------------|

| 00       | No emphasis                |

| 01       | 50/15 microsecond emphasis |

| 10       | Reserved                   |

| 11       | CCITT J.17                 |

Reserved [3:0]

Reserved for future use.

## 4.7 Presentation Time Stamp (PTS) Registers

These five eight-bit registers contain the current Presentation Time Stamp. Each register may be read through Controller Interface data bits D[7:0]. This data is valid when the PTS AVAILABLE field, is set HIGH. It is overwritten when the next presentation time stamp is parsed. The data stored here is as specified in Section 2.4.3 of the MPEG Systems CD 11172-1. This data is only valid if the L64111 is decoding a system stream, and is synchronized to that stream.

| Address<br>A[4:0] | Register<br># | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------------|---------------|---|------------|---|---|---|---|---|---|--|

| 011002            | PTS1          |   | pts[7:0]   |   |   |   |   |   |   |  |

| 011012            | PTS2          |   | pts[15:8]  |   |   |   |   |   |   |  |

| 011102            | PTS3          |   | pts[23:16] |   |   |   |   |   |   |  |

| 011112            | PTS4          |   | pts[31:24] |   |   |   |   |   |   |  |

| 100002            | PTS5          |   | 0 pts32    |   |   |   |   |   |   |  |

## 4.8 Ancillary/User Data FIFO

This eight-bit register represents the top of a 16 by 8 bit FIFO that contains any Ancillary/User data from the current stream. Successive reads from this register will read the next byte in the FIFO.

The FIFO is filled in MSB order, that is, the first bit in the stream becomes bit 7 on the top of the FIFO, the second bit in the stream becomes bit 6 in the top of the FIFO, and so on. The ninth bit in the stream becomes bit 7 in