# S3F49DAX

# MultiMediaCard Controllers

Datasheet

**Revision 1.0**

# PRODUCT OVERVIEW

S3F49DAX 16/32-bit RISC microprocessor would be designed to provide a cost-effective, low power, small die size and high performance micro-controller solution for Low voltage MMC (MultiMediaCard). To reduce total system cost, S3F49DAX also provides the followings: 16K Byte SRAM, 48K Byte Internal NOR Flash memory, NAND Flash controller, interrupt controller, 2-channel DMA (Direct Memory Access), 3-channel Timer and Analog block including IVC (Internal Voltage Converter), POR (Power-On Reset) and RCOSC (RC Oscillator).

S3F49DAX microprocessor would be developed using an ARM7TDMI-S core, 0.18um CMOS standard cells housed in 64UELP package. And S3F49DAX adopts the new bus architecture, AMBA 2.0 (Advanced Micro-controller Bus Architecture).

The integrated on-chip functions that are described in this document include:

- Compliant with MMC (MultiMediaCard) system specification version 3.3

- Built in internal memory: 48K Byte NOR Flash for program, 16K Byte SRAM for data buffer and stack

- Integrated NAND Flash memory controller

- Built in ECC (Error Correction Code) Engine.

- Two-channel DMA (Direct Memory Access)

- Three-channel Timer and one-channel UART with interrupt-based operation

- Interrupt controller: 21 interrupt sources

- Power control: Normal, Slow and Standby mode

- Built in analog function block: POR (Power-On Reset), RCOSC (RC Oscillator) and IVC (Internal Voltage Converter)

# FEATURES

#### Architecture

- Integrated system for Low Voltage MMC (MultiMediaCard).

- 16/32-bit RISC architecture and powerful instruction set with ARM7TDMI-S CPU core.

- Internal AMBA (Advanced Micro-controller Bus Architecture, AMBA 2.0)

#### ARM7TDMI-S

- Supports fixed little endian mode.

- 32/16-bit RISC architecture. (ARM V4T)

- 32-bit ARM instruction set for maximum performance and flexibility

- 16-bit Thumb instruction set for increased code density

- Coprocessor Interface / JTAG debug interface unit

#### **MMC Interface**

- Fully compliant with MultiMediaCard specification version 3.3

- Supports MMC (MultiMediaCard) mode and SPI mode.

- Supports command classes which are class 0, 2, 4, 5, 6, 7

- CRC (Cyclic Redundancy Check) bits generation and check

#### NAND Flash Memory Controller

- Supports variable capacity NAND Flash memory.

- Supports low voltage NAND Flash memory (Operating voltage range of NAND Flash: 1.65 V to 1.95 V)

- Supports up to Two NAND flash memories extension.

#### NOR Flash Memory Controller

- Built in 48K Byte NOR Flash memory.

- Supports two type programming mode: User programming mode, Tool programming mode

- Supports three type data protection: Read Protection, LD Protection, Hardware Protection

- Supports Byte Programming/Option Sector Programming/Chip Erase/Sector Erase/Verify Sequence.

#### **SRAM Memory Controller**

• Built in 16K Byte SRAM memory for FTL map table, ECC, Global variables, Stack & Heap area.

#### Interrupt Controller

- Supports normal or fast interrupt modes (IRQ, FIQ)

- Supports vectored interrupts (Hard-wired Interrupt)

- S/W programmable interrupt priority.

#### DMA (Direct Memory Access)

Two dedicated DMA (Host I/F DMA, NAND Flash I/F DMA)

#### Timer

- One-channel 16-bit timer & 32-bit timer.

- Watch-dog Timer

- Interrupt-based operation (Support interval mode)

#### UART

- One-channel UART with interrupt-based operation

- Programmable baud rate.

#### DES / T-DES

- Built-in hardware DES

- Four keys for encryption and decryption

- Start / Stop control

#### **Random Number Generator**

- One 16-bit random number generator in accordance with FIPS140-2

- Start / Stop Control

### **Analog Function Block**

- Built-in RCOSC (RC Oscillator): 18 MHz @ 1.8 V

- Built-in POR (Power-on Reset) and LVD (Low Voltage Detector)

- Built-in IVC: 3.3 V to 1.8 V

#### **Operating Frequency**

• 18 MHz ± 3 MHz (RCOSC Output Frequency)

#### **Operating Voltage**

- Internal Logic: 1.65 V to 1.95 V

- I/O: 1.65 V to 3.6 V

- NAND flash interface: 1.65 V to 3.6 V

- In case of high voltage MMC, You must use the interface power (2.7 V to 3.6 V).

#### **Operating Temperature**

• Regular specification: -25 °C to +85 °C

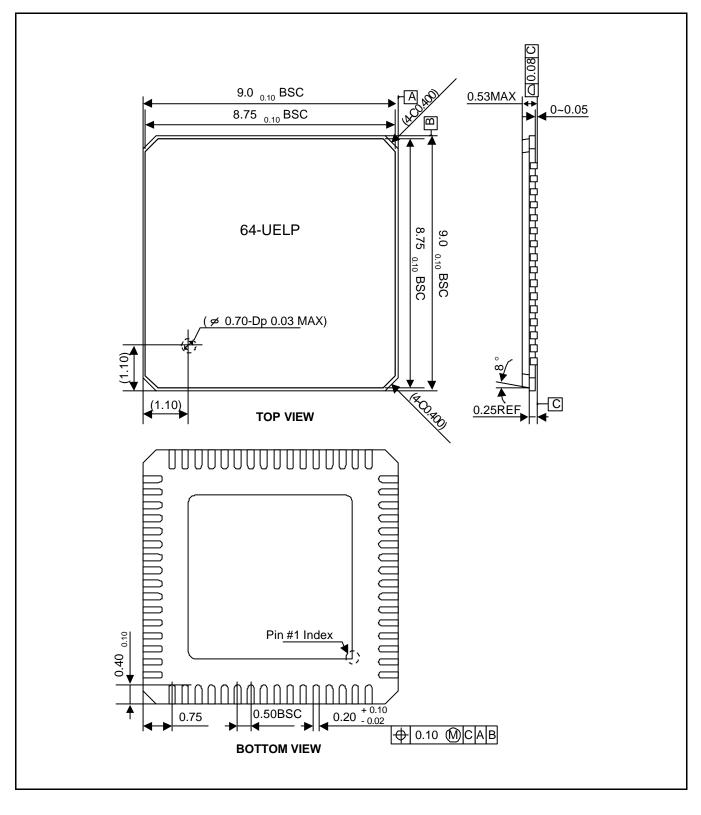

### Package Type

• 64-pin UELP

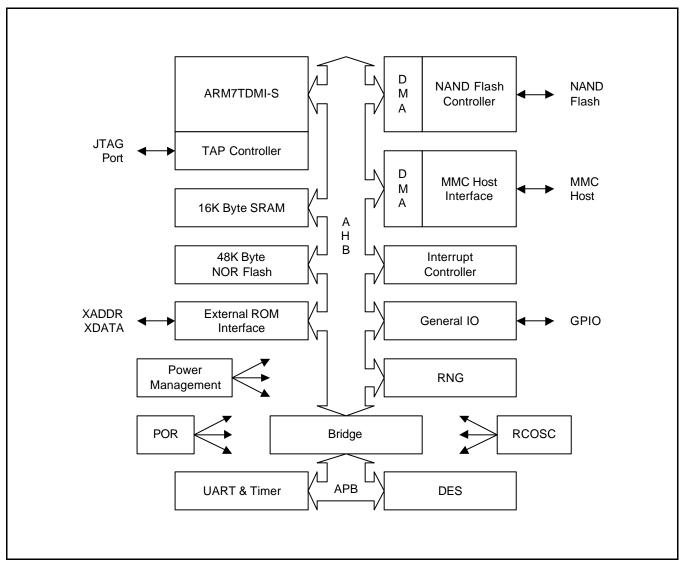

# **BLOCK DIAGRAM**

Figure 1. S3C49DAX Block Diagram

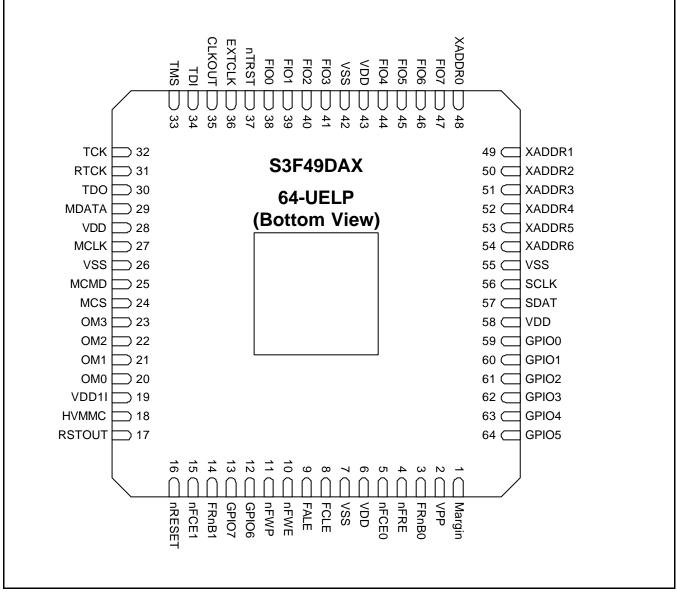

# **PIN ASSIGNMENTS**

#### Figure 2. S3F49DAX Pin Assignments

| Pin No | Pin Name     | Function                                      | I/O State | I/O Type  |

|--------|--------------|-----------------------------------------------|-----------|-----------|

| 1      | Margin       | Internal NOR flash cell margin test           | I         | phia      |

| 2      | VPP          | Internal NOR flash program power              | I         | vpp12     |

| 3      | FRnB0        | NAND flash memory ready/busy signal 0         | I         | phicu10   |

| 4      | nFRE         | NAND flash memory read enable signal          | 0         | phmbct    |

| 5      | nFCE0        | NAND flash memory chip enable signal 0        | 0         | phmbct    |

| 6      | VDD          | MMC power                                     | Р         | vdd3io    |

| 7      | VSS          | MMC ground                                    | G         | vss3io    |

| 8      | FCLE         | NAND flash memory command latch enable signal | 0         | phmbct    |

| 9      | FALE         | NAND flash memory address latch enable signal | 0         | phmbct    |

| 10     | nFWE         | NAND flash memory write enable signal         | 0         | phmbct    |

| 11     | nFWP         | NAND flash memory write protect signal        | 0         | phmbct    |

| 12     | GPIO6/XDATA6 | General IO port 6/External ROM data 6         | I/O       | phbcu60t  |

| 13     | GPIO7/XDATA7 | General IO port 7/External ROM data 7         | I/O       | phbcu60t  |

| 14     | FRnB1        | NAND flash memory ready/busy signal 1         | I         | phicu10   |

| 15     | nFCE1        | NAND flash memory chip enable signal 1        | 0         | phmbct    |

| 16     | nRESET       | Global reset input for the S3F49DAX           | I         | phicu60   |

| 17     | RSTOUT       | Internal POR monitoring output                | 0         | phob4     |

| 18     | HVMMC        | High voltage MMC select                       | 0         | phic      |

| 19     | IVCOUT       | Internal V <sub>DD</sub> (1.8V)               | Р         | vdd1i     |

| 20     | OM0          | Operation mode select 0                       | I         | phic      |

| 21     | OM1          | Operation mode select 1                       | I         | phic      |

| 22     | OM2          | Operation mode select 2                       | I         | phic      |

| 23     | OM3          | Operation mode select 3                       | I         | phic      |

| 24     | MCS          | MMC card select signal for SPI mode           | I         | phmicu60  |

| 25     | MCMD         | MMC command signal                            | I/O       | phmbcu10t |

| 26     | VSS          | MMC ground                                    | G         | vss3io    |

| 27     | MCLK         | MMC clock signal                              | I         | phmic     |

| 28     | VDD          | MMC power                                     | Р         | vdd3io    |

| 29     | MDATA        | MMC data signal                               | I/O       | phmbcu60t |

| 30     | TDO          | TAP controller data output                    | 0         | phob      |

| 31     | RTCK         | Returned TCK                                  | 0         | phob      |

| 32     | TDI          | TAP controller data input                     | I         | phicu60   |

Table 1. 64-Pin ELP Pin Assignment

| Pin No | Pin Name     | Function                                     | I/O State | I/O Type |

|--------|--------------|----------------------------------------------|-----------|----------|

| 33     | TMS          | TAP controller mode select                   | I         | phicu60  |

| 34     | TDI          | TAP controller data input                    | I         | phicu60  |

| 35     | CLKOUT       | Internal VCO clock monitoring output         | 0         | phob     |

| 36     | EXTCLK       | External clock input                         | I         | phic     |

| 37     | nTRST        | TAP controller reset                         | I         | phicu60  |

| 38     | FIO0         | NAND flash memory IO signal 0                | I/O       | phmbct   |

| 39     | FIO1         | NAND flash memory IO signal 1                | I/O       | phmbct   |

| 40     | FIO2         | NAND flash memory IO signal 2                | I/O       | phmbct   |

| 41     | FIO3         | NAND flash memory IO signal 3                | I/O       | phmbct   |

| 42     | VSS          | MMC ground                                   | G         | vss3io   |

| 43     | VDD          | MMC power                                    | Р         | vdd3io   |

| 44     | FIO4         | NAND flash memory IO signal 4                | I/O       | phmbct   |

| 45     | FIO5         | NAND flash memory IO signal 5                | I/O       | phmbct   |

| 46     | FIO6         | NAND flash memory IO signal 6                | I/O       | phmbct   |

| 47     | FIO7         | NAND flash memory IO signal 7                | I/O       | phmbct   |

| 48     | XADDR0       | External ROM address 0 out for test          | I/O       | phob     |

| 49     | XADDR1       | External ROM address 1 out for test          | I/O       | phob     |

| 50     | XADDR2       | External ROM address 2 out for test          | I/O       | phob     |

| 51     | XADDR3       | External ROM address 3 out for test          | I/O       | phob     |

| 52     | XADDR4       | External ROM address 4 out for test          | I/O       | phob     |

| 53     | XADDR5       | External ROM address 5 out for test          | I/O       | phob     |

| 54     | XADDR6       | External ROM address 6 out for test          | I/O       | phob     |

| 55     | VSS          | MMC ground                                   | G         | vss3io   |

| 56     | SCLK         | Serial clock input for NOR Flash programming | I         | phicu60  |

| 57     | SDAT         | Serial data signal for NOR Flash programming | I/O       | phbcu60t |

| 58     | VDD          | MMC power                                    | Р         | vdd3io   |

| 59     | GPIO0/XDATA0 | General IO port 0/External ROM data 0        | I/O       | phbcu60t |

| 60     | GPIO1/XDATA1 | General IO port 1/External ROM data 1        | I/O       | phbcu60t |

| 61     | GPIO2/XDATA2 | General IO port 2/External ROM data 2        | I/O       | phbcu60t |

| 62     | GPIO3/XDATA3 | General IO port 3/External ROM data 3        | I/O       | phbcu60t |

| 63     | GPIO4/XDATA4 | General IO port 4/External ROM data 4        | I/O       | phbcu60t |

| 64     | GPIO5/XDATA5 | General IO port 5/External ROM data 5        | I/O       | phbcu60t |

Table 1. 64-Pin ELP Pin Assignment (Continued)

| I/О Туре | Description                                                                                          |

|----------|------------------------------------------------------------------------------------------------------|

| phia     | High voltage analog input buffer                                                                     |

| phic     | High voltage CMOS input buffer                                                                       |

| phicu60  | High voltage CMOS input buffer with pull-up resistor (60 k $\Omega$ )                                |

| phicu10  | High voltage CMOS input buffer with pull-up resistor (10 k $\Omega$ )                                |

| phmic    | High voltage CMOS MMC input buffer                                                                   |

| phob     | High voltage normal output buffer, Io = 4 mA                                                         |

| phmbct   | High voltage CMOS MMC input buffer and tri-stat output buffer                                        |

| phmbc60t | High voltage CMOS MMC input buffer with pull-up resistor (60 k $\Omega$ ) and tri-stat output buffer |

| phmbc10t | High voltage CMOS MMC input buffer with pull-up resistor (10 k $\Omega$ ) and tri-stat output buffer |

| vdd3io   | 3.3 V V <sub>DD</sub>                                                                                |

| vss3io   | Ground                                                                                               |

| vdd1i    | 1.8 V V <sub>DD</sub> (Internal Regulator Output)                                                    |

Table 2. I/O Type Description

# SIGNAL DESCRIPTIONS

| Signal           | I/O    | Description                                                                                                                                                      |  |  |  |  |  |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAND Flash Inte  | erface |                                                                                                                                                                  |  |  |  |  |  |

| FIO [7:0]        | I/O    | <b>Data Input/Output:</b> These pins are use to input data during read operations, and to output command, address and data.                                      |  |  |  |  |  |

| nFCE [1:0]       | 0      | Chip Enable: The nFCE output is the device selection control.                                                                                                    |  |  |  |  |  |

| FCLE             | 0      | <b>Command Latch Enable:</b> The FCLE output controls the activating path for commands to the NAND Flash.                                                        |  |  |  |  |  |

| FALE             | 0      | Address Latch Enable: The FALE output controls the activating path for address to NAND Flash                                                                     |  |  |  |  |  |

| nFRE             | 0      | <b>Read Enable:</b> The nFRE output controls the serial data-out from NAND Flash, and when active fetches the data onto the I/O bus.                             |  |  |  |  |  |

| nFWE             | 0      | Write Enable: The nFWE output controls writes to I/O port                                                                                                        |  |  |  |  |  |

| nFWP             | 0      | Write Protect: The nFWP signal provides inadvertent write/erase protection during power transitions.                                                             |  |  |  |  |  |

| FRnB[1:0]        | I      | <b>Ready/Busy:</b> These pins indicate the status of the NAND Flash operation. When low, indicates that a program, erase or random read operation is in process. |  |  |  |  |  |

| MMC Interface    |        |                                                                                                                                                                  |  |  |  |  |  |

| MCS              | 1      | MMC Card Select: Host to card chip select signal                                                                                                                 |  |  |  |  |  |

| MCMD             | I/O    | MMC Command: Host to/from card Command/Response signal                                                                                                           |  |  |  |  |  |

| MCLK             | I      | MMC Serial Clock: Host to Card clock signal                                                                                                                      |  |  |  |  |  |

| MDATA            | I/O    | MMC Data: Host to/from card data signal                                                                                                                          |  |  |  |  |  |

| Clock & Reset    |        |                                                                                                                                                                  |  |  |  |  |  |

| nRESET           | I      | External System Reset: This signal suspends any operation in progress.                                                                                           |  |  |  |  |  |

| RSTOUT           | 0      | Internal POR Output: This pin is used to check the Power-On Reset detect voltage.                                                                                |  |  |  |  |  |

| EXTCLK           | I      | External Clock Source: External clock input for test mode                                                                                                        |  |  |  |  |  |

| CLKOUT           | 0      | VCO Output: This pin is used to check the Internal VCO Characteristics                                                                                           |  |  |  |  |  |

| Special Interfac | е      |                                                                                                                                                                  |  |  |  |  |  |

| OM[3:0]          | I      | These pins determine status of product for manufacture test.                                                                                                     |  |  |  |  |  |

|                  |        | 0000 = Normal operation mode                                                                                                                                     |  |  |  |  |  |

| HVMMC            | I      | This pin is used to select high voltage MMC                                                                                                                      |  |  |  |  |  |

| GPIO [7:0]       | Ю      | General IO port                                                                                                                                                  |  |  |  |  |  |

| XADDR[6:0]       | 0      | External ROM Address: These pins are used to check manufacture test.                                                                                             |  |  |  |  |  |

| XDATA            | I/O    | External ROM data: These pins are used to check manufacture test.                                                                                                |  |  |  |  |  |

#### Table 3. S3F49DAX Signal Description

| Signal           | I/O | Description                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NOR Flash Interf | ace |                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SCLK             | I   | <b>Serial CLOCK:</b> This pin is used Tool program for internal Flash (Write speed: Max 250 kHz, Read speed: Max 3 MHz)                                                                                                                              |  |  |  |  |  |

| SDAT             | Ю   | <b>Serial DATA:</b> This pin is used Tool program for internal Flash (Output when reading, Input when writing.) Input & push-pull output port can be assigned.                                                                                       |  |  |  |  |  |

| VPP              | Р   | Flash cell writing power supply pin for tool program mode. The function of entering flash writing Mode.                                                                                                                                              |  |  |  |  |  |

| Margin           | Ι   | This pin can used the flash cell margin test                                                                                                                                                                                                         |  |  |  |  |  |

| JTAG Interface   |     |                                                                                                                                                                                                                                                      |  |  |  |  |  |

| nTRST            | I   | This pin (TAP Controller Reset) can reset the TAP controller at power-up. If the debugger is not used, this pin should be "Low" level or low active pulse should be applied before CPU running. For example, nRESET signal can be tied with this pin |  |  |  |  |  |

| TMS              | I   | This pin (TAP Controller Mode Select) can control the sequence of the state diagram of TAP controller                                                                                                                                                |  |  |  |  |  |

| ТСК              | I   | This pin (TAP Controller Clock) can provide the clock input for the JTAG logic                                                                                                                                                                       |  |  |  |  |  |

| RTCK             | 0   | This pin is the returned TCK                                                                                                                                                                                                                         |  |  |  |  |  |

| TDI              | Ι   | This pin (TAP Controller Data Input) is the serial input for JTAG port.                                                                                                                                                                              |  |  |  |  |  |

| TDO              | 0   | This Pin (TAP Controller Data Output) is the serial data output for JTAG port.                                                                                                                                                                       |  |  |  |  |  |

| Power            |     |                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IVCOUT           | Р   | IVC Out: This pin output the internal IVC Output voltage (1.8 V)                                                                                                                                                                                     |  |  |  |  |  |

| VDD              | Р   | Interface power supply                                                                                                                                                                                                                               |  |  |  |  |  |

| VSS              | Р   | Interface ground                                                                                                                                                                                                                                     |  |  |  |  |  |

Table 3. S3F49DAX Signal Description (Continuous)

# 1. MULTIMEDIACARD FUNCTION DESCTION

The MultiMediaCard system defines two communication protocols: MMC and SPI mode. All communication between host and card is controlled by the host. The card automatically selects the mode of the reset command and will operate all command to be in the same communication mode.

# MMC MODE

The basic MultiMediaCard concept is based on transferring data via a minimal number of signals. The communication signals are:

- **CLK:** with each cycle of this signal an one bit transfer on the command and data lines is done. The frequency may vary between zero and the maximum clock frequency.

- **CMD:** is a bi-directional command channel used for card initialization and data transfer commands. The CMD signal has two operation modes: open-drain for initialization mode and push-pull for fast command transfer. Commands are sent from the MultiMediaCard bus master to the card and responses from the cards to the host.

- **DAT:** is a bi-directional data channel. The DAT signal operates in push-pull mode. Only one card or the host is driving this signal at a time.

| Pin |      | MultiMe   | diaCard Mode          |      | SF   | PI Mode                  |

|-----|------|-----------|-----------------------|------|------|--------------------------|

| No  | Name | Type1     | Description           | Name | Туре | Description              |

| 1   | RSV  | NC        | Reserved              | CS   | I    | Chip select (Active Low) |

| 2   | CMD  | I/O/PP/OD | Command/Response      | DI   | I/PP | Data In                  |

| 3   | VSS1 | S         | Supply voltage ground | VSS  | S    | Supply voltage ground    |

| 4   | VDD  | S         | Supply voltage        | VDD  | S    | Supply voltage           |

| 5   | CLK  | I         | Clock                 | SCLK | I    | Clock                    |

| 6   | VSS2 | S         | Supply voltage ground | VSS2 | S    | Supply voltage ground    |

| 7   | DAT  | I/O/PP    | Data                  | DO   | O/PP | Data Out                 |

#### Table 4. MMC/SPI Interface Pin Configuration

NOTE: S: Power supply; I: Input; O: Output; PP: Push-pull; OD: Open-drain; NC: Not connected (or Logical high)

# **SPI MODE**

The SPI mode consists of a secondary, optional communication protocol which is offered by Flash-based MultiMediaCards. This mode is a subset of the MultiMediaCard protocol, designed to communicate with a SPI channel, commonly found in Motorola's (and lately a few other vendors') microcontrollers. The interface is selected during the first reset command after power up (CMD0) and cannot be changed once the part is powered on.

The SPI standard defines the physical link only, and not the complete data transfer protocol. The MultiMediaCard SPI implementation uses a subset of the MultiMediaCard protocol and command set. It is intended to be used by systems which require a small number of cards (typically one) and have lower data transfer rates (compared to MultiMediaCard protocol based systems). From the application point of view, the advantage of the SPI mode is the capability of using an off-the-shelf host, hence reducing the design-in effort to minimum.

The MultiMediaCard SPI interface is compatible with SPI hosts available on the market. As in any other SPI device, the MultiMediaCard SPI channel consists of the following four signals:

- CS: Host to card Chip Select signal.

- CLK: Host to card clock signal

- Dataln: Host to card data signal.

- DataOut: Card to host data signal.

# MULTIMEDIACARD PROTOCOL

#### MMC MODE

After a power-on reset, the card is initialized by MultiMediaCard bus protocol using the command channel. MultiMediaCard bus protocol is represented by one of the following tokens:

- **Command:** A command is a token, which starts an operation. A command is sent from the host either to a single card (addressed command) or to all connected cards (broadcast command). A command is transferred serially on the CMD line.

- **Response:** A response is a token, which is sent from an addressed card, or (synchronously) from all connected cards, to the host as an answer to a previously received command. A response is transferred serially on the CMD line.

- **Data:** Data can be transferred from the card to the host or vice versa. Data is transferred via the data line.

Card addressing is implemented using a session address assigned during the initialization phase, by the bus controller to all currently connected cards. Individual cards are identified by their CID number. This method requires that every card will have an unique CID number. To ensure uniqueness of CIDs the CID register contains 24 bits (MID and OID fields - see Chapter 5), which are defined by the MMCA. Every card manufacturers is required to apply for an unique MID (and optionally OID) number.

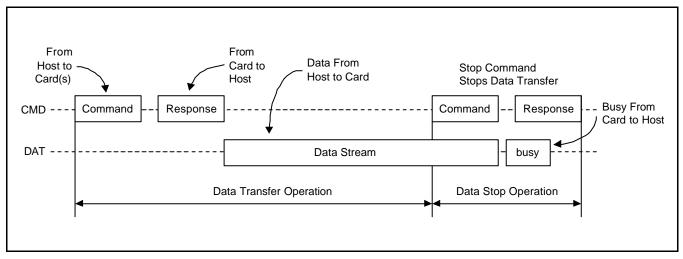

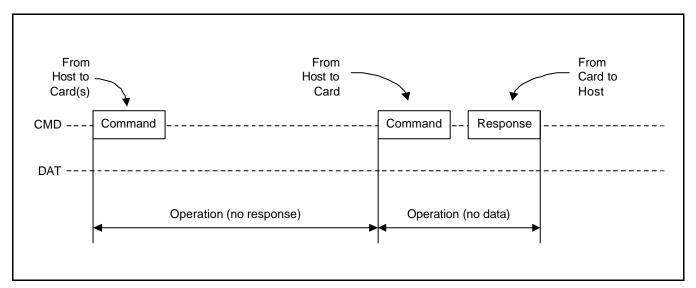

MultiMediaCard bus data transfers are composed of these tokens. One data transfer is a bus operation. There are different types of operations. Addressed operations always contain a command and a response token. In addition, some operations have a data token, the others transfer their information directly within the command or response structure. In this case no data token is present in an operation. The bits on the DAT and the CMD lines are transferred synchronous to the host clock.

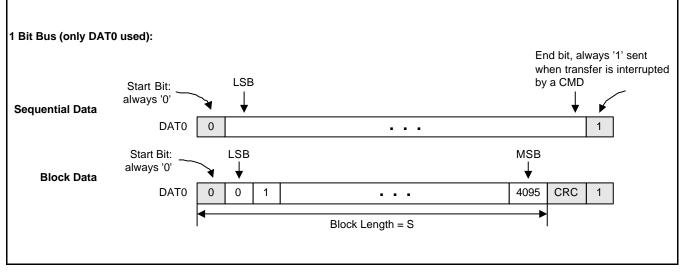

Two types of data transfer commands are defined:

- Sequential commands: These commands initiate a continuous data stream, they are terminated only when a stop command follows on the CMD line. This mode reduces the command overhead to an absolute minimum.

- Block-oriented commands: These commands send a data block succeeded by CRC bits. Both read and

write operations allow either single or multiple block transmission. A multiple block transmission is terminated

when a stop command follows on the CMD line similarly to the sequential read.

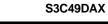

Figure 3. Sequential Read Operations

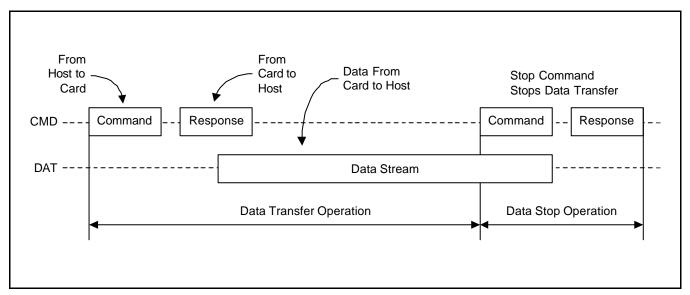

Figure 4. (Multiple) Block Read Operations

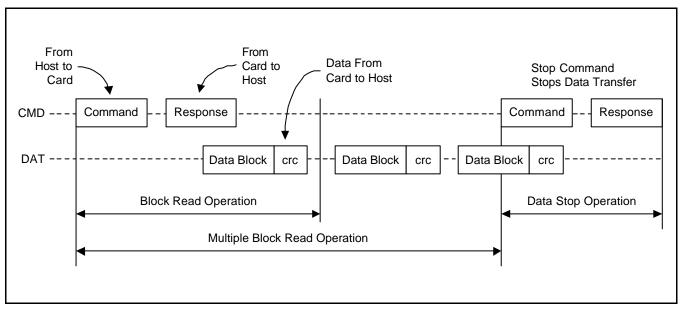

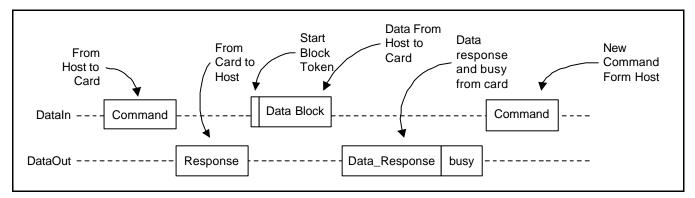

Figure 5. Sequential Write Operations

The block write operation uses a simple busy signalling of the write operation duration on the data (DAT) line. (see Figure6).

Figure 6. (Multiple) Block Write Operations

Figure 7. "No Response" and "No Data" Operations

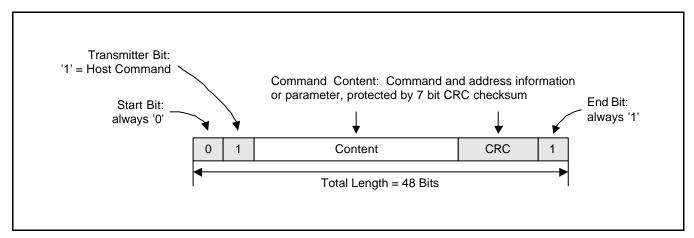

Command tokens have the following coding scheme:

Figure 8. Command Token Format

Each command token is preceded by a start bit ('0') and succeeded by an end bit ('1'). The total length is 48 bits. Each token is protected by CRC bits so that transmission errors can be detected and the operation may be repeated.

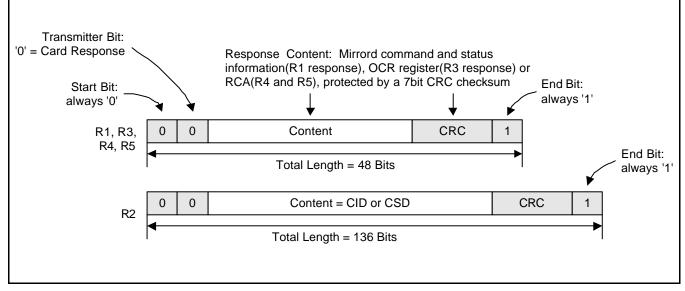

Response tokens have five coding schemes depending on their content. The token length is either 48 or 136 bits. The detailed commands and response definition is given in next sections. The CRC protection algorithm for block data is a 16 bits CCITT polynomial.

#### Figure 9. Response Token Format

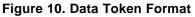

#### **SPI MODE**

While the MultiMediaCard channel is based on command and data bit streams, which are initiated by a start bit and terminated by a stop bit, the SPI channel is byte oriented. Every command or data block is built of 8-bit bytes and is byte aligned to the CS signal (i.e. the length is a multiple of 8 clock cycles).

Similar to the MultiMediaCard protocol, the SPI messages consist of command, response and data-block tokens (see Chapter 3 for a detailed description). All communication between host and cards is controlled by the host (master). The host starts every bus transaction by asserting the CS signal low.

The response behavior in the SPI mode differs from the MultiMediaCard mode in the following three aspects:

- The selected card always responds to the command.

- Additional (8, 16 & 40 bit) response structures are used

- When the card encounters a data retrieval problem, it will respond with an error response (which replaces the expected data block) rather than by a time-out, as in the MultiMediaCard mode.

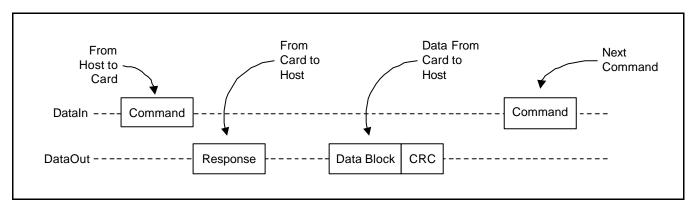

Only single and multiple block read/write operations are supported in SPI mode (sequential mode is not supported). In addition to the command response, every data block sent to the card during write operations will be responded to with a special data response token. A data block may be as big as one card write block and as small as a single byte. Partial block read/write operations are enabled by card options specified in the CSD register.

#### Data Read

The SPI mode supports single and multiple block read operations. The main difference between SPI and MultiMediaCard modes is that the data and the response are both transmitted to the host on the DataOut signal (refer to Figure11 and Figure12). Therefore the card response to the STOP\_COMMAND may cut-short and replace the last data block.

Figure 11. Single Block Read Operation

Figure 12. Multiple Block Read Operation

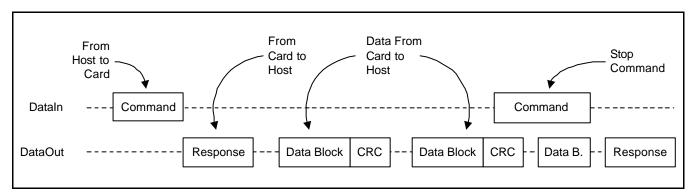

In case of a data retrieval error (e.g. out of range, address misalignment, internal error, etc.), the card will not transmit any data. Instead (as opposed to MultiMediaCard mode where the card times out), a special data error token will be sent to the host. Figure13 shows a single block read operation, which terminates with an error token rather than a data block.

Figure 13. Read Operation – Data Error

Multiple block read operation can be terminated the same way, the error token replacing a data block anywhere in the sequence. The host must than abort the operation by sending the stop transmission command.

If the host sends a stop transmission command after the card transmitted the last block of a multiple block read with a pre-defined number of blocks, it will be responded to as an illegal command.

If the host uses partial blocks whose accumulated length is not block aligned and block misalignment is not allowed, the card shall detect a block misalignment error condition at the beginning of the first misaligned block (ADDRESS\_ERROR error bit will is set in the data error token).

#### Data Write

The SPI mode supports single block and Multiple block write commands. Upon reception of a valid write command (CMD24 or CMD25), the card will respond with a response token and will wait for a data block to be sent from the host. CRC suffix, block length and start address restrictions are (with the exception of the CSD parameter WRITE\_BL\_PARTIAL controlling the partial block write option) identical to the read operation (see Figure14). If a CRC error is detected it will be reported in the data-response token and the data block will not be programmed.

Figure 14. Single Block Write Operation

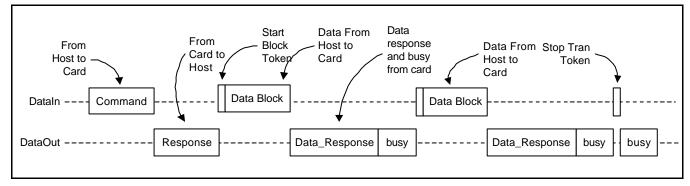

Every data block has a prefix of 'Start Block' token (one byte).

After a data block has been received, the card will respond with a data-response token. If the data block has been received without errors, it will be programmed. As long as the card is busy programming, a continuous stream of busy tokens will be sent to the host (effectively holding the DataOut line low).

In Multiple Block write operation the stop transmission will be done by sending 'Stop Tran' token instead of 'Start Block' token at the beginning of the next block.

Figure 15. Multiple Block Write Operation

# COMMANDS

#### **Command Types**

There are four kinds of commands defined to control the MultiMediaCard:

- Broadcast commands (bc), no response.

- Broadcast commands with response (bcr) response from all cards simultaneously.

- Addressed (point-to-point) commands (ac) no data transfer on DAT.

- Addressed (point-to-point) data transfer commands (adtc) data transfer on DAT

All commands and responses are sent over the CMD line of the MultiMediaCard bus. The command transmission always starts with the left bit of the bit-string corresponding to the command codeword.

#### **Command Format**

All commands have a fixed code length of 48 bits, needing a transmission time of 2.4usec @ 20 MHz

| Bit Position | 47        | 46               | [45:40]       | [39:8]   | [7:1] | [0]     |

|--------------|-----------|------------------|---------------|----------|-------|---------|

| Width (bits) | 1         | 1                | 6             | 32       | 7     | 1       |

| Value        | "0"       | "1"              | "X"           | "x"      | "x"   | "1"     |

| Description  | Start bit | Transmission bit | Command index | Argument | CRC7  | End bit |

A command always starts with a start bit (always '0'), followed by the bit indicating the direction of transmission (host = '1'). The next 6 bits indicate the index of the command, this value being interpreted as a binary coded number (between 0 and 63). Some commands need an argument (e.g. an address), which is coded by 32 bits. A value denoted by 'x' in the table above indicates this variable is dependent on the command. All commands are protected by a CRC (see Chapter 8.2 for the definition of CRC7). Every command codeword is terminated by the end bit (always '1'). All commands and their arguments are listed in Table 5, Table 13.

#### **Detailed Command Description**

The following tables define in detail all MultiMediaCard bus commands. The responses R1-R5 are defined in Response section. The registers CID, CSD and DSR are described in Register section.

| CMD<br>Index | Туре   | Argument                         | Resp.        | Abbreviation             | Command Description                                                                                                                                                                                                                                |

|--------------|--------|----------------------------------|--------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD0         | bc     | [31:0] stuff bits                | -            | GO_IDLE_STATE            | Resets all cards to idle state                                                                                                                                                                                                                     |

| CMD1         | bcr    | [31:0] OCR<br>without busy       | R3           | SEND_OP_COND             | Asks all cards in idle state to send their operation conditions register contents in the response on the CMD line.                                                                                                                                 |

| CMD2         | bcr    | [31:0] stuff bits                | R2           | ALL_SEND_CID             | Asks all cards to send their CID numbers on the CMD line.                                                                                                                                                                                          |

| CMD3         | ac     | [31:16] RCA                      | R1           | SET_RELATIVE_            | Assigns relative address to the card                                                                                                                                                                                                               |

|              |        | [15:0] stuff bits                |              | ADDR                     |                                                                                                                                                                                                                                                    |

| CMD4         | bc     | [31:16] DSR                      | -            | SET_DSR                  | Programs the DSR of all cards                                                                                                                                                                                                                      |

|              |        | [15:0] stuff bits                |              |                          |                                                                                                                                                                                                                                                    |

| CMD5         | Reserv | ed                               |              |                          |                                                                                                                                                                                                                                                    |

| CMD6         | Reserv | ed                               |              |                          |                                                                                                                                                                                                                                                    |

| CMD7         | ac     | [31:16] RCA<br>[15:0] stuff bits | R1b          | SELECT/DISELECT_<br>CARD | Command toggles a card between the<br>standby and transfer states or between<br>the programming and disconnect states.<br>In both cases the card is selected by its<br>own relative address and gets deselected<br>by any other address; address 0 |

|              |        |                                  |              |                          | deselects all.                                                                                                                                                                                                                                     |

| CMD8         | Reserv |                                  | 1            | <b></b>                  |                                                                                                                                                                                                                                                    |

| CMD9         | ac     | [31:16] RCA<br>[15:0] stuff bits | R2           | SEND_CSD                 | Addressed card sends its card-specific data (CSD) on the CMD line.                                                                                                                                                                                 |

| CMD10        | ac     | [31:16] RCA<br>[15:0] stuff bits | R2           | SEND_CID                 | Addressed card sends its card-<br>identification data (CID) on the CMD line.                                                                                                                                                                       |

| CMD11        | adtc   | [31:0] data<br>address           | R1           | READ_DATA_UNTIL<br>_STOP | Reads data stream from the card, starting<br>at the given address, until a<br>STOP_TRANSMISSION follows.                                                                                                                                           |

| CMD12        | ac     | [31:0] stuff bits                | R1 or<br>R1b | STOP_<br>TRANSMISSION    | Terminates a read/write stream/multiple<br>block operation. When CMD12 is used to<br>terminate a read transaction the card will<br>respond with R1. when it is used to stop a<br>write transaction the card will respond with<br>R1b.              |

| CMD13        | ac     | [31:16] RCA                      | R1           | SEND_STATUS              | Addressed card sends its status register.                                                                                                                                                                                                          |

|              |        | [15:0] stuff bits                |              |                          |                                                                                                                                                                                                                                                    |

| CMD14        | Reserv | ed                               | -            |                          |                                                                                                                                                                                                                                                    |

| CMD15        | ac     | [31:16] RCA<br>[15:0] stuff bits | _            | GO_INACTIVE_<br>STATE    | Set the card to inactive state in order to<br>protect the card stack against<br>communication breakdowns                                                                                                                                           |

Table 5. Basic Commands (class 0) and Read Stream Commands (class 1)

| CMD<br>Index | Туре     | Argument                | Resp. | Abbreviation            | Command Description                                                                                                                                  |  |  |

|--------------|----------|-------------------------|-------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CMD16        | ac       | [31:0] block<br>address | R1    | SET_BLOCKLEN            | Sets the block length (in bytes) for all following block commands (read/write). Default block length is specified in the CSD                         |  |  |

| CMD17        | adtc     | [31:0] block<br>address | R1    | READ_SINGLE_<br>BLOCK   | Reads a block of the size selected by the SET_BLOCKLEN command.                                                                                      |  |  |

| CMD18        | adtc     | [31:0] block<br>address | R1    | READ_MULTIPLE_<br>BLOCK | Continuously transfers data blocks from<br>card to host until interrupted by a stop<br>command or the requested number of data<br>block transmitted. |  |  |

| CMD19        | Reserved |                         |       |                         |                                                                                                                                                      |  |  |

Table 6. Block Oriented Read Commands (class 2)

| CMD<br>Index | Туре     | Argument                | Resp. | Abbreviation             | Command Description                                                                                 |  |  |

|--------------|----------|-------------------------|-------|--------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| CMD20        | adtc     | [31:0] block<br>address | R1    | WRITE_DAT_<br>UNTIL_STOP | Writes data stream from the host, starting at the given address. Until a STOP_SRANSMISSION follows. |  |  |

| CMD21        | Reserved |                         |       |                          |                                                                                                     |  |  |

| CMD22        | Reserved |                         |       |                          |                                                                                                     |  |  |

| CMD<br>Index | Туре | Argument                                      | Resp. | Abbreviation             | Command Description                                                                                                                                                                                                                                       |

|--------------|------|-----------------------------------------------|-------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD23        | ac   | [31:16] set to 0<br>[15:0] number of<br>block | R1    | SET_BLOCK_<br>COUNT      | Defines the number of blocks which are<br>going to be transfer in the immediately<br>succeeding multiple block read or write<br>commands.                                                                                                                 |

| CMD24        | adtc | [31:0] block<br>address                       | R1    | WRITE_BLOCK              | Writes a block of the size selected by the SET_BLOCKLEN command.                                                                                                                                                                                          |

| CMD25        | adtc | [31:0] block<br>address                       | R1    | WRITE_MULTIPLE<br>_BLOCK | Continuously writes blocks of data until a STOP_TRANSMISSION follows or the requested number of block received.                                                                                                                                           |

| CMD26        | adtc | [31:0] stuff bits                             | R1    | PROGRAM_CID              | Programming of the card identification<br>register. This command shall be issued<br>only once per card. The card contains<br>hardware to prevent this operation after the<br>first programming. Normally this command<br>is reserved for the manufacturer |

| CMD27        | adtc | [31:0] stuff bits                             | R1    | PROGRAM_CSD              | Programming of the programmable bits of the CSD.                                                                                                                                                                                                          |

Table 8. Block Oriented Write Commands (class 4)

#### Table 9. Block Oriented Write Protection Commands (class 6)

| CMD<br>Index | Туре    | Argument                                | Resp. | Abbreviation        | Command Description                                                                                                                                                                                             |

|--------------|---------|-----------------------------------------|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD28        | ac      | [31:0] block<br>address                 | R1    | SET_WRITE_PROT      | If the card has write protection features,<br>this command sets the write protection bit<br>of the addressed group. The properties of<br>write protection are coded in the card<br>specific data (WP_GRP_SIZE). |

| CMD29        | ac      | [31:0] block<br>address                 | R1b   | CLR_WRITE_PROT      | If the card provides write protection<br>features, this command clears the write<br>protection bit of the addressed group.                                                                                      |

| CMD30        | adtc    | [31:0] write<br>protect data<br>address | R1    | SEND_WRITE_<br>PROT | If the card provides write protection<br>features, this command asks the card to<br>send the status of the write protection bits                                                                                |

| CMD31        | Reserve | ed                                      |       |                     |                                                                                                                                                                                                                 |

| CMD<br>Index | Туре                                                                                                                                    | Argument                                  | Resp. | Abbreviation          | Command Description                                                                               |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| CMD32        |                                                                                                                                         | ed: These comman<br>ersions of the MultiN |       |                       | rder to maintain backwards compatibility with                                                     |  |  |  |

| CMD33        |                                                                                                                                         |                                           |       |                       |                                                                                                   |  |  |  |

| CMD34        |                                                                                                                                         |                                           |       |                       |                                                                                                   |  |  |  |

| CMD35        | ac                                                                                                                                      | [31:0] block<br>address                   | R1    | ERASE_GROUP_<br>START | Sets the address of the first erase group within a range to be selected for erase.                |  |  |  |

| CMD36        | ac                                                                                                                                      | [31:0] block<br>address                   | R1    | ERASE_GROUP_<br>END   | Sets the address of the last erase group<br>within a continuous range to be selected for<br>erase |  |  |  |

| CMD37        | Reserved: These command indexes cannot be used in order to maintain backwards compatibility with older versions of the MultiMediaCards. |                                           |       |                       |                                                                                                   |  |  |  |

| CMD38        | ac                                                                                                                                      | [31:0] stuff bits                         | R1b   | ERASE                 | Erases all previously selected write blocks                                                       |  |  |  |

### Table 10. Erase Commands (class 5)

#### Table 11. I/O Mode Commands (class 9, S3F49DAX cannot support the this command class)

| CMD<br>Index | Туре    | Argument                                                                                           | Resp. | Abbreviation | Command Description                                                                                                                                                                                                                                                                                                                                              |

|--------------|---------|----------------------------------------------------------------------------------------------------|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD39        | ac      | [31:16] RCA<br>[15] Register<br>write flag<br>[14:8] Register<br>address<br>[7:0] Register<br>data | R4    | FAST_IO      | Used to write and read 8 bit (register) data<br>fields. The command addresses a card<br>and a register and provides the data for<br>writing if the write flag is set. The R4<br>response contains data read from the<br>addressed register. This command<br>accesses application dependent registers<br>which are not defined in the<br>MultiMediaCard standard. |

| CMD40        | bcr     | [31:0] stuff bits                                                                                  | R5    | GO_IRQ_STATE | Sets the system into interrupt mode.                                                                                                                                                                                                                                                                                                                             |

| CMD41        | Reserve | ed                                                                                                 |       |              |                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 12. Lock Card (class 7)

| CMD<br>Index        | Туре    | Argument          | Resp. | Abbreviation | Command Description                                                                                                               |

|---------------------|---------|-------------------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| CMD42               | adtc    | [31:0] stuff bits | R1b   | LOCK_UNLOCK  | Used to set/reset the password or lock/<br>unlock the card. The size of the data<br>block is set by the SET_BLOCK_LEN<br>command. |

| CMD43<br>_<br>CMD54 | Reserve | ed                |       |              |                                                                                                                                   |

| CMD<br>Index | Туре    | Argument                        | Resp. | Abbreviation | Command Description                                                                                                                                                                                            |

|--------------|---------|---------------------------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD55        | ac      | [31:16] RCA<br>[15:0]stuff bits | R1    | APP_CMD      | Indicates to the card that the next<br>command is an application specific<br>command rather than a standard                                                                                                    |

|              |         |                                 |       |              | command                                                                                                                                                                                                        |

| CMD56        | adtc    | [31:1] stuff bits<br>[0] RD/WR  | R1b   | GEN_CMD      | Used either to transfer a data block to the card or to get a data block from the card for general purpose/application specific commands. The size of the data block shall be set by the SEL_BLOCK_LEN command. |

| CMD57        | Reserve | ed                              |       |              |                                                                                                                                                                                                                |

| CMD58        |         |                                 |       |              |                                                                                                                                                                                                                |

| CMD59        |         |                                 |       |              |                                                                                                                                                                                                                |

| CMD60        | Reserv  | ed for manufacture              |       |              |                                                                                                                                                                                                                |

| CMD61        |         |                                 |       |              |                                                                                                                                                                                                                |

| CMD62        |         |                                 |       |              |                                                                                                                                                                                                                |

| CMD63        |         |                                 |       |              |                                                                                                                                                                                                                |

# Table 13. Application Specific Commands (class 8, S3F49DAX cannot support the this command class)

#### RESPONSES

All responses are sent via the command line CMD. The response transmission always starts with the left bit of the bit-string corresponding to the response codeword. The code length depends on the response type.

A response always starts with a start bit (always '0'), followed by the bit indicating the direction of transmission (card = '0'). A value denoted by 'x' in the tables below indicates a variable entry. All responses except for the type R3 (see below) are protected by a CRC. Every command codeword is terminated by the end bit (always '1').

There are five types of responses. Their formats are defined as follows:

• **R1** (normal response command): code length 48 bit. The bits 45:40 indicate the index of the command to be responded to, this value being interpreted as a binary coded number (between 0 and 63). The status of the card is coded in 32 bits. The card status is described in next section.

| Bit Position | 47        | 46               | [45:40]       | [39:8]   | [7:1] | [0]     |

|--------------|-----------|------------------|---------------|----------|-------|---------|

| Width (bits) | 1         | 1                | 6             | 32       | 7     | 1       |

| Value        | "0"       | "O"              | "X"           | "x"      | "x"   | "1"     |

| Description  | Start bit | Transmission bit | Command index | Argument | CRC7  | End bit |

- **R1b** is identical to R1 with an optional busy signal transmitted on the data line. The card may become busy after receiving these commands based on its state prior to the command reception.

- R2 (CID, CSD register): code length 136 bits. The contents of the CID register are sent as a response to the commands CMD2 and CMD10. The contents of the CSD register are sent as a response to CMD9. Only the bits [127...1] of the CID and CSD are transferred, the reserved bit [0] of these registers is replaced by the end bit of the response.

| Bit Position | 135       | 134              | [133:128] | [127:1]                                 | [0]     |

|--------------|-----------|------------------|-----------|-----------------------------------------|---------|

| Width (bits) | 1         | 1                | 6         | 127                                     | 1       |

| Value        | "0"       | "O"              | "111111"  | "X"                                     | "1"     |

| Description  | Start bit | Transmission bit | Reserved  | CID or CSD register incl. Internal CRC7 | End bit |

• **R3** (OCR register): code length 48 bits. The contents of the OCR register is sent as a response to CMD1. The level coding is as follows: restricted voltage windows = LOW, card busy = LOW.

| Bit Position | Position 47 46 |                  | [45:40]  | [39:8]       | [7:1]     | [0]     |

|--------------|----------------|------------------|----------|--------------|-----------|---------|

| Width (bits) | 1              | 1                | 6        | 32           | 7         | 1       |

| Value        | "0"            | "O"              | "111111" | "x"          | "1111111" | "1"     |

| Description  | Start bit      | Transmission bit | Reserved | OCR Register | Reserved  | End bit |

| Bit Position | 47           | 46                  | [45:40]  | [39:8] Argument field |                     | [7:1]                           | [0]  |            |

|--------------|--------------|---------------------|----------|-----------------------|---------------------|---------------------------------|------|------------|

| Width (bits) | 1            | 1                   | 6        | 16                    | 8                   | 8                               | 7    | 1          |

| Value        | "0"          | "1"                 | "100111" | "x"                   | "x"                 | "x"                             | "x"  | "1"        |

| Description  | Start<br>bit | Transmission<br>bit | CMD39    | RCA[31:16]            | Register<br>Address | Read Register<br>Contents [7:0] | CRC7 | End<br>bit |

• **R5** (Interrupt request): code length 48 bits. If the response is generated by the host, the RCA field in the argument shall be 0x0.

| Bit Position | 47        | 46                  | [45:40]  | [39:8] Argument field                            |                                                    | [7:1] | [0]        |

|--------------|-----------|---------------------|----------|--------------------------------------------------|----------------------------------------------------|-------|------------|

| Width (bits) | 1         | 1                   | 6        | 16                                               | 16                                                 | 7     | 1          |

| Value        | "0"       | "1"                 | "100111" | "x"                                              | "X"                                                | "x"   | "1"        |

| Description  | Start bit | Transmission<br>bit | CMD39    | RCA [31:16] of<br>winning card or<br>of the host | [15:0] Not defined.<br>May be used for<br>IRQ data | CRC7  | End<br>bit |

#### CARD STATUS

The response format R1 contains a 32-bit field named card status. This field is intended to transmit the card's status information (which may be stored in a local status register) to the host. If not specified otherwise, the status entries are always related to the previous issued command. The semantics of this register is according to the CSD entry SPEC\_VERS (see Chapter 5.3), indicating the version of the response formats (possibly used for later extensions).

Table 16 defines the different entries of the status. The type and clear condition fields in the table are abbreviated as follows:

#### Types:

- E: Error bit.

- S: Status bit.

- R: Detected and set for the actual command response.

- X: Detected and set during command execution. The host must poll the card by issuing the status command in order to read these bits.

#### **Card Condition:**

- A: According to the card current state.

- B: Always related to the previous command. Reception of a valid command will clear it (with a delay of one command).

- C: Clear by read

S3C49DAX

| Bits | Identifier             | Туре | Value                                | Description                                                                                                                                      | Clear<br>Condition |

|------|------------------------|------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 31   | OUT_OF_RANGE           | ER   | 0 = No error<br>1 = Error            | The command's argument was out of the allowed range for this card                                                                                | С                  |

| 30   | ADDRESS_ERROR          | ERX  | 0 = No error<br>1 = Error            | A misaligned address, which did not match the block length, was used in the command.                                                             | С                  |

| 29   | BLOCK_LEN_ERROR        | ER   | 0 = No error<br>1 = Error            | The transferred block length is not<br>allowed for this card, or the number<br>of transferred bytes does not match<br>the block length.          | С                  |

| 28   | ERASE_SEQ_ERROR        | ER   | 0 = No error<br>1 = Error            | An error in the sequence of erase commands occurred.                                                                                             | С                  |

| 27   | ERASE_PARA             | EX   | 0 = No error<br>1 = Error            | An invalid selection of erase groups for erase occurred.                                                                                         | С                  |

| 26   | WP_VIOLATION           | ERX  | 0 = Not protected<br>1 = Protected   | Attempt to program a write protected block.                                                                                                      | С                  |

| 25   | CARD_IS_LOCKED         | SX   | 0 = Card unlocked<br>1 = Card locked | When set, signals that the card is locked by the host                                                                                            | A                  |

| 24   | LOCK_UNLOCK_<br>FAILED | ERX  | 0 = No error<br>1 = Error            | Set when a sequence or password<br>error has been detected in lock/<br>unlock card command or if there was<br>an attempt to access a locked card | С                  |

| 23   | COM_CRC_ERROR          | ER   | 0 = No error<br>1 = Error            | The CRC check of the previous<br>command failed.                                                                                                 | В                  |

| 22   | ILLEGAL_COMMAND        | ER   | 0 = No error<br>1 = Error            | Command not legal for the card state                                                                                                             | В                  |

| 21   | CARD_ECC_FAILED        | EX   | 0 = No error<br>1 = Error            | Card initial ECC was applied but failed to correct the data                                                                                      | С                  |

| 20   | CC_ERROR               | ERX  | 0 = No error<br>1 = Error            | Internal card controller error                                                                                                                   | С                  |

| 19   | ERROR                  | ERX  | 0 = No error<br>1 = Error            | A general or an unknown error occurred during the operation.                                                                                     | С                  |

| 18   | UNDERRUN               | EX   | 0 = No error<br>1 = Error            | The card could not sustain data transfer in stream read mode.                                                                                    | С                  |

| 17   | OVERRUN                | EX   | 0 = No error<br>1 = Error            | The card could not sustain programming in stream write mode.                                                                                     | С                  |

Table 14. Card Status

| Bits | Identifier            | Туре      | Value                                                                                                                | Description                                                                                                                                                                                                                                                  | Clear     |

|------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|      |                       |           |                                                                                                                      |                                                                                                                                                                                                                                                              | Condition |

| 16   | CID/CSD_              | ERX       | 0 = No error                                                                                                         | Card be either one of the following error:                                                                                                                                                                                                                   | С         |

|      | OVERWRITE             |           | 1 = Error                                                                                                            | <ul> <li>The CID register has been already<br/>written and cannot be overwritten.</li> </ul>                                                                                                                                                                 |           |

|      |                       |           |                                                                                                                      | <ul> <li>The read only section of the CSD does<br/>not match the card content.</li> </ul>                                                                                                                                                                    |           |

|      |                       |           |                                                                                                                      | <ul> <li>An attempt to reverse the copy (set as<br/>original) or permanent WP<br/>(unprotected) bits was made.</li> </ul>                                                                                                                                    |           |

| 15   | WP_ERASE_SKIP         | SX        | 0 = Not protected<br>1 = Protected                                                                                   | Only partial address space was erased due to existing write protected blocks.                                                                                                                                                                                | С         |

| 14   | CARD_ECC_<br>DISABLED | SX        | 0 = Enabled<br>1 = Disabled                                                                                          | The command has been executed without using the internal ECC.                                                                                                                                                                                                | A         |

| 13   | ERASE_RESET           | SR        | 0 = Cleared<br>1 = Set                                                                                               | An erase sequence was cleared before<br>executing because an out of erase<br>sequence command was received.                                                                                                                                                  | С         |

| 12:9 | CURRENT_STATE         | SX        | 0 = idle $1 = ready$ $2 = ident$ $3 = standby$ $4 = tran$ $5 = data$ $6 = rcv$ $7 = prg$ $8 = dis$ $9-15 = reserved$ | The state of the card when receiving the<br>command. If the command execution<br>causes a state change, it will be visible to<br>the host in the response to the next<br>command. The four bits are interpreted as<br>a binary coded number between 0 and 15 | В         |