#### INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

# **74HC/HCT297**Digital phase-locked-loop filter

Product specification

File under Integrated Circuits, IC06

September 1993

#### 74HC/HCT297

#### **FEATURES**

- Digital design avoids analog compensation errors

- Easily cascadable for higher order loops

- · Useful frequency range:

- DC to 55 MHz typical (K-clock)

- DC to 35 MHz typical (I/D-clock)

- · Dynamically variable bandwidth

- · Very narrow bandwidth attainable

- · Power-on reset

- · Output capability: standard/bus driver

- · I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT297 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

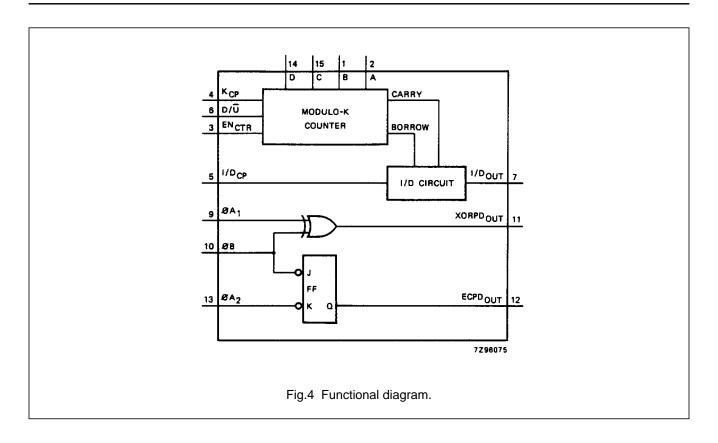

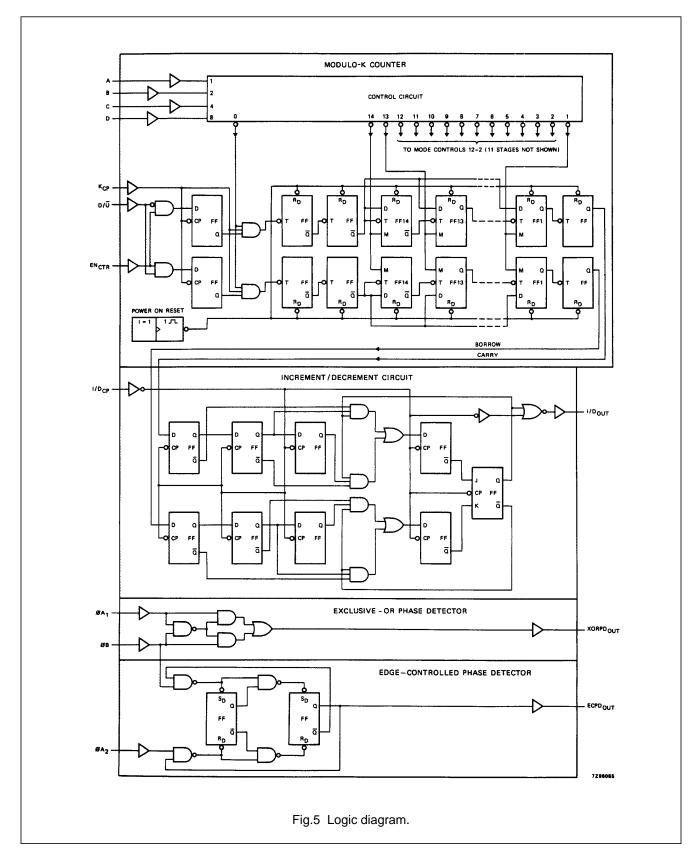

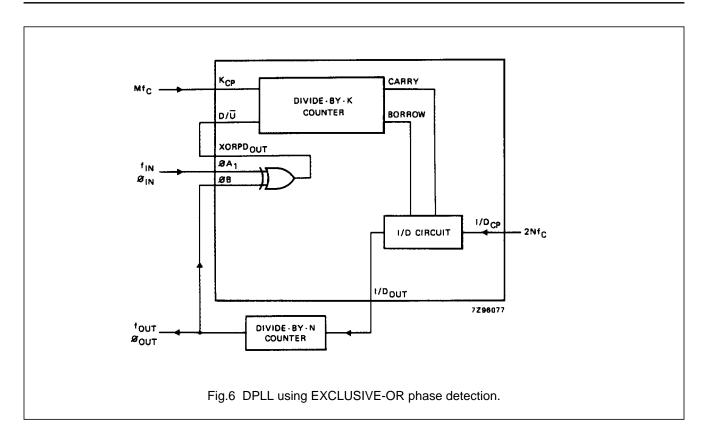

The 74HC/HCT297 are designed to provide a simple, cost-effective solution to high-accuracy, digital, phase-locked-loop applications. These devices contain all the necessary circuits, with the exception of the divide-by-n counter, to build first order phase-locked-loops.

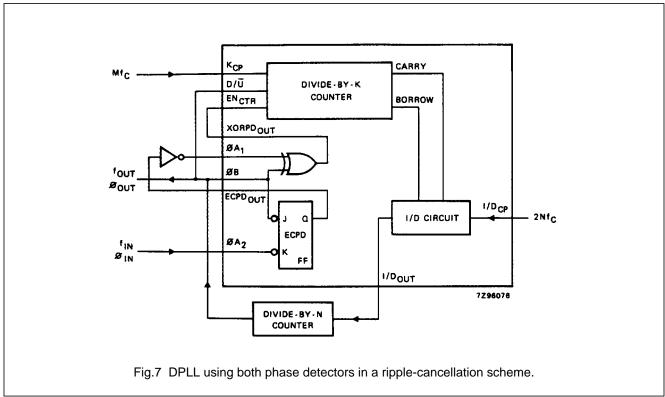

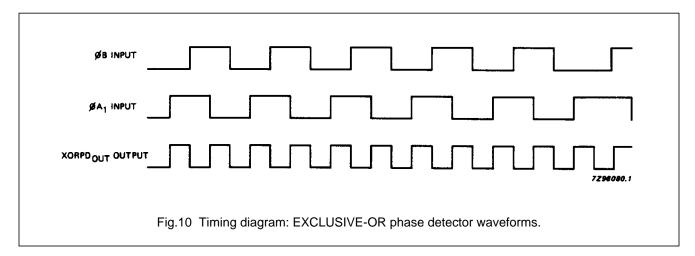

Both EXCLUSIVE-OR (XORPD) and edge-controlled (ECPD) phase detectors are provided for maximum flexibility. The input signals for the EXCLUSIVE-OR phase detector must have a 50% duty factor to obtain the maximum lock-range.

Proper partitioning of the loop function, with many of the building blocks external to the package, makes it easy for the designer to incorporate ripple cancellation (see Fig.7) or to cascade to higher order phase-locked-loops.

The length of the up/down K-counter is digitally programmable according to the K-counter function table. With, A, B, C and D all LOW, the K-counter is disabled. With A HIGH and B, C and D LOW, the K-counter is only three stages long, which widens the bandwidth or capture range and shortens the lock time of the loop. When A, B, C and D are all programmed HIGH, the K-counter becomes seventeen stages long, which narrows the bandwidth or capture range and lengthens the lock time. Real-time control of loop bandwidth by manipulating the A to D inputs can maximize the overall performance of the digital phase-locked loop.

The "297" can perform the classic first-order phase-locked-loop function without using analog

components. The accuracy of the digital phase-locked-loop (DPLL) is not affected by  $V_{CC}$  and temperature variations but depends solely on accuracies of the K-clock, I/D-clock and loop propagation delays.

The phase detector generates an error signal waveform that, at zero phase error, is a 50% duty factor square wave. At the limits of linear operation, the phase detector output will be either HIGH or LOW all of the time depending on the direction of the phase error  $(\varphi_{IN}-\varphi_{OUT}).$  Within these limits the phase detector output varies linearly with the input phase error according to the gain  $k_d,$  which is expressed in terms of phase detector output per cycle or phase error. The phase detector output can be defined to vary between  $\pm$  1 according to the relation:

phase detector output =

$$\frac{\% \text{ HIGH} - \% \text{ LOW}}{100}$$

.

The output of the phase detector will be  $k_d\phi_e$ , where the phase error  $\phi_e=\phi_{IN}-\phi_{OUT}$ .

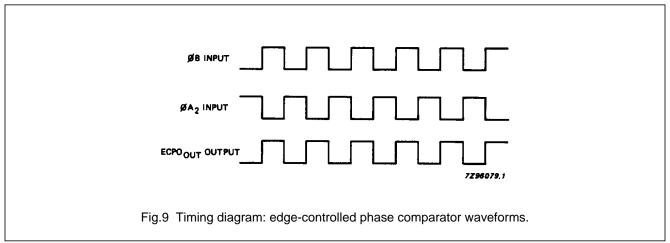

EXCLUSIVE-OR phase detectors (XORPD) and edge-controlled phase detectors (ECPD) are commonly used digital types. The ECPD is more complex than the XORPD logic function but can be described generally as a circuit that changes states on one of the transitions of its inputs. The gain ( $k_d$ ) for an XORPD is 4 because its output remains HIGH (XORPD<sub>OUT</sub> = 1) for a phase error of 1/4 cycle.

Similarly,  $k_d$  for the ECPD is 2 since its output remains HIGH for a phase error of 1/2 cycle. The type of phase detector will determine the zero-phase-error point, i.e., the phase separation of the phase detector inputs for a  $\phi_e$  defined to be zero. For the basic DPLL system of Fig.6  $\phi_e$  = 0 when the phase detector output is a square wave

The XORPD inputs are 1/4 cycle out-of-phase for zero phase error. For the ECPD,  $\phi_e$  = 0 when the inputs are 1/2 cycle out-of-phase.

The phase detector output controls the up/down input to the K-counter. The counter is clocked by input frequency  $Mf_{c},$  which is a multiple M of the loop centre frequency  $f_{c}.$  When the K-counter recycles up, it generates a carry pulse. Recycling while counting down generates a borrow pulse. If the carry and the borrow outputs are conceptually combined into one output that is positive for a carry and negative for a borrow, and if the K-counter is considered as a frequency divider with the ratio  $Mf_{c}/K,$  the output of the K-counter will equal the input frequency multiplied by the division ratio. Thus the output from the K-counter is  $(k_{d}\varphi_{e}Mf_{c})\ /\ K.$

74HC/HCT297

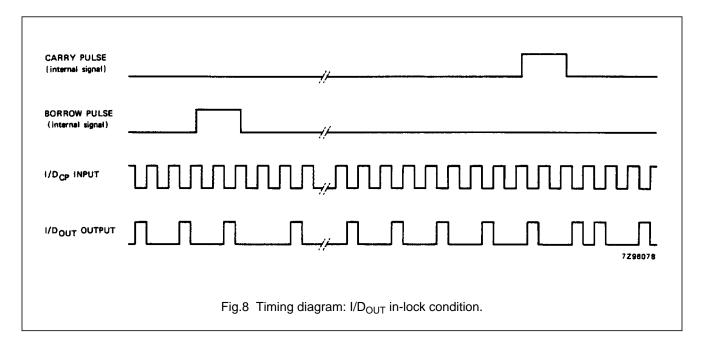

The carry and borrow pulses go to the increment/decrement (I/D) circuit which, in the absence of any carry or borrow pulses has an output that is 1/2 of the input clock (I/D<sub>CP</sub>). The input clock is just a multiple, 2N, of the loop centre frequency. In response to a carry or borrow pulse, the I/D circuit will either add or delete a pulse at I/D<sub>OUT</sub>. Thus the output of the I/D circuit will be Nf<sub>c</sub> + ( $k_d \oslash_e Mf_c$ )/2K.

The output of the N-counter (or the output of the phase-locked-loop) is thus:  $f_0 = f_c + (k_d \phi_e M f_c)/2KN$ .

If this result is compared to the equation for a first-order analog phase-locked-loop, the digital equivalent of the gain of the VCO is just  $Mf_c/2KN$  or  $f_c/K$  for M = 2N.

Thus the simple first-order phase-locked-loop with an adjustable K-counter is the equivalent of an analog phase-locked-loop with a programmable VCO gain.

#### **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb} = 25 \, ^{\circ}C$ ;  $t_r = t_f = 6 \, \text{ns}$

| SYMBOL                              | PARAMETER                                    | CONDITIONS                                    | TYF | LINUT                             |      |

|-------------------------------------|----------------------------------------------|-----------------------------------------------|-----|-----------------------------------|------|

| STIVIBUL                            | PARAMETER                                    | CONDITIONS                                    | НС  | 18<br>13<br>19<br>68<br>40<br>3.5 | UNIT |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay                            | C <sub>L</sub> = 15 pF; V <sub>CC</sub> = 5 V |     |                                   |      |

|                                     | I/D <sub>CP</sub> to I/D <sub>OUT</sub>      |                                               | 15  | 18                                | ns   |

|                                     | φA <sub>1</sub> , φB to XORPD <sub>OUT</sub> |                                               | 13  | 13                                | ns   |

|                                     | φB, φA <sub>2</sub> to ECPD <sub>OUT</sub>   |                                               | 19  | 19                                | ns   |

| f <sub>max</sub>                    | maximum clock frequency                      |                                               |     |                                   |      |

|                                     | K <sub>CP</sub>                              |                                               | 63  | 68                                | MHz  |

|                                     | I/D <sub>CP</sub>                            |                                               | 41  | 40                                | MHz  |

| Cı                                  | input capacitance                            |                                               | 3.5 | 3.5                               | pF   |

| $C_{PD}$                            | power dissipation capacitance per package    | notes 1 and 2                                 | 18  | 19                                | pF   |

#### Notes

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_L \times V_{CC}^2 \times f_o)$$

where:

f<sub>i</sub> = input frequency in MHz

fo = output frequency in MHz

$\sum (C_L \times V_{CC}^2 \times f_o) = \text{sum of outputs}$

C<sub>L</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I$  = GND to  $V_{CC}$ For HCT the condition is  $V_I$  = GND to  $V_{CC}$  – 1.5 V

#### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

# 74HC/HCT297

#### **PIN DESCRIPTION**

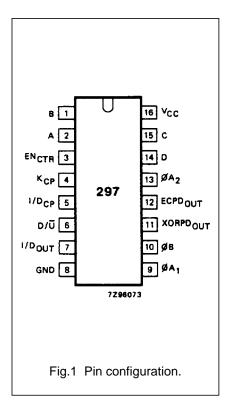

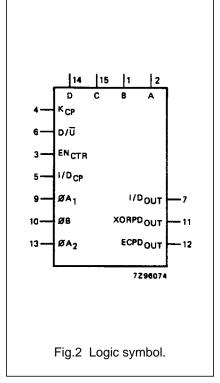

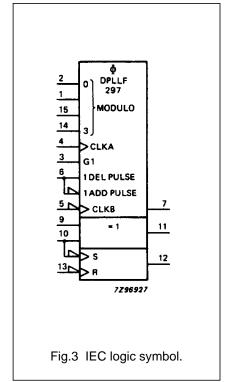

| PIN NO.      | SYMBOL                                | NAME AND FUNCTION                                             |

|--------------|---------------------------------------|---------------------------------------------------------------|

| 2, 1, 15, 14 | A, B, C, D                            | modulo control inputs                                         |

| 3            | EN <sub>CTR</sub>                     | K-counter enable input                                        |

| 4            | K <sub>CP</sub>                       | K-counter clock input (LOW-to-HIGH, edge-triggered)           |

| 5            | I/D <sub>CP</sub>                     | increment/decrement clock input (HIGH-to-LOW, edge-triggered) |

| 6            | D/Ū                                   | down/up control                                               |

| 7            | I/D <sub>OUT</sub>                    | increment/decrement bus output                                |

| 8            | GND                                   | ground (0 V)                                                  |

| 9, 10, 13    | φA <sub>1</sub> , φB, φA <sub>2</sub> | phase inputs                                                  |

| 11           | XORPD <sub>OUT</sub>                  | EXCLUSIVE-OR phase detector output                            |

| 12           | ECPD <sub>OUT</sub>                   | edge-controlled phase detector output                         |

| 16           | V <sub>CC</sub>                       | positive supply voltage                                       |

# Digital phase-locked-loop filter

# 74HC/HCT297

#### K-COUNTER (DIGITAL CONTROL) FUNCTION TABLE

| D | С | В | Α | MODULO (K)                       |

|---|---|---|---|----------------------------------|

| L | L | L | L | inhibited                        |

| L | L | L | Н | 23                               |

| L | L | Н | L | 2 <sup>3</sup><br>2 <sup>4</sup> |

| L | L | Н | Н | 2 <sup>5</sup>                   |

| L | Н | L | L | 2 <sup>6</sup>                   |

| L | Н | L | Н | 2 <sup>7</sup><br>2 <sup>8</sup> |

| L | Н | Н | L | 28                               |

| L | Н | Н | Н | 2 <sup>9</sup>                   |

| Н | L | L | L | 2 <sup>10</sup>                  |

| Н | L | L | Н | 211                              |

| Н | L | Н | L | 2 <sup>12</sup>                  |

| Н | L | Н | Н | 2 <sup>13</sup>                  |

| Н | Н | L | L | 2 <sup>14</sup>                  |

| Н | Н | L | Н | 2 <sup>15</sup>                  |

| Н | Н | Н | L | 2 <sup>16</sup>                  |

| Н | Н | Н | Н | 2 <sup>17</sup>                  |

# EXCLUSIVE-OR PHASE DETECTOR FUNCTION TABLE

| φ <b>A</b> <sub>1</sub> | φВ | XORPD <sub>OUT</sub> |

|-------------------------|----|----------------------|

| L                       | L  | L                    |

| L                       | Н  | Н                    |

| H                       | L  | Н                    |

| Н                       | Н  | L                    |

#### **EDGE-CONTROLLED PHASE DETECTOR TABLE**

| φ <b>A</b> <sub>2</sub> | φВ           | ECPD <sub>OUT</sub> H L no change |  |  |  |

|-------------------------|--------------|-----------------------------------|--|--|--|

| H or L                  | $\downarrow$ | Н                                 |  |  |  |

| ↓                       | H or L       | L                                 |  |  |  |

| H or L                  | <b> </b> ↑   | no change                         |  |  |  |

| <b>1</b>                | H or L       | no change                         |  |  |  |

#### **Notes**

1. H = HIGH voltage level

L = LOW voltage level

$\downarrow$  = HIGH-to-LOW transition

↑ = LOW-to-HIGH transition

# 74HC/HCT297

# Digital phase-locked-loop filter

# 74HC/HCT297

# Digital phase-locked-loop filter

## 74HC/HCT297

74HC/HCT297

#### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard/bus driver

I<sub>CC</sub> category: MSI

#### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

| SYMBOL                              |                                                                                                             | T <sub>amb</sub> (°C) |                 |                 |                 |                 |                 |                 |      | TEST CONDITIONS        |               |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------|------------------------|---------------|

|                                     |                                                                                                             | 74HC                  |                 |                 |                 |                 | 1               |                 |      |                        |               |

|                                     | PARAMETER                                                                                                   | +25                   |                 |                 | -40 to +85      |                 | -40 to +125     |                 | UNIT | V <sub>CC</sub><br>(V) | WAVEFORMS     |

|                                     |                                                                                                             | min.                  | typ.            | max.            | min.            | max.            | min.            | max.            |      | (*)                    |               |

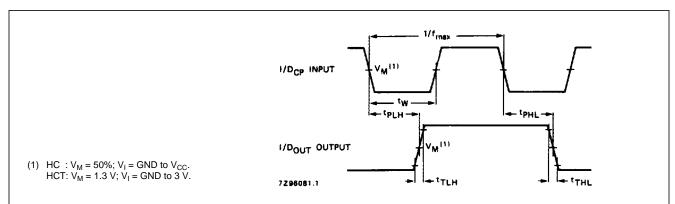

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay I/D <sub>CP</sub> to I/D <sub>OUT</sub>                                                   |                       | 50<br>18<br>14  | 175<br>35<br>30 |                 | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns   | 2.0<br>4.5<br>6.0      | Fig.11        |

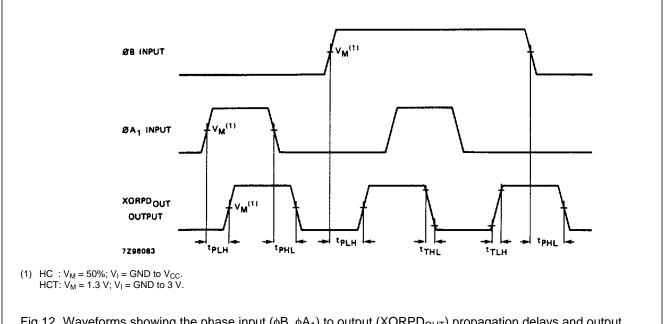

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>φA <sub>1</sub> , φB<br>to XORPD <sub>OUT</sub>                                        |                       | 44<br>16<br>13  | 160<br>32<br>27 |                 | 200<br>40<br>34 |                 | 240<br>48<br>41 | ns   | 2.0<br>4.5<br>6.0      | Fig.12        |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>φB, φA <sub>2</sub><br>to ECPD <sub>OUT</sub>                                          |                       | 61<br>22<br>18  | 220<br>44<br>37 |                 | 275<br>55<br>47 |                 | 330<br>66<br>56 | ns   | 2.0<br>4.5<br>6.0      | Fig.13        |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time:<br>bus driver output;<br>I/D <sub>OUT</sub> (pin 7)                                 |                       | 14<br>5<br>4    | 60<br>12<br>10  |                 | 75<br>15<br>13  |                 | 90<br>18<br>15  | ns   | 2.0<br>4.5<br>6.0      | Fig.11        |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time:<br>standard outputs;<br>XORPD <sub>OUT</sub> , ECPD <sub>OUT</sub><br>(pins 11, 12) |                       | 19<br>7<br>6    | 75<br>15<br>13  |                 | 95<br>19<br>16  |                 | 110<br>22<br>19 | ns   | 2.0<br>4.5<br>6.0      | Fig.12 and 13 |

| t <sub>W</sub>                      | clock pulse width K <sub>CP</sub>                                                                           | 80<br>16<br>14        | 22<br>8<br>6    |                 | 100<br>20<br>17 |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.14        |

| t <sub>W</sub>                      | clock pulse width I/D <sub>CP</sub>                                                                         | 100<br>20<br>17       | 28<br>10<br>8   |                 | 125<br>25<br>21 |                 | 150<br>30<br>26 |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.11        |

| t <sub>su</sub>                     | set-up time<br>D/Ū, EN <sub>CTR</sub> to K <sub>CP</sub>                                                    | 120<br>24<br>20       | 33<br>12<br>10  |                 | 150<br>30<br>26 |                 | 180<br>36<br>31 |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.14        |

| t <sub>h</sub>                      | hold time D/Ū, EN <sub>CTR</sub> to K <sub>CP</sub>                                                         | 0<br>0<br>0           | -19<br>-7<br>-6 |                 | 0<br>0<br>0     |                 | 0<br>0<br>0     |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.14        |

| f <sub>max</sub>                    | maximum clock pulse frequency K <sub>CP</sub>                                                               | 6.0<br>30<br>35       | 19<br>57<br>68  |                 | 4.8<br>24<br>28 |                 | 4.0<br>20<br>24 |                 | MHz  | 2.0<br>4.5<br>6.0      | Fig.14        |

| f <sub>max</sub>                    | maximum clock pulse<br>frequency I/D <sub>CP</sub>                                                          | 4.0<br>20<br>24       | 12<br>37<br>44  |                 | 3.2<br>16<br>19 |                 | 2.6<br>13<br>15 |                 | MHz  | 2.0<br>4.5<br>6.0      | Fig.11        |

# Digital phase-locked-loop filter

# 74HC/HCT297

#### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard/bus driver

I<sub>CC</sub> category: MSI

#### Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications.

To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT                                         | UNIT LOAD COEFFICIENT |

|-----------------------------------------------|-----------------------|

| EN <sub>CTR</sub> , D/ <del>U</del>           | 0.3                   |

| A, B, C, D, K <sub>CP</sub> , φA <sub>2</sub> | 0.6                   |

| I/D <sub>CP</sub> , φA <sub>1</sub> , φB      | 1.5                   |

#### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V, t_r = t_f = 6 ns; C_L = 50 pF$

| SYMBOL                              |                                                                                                           |      |      |      | T <sub>amb</sub> (° | C)   |             |      |       | TEST CONDITIONS |                |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|---------------------|------|-------------|------|-------|-----------------|----------------|

|                                     | PARAMETER                                                                                                 |      |      |      | 74HC                | Т    |             |      | LINIT |                 | WAVEFORMS      |

|                                     | PARAMETER                                                                                                 | +25  |      |      | -40 to +85          |      | -40 to +125 |      | UNIT  | V <sub>CC</sub> | WAVEFORWIS     |

|                                     |                                                                                                           | min. | typ. | max. | min.                | max. | min.        | max. | ]     | (',             |                |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay I/D <sub>CP</sub> to I/D <sub>OUT</sub>                                                 |      | 21   | 35   |                     | 44   |             | 53   | ns    | 4.5             | Fig.11         |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>φA <sub>1</sub> , φB to XORPD <sub>OUT</sub>                                         |      | 16   | 32   |                     | 40   |             | 48   | ns    | 4.5             | Fig.12         |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>φB, φA <sub>2</sub> to ECPD <sub>OUT</sub>                                           |      | 22   | 44   |                     | 55   |             | 66   | ns    | 4.5             | Fig.13         |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time<br>bus driver output<br>I/D <sub>OUT</sub> (pin 7)                                 |      | 5    | 12   |                     | 15   |             | 18   | ns    | 4.5             | Fig.11         |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time<br>standard outputs<br>XORPD <sub>OUT</sub> , ECPD <sub>OUT</sub><br>(pins 11, 12) |      | 7    | 15   |                     | 19   |             | 22   | ns    | 4.5             | Figs 12 and 13 |

| t <sub>W</sub>                      | clock pulse width K <sub>CP</sub>                                                                         | 16   | 8    |      | 20                  |      | 24          |      | ns    | 4.5             | Fig.14         |

| t <sub>W</sub>                      | clock pulse width I/D <sub>CP</sub>                                                                       | 25   | 13   |      | 31                  |      | 38          |      | ns    | 4.5             | Fig.11         |

| t <sub>su</sub>                     | set-up time<br>D/U, EN <sub>CTR</sub> to K <sub>CP</sub>                                                  | 24   | 13   |      | 30                  |      | 36          |      | ns    | 4.5             | Fig.14         |

| t <sub>h</sub>                      | hold time<br>D/U, EN <sub>CTR</sub> to K <sub>CP</sub>                                                    | 0    | -8   |      | 0                   |      | 0           |      | ns    | 4.5             | Fig.14         |

| f <sub>max</sub>                    | maximum clock pulse frequency K <sub>CP</sub>                                                             | 30   | 62   |      | 24                  |      | 20          |      | MHz   | 4.5             | Fig.14         |

| f <sub>max</sub>                    | maximum clock pulse frequency I/D <sub>CP</sub>                                                           | 20   | 36   |      | 16                  |      | 13          |      | MHz   | 4.5             | Fig.11         |

## 74HC/HCT297

#### **AC WAVEFORMS**

Fig.11 Waveforms showing the clock ( $I/D_{CP}$ ) to output ( $I/D_{OUT}$ ) propagation delays, the clock pulse width, output transition times and maximum clock pulse frequency.

Fig.12 Waveforms showing the phase input  $(\phi B, \phi A_1)$  to output (XORPD<sub>OUT</sub>) propagation delays and output transition times.

# Digital phase-locked-loop filter

74HC/HCT297

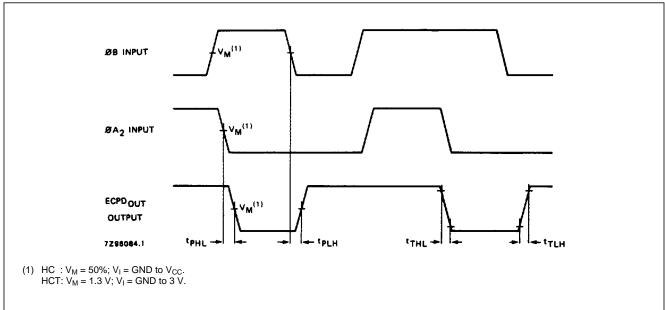

Fig.13 Waveforms showing the phase input  $(\phi B, \phi A_2)$  to output (ECPD<sub>OUT</sub>) propagation delays and output transition times.

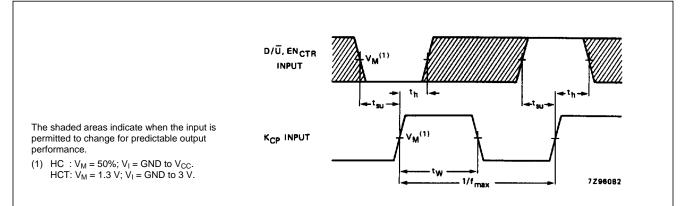

Fig.14 Waveforms showing the clock ( $K_{CP}$ ) pulse width and the maximum clock pulse frequency, and the input (D/ $\overline{U}$ , EN<sub>CTR</sub>) to clock ( $K_{CP}$ ) set-up and hold times.

#### **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.