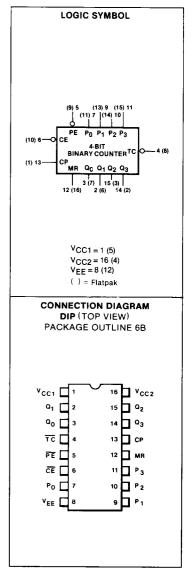

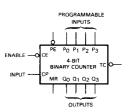

# F10010 • F10016 V BCD DECADE COUNTER/4-BIT BINARY COUNTER

GENERAL DESCRIPTION — The F10010 is a high-speed synchronous, presettable, cascadable BCD Decade Counter and the F10016 is a high-speed synchronous, presettable, cascadable 4-Bit Binary Counter. They are multifunction MSI building blocks useful for a large number of counting, digital integration, and conversion applications. Up to nine devices can be cascaded with no speed degradation using standard 10K gates. A multidecade synchronous counter up to 150 MHz can be built. Typical count frequency is 200 MHz.

Features include assertion inputs and outputs on each of the four master/slave counting flip-flops. Terminal count is generated internally in a manner that allows synchronous loading at nearly the speed of the basic counter.

- HIGH SPEED COUNT . . . 200 MHz TYPICAL COUNT FREQUENCY

- INTERNAL COUNT ENABLE—FOR HIGHEST SPEED EXPANSION

- ASYNCHRONOUS MASTER RESET

- 50 Ω DRIVE CAPABILITY

- WIRED-OR CAPABILITY

- SEPARATE VCC PINS-ELIMINATE NOISE COUPLING

- INTERNAL 50 kΩ INPUT PULL DOWNS

- SINGLE 5.2 V POWER SUPPLY

#### PIN NAMES

| PĒ | Parallel Load Enable (Active LOW)                      |

|----|--------------------------------------------------------|

| Pn | Parallel Inputs                                        |

| CP | Clock Input (Clocks on Positive Transition)            |

| CE | Count Enable (LOW to Count)                            |

| MR | Master Reset (HIGH Forces all Q Outputs LOW)           |

| TC | Terminal Count (10010, LOW at HLLH; 10016 LOW at HHHH) |

| Qn | Counter Outputs                                        |

#

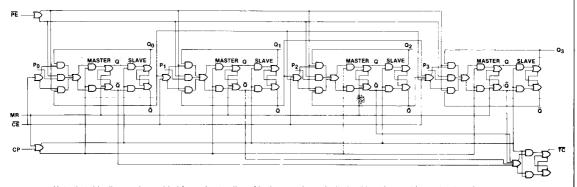

#### LOGIC DIAGRAM F10016

Note that this diagram is provided for understanding of logic operation only. It should not be used for evaluation of propagation delays as many gate functions are achieved internally without incurring a full gate delay.

FUNCTIONAL DESCRIPTION — The F10010 is a high-speed BCD Decade Counter and the F10016 is a high-speed Binary Counter. The four master/slave flip-flops are fully synchronous and are driven in parallel through a clock driver. The masters are loaded during the LOW period of the clock pulse. During the LOW to HIGH transition of the clock, the master is disabled from the input and data is transferred to the slaves and then to the outputs. When the clock is HIGH, the masters are inhibited from changing and the master/slave data path remains open. During the HIGH to LOW transition of the clock, the master/slave data path is inhibited, followed by the enabling of the masters for the acceptance of inputs from the counting logic, parallel entry, or count hold logic.

The Terminal Count (TC) is generated at count 9 (HLLH) on the 10010 and at count 15 (HHHH) on the 10016.

The  $\overline{\text{TC}}$  output is available simultaneously with the Q outputs through the use of unique lookahead logic and a fifth slave which is loaded during the LOW portion of the clock cycle. This feature, in conjunction with the triggered Count Enable ( $\overline{\text{CE}}$ ) and the Parallel Enable ( $\overline{\text{PE}}$ ) select the mode of operation as shown in the table next page. The status of these control lines is sampled only during the LOW to HIGH transition of the clock.

The Master Reset (MR) function is asynchronous. When HIGH, it overrides all other commands and forces all Q outputs LOW and the TC HIGH.

#### TRUTH TABLE

| CE | PE | MR | СР | Function                                |

|----|----|----|----|-----------------------------------------|

| L  | L  | L  | z  | Load Parallel (Pn to Qn)                |

| Н  | L  | L  | z  | Load Parallel (Pn to Qn)                |

| L  | н  | L  | z  | Count                                   |

| Н  | н  | L  | z  | Hold                                    |

| x  | Х  | Ļ  | ZZ | Masters Respond; Slaves Hold            |

| Х  | X  | н  | Х  | Reset (Q <sub>n</sub> = LOW, TC = HIGH) |

L = LOW H = HIGH Voltage Level X = Don't Care Z = Clock Pulse (LOW to HIGH) ZZ = Clock Pulse (HIGH to LOW)

#### STATE DIAGRAMS

NOTE: The 10010 can be preset to any state, but will not count beyond 9 (HLLH). If preset to state 10, 11, 12, 13, 14 or 15, it will return to its normal sequence within two clock pulses.

# DC CHARACTERISTICS: $V_{\mbox{EE}} = -5.2 \mbox{ V, } V_{\mbox{CC}} = \mbox{GND}$

| SYMBOL | CHARACTERISTIC                    | LIMITS |      |            | LINITO | <b>-</b> . | CONDITIONS                          |  |

|--------|-----------------------------------|--------|------|------------|--------|------------|-------------------------------------|--|

|        |                                   | В      | TYP  | Α          | UNITS  | TA         | CONDITIONS                          |  |

| ΊΗ     | Input Current HIGH<br>MR (Pin 12) |        |      | 265<br>700 | μА     | 25°C       | VIN = VIHA                          |  |

| IEE    | Power Supply Current              | - 115  | - 80 |            | mA     | 25°C       | Outputs Open, Pin 12 Tied<br>to VIH |  |

| SYMBOL           | CHARACTERISTIC                                              | LIMITS |     |     |       |              |

|------------------|-------------------------------------------------------------|--------|-----|-----|-------|--------------|

|                  |                                                             | В      | TYP | Α   | UNITS | CONDITIONS   |

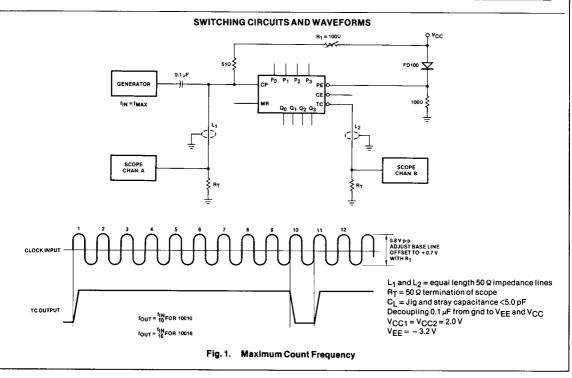

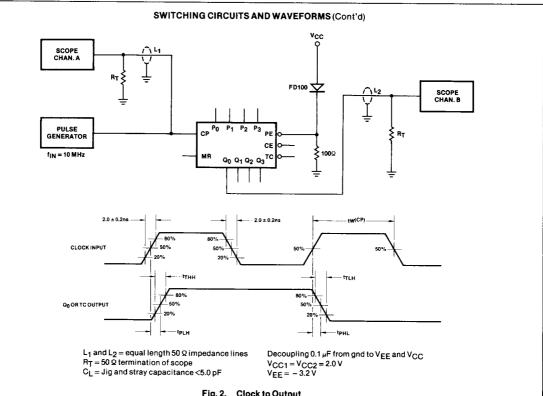

| fcount           | Count Frequency                                             | 140    | 200 |     | MHz   | See Figure 1 |

| <sup>t</sup> PLH | Propagation Delay<br>Clock to Output (Q <sub>n</sub> or TC) | 2.0    | 3.6 | 5.0 | ns    |              |

| <sup>t</sup> PHL | Propagation Delay<br>Clock to Output (Q <sub>n</sub> or TC) | 2.0    | 3.6 | 5.0 | ns    | See Figure 2 |

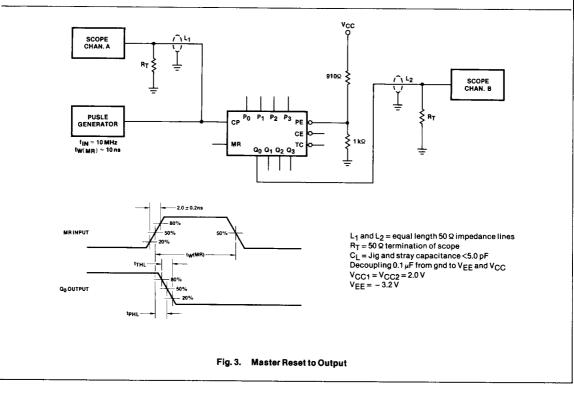

| <sup>t</sup> PHL | Propagation Delay<br>Master Reset to Output                 |        | 4.0 |     | ns    | See Figure 3 |

| <sup>t</sup> TLH | Output Transition Time<br>LOW to HIGH (20% to 80%)          | 1.3    | 2.5 | 3.3 | ns    |              |

| tTHL             | Output Transition Time<br>HIGH to LOW (80% to 20%)          | 1.3    | 2.5 | 3.3 | ns    | See Figure 2 |

| t <sub>W</sub>   | Clock Pulse Width                                           |        | 2.3 |     | ns    | See Figure 2 |

| t <sub>w</sub>   | MR Pulse Width                                              |        | 2.8 |     | ns    | See Figure 3 |

| t <sub>s</sub>   | Set-Up Time Prior to Clock<br>Pn to CP                      | 2.0    |     |     | ns    |              |

| th               | Hold Time After Clock Pn to CP                              | 1.0    |     |     | ns    |              |

| t <sub>s</sub>   | Set-Up Time Prior to Clock<br>PE or CE to CP                | 2.5    |     |     | ns    |              |

| t <sub>h</sub>   | Hold Time After Clock PE or CE to CP                        | 0.5    | ,   |     | ns    |              |

Fig. 2. Clock to Output

#### APPLICATION INFORMATION

| DIVIDE<br>RATIO | PO P1 P2 P3 |   |    |    |  |  |  |

|-----------------|-------------|---|----|----|--|--|--|

|                 |             |   |    | Р3 |  |  |  |

| 2               | L           | н | H  | н  |  |  |  |

| 3               | н           | L | H  | н  |  |  |  |

| 4               | L           | L | н  | н  |  |  |  |

| 5               | н           | Н | L  | Н  |  |  |  |

| 6               | L           | Ξ | L  | Н  |  |  |  |

| 7               | Н           | L | L  | Н  |  |  |  |

| 8               | L           | L | L  | Н  |  |  |  |

| 9               | Н           | Н | Н  | L  |  |  |  |

| 10              | L           | Η | н. | L  |  |  |  |

| 11              | н           | L | н  | L  |  |  |  |

| 12              | L           | L | н  | L  |  |  |  |

| 13              | Н           | н | L  | L  |  |  |  |

| 14              | L           | Н | L  | L  |  |  |  |

| 15              | Н           | L | L  | L  |  |  |  |

| 16              | L           | L | L  | L, |  |  |  |

The F10016 may be connected to divide by any modulo from 2 to 16. The table illustrates the inputs required for each modulo. The terminal count output is utilized to load the parallel data, this in turn determines the number of clock pulses which will occur before TC goes LOW again.

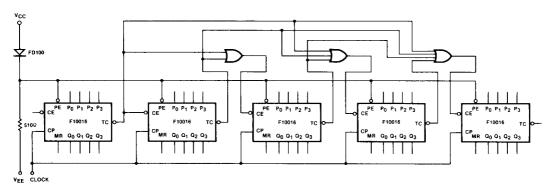

CASCADE COUNTERS USING OR GATES FOR CARRY PROPAGATION