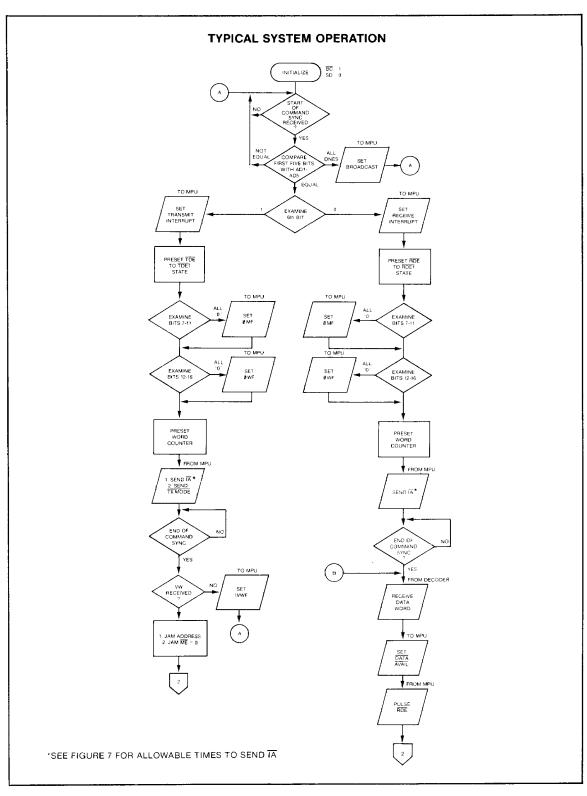

# COM 1553A µPC FAMILY

## MIL-STD-1553A "SMART®"

#### **FEATURES**

- ☐ Support of MIL-STD-1553A

- Operates as a: Remote Terminal Responding

Bus Controller Initiating

- ☐ Performs Parallel to Serial Conversion when Transmitting

- ☐ Performs Serial to Parallel Conversion when Receiving

- ☐ Compatible with HD-15531 Manchester Encoder/ Decoder

- ☐ All Inputs and Outputs are TTL Compatible

- ☐ Single +5 Volt Supply

- ☐ COPLAMOS® N Channel MOS Technology

- ☐ Available in PC Board Form from Grumman Aerospace Corporation

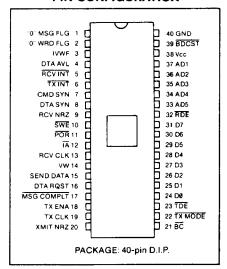

#### PIN CONFIGURATION

## **GENERAL DESCRIPTION**

The COM 1553A SMART® (Synchronous Mode Avionics Receiver/Transmitter) is a special purpose COPLAMOS N-Channel MOS/LSI device designed to provide the interface between a parallel 8-bit bus and a MIL-STD-1553A serial bit stream.

The COM 1553A is a double buffered serial/parallel and parallel/serial converter providing all of the "hand shaking" required between a Manchester decoder/encoder and a microprocessor as well as the protocol handling for both a MIL-STD-1553 bus controller and remote terminal.

The COM 1553A performs the following functions in response to a 16 bit Command Word. It provides address detection for the first five bits of the serial data input. If all 1's appear in the address field, a broadcast signal is generated. The sixth bit is decoded as mode: transmit or receive. The next five bits are decoded for zero message flag and special flags in the subaddress/mode field. The last five bits (word-count field) are decoded determining the number of words to be received or transmitted.

When receiving data sync the COM 1553A performs a serial to parallel conversion, buffers the 16 bit message

word, and formats it into two parallel (8 bit) bytes for presentation to the I/O bus under processor or hard wired logic control.

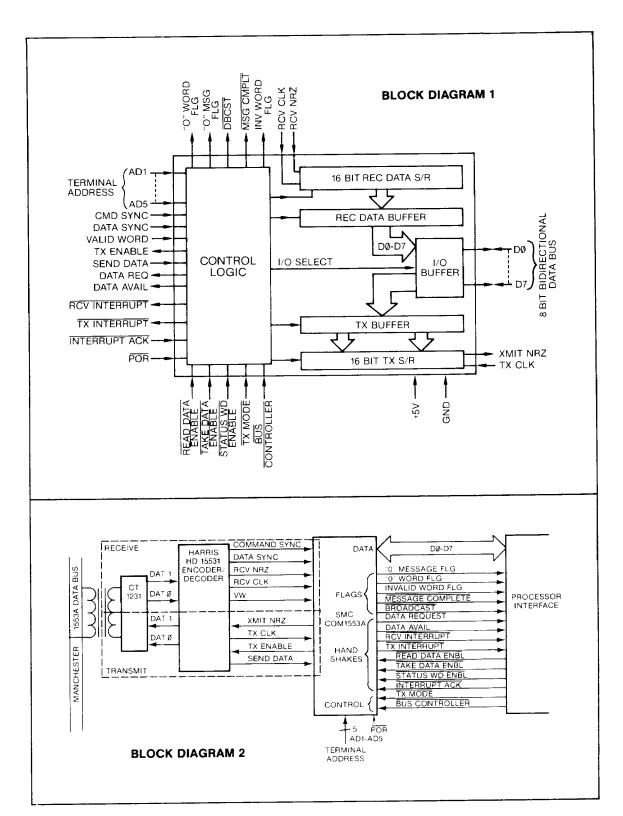

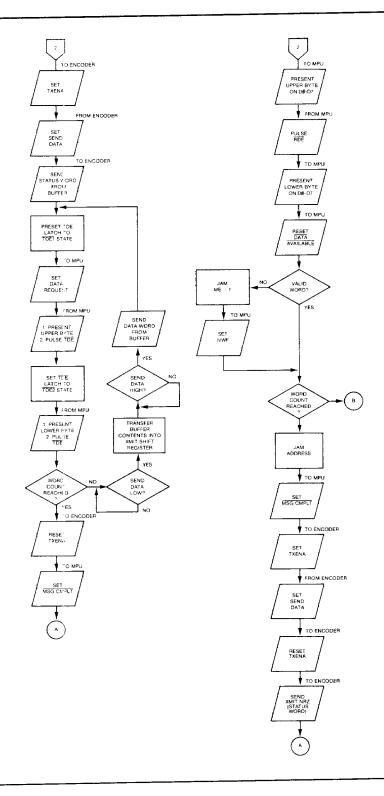

In the transmit mode the COM 1553A takes two parallel 8 bit data words from the I/O bus and serially transmits the resultant 16 bit word to the Manchester encoder. This is done under the control of Send Data. To facilitate data transfer the COM 1553A provides all necessary buffering and storage for transmitted and received data. It also provides all necessary hand shaking, control flags and interrupts to a processor or hard wired logic terminal. See block diagram 1.

The COM 1553A can be set up as either a remote terminal or a bus controller interface.

The COM 1553A is compatible with Harris' HD-15531 CMOS Manchester Encoder-Decoder chip and interfaces directly with it. A 3 device kit consisting of: SMC's COM 1553A, Harris' HD-15531 and Circuit Techsology's com CT1231 forms a complete system interface for the message structure of MIL-STD-1553A. See block diagram 2.

Note: All terminology utilized in this data sheet is consistent with MIL-STD-1553.

## **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | NAME                  | SYMBOL  | FUNCTION                                                                                                                                                                                                                                                                |  |  |

|---------|-----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

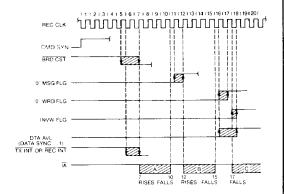

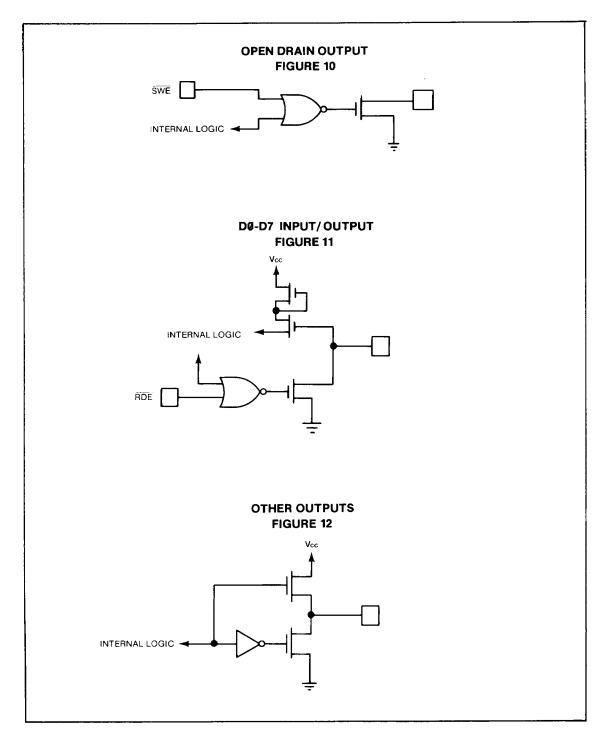

| 1       | "Ø" MESSAGE FLAG      | ØMF     | The ZERO MESSAGE FLAG output is set when the 7th through 11th bits of the NRZ serial input data in a command envelope (see figure 1) are zero. @MF is an open drain output.                                                                                             |  |  |

| 2       | "Ø" WORD FLAG         | ØWF     | The ZERO WORD FLAG output is set when the 12th through 16th bits of the NRZ serial input data in a command envelope (see figure 1) are zero. @WF is an open drain output.                                                                                               |  |  |

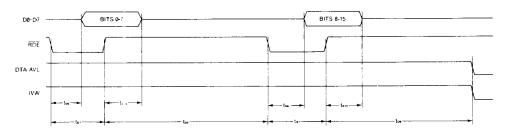

| 3       | INVALID WORD<br>FLAG  | IVWF    | The INVALID WORD FLAG output is set when the word just received has an invalid parity bit or invalid format. IVWF is an open drain output.                                                                                                                              |  |  |

| 4       | DATA AVAILABLE        | DTA AVL | DATA AVAILABLE is set when a word received is ready to be read. When the COM 1553A is the bus controller, DTA AVL occurs on command, status or data words. When the COM 1553A is a remote terminal, DTA AVL is set only on data words. DTA AVL is an open drain output. |  |  |

| 5       | RECEIVE INTERRUPT     | RCV INT | RECEIVE INTERRUPT is set to zero when the 6th bit following a command sync is a zero and the first 5 bits match AD1-AD5. RCV INT is reset to one by IA or POR, or if the line is not active for 32 receive clocks.                                                      |  |  |

| 6       | TRANSMIT INTERRUPT    | TX INT  | TRANSMIT INTERRUPT is set to zero when the 6th bit following a command sync is a one, and the first 5 bits match AD1-AD5. TXINT is reset to one by IA or POR.                                                                                                           |  |  |

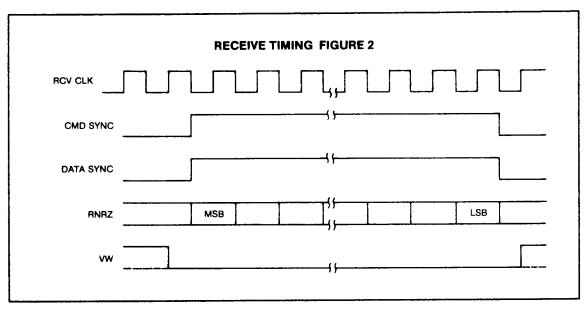

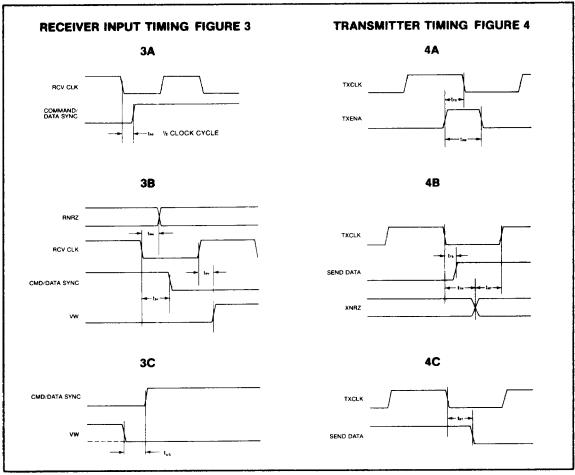

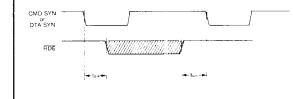

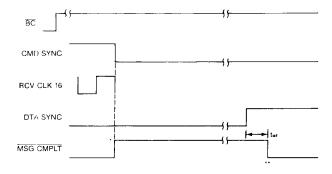

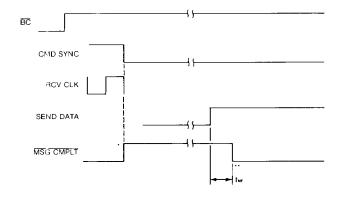

| 7       | COMMAND SYNC          | CMD SYN | COMMAND SYNC is an input from the Manchester decoder and must be high for 16 receive clocks enveloping the receive NRZ data of a command word.                                                                                                                          |  |  |

| 8       | DATA SYNC             | DTA SYN | DATA SYNC is an input from the Manchester decoder and must be high for 16 receive clocks enveloping the receive NRZ data of a data word.                                                                                                                                |  |  |

| 9       | RECEIVER NRZ          | RCV NRZ | Receiver serial input from Manchester decoder. Data must be stable during the rising edge of the receive clock.                                                                                                                                                         |  |  |

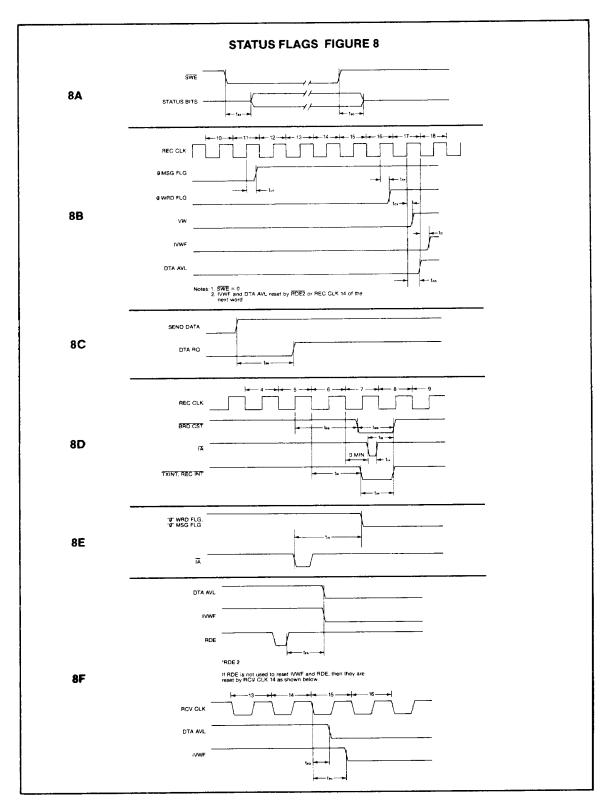

| 10      | STATUS WORD<br>ENABLE | SWE     | SWE is the output enable for the following open drain outputs:  ØMF  IVWF  DTA AVL  DTA RQ  MSG CPLT                                                                                                                                                                    |  |  |

| 11      | POWER ON RESET        | POR     | POWER ON RESET. Active low for reset.                                                                                                                                                                                                                                   |  |  |

| 12      | INTERRUPT ACKNOWLEDGE | ĪĀ      | IA resets TX INT, REC INT, ØMF, ØWF and BRD CST. IA may occur between the trailing edges of receive clocks 6 and 10, or between the leading edge of receive clock 12 and the falling edge of receive clock 15, or after the falling edge of clock 17.                   |  |  |

| 13      | RECEIVE CLOCK         | RCV CLK | The RECEIVE CLOCK is synchronous with the Receiver NRZ input during the command sync or data sync envelopes.                                                                                                                                                            |  |  |

| 14      | VALID WORD            | VW      | This input is driven by the VALID WORD output of the Manchester Decoder. VW should occur immediately after the rise of the first RCV CLK following the fall DATA SYNC or COMMAND SYNC.                                                                                  |  |  |

## **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | NAME             | SYMBOL    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

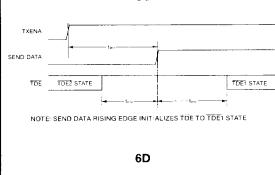

| 15      | SEND DATA        | SD        | SEND DATA is a "handshake" signal received from the Manchester encoder indicating that the encoder is ready for the COM 1553A to transmit data. SD will bracket 16 transmit data clocks. The contents of the transmitter buffer will be transferred into the transmit register when SD is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

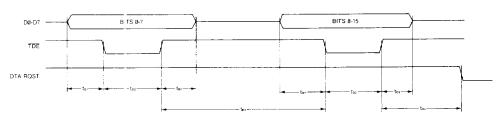

| 16      | DATA REQUEST     | DTA RQST  | DATA REQUEST is an open drain output which is set high when the transmitter holding register is ready to accept more data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 17      | MESSAGE COMPLETE | MSG CMPLT | In the receive mode the MESSAGE COMPLETE output is set low when the appropriate number of data words have been received. In the transmit mode, MSG CMPLT indicates that the appropriate number of command, status or data words have been transmitted. When the COM 1553A is a bus controller, MSG CMPLT will be asserted low when 33 command status or data words have been transmitted. MSG CMPLT is an open drain output.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

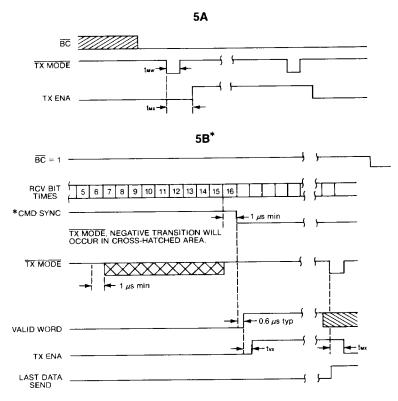

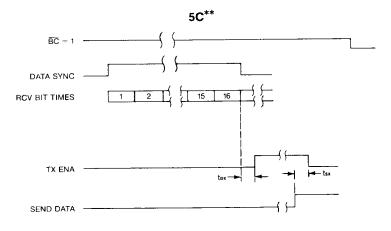

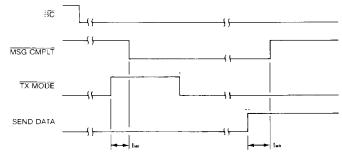

| 18      | TRANSMIT ENABLE  | TXENA     | A TRANSMIT ENABLE signal will be sent to the Manchester Encoder to initiate transmission of a word. TXENA is generated under the following conditions:  1) COM 1553A is a bus controller: A TXMODE pulse will set TXENA. A second TXMODE pulse will reset TXENA.  2) COM 1553A is a remote terminal. A Transmit Command from the Controller will cause a TRANSMIT INTERRUPT (see pin 6). When this is acknowledged by a TXMODE pulse from the system, TXENA will be set.  TXENA will then be reset by either  A) Send Data Command associated with the last data word.  B) a second TXMODE pulse.  3) COM 1553A is a remote terminal. The falling edge of a DATA SYNC associated with the last data word of a message while in the receive mode. TXENA will be reset during the next SEND DATA envelope. |  |  |  |

| 19      | TRANSMIT CLOCK   | TXCLK     | Transmitter shift clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 20      | TRANSMIT NRZ     | XMIT NRZ  | Serial data output to the Manchester Encoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 21      | BUS CONTROLLER   | BC        | $\overline{BC}$ determines whether the COM 1553A is acting as bus controller ( $\overline{BC}=0$ ) or as a remote terminal ( $\overline{BC}=1$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 22      | TRANSMIT MODE    | TXMODE    | TXMODE is a system input controlling transmission. See TXENA (pin 18).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 23      | TAKE DATA ENABLE | TDE       | TDE is an input from the system initiating transmission. Two TDE pulses are required for each 16 bit data word, one for each 8 data bits placed on DØ-D7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 24-31   | DATA BUS         | DØ-D7     | Bidirectional 8 bit Data Bus to the system. DØ is the LSB. DØ-D7 present open drain outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 32      | READ DATA ENABLE | RDE       | RDE is an input from the system instructing the COM 1553A to place the received data onto D0-D7. Two RDE pulses are required per 16 bit data word, one for each 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 33-37   | ADDRESS          | AD5-AD1   | AD1-AD5 provide addressing to the COM 1553A. Each input has a pull-up resister allowing simple switching to ground to select the user address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 38      | POWER SUPPLY     | vcc       | +5 Volt supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 39      | BROADCAST        | BDCST     | BDCST is set low when a "broadcast" command word (the address bits all set to "one") is being received. BDCST is reset by IA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 40      | GROUND           | GND       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

#### OPERATION...RECEIVE MODE

The COM 1553A is considered in the receive mode when TXENA = 0. The most significant bit of both command and data words is received first.

Message reception is initiated when CMD SYN goes high. The next 16 receive clocks are used to shift serial data into RCV NRZ.

The first 5 bits of a command word designate a remote terminal address. These 5 bits are compared with AD1-5. Should the address bits compare, the sixth bit is examined. If it is a zero, a RECEIVE INTERRUPT is generated. If it is a one, a TRANSMIT INTERRUPT is generated.

Bit fields 7-11 and 12-16 are examined for all zeros. All zeros in bit field 7-11 denotes a "ZERO MESSAGE" and all zeros in bit field 12-16 denotes a "ZERO WORD."

Receipt of a data word is indicated when DTA SYN goes high.

When DTA SYN or CMD SYN goes low, the contents of the 16 bit receive register are loaded into the receive buffer. The buffer is organized into two groups of 8 bits each. The most significant 8 bits (byte 1) will be enabled onto the 8 bit data bus on receipt of the first RDE pulse (RDE1). The second byte will be enabled on receipt of the second RDE pulse (RDE2).

A DATA AVAILABLE is generated for data words only. However, data will be available on D0-D7 for both command and data words.

If 32 clocks are received after the rising edge of CMD SYN or DTA SYN an "Idle Line Reset" condition exists. This implies that a new CMD SYN or DTA SYN has not yet been received within 16 clocks of the fall of the previous sync signal. The "Idle Line Reset" will reset the following signals:

REC INT

"0" MSG FLG

TX INT

"0" WRD FLG

BRD CST

When the commanded number of data words have been received, a MESSAGE COMPLETE signal is generated.

As the transmitter and receiver registers operate independently, the COM 1553A will receive its own transmission. The following signals are inhibited during transmission:

| $\overline{BC} = 0$ | BC = 1             |

|---------------------|--------------------|

| REC INT             | DAT AVL            |

| XMT INT             | IVWF               |

| BRD CST             | REC INT            |

| ØWF                 | XMT INT            |

| ØMF                 | ØМG                |

| JAM MESSAGE ERROR*  | ØWF                |

|                     | BRD CST            |

|                     | JAM MESSAGE ERROR* |

\*JAM MESSAGE ERROR is an internal signal. See OPERATION...TRANSMIT MODE.

#### OPERATION...TRANSMIT MODE

The COM 1553A is considered in the transmit mode when TXENA = 1. This is caused by a TXMODE pulse (see description of pin functions, pin 18). The TXMODE pulse in turn is a system response to a transmit command from the receiver.

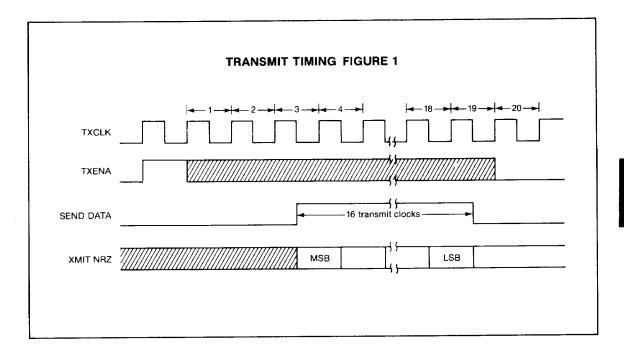

When the Manchester Encoder receives TXENA = 1, it will respond with SEND DATA = 1. The COM 1553A will then send the system a DATA REQUEST.

Data is loaded into the transmitter data buffer from the 8 bit data bus by pulsing TDE. The 8 most significant bits are loaded in by the first TDE pulse (TDE1), the 8 least significant bits by the second TDE pulse (TDE2).

When SEND DATA (pin 15) is low, the transmitter shift register inputs will follow either the transmit buffer output, JAM ADDRESS or JAM MESSAGE ERROR signals. When SEND DATA is high, the shift register parallel inputs are disabled and the shift register contents are shifted out in NRZ form using the 16 negative edges in the send data envelope.

To facilitate transmission of the status word from a remote terminal, the COM 1553A will "jam" the first (most significant) 6 bits of the status word into the transmit register when BC is high. These bits will automatically be sent at the first SEND DATA pulse. In general for MIL-STD-1553A the remaining 10 bits will normally be all zeros and will automatically be sent out as such. If it is desired to send additional status information (for MIL-STD-1553B), a TDE1 pulse will load

the least significant 2 bits of the first 8 bit byte, and a  $\overline{\text{TDE2}}$  will load all 8 bits of the second byte. Note that these TDE pulses must be sent (and data presented) before the first SD = 1 response from the Manchester Encoder.

A JAM ADDRESS occurs when 1) a transmit command is addressed to the COM 1553A 2) A TXMODE pulse is received and 3) a valid word signal is received. Upon a JAM ADDRESS the COM 1553A will load its address into the first 5 bits of the transmit register.

Alternatively, a JAM ADDRESS will also occur at the fall of the last data sync after valid receive command has been detected.

The JAM ADDRESS function will be inhibited if a "0" word and "0" message condition exists in the command word. The JAM ADDRESS will be reset by the leading edge of SEND DATA.

The JAM MESSAGE ERROR function occurs when, in the receive mode, a data word is not followed by a VALID WORD signal. JAM MESSAGE ERROR consists of loading a one in the sixth bit location of the transmit shift register (the message error location).

JAM MESSAGE ERROR is inhibited when the transmit command word contains "0" Message and "0" Word fields.

When the commanded number of data words has been transmitted a MESSAGE COMPLETE signal will be generated.

## **GENERAL OPERATION NOTES**

- 1. BUS CONTROLLER. When  $\overline{BC} = 0$ , signifying that the COM 1553A is the bus controller the following is true:

- A. DTA AVL is generated on the rising edge of the 17th receive clock following a Command Sync or Data Sync. This allows the bus controller to receive command, status or data words regardless of their address.

- B. TXENA is contingent only on TXMODE. A bus controller can therefore transmit whenever it desires.

- C. The jam functions are inhibited.

- 2. INVALID WORD FLAG. When  $\overline{BC}=0$ , IVWF will be set if the Valid Word input (from the Manchester decorder) does not go high following receipt of all words. This includes words received from the same device's transmitter. (This provides a validity test of the controller transmission).

When  $\overline{BC} = 1$ , IVWF will be set if Valid Word does not go high following receipt of all command and address words addressed to the terminal.

IVWF will be set for the following conditions:

| Message type         | Word             | Terminal is  | IVWF generated |

|----------------------|------------------|--------------|----------------|

| Transit Group        | Transmit command | receiving    | yes            |

| Transit Group        | Status word      | transmitting | no             |

|                      | Data word        | transmitting | no             |

| Receive Group        | Receive command  | receiving    | yes            |

| 11000110 31 04       | Data word        | receiving    | yes            |

|                      | Status word      | transmitting | no             |

| Receive/Transmit     | Receive command  | receiving    | yes            |

| Group (this          | Transmit command | receiving    | no             |

| terminal addressed   | Status word      | receiving    | no             |

| to receive)          | Data word        | receiving    | yes            |

| 10 1000140)          | Status word      | transmitting | no             |

| Receive/Transmit     | Receive command  | receiving    | no             |

| group (this terminal | Transmit command | receiving    | yes            |

| addressed to         | Status word      | transmitting | no             |

| transmit)            | Data word        | transmitting | no             |

| tianomity            | Status word      | receiving    | no             |

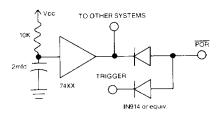

3. POWER ON RESET. During power-up, POR is a low to high exponential with a minimum low time, after the supply is within specified limits, of 10 microseconds. POR may also occur asynchronously anytime after power has stabilized.

POR initializes the following outputs:

ØMG ØWF BRD CST XMT INT REC INT MSG CMPLT IVW RDE

TDE DTA AVL TXENA DTA RQ

The following circuit may be used to implement POR.

4. WORD COUNT: Word count is decoded as follows:

| D1 | D2 | D3 | D4 | D5 | Word Count |

|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 1  | 1          |

| 0  | 0  | 0  | 1  | 0  | 2          |

| 1  | 1  | 1  | 1  | 1  | 31         |

| 0  | 0  | 0  | 0  | 0  | 32         |

|    |    |    |    |    |            |

## MAXIMUM GUARANTEED RATINGS\*

| Operating Temperature Range55°                      | <sup>3</sup> C to +125°C |

|-----------------------------------------------------|--------------------------|

| Storage Temperature Range                           | °C to +150°C             |

| Storage remperature manage                          | 120500                   |

| Lead Temperature (soldering, 10 sec.)               | +325° C                  |

| Positive Voltage on any Pin, with respect to ground | +8.0V                    |

| Negative Voltage on any Pin, with respect to ground | 0.3V                     |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists it is suggested that a clamp circuit be used.

## **ELECTRICAL CHARACTERISTICS** ( $T_A = -55^{\circ}C$ to 125°C, $V_{CC} = +5 \pm 5\%$ , unless otherwise noted)

| PARAMETER                                                                                                             | MIN | TYP     | MAX       | UNIT     | COMMENTS                                                                              |

|-----------------------------------------------------------------------------------------------------------------------|-----|---------|-----------|----------|---------------------------------------------------------------------------------------|

| DC CHARACTERISTICS                                                                                                    |     |         |           |          |                                                                                       |

| Input Voltage Levels<br>Low Level, Vіь<br>High Level, Vін<br>Output Voltage Levels<br>Low Level Vоь<br>High Level Vон | 3.0 | 4.0     | 0.8       | V V V V  | $I_{\rm OL}=$ -1.6 mA, except open drain $I_{\rm OH}=$ 100 $\mu$ A, except open drain |

| Low Level Vol<br>Output Leakage, Ilo                                                                                  |     |         | 0.4<br>10 | V<br>μA  | lo <sub>L</sub> = -1.6 mA, open drain output                                          |

| Input Current, AD1-AD5                                                                                                |     | 60      |           | μΑ       | $V_{IN} = 0V$                                                                         |

| Output Capacitance Input Capacitance                                                                                  |     | 5<br>10 | 10<br>25  | pf<br>pf |                                                                                       |

| Power Dissipation                                                                                                     |     | .       | 500       | mW       |                                                                                       |

| PARAMETER                             | SYMBOL           | MIN | TYP  | MAX   | UNIT     | COMMENTS               |

|---------------------------------------|------------------|-----|------|-------|----------|------------------------|

| AC CHARACTERISTICS                    |                  |     |      |       | _        |                        |

| Clock Frequency                       | f⊤, fa           | 980 | 1000 | 1020  | KHz      |                        |

| Clock Duty Cycle                      | ,                | 45  | 50   | 55    | %        |                        |

| Rise and fall times, IA, TDE          |                  | 1   |      |       |          |                        |

| TX MODE, SWE, RDE                     | tr, tf           |     |      | 20    | ns       |                        |

| rise and fall times, all              |                  |     |      | 50    |          |                        |

| other inputs                          | tr, tf           |     |      | 50    | ns       | e an                   |

| receiver clock-NRZ                    | trn              |     |      | 65    | ns       | figure 3B              |

| receiver clock-sync delay             | tsя              |     |      | 85    | ns       | figure 3B              |

| receiver clock-VW delay               | trv              |     |      | 100   | ns       | figure 3B              |

| VW reset delay                        | tvs              | 0.5 |      | 500   | ns       | figure 3C              |

| transmit clock-TX ENA delay           | tтх              | 25  |      |       | ns       | figure 4A              |

| TX ENA pulse width                    | txw              | 60  | İ    | 40    | ns       | figure 4A<br>figure 4B |

| transmit clock-send data set-up       | trs              | 1   | ļ    | 40    | ns       | figure 46              |

| transmit clock-send data hold time    | tsr              |     |      | 140   | ns       | figure 4B              |

| transmit clock fall to NRZ            | ttn              | 0   | ľ    |       | ns<br>ns | figure 4B              |

| transmit clock rise to NRZ            | tnt              | 95  |      |       | ns       | figure 5A              |

| TX MODE pulse width                   | tww              | 150 |      | 750   | ns       | figure 5B              |

| TX MODE to TX ENA delay               | tmx              |     |      | 750   | ns       | figure 5B              |

| VALID word to TX ENA delay            | tvx              |     |      | 750   | ns       | figure 5C              |

| Data sync to TX ENA delay             | tox              |     |      | 750   | ns       | figure 5C              |

| TX ENA reset delay                    | tsx              | 100 |      | /30   | ns       | figure 6A              |

| DATA SET-up time                      | to:              | 150 |      |       | ns       | figure 6A              |

| TDE pulse width                       | to2              | 100 |      |       | ns       | figure 6A              |

| Data Hold time                        | tD3              | 450 |      | 16000 | ns       | figure 6A              |

| Cycle time                            | tos              | 450 |      | 10000 | ns       | figure 6A              |

| DTA RQST Delay                        | tps              | 100 |      |       | ns       | figure 6B              |

| Output Enable time RDE Pulse width    | tor              | 150 |      |       | ns       | figure 6B              |

|                                       | tos              | 450 |      | 17000 | ns       | figure 6B              |

| receive cycle time<br>Flag delay time | tps              | 450 | İ    |       | ns       | figure 6B              |

| Output disable time                   | t <sub>D10</sub> | 100 |      |       | ns       | figure 6B              |

| SEND DATA delay                       | tpm              | 2.5 |      | 3.5   | μs       | figure 6C              |

| TDE off delay                         | tp12             | 1.5 |      |       | μs       | figure 6C              |

| TDE1 delay                            | tp13             | 500 |      | 1     | ns       | figure 6C              |

| SYN to RDE                            | t <sub>D14</sub> | 500 |      |       | ns       | figure 6D              |

| RDE to SYN                            | t <sub>D15</sub> |     |      | 2.5   | μs       | figure 6D              |

| Status word Enable                    | tse              |     |      | 100   | ns       | figure 8A              |

| Status word Disable                   | tsp              |     |      | 100   | ns       | figure 8A              |

| Flag delay time                       | tcr              |     |      | 1     | μs       | figure 8B              |

| VW delay time                         | tcv              |     |      | 90    | ns       | figure 8B              |

| IVWF delay time                       | tcı              | 1   |      | 450   | ns       | figure 8B              |

| DTA AVL delay time                    | tcp              |     |      | 500   | ns       | figure 8B              |

| DTA RQST delay time                   | tsa              |     |      | 450   | ns       | figure 8C              |

| BRD CST delay time                    | tяв              |     |      | 2     | μs       | figure 8C              |

| BRD CST pulse width                   | tew              | 1   |      | Į     | μs       | figure 8D              |

| flag reset delay                      | tıв              |     |      | 750   | ns       | figure 8D, 8E          |

| Interrupt delay                       | tri              |     |      | 1.5   | μs       | figure 8D              |

| IA pulse width                        | tia              | 150 |      |       | ns       | figure 8D              |

| Interrupt pulse width                 | tiw              | 1   |      |       | μs       | figure 8D              |

| Flag reset time                       | tFR              | 1   |      | 450   | ns       | figure 8F              |

| DTA AVL reset delay                   | tro              |     |      | 750   | ns       | figure 8F              |

| IVWF reset delay                      | trv              |     |      | 750   | ns       | figure 8F              |

| MSG CMPLT turn-on delay               | tmr              |     |      | 1.5   | μs       | figure 9A, 9B          |

| MSG CMPLT turn-on delay               | tmf              |     | 1    | 1.5   | μS       | figure 9A, 9C          |

|                                       |                  |     |      |       |          |                        |

## TRANSMIT ENABLE (TX ENA) TIMING FIGURE 5

\*THIS IS A CMD WORD BEING RECEIVED. IT IS ADDRESSED TO THIS BUFFER AND THE T/R BIT \* 1. TX ENA IS RESET BY 2ND TX MODE NEGATIVE TRANSITION OR BY LAST SEND DATA (MESSAGE COMPLETE FUNCTION).

\*\*THIS IS THE LAST DATA WORD BRING RECEIVED. THIS TERMINAL PREVIOUSLY HAD RECEIVED A REC CMD WORD WITH OUR ADDRESS AND A REC'XMIT BIT = 0 DURING THIS MESSAGE SEQUENCE. TX ENABLE IS SET BY MSG CMPLT FUNCTION AND RESET BY RECEIPT OF SEND DATA.

## **DATA BUS TIMING FIGURE 6**

## 6B

## **DATA BUS TIMING FIGURE 6**

## 6C

## **IA RESETS FIGURE 7**

TÁ OCCURRING DURING ZONE A RESETS: BRD CST, TX INT, REC INT, IA OCCURRING DURING ZONE B RESETS: BRD CST, TX INT, REC INT, "0" MSG FLG.

TÁ OCCURRING DURING ZONE C RESETS: BRD CST, TX INT, REC INT, "0" MSG FLG.

"0" WRD FLG.

## **MESSAGE COMPLETE FIGURE 9**

## **BUS CONTROLLER MODE**

"WORD COUNTER IS PRESET TO 33

9A

9B

9C

"MSG CMPLT SET two MAX AFTER RISE OF 33RD SEND DATA PULSE

## REMOTE TERMINAL, RECEIVE COMMAND RECEIVED

"WORD COUNTER PRESET TO COUNT IN COMMAND WORD

"MSG CMPLT GENERATED BY LAST DATA SYNC OF

THE MESSAGE GROUP

## REMOTE TERMINAL, TRANSMIT COMMAND RECEIVED

WORD COUNTER PRESET TO TRANSMIT COMMAND WORD FIELD PLUS 1. THIS ALLOWS FOR THE STATUS WORD.

"MSG CMPLT GENERATED BY THE LAST SEND DATA OF THE TRANSMIT MESSAGE GROUP.

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patient rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.