## FEATURES

- ◆ 25 dBm Output Power at 1-dB Compression at 18 GHz

- ♦ 9.5 dB Power Gain at 18 GHz

- ♦ 55% Power-Added Efficiency

- ♦ Source Vias to Backside Metallization

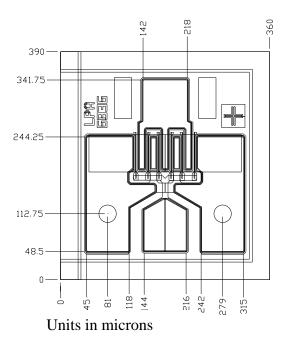

DIE SIZE: 15.4X14.2 mils (390x360 μm)

DIE THICKNESS: 3.9 mils (100 μm)

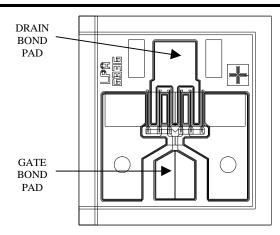

BONDING PADS: 3.0X3.0 mils (75x75 μm)

# DESCRIPTION AND APPLICATIONS

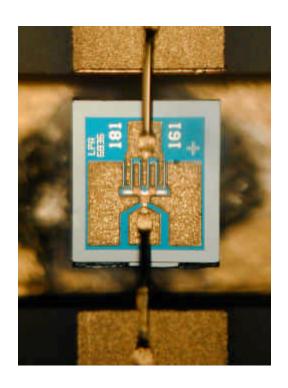

The FPA6836V is an Aluminum Gallium Arsenide / Indium Gallium Arsenide (AlGaAs/InGaAs) Pseudomorphic High Electron Mobility Transistor (PHEMT), utilizing an Electron-Beam direct-write  $0.25~\mu m$  by  $360~\mu m$  Schottky barrier gate. The recessed "mushroom" gate structure minimizes parasitic gate-source and gate resistances. The epitaxial structure and processing have been optimized for high dynamic range.

Typical applications include high dynamic range driver stages for commercial applications including wireless infrastructure systems, broad bandwidth amplifiers, and optical systems.

Source vias have been added for improved performance and assembly convenience. Each via hole has 0.02 nH of inductance. Additionally, the via holes remove the need for source bond wires, meaning only two bond wires are required for assembly. Because the via connects the source pad to the backside metallization, self-bias configurations should be designed with caution.

# ELECTRICAL SPECIFICATIONS @ T<sub>Ambient</sub> = 25°C

| Parameter                                  | Symbol           | <b>Test Conditions</b>                        | Min   | Тур  | Max  | Units |

|--------------------------------------------|------------------|-----------------------------------------------|-------|------|------|-------|

| Saturated Drain-Source Current             | $I_{DSS}$        | $V_{DS} = 2 \text{ V}; V_{GS} = 0 \text{ V}$  | 80    | 115  | 125  | mA    |

| Power at 1-dB Compression                  | P-1dB            | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$ | 24    | 25   |      | dBm   |

| Power Gain at 1-dB Compression             | G-1dB            | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$ | 8.5   | 9.5  |      | dB    |

| Power-Added Efficiency                     | PAE              | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$ |       | 55   |      | %     |

| Maximum Drain-Source Current               | $I_{MAX}$        | $V_{DS} = 2 \text{ V}; V_{GS} = 1 \text{ V}$  |       | 190  |      | mA    |

| Transconductance                           | $G_{M}$          | $V_{DS} = 2 V; V_{GS} = 0 V$                  | 75    | 100  |      | mS    |

| Gate-Source Leakage Current                | $I_{GSO}$        | $V_{GS} = -5 \text{ V}$                       |       | 1    | 10   | μΑ    |

| Pinch-Off Voltage                          | $V_P$            | $V_{DS} = 2 \text{ V}; I_{DS} = 2 \text{ mA}$ | -0.25 | -1.2 | -2.0 | V     |

| Gate-Source Breakdown<br>Voltage Magnitude | $ V_{BDGS} $     | $I_{GS} = 2 \text{ mA}$                       | 11    | 15   |      | V     |

| Gate-Drain Breakdown<br>Voltage Magnitude  | $ V_{BDGD} $     | $I_{GD} = 2 \text{ mA}$                       | 12    | 16   |      | V     |

| Thermal Resistivity                        | $\Theta_{ m JC}$ |                                               |       | 100  |      | °C/W  |

frequency=18 GHz

Phone: (408) 988-1845 http://www.filss.com Revised: 2/22/02 Fax: (408) 970-9950 Email: sales@filss.com

# • ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol           | <b>Test Conditions</b>              | Min | Max         | Units |

|-------------------------------|------------------|-------------------------------------|-----|-------------|-------|

| Drain-Source Voltage          | $V_{DS}$         | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | 10          | V     |

| Gate-Source Voltage           | $V_{GS}$         | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | -4          | V     |

| Drain-Source Current          | $I_{DS}$         | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | $2xI_{DSS}$ | mA    |

| Gate Current                  | $I_{G}$          | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | 18          | mA    |

| RF Input Power                | P <sub>IN</sub>  | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | 180         | mW    |

| Channel Operating Temperature | $T_{CH}$         | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | 175         | °C    |

| Storage Temperature           | $T_{STG}$        | _                                   | -65 | 175         | °C    |

| Total Power Dissipation       | P <sub>TOT</sub> | $T_{Ambient} = 22 \pm 3  ^{\circ}C$ |     | 1.4         | W     |

#### Notes:

Operating conditions that exceed the Absolute Maximum Ratings could result in permanent damage to the device.

• Power Dissipation defined as:  $P_{TOT} \equiv (P_{DC} + P_{IN}) - P_{OUT}$ , where

P<sub>DC</sub>: DC Bias Power P<sub>IN</sub>: RF Input Power P<sub>OUT</sub>: RF Output Power

Absolute Maximum Power Dissipation to be de-rated as follows above 25°C:

$P_{TOT} = 1.4W - (0.0093W/^{\circ}C) \times T_{HS}$

where  $T_{HS}$  = heatsink or ambient temperature.

### HANDLING PRECAUTIONS

To avoid damage to the devices care should be exercised during handling. Proper Electrostatic Discharge (ESD) precautions should be observed at all stages of storage, handling, assembly, and testing. These devices should be treated as Class 1A (0-500 V). Further information on ESD control measures can be found in MIL-STD-1686 and MIL-HDBK-263.

## ASSEMBLY INSTRUCTIONS

The recommended die attach is gold/tin eutectic solder under a nitrogen atmosphere. Stage temperature should be 280-290°C; maximum time at temperature is one minute. The recommended wire bond method is thermo-compression wedge bonding with 0.7 or 1.0 mil (0.018 or 0.025 mm) gold wire. Stage temperature should be 250-260°C.

## APPLICATIONS NOTES & DESIGN DATA

Applications Notes are available from your local Filtronic Sales Representative or directly from the factory. Complete design data, including S-parameters, noise data, and large-signal models are available on the Filtronic web site.

# **Preliminary Data Sheet**