# FSF150D, FSF150R

25A, 100V, 0.070 Ohm, Rad Hard, SEGR Resistant, N-Channel Power MOSFETs

June 1998

### **Features**

- 25A, 100V,  $r_{DS(ON)} = 0.070\Omega$

- Total Dose

- Meets Pre-RAD Specifications to 100K RAD (Si)

- Single Event

- Safe Operating Area Curve for Single Event Effects

- SEE Immunity for LET of 36MeV/mg/cm<sup>2</sup> with V<sub>DS</sub> up to 80% of Rated Breakdown and V<sub>GS</sub> of 10V Off-Bias

- Dose Rate

- Typically Survives 3E9 RAD (Si)/s at 80% BVDSS

- Typically Survives 2E12 if Current Limited to IDM

- Photo Current

- 7.0nA Per-RAD(Si)/s Typically

- Neutron

- Maintain Pre-RAD Specifications for 3E13 Neutrons/cm<sup>2</sup>

- Usable to 3E14 Neutrons/cm<sup>2</sup>

# **Ordering Information**

| RAD LEVEL | SCREENING LEVEL | PART NUMBER/BRAND |

|-----------|-----------------|-------------------|

| 10K       | Commercial      | FSF150D1          |

| 10K       | TXV             | FSF150D3          |

| 100K      | Commercial      | FSF150R1          |

| 100K      | TXV             | FSF150R3          |

| 100K      | Space           | FSF150R4          |

Formerly available as type TA17656.

# Description

The Discrete Products Operation of Intersil Corporation has developed a series of Radiation Hardened MOSFETs specifically designed for commercial and military space applications. Enhanced Power MOSFET immunity to Single Event Effects (SEE), Single Event Gate Rupture (SEGR) in particular, is combined with 100K RADS of total dose hardness to provide devices which are ideally suited to harsh space environments. The dose rate and neutron tolerance necessary for military applications have not been sacrificed.

The Intersil portfolio of SEGR resistant radiation hardened MOSFETs includes N-Channel and P-Channel devices in a variety of voltage, current and on-resistance ratings. Numerous packaging options are also available.

This MOSFET is an enhancement-mode silicon-gate power field-effect transistor of the vertical DMOS (VDMOS) structure. It is specially designed and processed to be radiation tolerant. The MOSFET is well suited for applications exposed to radiation environments such as switching regulation, switching converters, motor drives, relay drivers and drivers for high-power bipolar switching transistors requiring high speed and low gate drive power. This type can be operated directly from integrated circuits.

Reliability screening is available as either commercial, TXV equivalent of MIL-S-19500, or Space equivalent of MIL-S-19500. Contact Intersil for any desired deviations from the data sheet.

### Symbol

### **Package**

**TO-254AA**

CAUTION: Beryllia Warning per MIL-S-19500 refer to package specifications.

# FSF150D, FSF150R

# **Absolute Maximum Ratings** $T_C = 25^{\circ}C$ , Unless Otherwise Specified

|                                                               | FSF150D, FSF150R | UNITS |

|---------------------------------------------------------------|------------------|-------|

| Drain to Source Voltage                                       | 100              | V     |

| Drain to Gate Voltage ( $R_{GS} = 20k\Omega$ )                | 100              | V     |

| Continuous Drain Current                                      |                  |       |

| $T_C = 25^{\circ}C$ $I_D$                                     | 25 (Note 1)      | Α     |

| $T_C = 100^{\circ}C$ $I_D$                                    | 20               | Α     |

| Pulsed Drain Current                                          | 75               | Α     |

| Gate to Source VoltageV <sub>GS</sub>                         | ±20              | V     |

| Maximum Power Dissipation                                     |                  |       |

| $T_C = 25^{\circ}C \dots P_T$                                 | 125              | W     |

| $T_C = 100^{\circ}C$ $P_T$                                    | 50               | W     |

| Linear Derating Factor                                        | 1.00             | W/°C  |

| Single Pulsed Avalanche Current, L = 100μH, (See Test Figure) | 75               | Α     |

| Continuous Source Current (Body Diode)                        | 25 (Note 1)      | Α     |

| Pulsed Source Current (Body Diode)                            | 75               | Α     |

| Operating and Storage Temperature                             | -55 to 150       | °C    |

| Lead Temperature (During Soldering)                           | 300              | °C    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1. Current is limited by the package capability.

# **Electrical Specifications** $T_C = 25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                              | SYMBOL                 | TEST CON                                               | IDITIONS                                   | MIN | TYP   | MAX   | UNITS |

|----------------------------------------|------------------------|--------------------------------------------------------|--------------------------------------------|-----|-------|-------|-------|

| Drain to Source Breakdown Voltage      | BV <sub>DSS</sub>      | $I_D = 1 \text{mA}, V_{GS} = 0$                        | $I_D = 1mA$ , $V_{GS} = 0V$                |     | -     | -     | V     |

| Gate Threshold Voltage                 | V <sub>GS(TH)</sub>    | $V_{GS} = V_{DS}$                                      | $T_C = -55^{\circ}C$                       | -   | -     | 5.0   | V     |

|                                        | I <sub>D</sub> = 1mA   | $T_{\rm C} = 25^{\rm o}{\rm C}$                        | 1.5                                        | -   | 4.0   | V     |       |

|                                        |                        |                                                        | $T_{\rm C} = 125^{\rm o}{\rm C}$           | 0.5 | -     | -     | V     |

| Zero Gate Voltage Drain Current        | I <sub>DSS</sub>       | V <sub>DS</sub> = 80V,                                 | $T_C = 25^{\circ}C$                        | -   | -     | 25    | μΑ    |

|                                        |                        | $V_{GS} = 0V$                                          | $T_{\rm C} = 125^{\rm o}{\rm C}$           | -   | -     | 250   | μΑ    |

| Gate to Source Leakage Current         | I <sub>GSS</sub>       | V <sub>GS</sub> = ±20V                                 | $T_{C} = 25^{\circ}C$                      | -   | -     | 100   | nA    |

|                                        |                        |                                                        | $T_{C} = 125^{\circ}C$                     |     |       | 200   | nA    |

| Drain to Source On-State Voltage       | V <sub>DS(ON)</sub>    | $V_{GS} = 12V, I_D = 25.$                              | A                                          |     |       | 1.84  | V     |

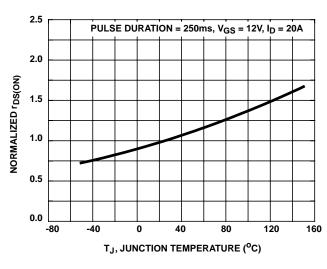

| Drain to Source On Resistance          |                        | I <sub>D</sub> = 20A,                                  | $T_{C} = 25^{\circ}C$                      | -   | 0.045 | 0.070 | Ω     |

|                                        |                        | V <sub>GS</sub> = 12V                                  | $V_{GS} = 12V \qquad T_{C} = 125^{\circ}C$ | -   | -     | 0.105 | Ω     |

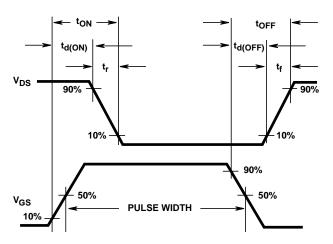

| Turn-On Delay Time                     | t <sub>d(ON)</sub>     | V <sub>DD</sub> = 50V, I <sub>D</sub> = 25A,           |                                            | -   | -     | 140   | ns    |

| Rise Time                              | t <sub>r</sub>         | $R_L = 2.0\Omega, V_{GS} = 1$<br>$R_{GS} = 2.35\Omega$ | 2V,                                        | -   | -     | 310   | ns    |

| Turn-Off Delay Time                    | t <sub>d(OFF)</sub>    | 11.63 = 2.0022                                         |                                            | -   | -     | 170   | ns    |

| Fall Time                              | t <sub>f</sub>         | ]                                                      |                                            | -   | -     | 70    | ns    |

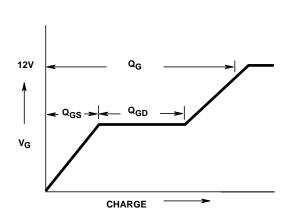

| Total Gate Charge                      | Q <sub>g(TOT)</sub>    | $V_{GS} = 0V \text{ to } 20V$                          | V <sub>DD</sub> = 50V,                     | -   | -     | 240   | nC    |

| Gate Charge at 12V                     | Q <sub>g(12)</sub>     | V <sub>GS</sub> = 0V to 12V                            | I <sub>D</sub> = 25A                       | -   | 130   | 160   | nC    |

| Threshold Gate Charge                  | Q <sub>g(TH)</sub>     | $V_{GS} = 0V \text{ to } 2V$                           |                                            | -   | -     | 8.1   | nC    |

| Gate Charge Source                     | Q <sub>gs</sub>        |                                                        | ]                                          | -   | 23    | 31    | nC    |

| Gate Charge Drain                      | Q <sub>gd</sub>        |                                                        |                                            | -   | 67    | 88    | nC    |

| Plateau Voltage                        | V <sub>(PLATEAU)</sub> | I <sub>D</sub> = 25A, V <sub>DS</sub> = 15             | V                                          | -   | 7     | -     | ٧     |

| Input Capacitance                      | C <sub>ISS</sub>       | $V_{DS} = 25V, V_{GS} = 0$                             | OV,                                        | -   | 3250  | -     | pF    |

| Output Capacitance                     | C <sub>OSS</sub>       | f = 1MHz                                               |                                            | -   | 1060  | -     | pF    |

| Reverse Transfer Capacitance           | C <sub>RSS</sub>       |                                                        |                                            | -   | 370   | -     | pF    |

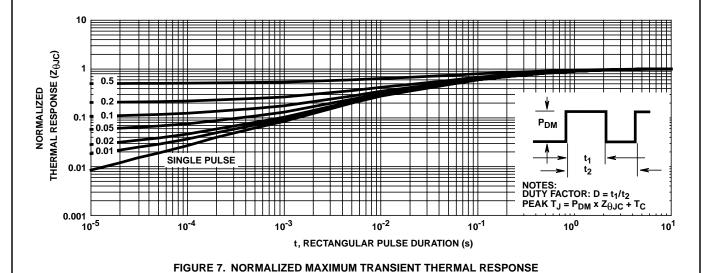

| Thermal Resistance Junction to Case    | $R_{\theta JC}$        |                                                        |                                            | -   | -     | 1.00  | °C/W  |

| Thermal Resistance Junction to Ambient | $R_{\theta JA}$        |                                                        |                                            | -   | -     | 48    | °C/W  |

### **Source to Drain Diode Specifications**

| PARAMETER             | SYMBOL          | TEST CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|-----------------------|-----------------|-------------------------------------------------------|-----|-----|-----|-------|

| Forward Voltage       | $V_{SD}$        | I <sub>SD</sub> = 25A                                 | 0.6 | -   | 1.8 | V     |

| Reverse Recovery Time | t <sub>rr</sub> | I <sub>SD</sub> = 25A, dI <sub>SD</sub> /dt = 100A/μs | -   | -   | 400 | ns    |

### Electrical Specifications up to 100K RAD $T_C = 25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                       |              | SYMBOL                | TEST CONDITIONS                             | MIN | MAX   | UNITS |

|---------------------------------|--------------|-----------------------|---------------------------------------------|-----|-------|-------|

| Drain to Source Breakdown Volts | (Note 3)     | BV <sub>DSS</sub>     | $V_{GS} = 0$ , $I_D = 1mA$                  | 100 | -     | V     |

| Gate to Source Threshold Volts  | (Note 3)     | V <sub>GS(TH)</sub>   | $V_{GS} = V_{DS}$ , $I_D = 1mA$             | 1.5 | 4.0   | V     |

| Gate to Body Leakage            | (Notes 2, 3) | I <sub>GSS</sub>      | $V_{GS} = \pm 20V, V_{DS} = 0V$             | -   | 100   | nA    |

| Zero Gate Leakage               | (Note 3)     | I <sub>DSS</sub>      | V <sub>GS</sub> = 0, V <sub>DS</sub> = 80V  | -   | 25    | μΑ    |

| Drain to Source On-State Volts  | (Notes 1, 3) | V <sub>DS(ON)</sub>   | V <sub>GS</sub> = 12V, I <sub>D</sub> = 25A | -   | 1.84  | V     |

| Drain to Source On Resistance   | (Notes 1, 3) | r <sub>DS(ON)12</sub> | $V_{GS} = 12V, I_D = 20A$                   | -   | 0.070 | Ω     |

### NOTES:

- 2. Pulse test, 300µs Max.

- 3. Absolute value.

- 4. Insitu Gamma bias must be sampled for both  $V_{GS}$  = 12V,  $V_{DS}$  = 0V and  $V_{GS}$  = 0V,  $V_{DS}$  = 80% BV<sub>DSS</sub>.

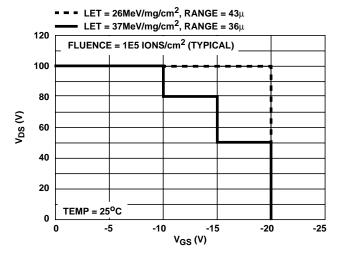

### Single Event Effects (SEB, SEGR) (Note 4)

|                                     |        | EN             | VIRONMENT (NOTE            |                      | (NOTE 6)                               |                                        |

|-------------------------------------|--------|----------------|----------------------------|----------------------|----------------------------------------|----------------------------------------|

| TEST                                | SYMBOL | ION<br>SPECIES | TYPICAL LET<br>(MeV/mg/cm) | TYPICAL<br>RANGE (μ) | APPLIED<br>V <sub>GS</sub> BIAS<br>(V) | MAXIMUM<br>V <sub>DS</sub> BIAS<br>(V) |

| Single Event Effects Safe Operating | SEESOA | Ni             | 26                         | 43                   | -20                                    | 100                                    |

| Area                                |        | Br             | 37                         | 36                   | -10                                    | 100                                    |

|                                     |        | Br             | 37                         | 36                   | -15                                    | 80                                     |

|                                     |        | Br             | 37                         | 36                   | -20                                    | 50                                     |

### NOTES:

- 5. Testing conducted at Brookhaven National Labs; sponsored by Naval Surface Warfare Center (NSWC), Crane, IN.

- 6. Fluence =  $1E5 \text{ ions/cm}^2 \text{ (typical)}, T = <math>25^{\circ}\text{C}$ .

- 7. Does not exhibit Single Event Burnout (SEB) or Single Event Gate Rupture (SEGR).

# Typical Performance Curves Unless Otherwise Specified

FIGURE 1. SINGLE EVENT EFFECTS SAFE OPERATING AREA

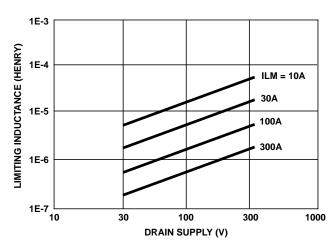

FIGURE 2. DRAIN INDUCTANCE REQUIRED TO LIMIT GAMMA DOT CURRENT TO IAS

# Typical Performance Curves Unless Otherwise Specified (Continued)

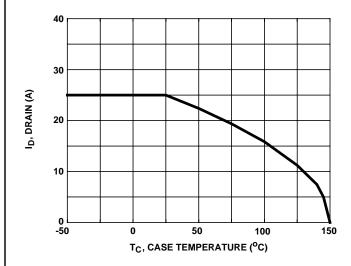

FIGURE 3. MAXIMUM CONTINUOUS DRAIN CURRENT vs TEMPERATURE

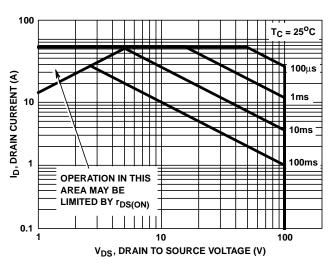

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA

FIGURE 5. BASIC GATE CHARGE WAVEFORM

FIGURE 6. NORMALIZED r<sub>DS(ON)</sub> vs JUNCTION TEMPERATURE

# Typical Performance Curves Unless Otherwise Specified (Continued)

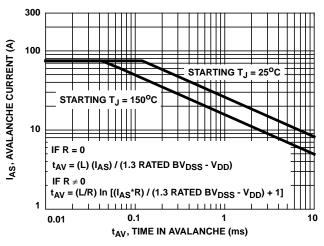

FIGURE 8. UNCLAMPED INDUCTIVE SWITCHING

# Test Circuits and Waveforms

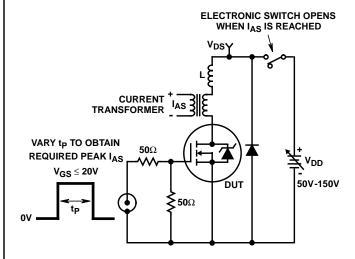

FIGURE 9. UNCLAMPED ENERGY TEST CIRCUIT

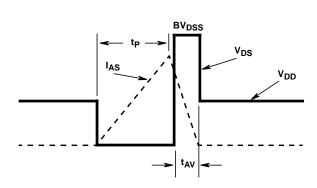

FIGURE 10. UNCLAMPED ENERGY WAVEFORMS

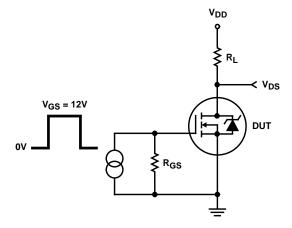

FIGURE 11. RESISTIVE SWITCHING TEST CIRCUIT

FIGURE 12. RESISTIVE SWITCHING WAVEFORMS

# **Screening Information**

Screening is performed in accordance with the latest revision in effect of MIL-S-19500, (Screening Information Table).

Delta Tests and Limits (JANTXV Equivalent, JANS Equivalent) T<sub>C</sub> = 25°C, Unless Otherwise Specified

| PARAMETER                       | SYMBOL              | TEST CONDITIONS                               | MAX           | UNITS |

|---------------------------------|---------------------|-----------------------------------------------|---------------|-------|

| Gate to Source Leakage Current  | I <sub>GSS</sub>    | $V_{GS} = \pm 20V$                            | ±20 (Note 7)  | nA    |

| Zero Gate Voltage Drain Current | I <sub>DSS</sub>    | V <sub>DS</sub> = 80% Rated Value             | ±25 (Note 7)  | μΑ    |

| Drain to Source On Resistance   | r <sub>DS(ON)</sub> | T <sub>C</sub> = 25°C at Rated I <sub>D</sub> | ±20% (Note 8) | Ω     |

| Gate Threshold Voltage          | V <sub>GS(TH)</sub> | I <sub>D</sub> = 1.0mA                        | ±20% (Note 8) | V     |

### NOTES:

- 8. Or 100% of Initial Reading (whichever is greater).

- 9. Of Initial Reading.

# **Screening Information**

| TEST                                        | JANTXV EQUIVALENT                                                                                                   | JANS EQUIVALENT                                                                                                    |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Gate Stress                                 | V <sub>GS</sub> = 30V, t = 250μs                                                                                    | V <sub>GS</sub> = 30V, t = 250μs                                                                                   |

| Pind                                        | Optional                                                                                                            | Required                                                                                                           |

| Pre Burn-In Tests (Note 9)                  | MIL-S-19500 Group A,<br>Subgroup 2 (All Static Tests at 25 <sup>o</sup> C)                                          | MIL-S-19500 Group A,<br>Subgroup 2 (All Static Tests at 25 <sup>o</sup> C)                                         |

| Steady State Gate<br>Bias (Gate Stress)     | MIL-STD-750, Method 1042, Condition B<br>$V_{GS} = 80\%$ of Rated Value,<br>$T_A = 150^{\circ}$ C, Time = 48 hours  | MIL-STD-750, Method 1042, Condition B<br>$V_{GS} = 80\%$ of Rated Value,<br>$T_A = 150^{\circ}$ C, Time = 48 hours |

| Interim Electrical Tests (Note 9)           | All Delta Parameters Listed in the Delta Tests and Limits Table                                                     | All Delta Parameters Listed in the Delta Tests and Limits Table                                                    |

| Steady State Reverse<br>Bias (Drain Stress) | MIL-STD-750, Method 1042, Condition A<br>$V_{DS} = 80\%$ of Rated Value,<br>$T_A = 150^{\circ}$ C, Time = 160 hours | MIL-STD-750, Method 1042, Condition A $V_{DS}$ = 80% of Rated Value, $T_A$ = 150°C, Time = 240 hours               |

| PDA                                         | 10%                                                                                                                 | 5%                                                                                                                 |

| Final Electrical Tests (Note 9)             | MIL-S-19500, Group A, Subgroup 2                                                                                    | MIL-S-19500, Group A,<br>Subgroups 2 and 3                                                                         |

### NOTE:

# **Additional Screening Tests**

| PARAMETER                     | SYMBOL           | TEST CONDITIONS                                                   | MAX  | UNITS |

|-------------------------------|------------------|-------------------------------------------------------------------|------|-------|

| Safe Operating Area           | SOA              | V <sub>DS</sub> = 80V, t = 10ms                                   | 4.50 | А     |

| Unclamped Inductive Switching | I <sub>AS</sub>  | V <sub>GS(PEAK)</sub> = 15V, L = 0.1mH                            | 75   | А     |

| Thermal Response              | ΔV <sub>SD</sub> | t <sub>H</sub> = 100ms; V <sub>H</sub> = 25V; I <sub>H</sub> = 4A | 136  | mV    |

| Thermal Impedance             | ΔV <sub>SD</sub> | $t_H = 500 \text{ms}; V_H = 25 \text{V}; I_H = 4 \text{A}$        | 187  | mV    |

<sup>10.</sup> Test limits are identical pre and post burn-in.

### Rad Hard Data Packages - Intersil Power Transistors

#### **TXV** Equivalent

#### 1. Rad Hard TXV Equivalent - Standard Data Package

- A. Certificate of Compliance

- B. Assembly Flow Chart

- C. Preconditioning Attributes Data Sheet

D. Group A Attributes Data Sheet

E. Group B Attributes Data Sheet

F. Group C Attributes Data Sheet

G. Group D Attributes Data Sheet

#### 2. Rad Hard TXV Equivalent - Optional Data Package

- A. Certificate of Compliance

- B. Assembly Flow Chart

- C. Preconditioning Attributes Data Sheet

- Precondition Lot Traveler

- Pre and Post Burn-In Read and Record

- D. Group A Attributes Data Sheet

- Group A Lot Traveler

- E. Group B Attributes Data SheetGroup B Lot Traveler

- Pre and Post Read and Record Data for Intermittent Operating Life (Subgroup B3)

Bond Strength Data (Subgroup B3)

Pre and Post High Temperature Operating Life Read and Record Data (Subgroup B6)

- F. Group C Attributes Data Sheet Group C Lot Traveler

- Pre and Post Read and Record Data for Intermittent Operating Life (Subgroup C6)

Bond Strength Data (Subgroup C6)

- G. Group D Attributes Data Sheet

- Group D Lot Traveler

- Pre and Post RAD Read and Record Data

### Class S - Equivalents

### 1. Rad Hard "S" Equivalent - Standard Data Package

- A. Certificate of Compliance

- B. Serialization Records

- C. Assembly Flow Chart

- D. SEM Photos and Report

E. Preconditioning Attributes Data Sheet

Hi-Rel Lot Traveler

HTRB - Hi Temp Gate Stress Post Reverse

Bias Data and Delta Data

HTRB - Hi Temp Drain Stress Post Reverse

Bias Delta Data

F. Group A

G. Group B

H. Group C

I. Group D

Attributes Data Sheet

Attributes Data Sheet

Attributes Data Sheet

#### 2. Rad Hard Max. "S" Equivalent - Optional Data Package

- A. Certificate of Compliance

- B. Serialization Records

- C. Assembly Flow Chart

- D. SEM Photos and Report

- E. Preconditioning Attributes Data Sheet

- Hi-Rel Lot Traveler

HTRB - Hi Temp Gate Stress Post Reverse Bias Data and Delta Data

HTRB - Hi Temp Drain Stress Post Reverse Bias Delta Data

- X-Ray and X-Ray Report

F. Group A - Attributes Data Sheet

Hi-Rel Lot Traveler

- Subgroups A2, A3, A4, A5 and A7 Data

G. Group B - Attributes Data Sheet

Hi-Rel Lot Traveler

- Subgroups B1, B3, B4, B5 and B6 Data

H. Group C - Attributes Data Sheet

- Hi-Rel Lot Traveler

- Subgroups C1, C2, C3 and C6 Data

I. Group D - Attributes Data Sheet

- Hi-Rel Lot Traveler

- Pre and Post Radiation Data

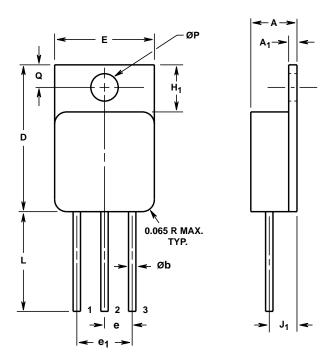

### TO-254AA

### 3 LEAD JEDEC TO-254AA HERMETIC METAL PACKAGE

|                | INC   | HES                | MILLIMETERS |       |       |

|----------------|-------|--------------------|-------------|-------|-------|

| SYMBOL         | MIN   | MAX                | MIN         | MAX   | NOTES |

| Α              | 0.249 | 0.260              | 6.33        | 6.60  | -     |

| A <sub>1</sub> | 0.040 | 0.050              | 1.02        | 1.27  | -     |

| Øb             | 0.035 | 0.045              | 0.89        | 1.14  | 2, 3  |

| D              | 0.790 | 0.800              | 20.07       | 20.32 | -     |

| E              | 0.535 | 0.545              | 13.59       | 13.84 | -     |

| е              | 0.150 | TYP                | 3.81        | TYP   | 4     |

| e <sub>1</sub> | 0.300 | 0.300 BSC 7.62 BSC |             | BSC   | 4     |

| H <sub>1</sub> | 0.245 | 0.265              | 6.23        | 6.73  | -     |

| J <sub>1</sub> | 0.140 | 0.160              | 3.56        | 4.06  | 4     |

| L              | 0.520 | 0.560              | 13.21       | 14.22 | -     |

| ØP             | 0.139 | 0.149              | 3.54        | 3.78  | -     |

| Q              | 0.110 | 0.130              | 2.80        | 3.30  | -     |

#### NOTES:

- These dimensions are within allowable dimensions of Rev. A of JEDEC outline TO-254AA dated 11-86.

- 2. Add typically 0.002 inches (0.05mm) for solder coating.

- 3. Lead dimension (without solder).

- Position of lead to be measured 0.250 inches (6.35mm) from bottom of dimension D.

- 5. Die to base BeO isolated, terminals to case ceramic isolated.

- 6. Controlling dimension: Inch.

- 7. Revision 1 dated 1-93.

# **WARNING!**

### **BERYLLIA WARNING PER MIL-S-19500**

Packages containing beryllium oxide (BeO) shall not be ground, machined, sandblasted, or subject to any mechanical operation which will produce dust containing any beryllium compound. Packages containing any beryllium compound shall not be subjected to any chemical process (etching, etc.) which will produce fumes containing beryllium or its' compounds.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

#### **NORTH AMERICA**

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000

FAX: (407) 724-7000 FAX: (407) 724-7240

#### **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029