# **Satellite Channel Demodulator**

# **Preliminary Information**

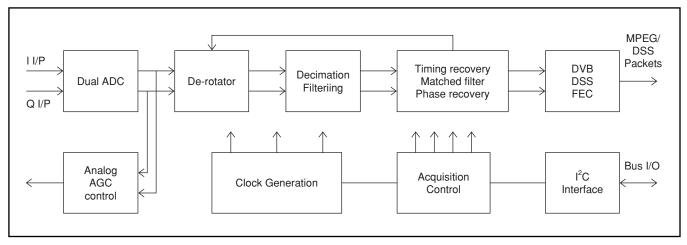

The VP310 is a QPSK/BPSK 1 to 45 MBaud demodulator and channel decoder for digital satellite television transmissions to the European Broadcast Union ETS 300 421 specification. It receives analog I and Q signals from the tuner, digitises and digitally demodulates the signals, and implements the complete DVB/DSS FEC (Forward Error Correction), and de-scrambling function. The output is in the form of MPEG2 or DSS transport stream data packets. The VP310 also provides automatic gain control to the RF front-end devices.

The VP310 has a serial I<sup>2</sup>C port interface to the control microprocessor. Minimal software is required to control the VP310 because of the built in automatic search and decode control functions.

# **Applications**

- DVB 1 to 45 MBaud compliant satellite receivers

- DSS 20 MBaud compliant satellite receivers

- SCPC receivers (Single Channel Per Carrier)

- SMATV trans-modulators (Single Master Antenna TV)

- LMDS (Local Multipoint Distribution Service)

- Satellite PC applications

# **Key Features**

- Conforms to EBU specification for DVB-S and DirecTV specification for DSS

- On-chip digital filtering supports 1 to 45 MBaud Symbol rates

- On-chip 6-bit 60 or 90 MHz dual-ADC

- High speed scanning mode for blind symbol rate and code rate acquisition

# Ordering Information VP310 CG GQ1N

- Up to ± 15 MHz LNB frequency tracking

- Fully digital timing and phase recovery loops

- High level software interface for minimum development time

- DiSEqC<sup>™</sup> v1.1: control outputs for full control of LNB and dish

### **Additional Features**

- I<sup>2</sup>C bus microprocessor interface

- All digital clock and carrier recovery

- On-chip PLL clock generation using low cost 10 to 15 MHz crystal

- 3.3V operation

- 80 pin MQFP package

- · Low external component count

- Commercial temperature range 0 to 70°C

#### **Demodulator**

· BPSK or QPSK programmable

#### Viterbi

- Programmable decoder rates 1/2, 2/3, 3/4, 5/6, 6/7, 7/8

- Constraint length k=7

- Trace back depth 128

- Extensive SNR and BER monitors

Figure 1 - VP310 Functional Block Diagram

# **Additional Features (continued)**

#### **De-Interleaver**

Compliant with DVB and DSS standards

#### **Reed Solomon**

- (204, 188) for DVB and (146,130) for DSS

- Reed Solomon Bit-error-rate monitor to indicate Viterbi performance

#### **De-Scrambler**

· EBU specification De-scrambler for DVB mode

## **Outputs**

- MPEG transport parallel & serial output

- Integrated MPEG2 TEI bit processing for DVB only

# **Application Support**

- · Channel decoder system evaluation board

- I<sup>2</sup>C interface board to PC

- · Windows based evaluation software

- ANSI C generic software

- Application support help desk via email/ telephone

2

# For more information about all Zarlink products visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in an  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2002, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE