TOSHIBA S6744

#### TOSHIBA THYRISTOR SILICON PLANAR TYPE

# **S6744**

#### MEDIUM POWER CONTROL APPLICATIONS

Repetitive Peak Off-State Voltage :  $V_{DRM}$  > 400V Repetitive Peak Reverse Voltage

Average On-State Current  $: I_{T(AV)} = 8A$

A Large Current Pulse Capability

#### **MAXIMUM RATINGS**

| CHARACTERISTIC                                                                       | SYMBOL                               | RATING     | UNIT   |  |

|--------------------------------------------------------------------------------------|--------------------------------------|------------|--------|--|

| Repetitive Peak Off-State Voltage<br>and Repetitive Peak Reverse<br>Voltage          | V <sub>DRM</sub><br>V <sub>RRM</sub> | 400        | V      |  |

| Non-Repetitive Peak Reverse Voltage (Non-Repetitive $< 5$ ms, $T_j = 0 \sim 125$ °C) | $V_{ m RSM}$                         | 500        | V      |  |

| Average On-State Current (Half Sine Waveform Tc=72°C)                                | I <sub>T (AV)</sub>                  | 8          | A      |  |

| R.M.S On-State Current                                                               | I <sub>T</sub> (RMS)                 | 12.6       | A      |  |

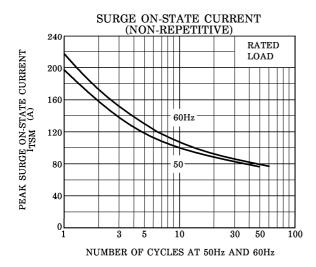

| Peak One Cycle Surge On-State                                                        | Imana                                | 200 (50Hz) | A      |  |

| Current (Non-Repetitive)                                                             | ITSM                                 | 220 (60Hz) |        |  |

| I <sup>2</sup> t Limit Value                                                         | ${ m I}^2{ m t}$                     | 200        | $A^2s$ |  |

| Repetitive Peak Surge On-State<br>Current (Note 1)                                   | $I_{TRM}$                            | 1300       | A      |  |

| Critical Rate of Rise of On-State Current (Note 2)                                   | di/dt                                | 100        | A/μs   |  |

| Peak Gate Power Dissipation                                                          | $P_{GM}$                             | 5          | W      |  |

| Average Gate Power Dissipation                                                       | P <sub>G</sub> (AV)                  | 0.5        | W      |  |

| Peak Forward Gate Voltage                                                            | $v_{FGM}$                            | 10         | V      |  |

| Peak Reverse Gate Voltage                                                            | $v_{RGM}$                            | <b>-</b> 5 | V      |  |

| Peak Forward Gate Current                                                            | $I_{GM}$                             | 2          | A      |  |

| Junction Temperature                                                                 | $\mathrm{T_{j}}$                     | -40~125    | °C     |  |

| Storage Temperature Range                                                            | $\mathrm{T}_{\mathrm{stg}}$          | -40~150    | °C     |  |

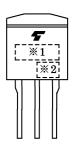

Unit in mm 10.3MAX 10.6MAX 1.6MA 2.54 ± 0.25 **CATHODE** 1. **ANODE** GATE **JEDEC EIAJ TOSHIBA** 13-10J1B

Weight: 1.7g

Note 1 :  $C_M \le 500 \mu F$ ,  $t_w \le 300 \mu s$ ,  $V_D \le 350 V$ Note 2 : di/dt Test condition

$V_{DRM} = 0.5 \times Rated, I_{TM} \le 25A, t_{gw} \ge 10 \mu s, t_{gr} \le 250 ns, i_{gp} = I_{GT} \times 2.0$

961001EAA2

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

## ELECTRICAL CHARACTERISTICS (Ta = 25°C)

| CHARACTERISTIC                                                              | SYMBOL                               | TEST CONDITION                                                                                            | MIN. | TYP. | MAX. | UNIT           |

|-----------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|----------------|

| Repetitive Peak Off-State<br>Current and Repetitive<br>Peak Reverse Current | I <sub>DRM</sub><br>I <sub>RRM</sub> | $ m V_{DRM} =  m V_{RRM} =  m Rated$                                                                      | _    | _    | 10   | $\mu$ <b>A</b> |

| Peak On-State Voltage                                                       | $V_{	extbf{TM}}$                     | $I_{	extbf{TM}} = 25 A$                                                                                   | _    | _    | 1.5  | V              |

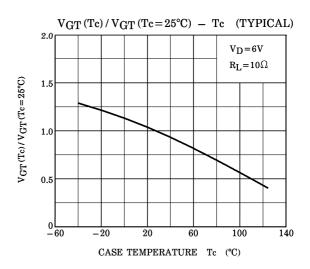

| Gate Trigger Voltage                                                        | $V_{GT}$                             | $V_D=6V, R_L=10\Omega$                                                                                    | _    | _    | 1.0  | V              |

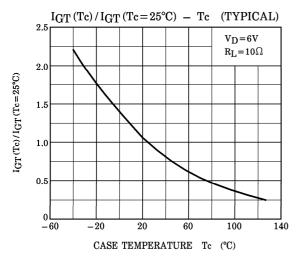

| Gate Trigger Current                                                        | $I_{GT}$                             | VD-6V, KL-1042                                                                                            | _    |      | 20   | mA             |

| Gate Non-Trigger Voltage                                                    | $v_{GD}$                             | $V_D = Rated \times 2/3$ , $T_c = 125$ °C                                                                 | 0.2  | _    | _    | V              |

| Critical Rate of Rise of Off-State Voltage                                  | dv / dt                              | V <sub>DRM</sub> =Rated, Tc=125°C,<br>Exponential Rise                                                    | _    | 50   | _    | V/μs           |

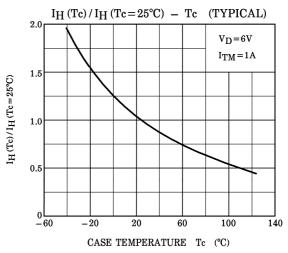

| Holding Current                                                             | $I_{\mathbf{H}}$                     | $V_D=6V$ , $I_{TM}=1A$                                                                                    | _    | _    | 40   | mA             |

| Latching Current                                                            | ${ m I_L}$                           | $V_{\rm D} = 6 { m V}, \ { m f} = 50 { m Hz}, \ { m t}_{ m gw} = 100 \mu { m s}, \ i_{ m G} = 40 { m mA}$ | _    | _    | 60   | mA             |

| Thermal Resistance                                                          | R <sub>th (j-a)</sub>                | Junction to Ambient                                                                                       | _    |      | 70   | °C/W           |

### MARKING

| *1        | TYPE<br>NAME | S6744                                                            | MARK                                              | S6744    |

|-----------|--------------|------------------------------------------------------------------|---------------------------------------------------|----------|

| <b>*2</b> |              | Starting from Alphabet A  Last Decimal Digit of the Current Year | Example<br>8A : Janua<br>8B : Febru<br>8L : Decen | ary 1998 |