### INTEGRATED CIRCUIT **TOSHIBA** TECHNICAL DATA

### TOSHIBA CCD AREA IMAGE SENSOR TC6134AF

CCD(Charge Coupled Device)

### **OUTLINE**

The CMOS LSI of TC6134AF was developed to drive the TCD5340C, TCD5280D, TCD5120AC and TCD5130AC. TC6134AF can be combined with a vertical clock driver to constitute the CCD area image sensor driving circuit.

#### **FEATURES**

- Generation of all timing pulses required to drive TCD5340C, TCD5280D, TCD5120AC and TCD5130AC.

- Correspondence with electronic shutter from 1/50, 1/60 to 1/10000 s.

(TCD5120AC, TCD5130AC: 1/50~1/2000 s)

Generation of sampling pulses for CDS signal processing.

Weight: 0.33g (Typ.)

#### MAXIMUM RATINGS $(V_{SS} = 0V)$

| CHARACTERISTIC      | SYMBOL           | RATING                    | UNIT |

|---------------------|------------------|---------------------------|------|

| Supply Voltage      | V <sub>DD</sub>  | -0.3~7.0                  | V    |

| Input Voltage       | VIN              | -0.3~V <sub>DD</sub> +0.3 | V    |

| Input Current       | IN               | ± 10                      | mA   |

| Storage Temperature | T <sub>stg</sub> | <b>-40∼125</b>            | °C   |

### **RECOMMENDED OPERATING CONDITIONS** $(V_{SS} = 0V)$

| CHARACTERISTIC        | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Supply Voltage        | $V_{DD}$         | 4.50 ~ 5.50     | V    |

| Operating Temperature | T <sub>opr</sub> | <b>-20 ∼ 70</b> | °C   |

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

(i) These TOSHIBA products are intended for use in general commercial applications (office equipment, communication equipment, measuring equipment, domestic appliances, etc.), please make sure that you consult with us before you use these TOSHIBA products in equipment which requires extraordinarily high quality and/or reliability, and in equipment which may involve life threatening or critical application, including but not limited to such uses as atomic energy control, airplane or spaceship instrumentation, traffic signals, medical instrumentation, combustion control, all types of safety devices, etc. TOSHIBA conto accept and hereby disclaims liability for any damage which may occur in case the TOSHIBA products are used in such equipment or applications without prior consultation with TOSHIBA.

# INTEGRATED CIRCUIT TOSHIBA TECHNICAL DATA

# TC6134AF

# **ELECTRICAL CHARACTERISTICS** ( $V_{SS} = 0V$ , $V_{DD} = 4.75 \sim 5.25V$ , $Ta = 0 \sim 70^{\circ}C$ )

| CHARACTERISTIC         |           | SYMBOL TEST CONDITIONS |                                                          | MIN.  | TYP. | MAX. | UNIT           |

|------------------------|-----------|------------------------|----------------------------------------------------------|-------|------|------|----------------|

| Innut Valtage          | "H" Level | V <sub>IH</sub>        |                                                          | 3.5   | _    | _    | V              |

| Input Voltage "L" Leve |           | V <sub>IL</sub>        |                                                          | _     | _    | 1.5  | "              |

|                        | "H" Level | 1                      | $V_{IN} = V_{DD}$                                        | - 10  | _    | 10   |                |

|                        |           | ЧН                     | V <sub>IN</sub> = V <sub>DD</sub> , (included PULL-DOWN) | 10    | _    | 200  | ا ۱            |

| Input Current          | "L" Level | IJĽ                    | V <sub>IN</sub> = V <sub>SS</sub>                        | - 10  | _    | 10   | $\mu$ A        |

|                        | L Level   |                        | V <sub>IN</sub> = V <sub>SS</sub> , (included PULL-UP)   | - 200 | _    | - 10 |                |

| "H" Level              |           | Vall                   | I <sub>OH</sub> = -8mA, H1A, H2A                         | 2.4   |      |      |                |

| Output Valtage         | III LEVEI | ∨он                    | I <sub>OH</sub> = –4mA except H1A, H2A                   | ] 2.4 | _    |      | ] <sub>v</sub> |

| Output Voltage         | "L" Level | V                      | I <sub>OL</sub> = 8mA, H1A, H2A                          |       |      | 0.4  |                |

|                        | L Level   | VOL                    | I <sub>OL</sub> = 4mA except H1A, H2A                    | ] _   |      | 0.4  |                |

| Static Consumptio      | n Current | l <sub>DD</sub>        | $C_L = 0pF, V_{DD} = 5V, Ta = 25°C$                      |       | _    | 200  | μΑ             |

TC6134AF – 2 1994 – 11 – 28

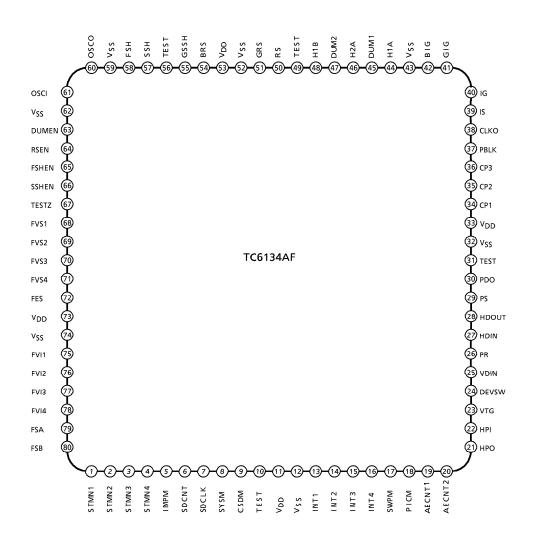

**PIN CONNECTION**

TC6134AF – 3 1994 – 11 – 28

# INTEGRATED CIRCUIT **TOSHIBA**

# TC6134AF

TECHNICAL DATA

### PIN FUNCTION

|            | NCTION   |     |          |                                                                                                                                                                                 |  |  |  |  |  |  |

|------------|----------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PIN<br>No. | SYMBOL   | 1/0 | POLARITY | FUNCTION                                                                                                                                                                        |  |  |  |  |  |  |

| 1          | STM1     | ı   |          |                                                                                                                                                                                 |  |  |  |  |  |  |

| 2          | STM2     | I   |          | Shutter period setting terminal.                                                                                                                                                |  |  |  |  |  |  |

| 3          | STM3     | I   | <b>—</b> | (See the attached table for the shutter period)                                                                                                                                 |  |  |  |  |  |  |

| 4          | STM4     | I   | 1        |                                                                                                                                                                                 |  |  |  |  |  |  |

| 5          | INPM     | I   | _        | Terminal for switching shutter speed setting mode serial input mode in H level - parallel input mode in L level                                                                 |  |  |  |  |  |  |

| 6          | SDCNT    | ı   | _        | Serial data control input connected to VD of synchronization generator IC.                                                                                                      |  |  |  |  |  |  |

| 7          | SDCLK    | ı   | _        | Serial data clock input.                                                                                                                                                        |  |  |  |  |  |  |

| 8          | SYSM     | I   | _        | Terminal for switching PAL or NTSC mode NTSC mode in L level - PAL mode in H level                                                                                              |  |  |  |  |  |  |

| 9          | CSDM     | ı   | _        | Input terminal for CDS mode.                                                                                                                                                    |  |  |  |  |  |  |

| 10         | TEST     | I   | _        | Test terminal is opened for normal use.                                                                                                                                         |  |  |  |  |  |  |

| 11         | $V_{DD}$ | _   | _        | Connected to power supply 5V ± 0.25V                                                                                                                                            |  |  |  |  |  |  |

| 12         | VSS      | _   | _        | Electronic shutter (Substrate sweep mode) is available on high resolution mode.                                                                                                 |  |  |  |  |  |  |

| 13         | INT1     | I   | _        | Resolution mode switching input.    INT1                                                                                                                                        |  |  |  |  |  |  |

|            |          |     |          |                                                                                                                                                                                 |  |  |  |  |  |  |

| 14         | INT2     | I   | _        | # Electronic shutter (Substrate sweep mode) is available on high resolution mode.  # TCD5120AC, TCD5130AC: high resolution mode is available only in normal speed.              |  |  |  |  |  |  |

| 15         | INT3     | I   | _        | Input terminal for switching electronic shutter sweep mode.  -Substrate sweep mode in L level. (TCD5120AC, TCD5130AC: this mode is not available.)  -FIT sweep mode in H level. |  |  |  |  |  |  |

| 16         | INT4     | I   | _        | Input terminal for switching storage mode2-4 storage in L level. (Recommend) -1-4 storage in H level.                                                                           |  |  |  |  |  |  |

| TC6134AF – 4        |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

# TC6134AF

| PIN<br>No. | SYMBOL   | 1/0 | POLARITY | FUNCTION                                                                                                                                                                                    |

|------------|----------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | SWPM     | I   | _        | Input terminal for switching storage mode reversible transfer in L level sequencial transfer in H level (Recommend) * Sweep mode is fixed to sequencial transfer mode on normal speed mode. |

| 18         | PICM     | I   | _        | Input terminal for switching number of horizontal pixels 400K TCD5120AC, TCD5130AC, TCD5280D in H level 600K TCD5340C in L level.                                                           |

| 19         | AECNT1   | I   | _        | Input terminal for controlling MNCSD mode, AECNT mode and                                                                                                                                   |

| 20         | AECNT2   | I   | _        | electronic shutter speed.                                                                                                                                                                   |

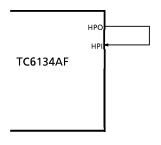

| 21         | НРО      | 0   | 几        | Horizontal transfer control pulse. This pulse is output within horizontal flyback time to indicate that horizontal CCD transfer period has stopped.                                         |

| 22         | HPI      | I   | _        | Connected to HPO for normal use.                                                                                                                                                            |

| 23         | VTG      | 0   | _        | Output terminal for standard pulse of AE mode is opened for normal use.                                                                                                                     |

| 24         | DEVSW    | ı   | _        | Input terminal for controlling 1H divider - stop working in L level work in H level.                                                                                                        |

| 25         | VDIN     | ı   | _        | Input terminal for VD of synchronization generator IC.                                                                                                                                      |

| 26         | PR       | ı   | _        | Input terminal for phase comparator.                                                                                                                                                        |

| 27         | HDIN     | I   | _        | Input terminal for HD of synchronization generator IC.                                                                                                                                      |

| 28         | HDOUT    | 0   | Л        | Horizontal drive pulse is output when 1H divider works.                                                                                                                                     |

| 29         | PS       | I   | _        | Input terminal for phase comparator.                                                                                                                                                        |

| 30         | PDO      | 0   | _        | Output terminal for phase comparator.                                                                                                                                                       |

| 31         | TEST     | I   | _        | Test terminal is opened for normal use.                                                                                                                                                     |

| 32         | VSS      | _   | _        | GND                                                                                                                                                                                         |

| 33         | $V_{DD}$ | _   | _        | Connected to power supply 5V ± 0.25V.                                                                                                                                                       |

| 34         | CP1      | 0   | Л        | Clamp pulse output for clamping the OB portion of CCD signal output.                                                                                                                        |

| 35         | CP2      | 0   | 几        | Clamp pulse output for signal processing.                                                                                                                                                   |

| 36         | CP3      | 0   | 几        | Clamp pulse output for signal processing.                                                                                                                                                   |

| 37         | PBLK     | 0   | 几        | Pre-blanking pulse output. H level indicates the erase piriod.                                                                                                                              |

| 38         | CLKO     | 0   | Ш        | Master clock output for synchronization generator IC. (fck)                                                                                                                                 |

| TC6134AF – 5        |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

| PIN<br>No. | SYMBOL   | 1/0 | POLARITY | FUNCTION                                                                                                                                             |

|------------|----------|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39         | IS       | 0   | _        | Test terminal is opened for normal use.                                                                                                              |

| 40         | IG       | 0   | _        | Test terminal is opened for normal use.                                                                                                              |

| 41         | GIG      | I   |          | Test terminal is amount for resource tree                                                                                                            |

| 42         | BIG      | 0   | 1 -      | Test terminal is opened for normal use.                                                                                                              |

| 43         | VSS      | _   | _        | GND                                                                                                                                                  |

| 44         | H1A      | 0   | Ш        | Horizontal CCD drive pulse to be connected to the H1A gate of the CCD image sensor.                                                                  |

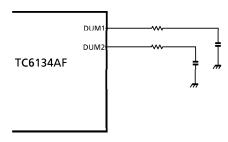

| 45         | DUM1     | 0   | _        | Dummy output 1.                                                                                                                                      |

| 46         | H2A      | 0   | Ш        | Horizontal CCD drive pulse to be connected to the H2A gate of the CCD image sensor.                                                                  |

| 47         | DUM2     | 0   | _        | Dummy output 2.                                                                                                                                      |

| 48         | H1B      | 0   |          | Horizontal CCD drive pulse to be connected to the H1B gate of the CCD image sensor.                                                                  |

| 49         | TEST     | _   | _        | Test terminal is opened for normal use.                                                                                                              |

| 50         | RS       | 0   | Л        | Reset gate pulse to be connected to the RS gate of the CCD image sensor.                                                                             |

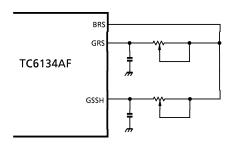

| 51         | GRS      | I   | _        | Input and output terminal for adjusting RSO and SSH phase. The BRS output is delayed with a capacitor and resistor connected to the GRS, GSSH input. |

| 52         | VSS      | _   | _        | GND                                                                                                                                                  |

| 53         | $V_{DD}$ |     | _        | Connected to power supply 5.0V ± 0.25V.                                                                                                              |

| 54         | BRS      | 0   | Ш        | Input and output terminal for adjusting RSO and SSH phase. The BRS output is delayed with a capacitor and resistor connected to                      |

| 55         | GSSH     | ł   | _        | the GRS, GSSH input.                                                                                                                                 |

| 56         | TEST     | 1   | _        | Test terminal is opened for normal use.                                                                                                              |

| 57         | SSH      | 0   | Л        | Signal sampling pulse output.                                                                                                                        |

| 58         | FSH      | 0   | Л        | Feed through sampling pulse output.                                                                                                                  |

| 59         | VSS      | _   | _        | GND                                                                                                                                                  |

| 60         | osco     | O   | Ш        | Master clock output. (2 fck)                                                                                                                         |

| 61         | OSCI     | I   | _        | Master clock input (2 fck)                                                                                                                           |

| 62         | Vss      | _   | _        | GND                                                                                                                                                  |

| 63         | DUMEN    | I   | _        | Test terminal is opened for normal use. When L level puts on this terminal, dummy output is enable.                                                  |

| 64         | RSEN     | I   | _        | Test terminal is opened for normal use. When L level puts on this terminal, RS output is enable.                                                     |

| TC6134AF – 6        |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

# INTEGRATED CIRCUIT **TOSHIBA**TECHNICAL DATA

# **TC6134AF**

| PIN<br>No. | SYMBOL   | 1/0 | POLARITY | FUNCTION                                                                                          |  |

|------------|----------|-----|----------|---------------------------------------------------------------------------------------------------|--|

| 65         | FSHEN    | I   | _        | Test terminal is opened for normal use. When L level puts on this terminal, FSH output is enable. |  |

| 66         | SSHEN    | I   | _        | Test terminal is opened for normal use. When L level puts on this terminal, SSH output is enable. |  |

| 67         | TESTZ    | I   | _        | Test terminal is opened for normal use.                                                           |  |

| 68         | FVS1     | 0   | 几        |                                                                                                   |  |

| 69         | FVS2     | O   |          | Vertical CCD drive pulse $\phi$ S1, $\phi$ S2, $\phi$ S3 and $\phi$ S4 connected to the           |  |

| 70         | FVS3     | 0   | 7        | inversion type vertical clock driver.                                                             |  |

| 71         | FVS4     | 0   | 几        |                                                                                                   |  |

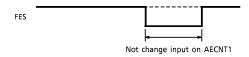

| 72         | FES      | 0   | l T      | Electronic shutter pulse connected to the inversion type drive.                                   |  |

| 73         | $v_{DD}$ | _   | _        | Connected to power supply 5V ± 0.25V.                                                             |  |

| 74         | VSS      | _   | _        | GND                                                                                               |  |

| 75         | FVI1     | 0   |          |                                                                                                   |  |

| 76         | FVI2     | O   |          | Vertical CCD drive pulse $\phi$ I1, $\phi$ I2, $\phi$ I3 and $\phi$ I4 connected to the           |  |

| 77         | FVI3     | 0   |          | inversion type vertical clock driver.                                                             |  |

| 78         | FVI4     | 0   |          |                                                                                                   |  |

| 79         | FSA      | 0   |          | Field shift drive pulse $\phi$ I1 and $\phi$ I3 connected to the inversion                        |  |

| 80         | FSB      | 0   |          | type vertical clock driver.                                                                       |  |

TC6134AF - 7 1994 - 11 - 28 TOSHIBA CORPORATION

# INTEGRATED CIRCUIT **TOSHIBA**TECHNICAL DATA

### TC6134AF

### SETTING FOR ELECTRONIC SHUTTER SPEED

| INPM                  | *3 CSDM      |                                          |          | Ele   | ctronic | shutter             |              |                             | Storage |         |       |

|-----------------------|--------------|------------------------------------------|----------|-------|---------|---------------------|--------------|-----------------------------|---------|---------|-------|

| (setting mode)        |              | STM1                                     | STM2     | STM3  | STMA    | func                | tion         | sub-                        | FIT     | *6 h    |       |

| (setting mode)        | (CSD IIIOGE) |                                          |          |       |         | NTSC                | PAL          | strate                      | shutter | resolu  |       |

|                       |              | L                                        | L        | L     | L       |                     | 1/50 (1/25)* | ×                           | ×       | ×*1     | ×*1   |

|                       |              | Н                                        | L        | L     | L       | 1 / 100             | 1 / 60       | 0                           | 0       | $\circ$ | 0     |

|                       |              | L                                        | Н        | L     | L       | 1/1                 | 120          | 0                           | 0       | 0       | 0     |

|                       |              | Н                                        | Н        | L     | L       | 1/2                 | 250          | 0                           | 0       | 0       | 0     |

|                       |              | L                                        | L        | Н     | L       | 1/5                 | 500          | 0                           | 0       | 0       | ○*2   |

|                       |              | Н                                        | L        | Н     | L       | 1/1000,1/56         | 1 / 1000     | 0                           | 0       | ○*2     | ×     |

|                       | H            |                                          | Н        | Н     | L       | 1/2                 | 000          | 0                           | ○*2     | ×       | ×     |

|                       | or<br>L      | Н                                        | Н        | Н     | L       | 1/4                 | .000         | 0                           | ×       | ×       | ×     |

|                       | L            | L                                        | L        | L     | Н       | 1/8                 | 000          | 0                           | ×       | ×       | ×     |

| L                     |              | Н                                        | L        | L     | Н       | 1 / 10              | 0000         | 0                           | ×       | ×       | ×     |

| (Parallel<br>setting) |              | L                                        | Н        | L     | Н       | test mode           |              | _                           | _       | _       | _     |

|                       |              | Н                                        | Н        | L     | Н       | test r              | test mode    |                             | _       | _       | _     |

|                       |              | L                                        | L        | Н     | Н       | 1/                  | 51           | 0                           | 0       | 0       | 0     |

|                       |              | Н                                        | L        | Н     | Н       | 1/                  | 61           | 0                           | 0       | 0       | 0     |

|                       |              |                                          |          |       |         | *4 MNCSD r          | node. The    |                             |         |         |       |

|                       |              |                                          |          |       |         | data about          | change       | 0                           |         | ×       | ×     |

|                       | Н            | L                                        | н        | Н     | Н       | vector on A         | AECNT1 and   |                             |         |         |       |

|                       | П            | _                                        | "        | "     | "       | AECNT2 increases or |              | prohibitted from setting on |         |         | ng on |

|                       |              |                                          |          |       |         | decreases sl        |              | frame storage mode.         |         |         |       |

|                       |              |                                          |          |       |         | speed grad          | -            |                             |         |         |       |

|                       |              |                                          |          |       |         | *5 AECNT n          |              |                             |         |         |       |

|                       | L            | Н                                        | Н        | Н     | Н       |                     | se on AECN   | Γ1 and                      | AECNT2  | contro  | ls    |

|                       | _            |                                          |          |       |         | shutter speed.      |              |                             |         |         |       |

|                       |              |                                          |          |       |         |                     |              |                             |         |         |       |

| н                     | Н            | Serial binary data on SDCLK and STM4 can |          |       |         |                     |              |                             |         |         |       |

| <b>*</b> 7            | or           |                                          |          |       | oeed ir | 1 1H                |              | 0                           | 0       | $\circ$ | 0     |

| (serial setting)      | L            | (parti                                   | ially in | 1.5H) | •       |                     |              |                             |         |         |       |

| 🔯 🛮 shutter speed on frame storage mod | ☆ | shutter | speed | on | frame | storage | mod |

|----------------------------------------|---|---------|-------|----|-------|---------|-----|

|----------------------------------------|---|---------|-------|----|-------|---------|-----|

availabledisable

| TC6134AF – 8        |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

<sup>\*1</sup> When normal mode is set on high resolution mode, there is different storage time in between 1 st and 2 nd field.

<sup>\*2</sup> When this mode is set, blooming margin of CCD area image sensor decrease.

# INTEGRATED CIRCUIT TOSHIBA TECHNICAL DATA

### TC6134AF

### \*3 CSD mode

CSDM:L When a shutter speed is on normal mode, the shutter speed is changed on

the next field.

CSDM:H (CSD mode) When a shutter speed is set, the shutter speed is changed gradually. The

change slope shows as follows;

| Storage time     | Change slope                   |

|------------------|--------------------------------|

| 1.5H~8H          | 1H/4 per field                 |

| ~262.5 (312.5) H | 3 percents of the storage time |

#### \*4 MNCSD mode

On MNCSO mode (CSDM:H) linputs on AECNT1 and AECNT2 increase or decrease the shutter speed. This mode is prohibitted on the frame storage mode.

| CSDM | AECNT1 | AECNT2 | Function                  |  |  |  |  |  |  |

|------|--------|--------|---------------------------|--|--|--|--|--|--|

|      | L      | L      | Lengthen the storage time |  |  |  |  |  |  |

| l H  | u H L  |        | Not change                |  |  |  |  |  |  |

| "    | L      | Н      | Not change                |  |  |  |  |  |  |

| İ    | Н      | Н      | Shorten the storage time  |  |  |  |  |  |  |

In this mode the highest shutter speed is limitted as follows:

| INT1 | INT2 | INT3 | Mode                           | Highest shutter speed |

|------|------|------|--------------------------------|-----------------------|

| L    | L    | L    | Substrate sweep, field storage | ~1/4000               |

| L    | L    | Н    | FIT sweep, frame storage       | ~1 / 1000             |

| Н    | L    | _    | High resolution mode 50%       | Prohibition           |

| L    | Н    | _    | High resolution mode 25%       | Prohibition           |

| Н    | Н    | L    | Substrate sweep, frame storage | Prohibition           |

| Н    | Н    | Н    | FIT sweep, frame storage       | Prohibition           |

TC6134AF - 9 1994 - 11 - 28 TOSHIBA CORPORATION

Electronic shutter iris is realized in this mode.

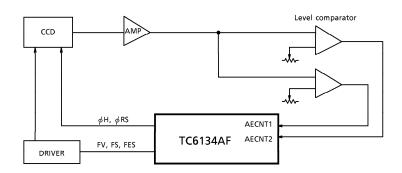

### \*5 AECNT mode

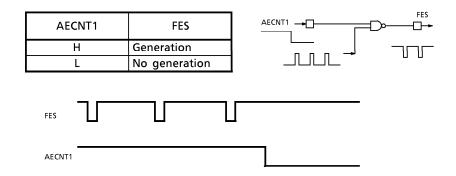

In this mode timing pulse on AECNT1 and AECNT2 can control the shutter speed.

Input on AECNT1 controls FES pulse. The available range of setting the substrate shutter is until  $1/10000 \, s$ .

AECNT is not allowed to change while FES pulse is L level. Because AECNT1 gates FES pulse.

| TC6134AF – 10       |

|---------------------|

| 1994 – 11 – 28      |

|                     |

| TOSHIBA CORPORATION |

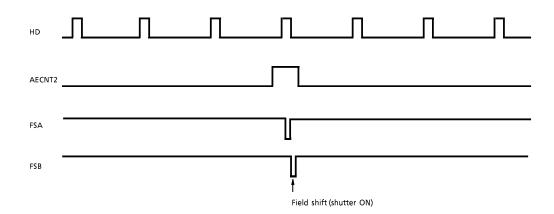

Input on AECNT2 controls FSA and FSB pulses. (FIT shutter).

| AECNT2 | FSA, FSB, FI1~4 |

|--------|-----------------|

| Н      | Field shift     |

| L      | Line shift      |

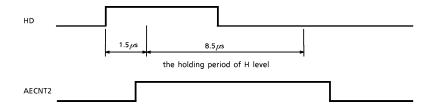

The period of H level on AECNT2 should be longer than the holding period of H level as follows.

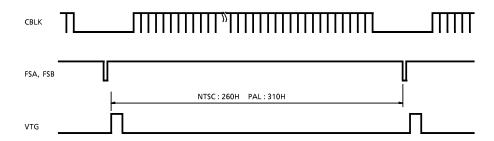

On AECNT mode, generation of trigger pulse needs external counter circuits. And VTG pulse is used for the standard pulse resetting the external counter circuits. The time difference of VTG and field shift (shutter OFF) in the next field are set as follows;

260H (NTSC) 310H (PAL)

### \*6 High resolution mode

On high resolution mode, substrate and FIT shutter adds and reads out signal of two vertical pixels each field as pixels having different storaged signal. This mode realized high resolution.

### For example:

When the shutter speed is set  $1/100\,\mathrm{s}$  on high resolution (50%) mode,  $1/100\,\mathrm{s}$  storaged signal and  $1/200\,\mathrm{s}$  ( $1/100\,\mathrm{s}\times50\%$ ) storaged signal are added and read out. But substrate shutter is not available for TCD5120AC and TCD5130AC, so 1 field storaged ( $1/60\,\mathrm{s}$  or  $1/50\,\mathrm{s}$ ) signal and  $1/200\,\mathrm{s}$  storaged signal are added and read out.

TC6134AF – 12 1994 – 11 – 28

# INTEGRATED CIRCUIT **TOSHIBA**

TC6134AF

TECHNICAL DATA

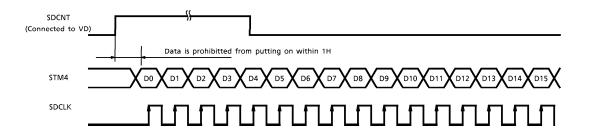

### \*7 • Serial setting mode

INPM : H level STM4 : Serial data

SDCLK: Clock for serial data

SDCNT: Serial data control connected to VD of synchronization generator IC.

SDCNT is connected to VD of synchronization generator IC.

Data is prohibitted from putting on within 1H after VD pulse raises. The data set on STM4 is fed into shutter speed controller when SDCLK pulse raises. The data is organized 16 bits.

| D0    | D1                                                                       | D2     | D3         | D4 | D5         | D6        | D7         | D8        | D9         | D10    | D11 D12 D13 D14 D1 |  |  |  | D15 |

|-------|--------------------------------------------------------------------------|--------|------------|----|------------|-----------|------------|-----------|------------|--------|--------------------|--|--|--|-----|

| 0     | SS0                                                                      | S0     | <b>S</b> 1 | S2 | <b>S</b> 3 | <b>S4</b> | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 | S8     | ×                  |  |  |  |     |

| Put   | 9bits binary data put on S0 – 8 can set the shutter speed in 1H. And the |        |            |    |            |           |            |           | the        | Not co | ncerned            |  |  |  |     |

| "0"   | data on SSO can set the shutter speed in 0.5H below 10H on NTSC mode     |        |            |    |            |           |            |           | ode        |        |                    |  |  |  |     |

| on D0 | or 14H                                                                   | on PAL | mode.      |    |            |           |            |           |            |        |                    |  |  |  |     |

TC6134AF has shift resistor (clock: SDCLK). When data above 16 bits puts on, last 16 bits is available.

Input on SDCNT always connect to VD.

Allowance range of input shows as follows.

|        | Storage mode |                |                 |          |  |  |  |  |

|--------|--------------|----------------|-----------------|----------|--|--|--|--|

| System | Substrate    | FIT shutter    | High resolution |          |  |  |  |  |

|        | shutter      | i Fii siiuttei | 50%             | 25%      |  |  |  |  |

| NTSC   | 1H~256H      | 11H~256H       | 22H~256H        | 44H~256H |  |  |  |  |

| PAL    | 1H~306H      | 11H~306H       | 22H~306H        | 44H~306H |  |  |  |  |

| TC6134AF – 13       |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

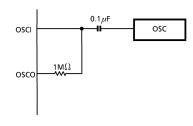

### **INPUT OF MASTER CLOCK**

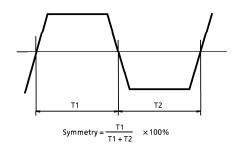

• It is necessary the symmetry of master clock put on OSCI is within  $50 \pm 10\%$ .

### Clock frequency

| CCD type No. | TV system | Nominal pixel<br>number | Clock frequency      |

|--------------|-----------|-------------------------|----------------------|

| TCD5120AC    | NTSC      | 400k                    | 1820fH = 28.63636MHz |

| TCD5130AC    | PAL       | 470k                    | 1816fH = 28.37500MHz |

| TCD5340C     | NTSC      | 600k                    | 2730fH = 42.95454MHz |

| TCD5280D     | NTSC      | 400k                    | 1820fH = 28.63636MHz |

### LOW SPEED SHUTTER MODE

| TESTZ | SYSM        | INPM        | CSD | INT1 | INT2 | INT3 | STM1 | STM2 | STM3 | STM4 | Storage time       |

|-------|-------------|-------------|-----|------|------|------|------|------|------|------|--------------------|

| Н     | L<br>(NTSC) | L           | L   | Н    | Н    | н    | н    | L    | Н    | L    | 1 / 56 s<br>(279H) |

|       | Н           | ,           |     | Н    | Н    | V    |      |      | 11   | 11   | 1 / 56 s           |

| Н     | (PAL)       | AL)   L   L | L   | L    | L    | L X  | L    | L    | Н    | Н    | (277H)             |

In the case of NTSC mode, this mode is available only in the frame storage and FIT sweep mode.

| TC6134AF – 14       |

|---------------------|

| 1994 – 11 – 28      |

| TOSHIBA CORPORATION |

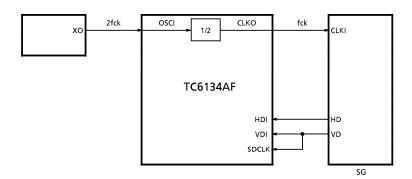

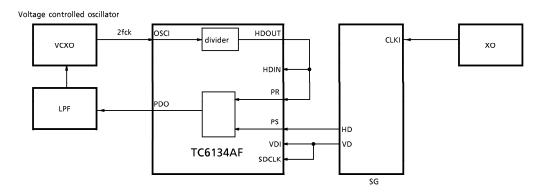

#### CONNECTION TO SYNCHRONIZATION GENERATOR IC

Connection to synchronization generator IC (master clock is fck)

Connection to synchronization generator IC (master clock is except fck)

If master clock of SG is except fck, it is necessary to lock the phase of an oscillator of SG and TC6134AF.

Therefore TC6134AF has a divider dividing 2 fck into 1H and an internal phase comparator.

TC6134AF - 15 1994 - 11 - 28 TOSHIBA CORPORATION

### **ADJUSTING PHASE OF THE PULSE**

SSH, RS

### **DEALING WITH DUM1 AND DUM2**

### CONNECTING HPO AND HPI

TC6134AF – 16 1994 – 11 – 28

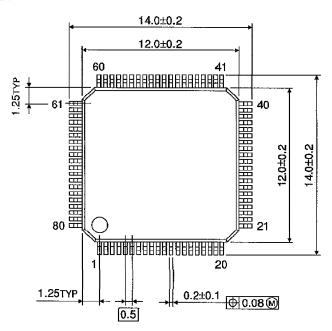

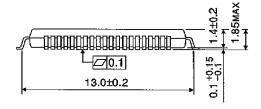

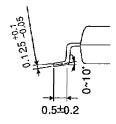

OUTLINE DRAWING QFP80-P-1212A

Unit: mm

Weight: 0.33g (Typ.)

| 1C6134AF – 1/*    |    |

|-------------------|----|

| 1994 – 11 – 28    |    |

| TOSHIBA CORPORATI | 01 |