TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T6L09

## SOURCE DRIVER FOR TFT LCD PANELS

The T6L09 is a 240-channel-output source driver for TFT LCD panels. Its sampling select pin allows switching of the VIDEO input signals (R, G, B) to the desired output pins. Furthermore, two or more of these devices can be used in combination enabling designers to keep pace with increasing LCD panel sizes.

The T6L09 offers both low power consumption and high integration circuit due to CMOS technology.

#### **FEATURES**

LCD drive output pins : 240 pins

(80 pins each for R, G and B)

LCD drive voltage : Max 15 V

Data transfer method : Bidirectional shift register

Operating temperature : -20 to 75°C

Package : Tape carrier package (TCP)

TFT LCD gate driver : T6L08

Unit: mm USER AREA T6L09 PITCH (SGN, 7ES) 1.0 0.09

Please contact Toshiba or a distributor for the latest TCP specification and product line-up.

TCP (Tape Carrier Package)

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

Polyimide base film is hard and thin. Be careful not to injure yourself on the film or to scratch any other parts with the film. Try to design and manufacture products so that there is no chance of users touching the film after assembly, or if they do , that there is no chance of them injuring themselves. When cutting out the film, try to ensure that the film shavings do not cause accidents. After use, treat the leftover film and reel spacers as industrial waste.

Light striking a semiconductor device generates electromotive force due to photoelectric effects. In some cases this can

cause the device to malfunction. This is especially true for devices in which the surface (back), or side of the chip is exposed. When designing circuits, make sure that devices are protected against incident light from external sources. Exposure to light both during regular operation and during inspection must be taken into account.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

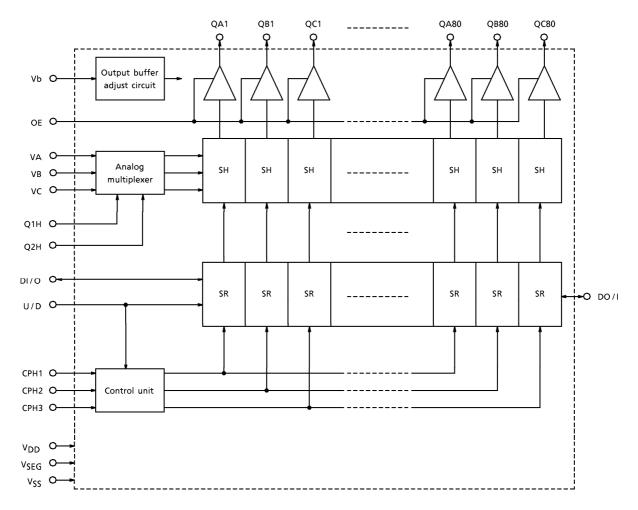

## **BLOCK DIAGRAM**

SR : Shift Register

SH : Sample-and-Hold Circuit

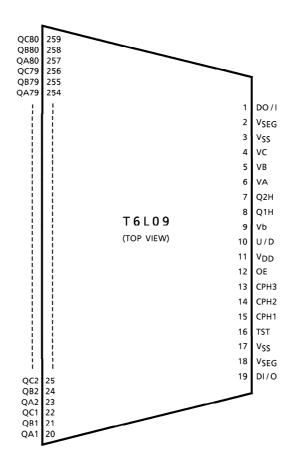

#### **PIN ASSIGNMENT**

The above diagram shows the device's pin configuration only and does not necessarily correspond to the pad layout on the chip. Please contact Toshiba or our distributors for the latest TCP specification.

# PIN FUNCTION

| PIN NAME       | 1/0   |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                      | FUNCTIO         | N               |                                                                     |  |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------------------------------------------------------|--|

|                |       | Vertical shift data I/O pins  These pins are used to input and output shift data. These pins are switched for input or output by setting the U/D pin as shown below.                                               |                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                                                                     |  |

|                |       |                                                                                                                                                                                                                    | U/D                                                                                                                                                                                                                                                                                                                                                                                  | DI/O            | DO/I            |                                                                     |  |

| DI/O           |       |                                                                                                                                                                                                                    | H<br>L                                                                                                                                                                                                                                                                                                                                                                               | INPUT<br>OUTPUT | OUTPUT<br>INPUT |                                                                     |  |

| DO / I         | 1/0   | LCD driver. The o<br>CPH1.<br>When set for outpu                                                                                                                                                                   | ata is latc<br>t<br>re T6L09s                                                                                                                                                                                                                                                                                                                                                        | hed into the s  | hift registers  | the first stage of the at the rising edge of uts the data to be fed |  |

| U/D            | Input | Transfer direction se This pin specifies hold circuit. When U/D is QA1→QB1→ When U/D is QC80→QB80→                                                                                                                 | When U/D is high, data is sampled in the sequence $QA1 \rightarrow QB1 \rightarrow QC1 \rightarrow QA2 \rightarrow QB2 \rightarrow \cdots \rightarrow QC80$ When U/D is low, the sequence is reversed to give $QC80 \rightarrow QB80 \rightarrow QA80 \rightarrow QC79 \rightarrow \cdots \rightarrow QA1$ The voltage applied to this pin must be a DC-level voltage that is either |                 |                 |                                                                     |  |

| CPH1 to 3      | Input | Shift clock input<br>These clocks sequ                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                                                                     |  |

| OE             | Input | Output enable input<br>This signal enable<br>The LCD drive ou                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                                                                     |  |

| Q1H/Q2H        | Input | Analog signal select<br>These signals swit<br>output pins: QA,                                                                                                                                                     | ch the inp                                                                                                                                                                                                                                                                                                                                                                           |                 | /B and VC to    | the corresponding                                                   |  |

| Vb             | Input | Dutput buffer adjustment input  This signal allows the capacity of the LCD drive output buffer to be varied depending on the voltage applied to it. The lower the applied voltage, the greater the drive capacity. |                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                                                                     |  |

| VA<br>VB<br>VC | Input | Analog signal input<br>These pins accept<br>LCD drive output                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                      | nput the anal   | og signals tha  | t are output to the                                                 |  |

| PIN NAME         | 1/0    | FUNCTION                                                                  |

|------------------|--------|---------------------------------------------------------------------------|

| QA1 to 80        |        | LCD drive output                                                          |

| QB1 to 80        | Output | These pins output one of the analog signal inputs (VA, VB or VC) after it |

| QC1 to 80        |        | has been sampled and held by the sample-and-hold circuit.                 |

| V <sub>SEG</sub> |        | Power supply for the device's high-voltage block                          |

| $V_{DD}$         |        | Power supply for the device's logic block                                 |

| V <sub>SS</sub>  |        | Common GND for the device                                                 |

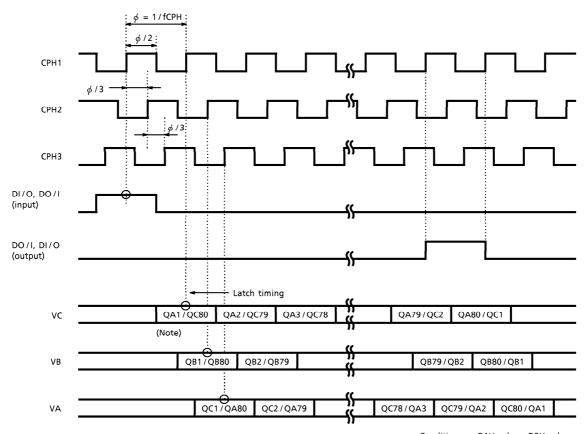

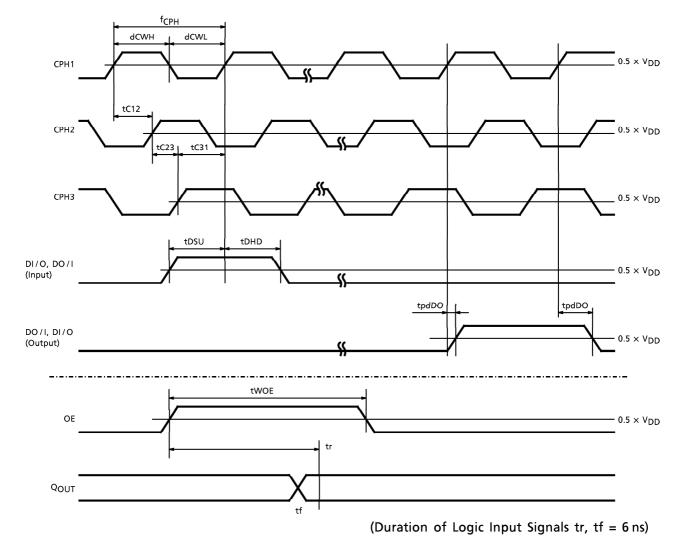

#### **DEVICE OPERATION** (see timing diagram)

#### (1) Analog signal sampling

Data transfer begins with the assertion of DI/O (when U/D = high) or DO/I (when U/D = low). The table below shows the relation between the shift clocks and the analog signals.

| U/D | CPH1      | CPH2      | СРН3      |

|-----|-----------|-----------|-----------|

| Н   | QA1 to 80 | QB1 to 80 | QC1 to 80 |

| L   | QC80 to 1 | QB80 to 1 | QA80 to 1 |

#### <When U/D = high>

- A high on DI/O is latched into the internal logic synchronously with the rising edge of CPH1, and the analog signal to be output to QA1 is sampled at the next rising edge of CPH1. In this way, all analog signals are sampled sequentially at each rising edge of CPH2, CPH3, CPH1, CPH2, CPH3 and so on, as the analog signals are output to QB1, QC1, QA2, QB2, QC2 and so on.

- After the device finishes sampling the data for QC80, it automatically enters standby state. Unless DI/O is asserted again, no data is sampled, irrespective of whether CPH1 to CPH3 are input to the device.

#### <When U/D = low>

- A high on DO/I is latched into the internal logic synchronously with the rising edge of CPH1, and the analog signal to be output to QC80 is sampled at the next rising edge of CPH1. In this way, all analog signals are sampled sequentially at each rising edge of CPH2, CPH3, CPH1, CPH2, CPH3 and so on and the analog signals are output to QB80, QA80, QC79, QB79, QA79 and so on.

- After the device finishes sampling the data for QA1, it automatically enters standby state. Unless DO/I is asserted again, no data is sampled, irrespective of whether CPH1 to CPH3 are input to the device.

Analog signal inputs VA, VB and VC are fed into the sample-and-hold circuits before they are forwarded to the LCD drive outputs: QA1-80, QB1-80 and QC1-80. Which analog input is sampled and held by which LCD drive output is determined by the Q1H/Q2H select signal as shown below.

| ANALOG SIGNAL | INPUT SELECT PIN | ANALOG SIGNAL | LCD DRIVE OUTPUT |           |  |  |

|---------------|------------------|---------------|------------------|-----------|--|--|

| Q1H           | Q2H              | INPUT         | U/D = high       | U/D = low |  |  |

|               |                  | VA            | QC1 to 80        | QA1 to 80 |  |  |

| 0             | 0                | VB            | QB1 to 80        | QB1 to 80 |  |  |

|               |                  | VC            | QA1 to 80        | QC1 to 80 |  |  |

|               |                  | VA            | QA1 to 80        | QB1 to 80 |  |  |

| 0             | 1                | VB            | QC1 to 80        | QC1 to 80 |  |  |

|               |                  | VC            | QB1 to 80        | QA1 to 80 |  |  |

|               |                  | VA            | QB1 to 80        | QC1 to 80 |  |  |

| 1             | 0/1              | VB            | QA1 to 80        | QA1 to 80 |  |  |

|               |                  | VC            | QC1 to 80        | QB1 to 80 |  |  |

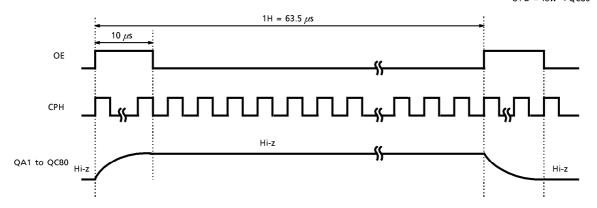

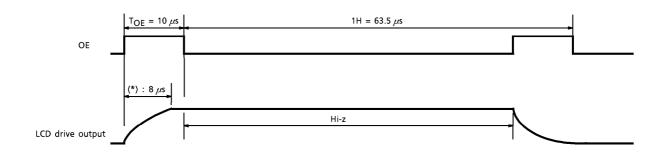

#### (2) LCD drive output

When OE is driven high, the sampled-and-held data is fed to the LCD drive output pins (QA1 through QC80).

The LCD drive output is enabled when OE is high; it is put in the Hi-Z state when OE is low.

OE should be kept low while the device is sampling data.

The drive capabilities of the LCD drive output pins are controlled by the output buffer adjustment input (Vb). The drive capability is at a minimum when  $Vb = V_{SEG}$  and decrease as the Vb voltage is raised, hence the drive capability can be set to the desired level.

#### (3) Vertical shift data output

The output DO/I (when U/D = high) or DI/O (when U/D = low) is driven high for one clock period synchronously with the rising edge of CPH1 one clock period before the data to be output to QA80 or QC1 is latched into the shift register (see timing diagram).

#### (4) Expanding LCD drive output

When using two or more of these devices to drive a large screen, connect the vertical shift data output from the first stage of the LCD driver directly to the vertical shift data input at the next stage. In this way, the device's LCD drive output pin can easily be expanded as necessary.

## **TIMING DIAGRAM**

Conditions Q1H = low, Q2H = low (Note) : QA1/QC80 : U/D = high  $\rightarrow$  QA1 U/D = low  $\rightarrow$  QC80

# ABSOLUTE MAXIMUM RATINGS $(V_{SS} = 0 V)$

| PARAMETER            | SYMBOL           | RATING                         | UNIT | RELEVANT<br>PIN |

|----------------------|------------------|--------------------------------|------|-----------------|

| Supply Voltage (1)   | V <sub>SEG</sub> | -0.3 to 18                     | V    |                 |

| Supply Voltage (2)   | V <sub>DD</sub>  | -0.3 to 7.0                    | V    |                 |

| Input Voltage        | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3  | V    | (Note 1)        |

| Storage Temperature  | T <sub>stg</sub> | – 55 to 125                    | °C   |                 |

| Analog Input Voltage | VVIDEO           | -0.3 to V <sub>SEG</sub> + 0.3 | V    | (Note 2)        |

# RECOMMENDED OPERATING CONDITIONS ( $V_{SS} = 0 V$ )

| PARAMETER               | SYMBOL          | RATING                        | UNIT | RELEVANT<br>PIN |

|-------------------------|-----------------|-------------------------------|------|-----------------|

| Supply Voltage (1)      | $V_{SEG}$       | V <sub>DD</sub> to 15         | V    |                 |

| Supply Voltage (2)      | $V_{DD}$        | 4.5 to 5.5                    | V    |                 |

| Operating Temperature   | T <sub>OP</sub> | -20 to 75                     | °C   |                 |

| Operating Frequency     | fCPH            | 0.5 to 6.0                    | MHz  |                 |

| Output Load Capacitance | $C_L$           | 0 to 200                      | pF   |                 |

| Analog Input Voltage    | VVIDEO          | 1.0 to V <sub>SEG</sub> - 2.0 | V    | (Note 2)        |

(Note 1) : All input pins except the analog signal input pins (VA, VB, VC and Vb) (Note 2) : Analog signal input pins (VA, VB, VC and Vb)

## **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS (Referenced to  $V_{DD}=4.5$  to  $5.5\,V$ ,  $V_{SEG}=13\,V$ ,  $V_{SS}=0\,V$ ,  $T_{a}=-20$  to  $75^{\circ}C$  unless otherwise noted

| PARAMETER                 |                       | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITIONS          | MIN                      | TYP. | MAX                      | UNIT | RELEVANT<br>PIN |

|---------------------------|-----------------------|--------------------|----------------------|--------------------------|--------------------------|------|--------------------------|------|-----------------|

| Input                     | Low Level             | V <sub>IL</sub>    | _                    |                          | 0                        |      | 0.2 ×<br>V <sub>DD</sub> | v    | Logic input     |

| Voltage                   | High Level            | VIH                |                      |                          | 0.8 ×<br>V <sub>DD</sub> |      | V <sub>DD</sub>          | V    | Logic input     |

| Output                    | Low Level             | V <sub>OL</sub>    | ı                    | I <sub>OL</sub> = 40 μA  | V <sub>SS</sub>          |      | V <sub>SS</sub><br>+ 0.3 | - v  | DI/O, DO/I      |

| Voltage                   | High Level            | Vон                |                      | l <sub>OH</sub> = -40 μA | V <sub>DD</sub><br>- 0.3 |      | V <sub>DD</sub>          |      |                 |

| Output Offs               | Output Offset Voltage |                    | _                    |                          | - 50.0                   |      | 50.0                     | mV   | QA1 to QC80     |

| Output Curr               | ent                   | lOL                |                      | (Note 3)                 |                          | 0.2  |                          | mA   | QA1 to QC80     |

| Output Leakage<br>Current |                       | ID <sub>LEAK</sub> |                      | OE = Low                 | - 1.0                    |      | 1.0                      | μΑ   |                 |

| Input Current             |                       | IN                 | l                    |                          | - 1.0                    |      | 1.0                      | μΑ   | Logic input     |

| Current Consumption (1)   |                       | lDD                |                      | (Note 4)                 |                          |      |                          | mA   |                 |

| Current Con<br>(2)        | sumption              | ISEG               |                      | (Note 4)                 |                          |      |                          | mA   |                 |

(Note 3) : Vb = 11 V, V<sub>VIDEO</sub> = 11 V (Note 4) :  $f_{CPH}$  = 3 MHz, 1H = 63.5  $\mu$ s, TOE = 10  $\mu$ s, V<sub>VIDEO</sub> = amplitude of 1 to 11 V, load capacitance = 100 pF (all output pins)

(\*) : This interval can be varied by adjusting Vb.

AC CHARACTERISTICS (Referenced to  $V_{DD}$  = 4.5 to 5.5 V,  $V_{SEG}$  = 13 V,  $V_{SS}$  = 0 V, Ta = -20 to 75°C unless otherwise noted

| PARAMETER                    | SYMBOL                    | TEST CONDITIONS | MIN | MAX    | UNIT    |

|------------------------------|---------------------------|-----------------|-----|--------|---------|

| Operating Frequency          | f <sub>CPH</sub> (1/tCPH) |                 | 0.5 | 6      | MHz     |

| Clock to Clock Delay<br>Time | tC12, tC23, tC31          |                 | 40  | tCPH/2 | ns      |

| CPH Pulse Duty Cycle         | dCWH/dCWL                 |                 | 40  | 60     | %       |

| Data Set-up Time             | tDSU                      |                 | 20  |        | ns      |

| Data Hold Time               | tDHD                      |                 | 60  |        | ns      |

| Output Delay Time            | tpdDO                     | CL = 30 pF      |     | 60     | ns      |

| OE Pulse Width               | tWOE                      |                 | 5   | 20     | $\mu$ s |

(Note): The Qout rise and fall times (tr, tf) can be varied by changing Vb.

(\*): Use OE with a period at 63.5 ns intervals.