DS07-13509-2E

## 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16F MB90F243H

# MB90F243H

### **■ DESCRIPTION**

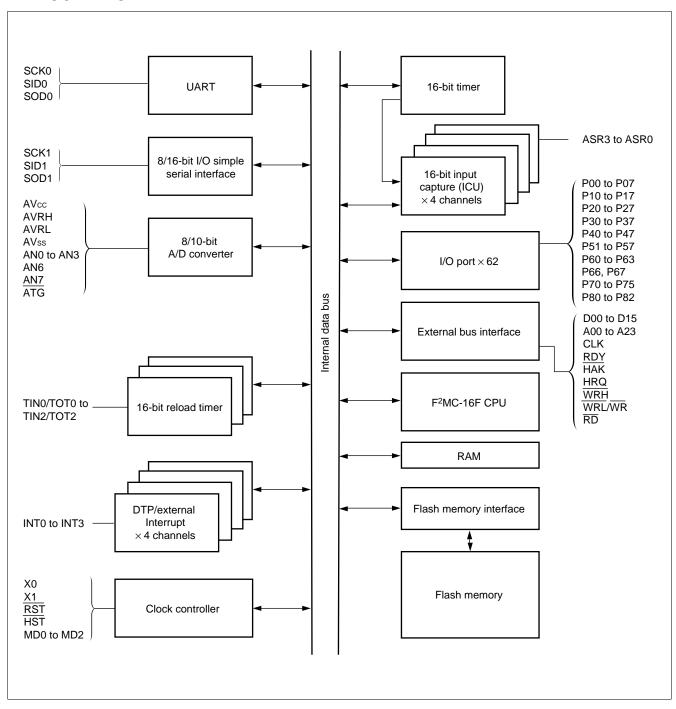

The MB90F243H is a 16-bit microcontroller optimized for applications in mechatronics such as HDD units. The architecture of the MB90F243 is based on the MB90242A, and embedded with a 128-Kbyte flash memory.

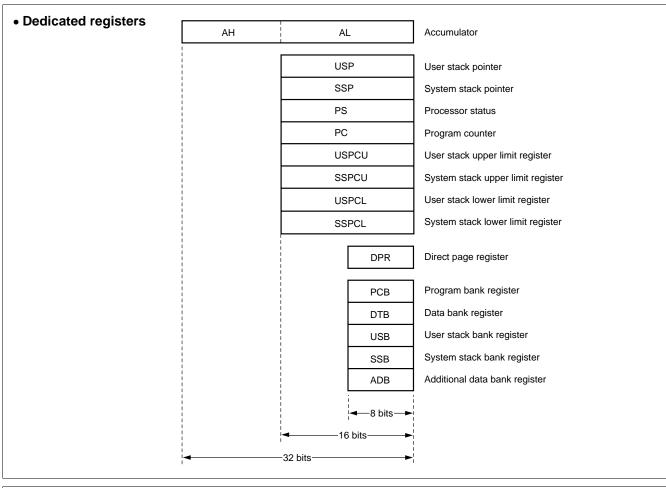

The instruction set is based on the AT architecture of the F<sup>2</sup>MC-16 and 16H family, with additional high-level language supporting instruction, expanded addressing modes, enhanced multiplication and division instructions, and improved bit processing instructions. In addition, long-word data can now be processed due to the inclusion of a 32-bit accumulator.

The MB90F243H includes a variety of peripherals on chip, such as the device is equipped with 6-channel 8/10-bit A/D converter, UART, 3-channel 16-bit reload timers, 1-channel 16-bit timer, 4-channel 16-bit input capture and 4-channel DTP/external interrupts.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

- Minimum execution time: 50.0 ns at 40 MHz oscillation

- Instruction set optimized for controller applications

Variety of data types: bit, byte, word, long-word

Expanded addressing modes: 25 types

High coding efficiency

Improvement of high-precision arithmetic operations through use of 32-bit accumulator Enhanced multiplication and division instructions (signed arithmetic operations)

(Continued)

### PACKAGE

#### (Continued)

• Instruction set supports high-level language (C language) and multitasking

Inclusion of system stack pointer

Variety of pointers

High instruction set symmetry

Barrel shift instruction

Stack clock function

- Improved execution speed: 8-byte queue

- · Powerful interrupt functions

Interrupt processing time: 0.8 µs at 40 MHz oscillation

Priority levels: 8 levels (programmable) External interrupt inputs: 4 channels

Automatic transfer function independent of CPU

Extended intelligent I/O Service: max.15 channels

128-Kbyte flash memory

Access time (min.): 120 ns

Sector structure of  $16K + 512 \times 2 + 7K + 8K + 32K + 64K$

Program/erase operations from both programmers and CPUs through built-in flash memory interface circuit Built-in program booster

Internal RAM: 1 Kbyte

According to mode settings, data stored on RAM can be executed as CPU instructions.

• General-purpose ports: max. 62 channels (single-chip mode)

max. 38 channels (external bus mode)

- 18-bit timebase timer

- Watchdog timer

- UART: 8 bits × 1 channel

- 8/16-bit I/O simple serial interface (max. 10 Mbps): 1 channel

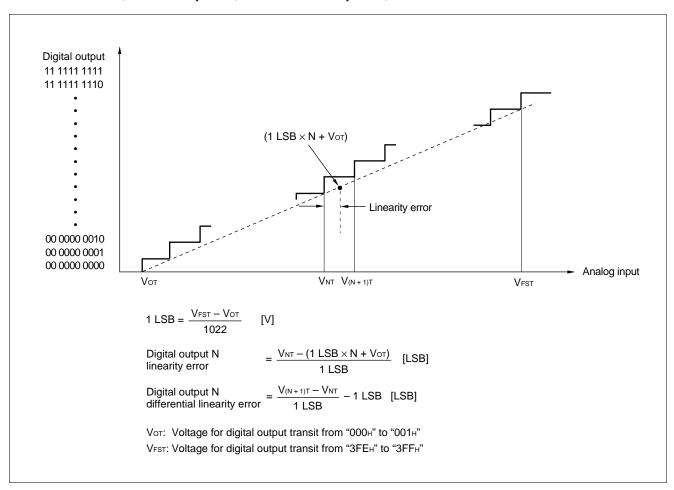

- 8/10-bit A/D converter: analog inputs: 6 channels

Resolution: 10 bits (switchable to 8 bits)

Conversion time: min. 1.0 µs

Conversion result store register: 4 channels

- 16-bit free-run timer: 1 channel (operating clock: 0.2 μs)

- 16-bit input capture: 4 channels

- 16-bit reload timer: 3 channels

- Low-power consumption modes

Sleep mode

Stop mode

Hardware standby mode

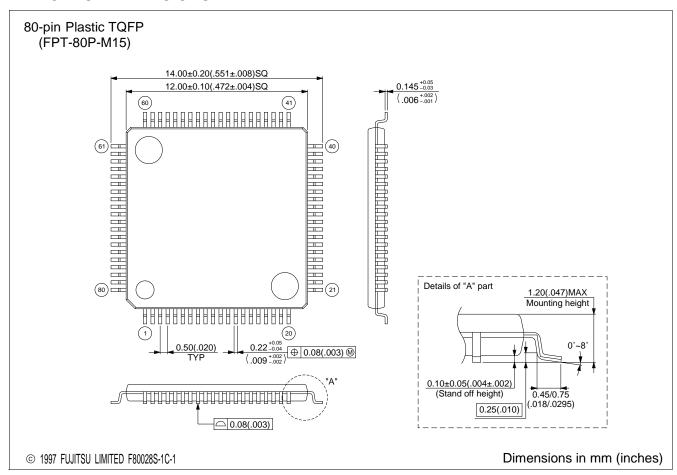

• Package: TQFP-80

CMOS technology

## **■ PRODUCT LINEUP**

| Ite             | Part number                          | MB90F243H                                                                | MB90F243                        | MB90242A                                                              | MB90V241       |  |  |

|-----------------|--------------------------------------|--------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------|----------------|--|--|

| Class           | sification                           | Flash mem                                                                | ory version                     | External ROM product                                                  | For evaluation |  |  |

|                 | ROM size                             |                                                                          | nemory<br>(bytes                | No                                                                    | one            |  |  |

|                 | RAM size                             | 1 K                                                                      | byte                            | 2 Kbytes                                                              | 4 Kbytes       |  |  |

| ē               | Number of instructions               |                                                                          | 412 inst                        | ructions                                                              |                |  |  |

| CPU core        | Minimum execution time               | 50.0 ns at<br>40 MHz                                                     |                                 | 62.5 ns at 32 MHz                                                     | <u>'</u>       |  |  |

|                 | Product-sum operation unit           | No                                                                       | one                             | On                                                                    | chip           |  |  |

|                 | Low-power consumption modes          |                                                                          | Sleep, stop, ha                 | rdware standby                                                        |                |  |  |

|                 | DTP/external interrupts              | Interrupt sources: 23 channels/<br>external interrupt inputs: 4 channels |                                 |                                                                       |                |  |  |

|                 | Ports                                | Output ports<br>(N-channel op<br>I/O ports (CM<br>Total:                 | pen-drain): 6<br>IOS): 56<br>62 | Output ports (N-channel open-drain): 6 I/O ports (CMOS): 32 Total: 38 |                |  |  |

|                 | Timebase timer                       | 18 bits × 1 channel                                                      |                                 |                                                                       |                |  |  |

| als             | UART                                 | 8 bits × 1 channel                                                       |                                 |                                                                       |                |  |  |

| Peripherals     | 8/10-bit A/D converter               | 8/10-bit resolution $\times$ 6 channels                                  |                                 |                                                                       |                |  |  |

| Peri            | 8/16-bit I/O simple serial interface |                                                                          | 8/16 bits × 1 channel           |                                                                       |                |  |  |

|                 | 16-bit free-run timer                | 16 bits × 1 channel                                                      |                                 |                                                                       |                |  |  |

|                 | 16-bit input capture                 |                                                                          | 16 bits × 4                     | 4 channels                                                            |                |  |  |

|                 | 16-bit reload timer                  | 3 cha                                                                    | nnels                           | 2 channels                                                            | 3 channels     |  |  |

|                 | Watchdog timer function              | On chip                                                                  |                                 |                                                                       |                |  |  |

| ics             | Power supply voltage*                |                                                                          | 4.5 V to                        | o 5.5 V                                                               |                |  |  |

| terist          | Operating temperature                | 0°C to +70°C                                                             | -25°C to +85°C                  | -30°C to +70°C                                                        | 0°C to +70°C   |  |  |

| Characteristics | System clock frequency               | 40 MHz<br>(5.0 V ±10%) 32 MHz (5.0 V ±10%)                               |                                 |                                                                       | %)             |  |  |

| Proce           | ess                                  | CMOS                                                                     |                                 |                                                                       |                |  |  |

<sup>\* :</sup> Varies with conditions such as the operating frequency. (See section "■ Electrical Characteristics.")

## ■ PACKAGE AND CORRESPONDING PRODUCTS

| Package       | Package MB90F243H |   | MB90242A |

|---------------|-------------------|---|----------|

| FPT-80P-M05 × |                   | 0 | 0        |

| FPT-80P-M15   | 0                 | 0 | ×        |

○ : Available × : Not available

Note: For more information about each package, see section "■ Package Dimensions."

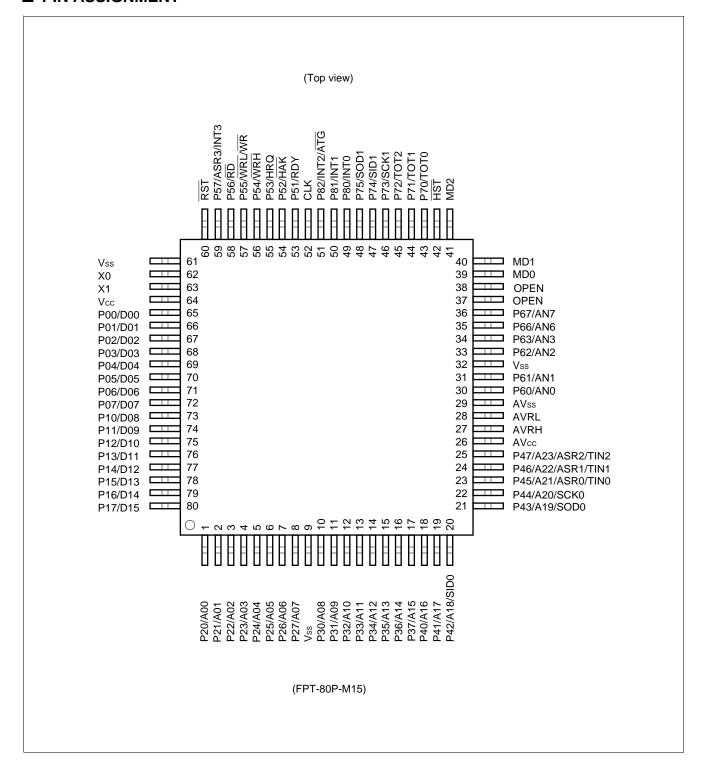

### **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

| Pin no.  | Pin name   | Circuit type | Function                                                                                                                                                                           |  |

|----------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFP-80* |            | 1            |                                                                                                                                                                                    |  |

| 62       | X0         | Α            | Crystal oscillator pins (40 MHz)                                                                                                                                                   |  |

| 63       | X1         |              |                                                                                                                                                                                    |  |

| 39 to 41 | MD0 to MD2 | С            | Operating mode selection input pins Connect directly to Vcc or Vss. In the flash memory mode, these pins are set to be Vid (= 12.0 V) input pins by performing a proper operation. |  |

| 60       | RST        | В            | External reset request input pin                                                                                                                                                   |  |

| 42       | HST        | D            | Hardware standby input pin                                                                                                                                                         |  |

| 65 to 72 | P00 to P07 | Е            | General-purpose I/O port                                                                                                                                                           |  |

|          | D00 to D07 |              | I/O pins for the lower 8 bits of the external data bus                                                                                                                             |  |

| 73 to 80 | P10 to P17 | Е            | General-purpose I/O port This function is valid when the external bus 8-bit mode.                                                                                                  |  |

|          | D08 to D17 |              | I/O pins for the upper 8 bits of the external data bus This function is valid when 16-bit bus mode.                                                                                |  |

| 1 to 8   | P20 to P27 | F            | General-purpose I/O port                                                                                                                                                           |  |

|          | A00 to A07 |              | Output pins for the medium 8 bits of the external address bus                                                                                                                      |  |

| 10 to 17 | P30 to P37 | F            | General-purpose I/O port This function is valid when the corresponding bit of the middle address control register specification is "port".                                         |  |

|          | A08 to A15 |              | Output pins for the medium 8 bits of the external address bus This function is valid when the corresponding bit of the middle address control register specification is "port".    |  |

| 18       | P40        | F            | General-purpose I/O port This function is valid when the corresponding bit of the upper address control register specification is "port".                                          |  |

|          | A16        |              | External address bus output pin of the bit 16 This function is valid when the corresponding bit of the upper address control register specification is "address".                  |  |

| 19       | P41        | F            | General-purpose I/O port This function is valid when the upper address control register specification is "port".                                                                   |  |

|          | A17        |              | External address bus output pin of the bit 17 This function is valid when the corresponding bit of the upper address control register specification is "address".                  |  |

<sup>\*:</sup> FPT-80P-M15 (Continued)

| Pin no.  | Pin name        | Circuit | Function                                                                                                                                                                                                                                                |

|----------|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP-80* | - I III IIailic | type    | T unotion                                                                                                                                                                                                                                               |

| 20       | P42             | F       | General-purpose I/O port This function is valid when the corresponding bit of the upper address control register specification is "port".                                                                                                               |

|          | A18             |         | External address bus output pin of the bit 18 This function is valid when the corresponding bit of the upper address control register specification is "address".                                                                                       |

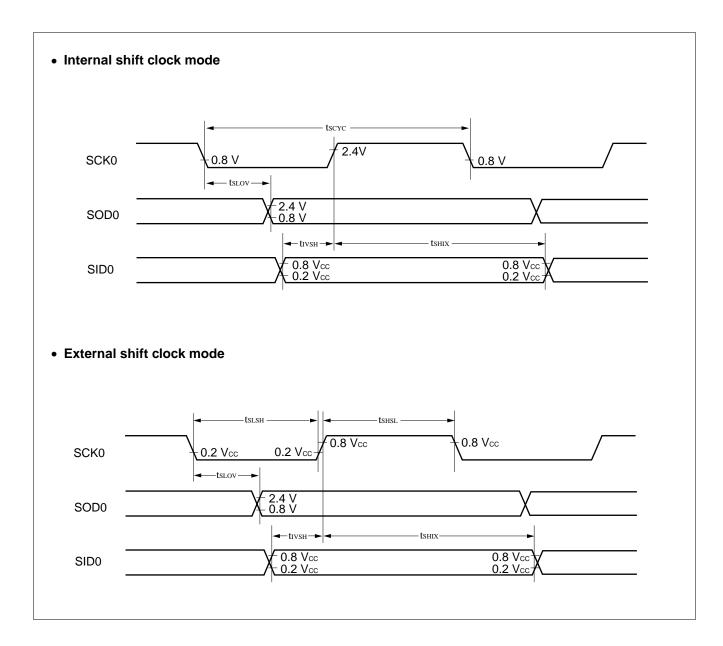

|          | SID0            |         | UART #0 data input pin During UART #0 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                                 |

| 21       | P43             | G       | General-purpose I/O port This function is valid when the UART #0 data output is disabled and the corresponding bit of the upper address control register specification is "port".                                                                       |

|          | A19             |         | External address bus output pin of the bit 19 This function is valid when the UART #0 data output is disabled and the corresponding bit of the upper address control register specification is "address".                                               |

|          | SOD0            |         | UART #0 data output pin This function is valid when the UART #0 data output is enabled.                                                                                                                                                                 |

| 22       | P44             | G       | General-purpose I/O port This function is valid when the UART #0 and SSI #2 clock output are disabled and the corresponding bit of the upper address control register specification is "port".                                                          |

|          | A20             |         | External address bus output pin of the bit 20 This function is valid when the UART #0 clock output is disabled and the corresponding bit of the upper address control register specification is "address".                                              |

|          | SCK0            |         | UART #0 clock I/O pin                                                                                                                                                                                                                                   |

| 23       | P45             | G       | General-purpose I/O port This function is valid when the SSI #2 data output is disabled and the corresponding bit of the upper address control register specification is "port".                                                                        |

|          | A21             |         | External address bus output pin of the bit 21 This function is valid when the SSI #2 data output is disabled and the corresponding bit of the upper address control register specification is "address".                                                |

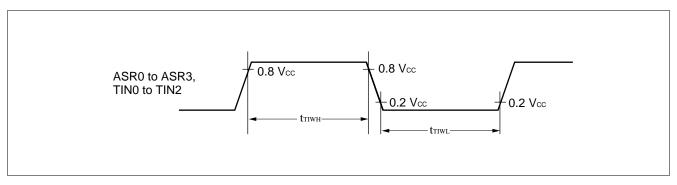

|          | ASR0            |         | 16-bit input capture #0 data input pin During 16-bit input capture #0 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately. |

|          | TINO            |         | 16-bit timer #0 data input pin During 16-bit timer #0 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                 |

| Pin no. | Pin name | Circuit<br>type | Function                                                                                                                                                                                                                                                |

|---------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | P46      | G               | General-purpose I/O port This function is valid when the corresponding bit of the upper address control register specification is "port".                                                                                                               |

|         | A22      |                 | External address bus output pin of the bit 22 This function is valid when the corresponding bit of the upper address control register specification is "address".                                                                                       |

|         | ASR1     |                 | 16-bit input capture #1 data input pin During 16-bit input capture #1 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately. |

|         | TIN1     |                 | 16-bit timer #1 data input pin During 16-bit timer #1 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                 |

| 25      | P47      | G               | General-purpose I/O port This function is valid when the corresponding bit of the upper address control register specification is "port".                                                                                                               |

|         | A23      |                 | External address bus output pin for the bit 23 This function is valid when the corresponding bit of the upper address control register specification is "address".                                                                                      |

|         | ASR2     |                 | 16-bit input capture #2 data input pin During 16-bit input capture #2 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately. |

|         | TIN2     |                 | 16-bit timer #2 data input pin During 16-bit timer #2 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                 |

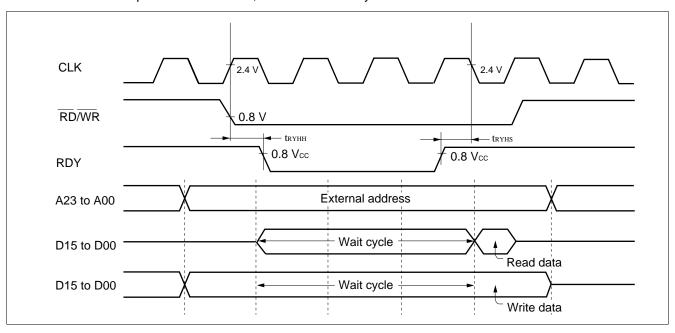

| 53      | P51      | Н               | General-purpose I/O port This function is valid when the ready function is disabled.                                                                                                                                                                    |

|         | RDY      |                 | Ready input pin This function is valid when the ready function is enabled.                                                                                                                                                                              |

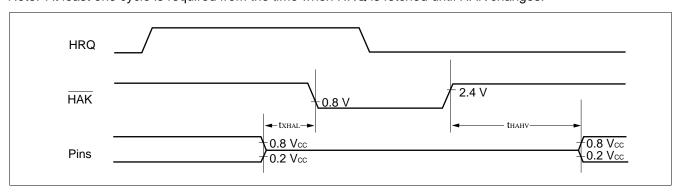

| 54      | P52      | Н               | General-purpose I/O port This function is valid when the hold function is disabled.                                                                                                                                                                     |

|         | HAK      | 1               | Hold acknowledge output pin This function is valid when the hold function is enabled.                                                                                                                                                                   |

| 55      | P53      | Н               | General-purpose I/O port This function is valid when the hold function is disabled.                                                                                                                                                                     |

|         | HRQ      |                 | Hold request input pin This function is valid and when the hold function is enabled.                                                                                                                                                                    |

| Pin no.                               | Pin name                                    | Circuit | Function                                                                                                                                                                                                                                                    |

|---------------------------------------|---------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP-80*                              | Fill liame                                  | type    | T unction                                                                                                                                                                                                                                                   |

| 56                                    | P54                                         | F       | General-purpose I/O port This function is valid in external bus eight-bit mode, or when WRH pin output is disabled.                                                                                                                                         |

|                                       | WRH                                         |         | Write strobe output pin for the upper eight bits of the data bus This function is valid in modes where the external bus 16-bit mode is enabled, and WRH pin output is enabled.                                                                              |

| 57                                    | P55                                         | F       | General-purpose I/O port This function is valid when WRL pin output is disabled.                                                                                                                                                                            |

|                                       | WRL / WR                                    |         | Write strobe output pin for the lower eight bits of the data bus This function is valid WRL pin output is enabled.                                                                                                                                          |

| 58                                    | P56                                         | F       | General-purpose I/O port                                                                                                                                                                                                                                    |

|                                       | RD                                          |         | Read strobe output pin for the data bus                                                                                                                                                                                                                     |

| 59                                    | P57                                         | F       | General-purpose I/O port                                                                                                                                                                                                                                    |

|                                       | ASR3                                        |         | 16-bit input capture #3 data input pin During 16-bit input capture #3 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.     |

|                                       | INT3                                        |         | DTP/external interrupt #3 data input pin During DTP/external interrupt #3 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately. |

| 30,<br>31,<br>33,<br>34,<br>35,<br>36 | P60,<br>P61,<br>P62,<br>P63,<br>P66,<br>P67 | I       | N-ch open-drain type I/O ports When bits corresponding to the ADER are set to "0", reading instructions other than the read-modify-write group returns the pin level. The value written on the data register is output to this pin directly.                |

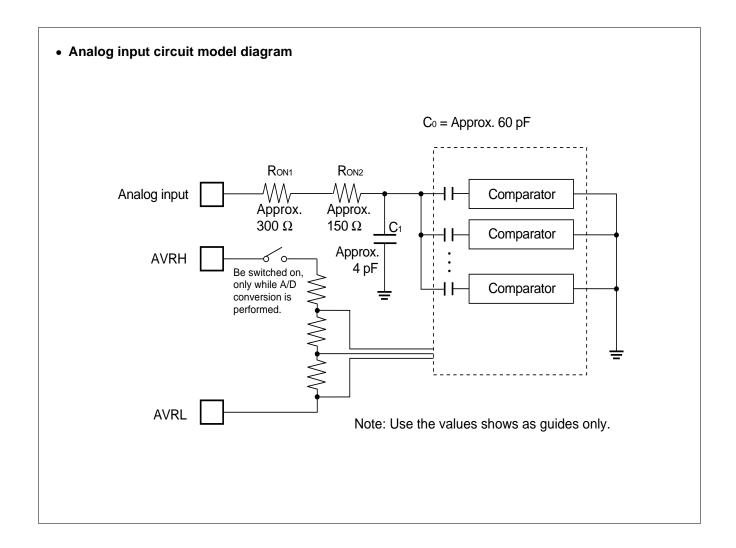

|                                       | AN0,<br>AN1,<br>AN2,<br>AN3,<br>AN6,<br>AN7 |         | 8/10-bit A/D converter analog input pins Use this function after setting bits corresponding to the ADER to "1" and setting corresponding bits of the data register to "1".                                                                                  |

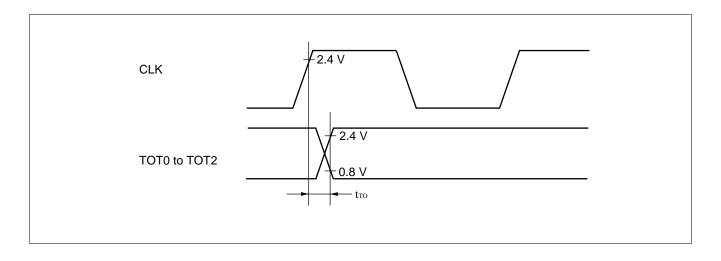

| 43 to 45                              | P70 to P72                                  | G       | General-purpose I/O port This function is valid when the reload timer #0, #1, and #2 output is disabled.                                                                                                                                                    |

|                                       | TOT0 to TOT2                                |         | 16-bit timer output pins This function is valid when the 16-bit timer #0, #1, and #2 output is enabled.                                                                                                                                                     |

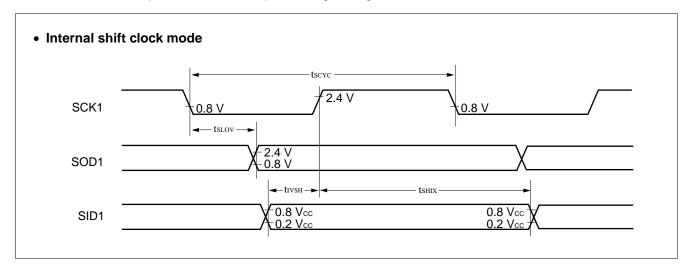

| 46                                    | P73                                         | G       | General-purpose I/O port This function is valid when the SSI #1 clock output is disabled.                                                                                                                                                                   |

|                                       | SCK1                                        |         | SSI #1 clock output I/O pin                                                                                                                                                                                                                                 |

| Pin no.         | Pin name      | Circuit      | Function                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP-80*        | Finitianie    | type         | Function                                                                                                                                                                                                                                                                                                                                                             |

| 47              | P74           | G            | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                                                                                                              |

|                 | SID1          |              | SSI #1 data input pin During SSI #1 input operations, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                                                                                                                                                |

| 48              | P75           | G            | General-purpose I/O port This function is valid when the SSI #1 data output is disabled.                                                                                                                                                                                                                                                                             |

|                 | SOD1          |              | SSI #1 data output pin This function is valid when the SSI #1 data output is disabled.                                                                                                                                                                                                                                                                               |

| 49,<br>50       | P80,<br>P81   | G            | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                                                                                                              |

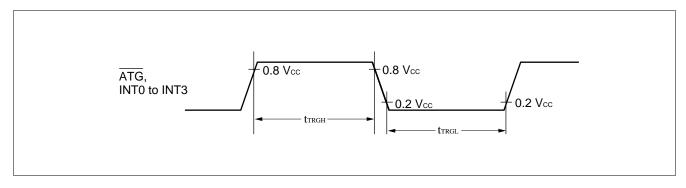

|                 | INTO,<br>INT1 |              | DTP/external interrupt input pin When external interrupts are enabled, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately.                                                                                                                               |

| 51              | P82           | G            | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                                                                                                              |

|                 | INT2          |              | DTP/external interrupt input pin When external interrupts are enabled, these inputs may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using them for output deliberately. Because an input to this pin is clamped to Low when the CPU stops, use INT0 or INT1 to wake up the system from the stop mode. |

|                 | ATG           |              | 8/10-bit A/D converter trigger input pin When 8/10-bit A/D converter is waiting for activation, this input may be used at any time; therefore, it is necessary to stop output by other functions on this pin, except when using it for output deliberately.                                                                                                          |

| 37,<br>38       | OPEN          | _            | Open pins No internal connections are made.                                                                                                                                                                                                                                                                                                                          |

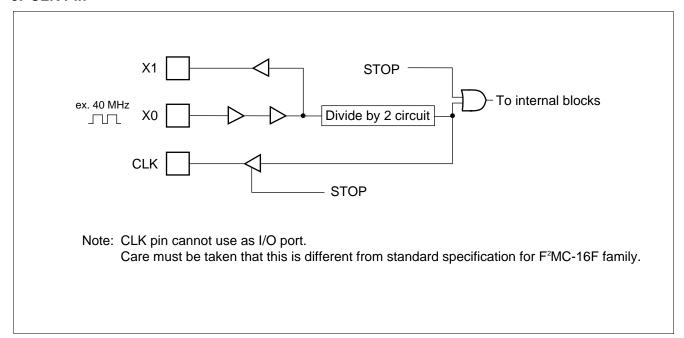

| 52              | CLK           | G            | CLK output pin                                                                                                                                                                                                                                                                                                                                                       |

| 64              | Vcc           | Power supply | Digital circuit power supply pin                                                                                                                                                                                                                                                                                                                                     |

| 9,<br>32,<br>61 | Vss           | Power supply | Digital circuit power supply (GND) pin                                                                                                                                                                                                                                                                                                                               |

| 26              | AVcc          | Power supply | Analog circuit power supply pin This power supply must only be turned on or off when electric potential of AVcc or greater is applied to Vcc.                                                                                                                                                                                                                        |

| *· EDT_Q0D_M15  |               |              | (Continued                                                                                                                                                                                                                                                                                                                                                           |

## (Continued)

| Pin no.<br>TQFP-80* | Pin name | Circuit<br>type | Function                                                                                                                                                          |

|---------------------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27                  | AVRH     | Power<br>supply | 8/10-bit A/D converter external reference voltage input pin This pin must only be turned on or off when electric potential of AVRH or greater is applied to AVcc. |

| 28                  | AVRL     | Power supply    | 8/10-bit A/D converter external reference voltage input pin                                                                                                       |

| 29                  | AVss     | Power supply    | Analog circuit power supply (GND) pin                                                                                                                             |

<sup>\*:</sup> FPT-80P-M15

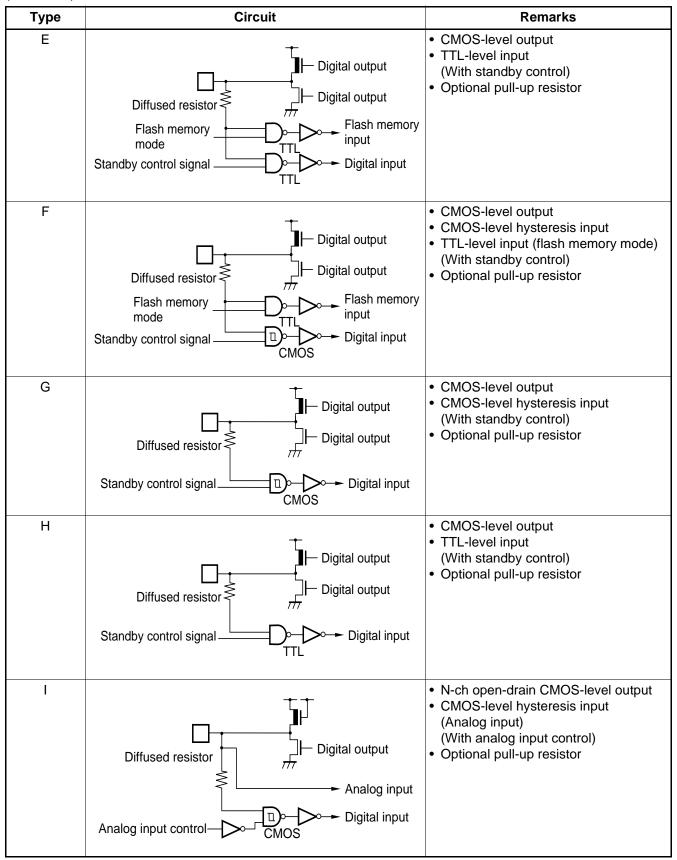

## ■ I/O CIRCUIT TYPE

| Туре | Circuit                                            | Remarks                                                                                                                    |

|------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| A    | X0 Clock input                                     | <ul> <li>40 MHz</li> <li>Oscillation feedback resistor:<br/>approximately 1 MΩ</li> </ul>                                  |

| В    | Diffusion resistor P-ch Tr  N-ch Tr  Digital input | <ul> <li>CMOS-level hysteresis input<br/>Without standby control</li> <li>Pull-up resistor: approximately 50 KΩ</li> </ul> |

| С    | Control signal  W Mode input  Diffusion resistor   | CMOS-level input     High voltage control for flash memory testing                                                         |

| D    | Diffusion resistor P-ch Tr  N-ch Tr  Digital input | CMOS-level hysteresis input<br>(Without standby control)     Optional pull-up resistor                                     |

#### (Continued)

#### **■ HANDLING DEVICES**

### 1. Preventing Latchup

Latchup may occur on CMOS ICs if voltage higher than Vcc or lower than Vss is applied to the input or output pins other than medium-and high-voltage pins or if higher than the voltage which shown on "■ Absolute Maximum Ratings" is applied between Vcc and Vss.

When latchup occurs, power supply current increases rapidly might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

In addition, for the same reasons take care to prevent the analog power supply from exceeding the digital power supply.

#### 2. Treatment of Unused Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistors.

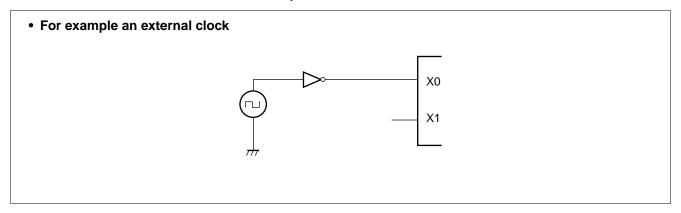

### 3. Precautions when Using an External Clock

When an external clock is used, drive X0 only.

### 4. Power Supply Pins

When there are several  $V_{CC}$  and  $V_{SS}$  pins, those pins that should have the same electric potential are connected within the device when the device is designed in order to prevent misoperation, such as latch-up. However, all of those pins must be connected to the power supply and ground externally in order to reduce unnecessary emissions, prevent misoperation of strobe signals due to an increase in the ground level, and to observe the total output current standards.

In addition, give a due consideration to the connection in that current supply be connected to  $V_{CC}$  and  $V_{SS}$  with the lowest possible impedance.

Finally, it is recommended to connect a capacitor of about 0.1  $\mu$ F between  $V_{CC}$  and  $V_{SS}$  near this device as a bypass capacitor.

### 5. Crystal Oscillation Circuit

Noise in the vicinity of the X0 and X1 pins will cause this device to operate incorrectly. Design the printed circuit board so that the bypass capacitor connecting X0 and X1 pins and the crystal oscillator (or ceramic oscillator) to ground is located as close to the device as possible.

In addition, because printed circuit board artwork in which the area around the X0 and X1 pins is surrounded by ground provides stable operation, such an arrangement is strongly recommended.

### 6. Sequence for Applying the A/D Converter Power Supply and the Analog Inputs

Always be sure to apply the digital power supply (Vcc) before applying the A/D converter power supply (AVcc, AVRH, and AVRL) and the analog inputs (AN0 to AN7).

In addition, when the power is turned off, turn off the A/D converter power supply and the analog inputs first, and then turn off the digital power supply. (Turning on or off the analog and digital power supplies simultaneously will not cause any problems.)

Whether applying or cutting off the power, be certain that AVRH does not exceed AVcc.

### 7. External Reset Input

To reliably reset the controller by inputting an "L" level to the  $\overline{RST}$  pin, ensure that the "L" level is applied for at least five machine cycles.

#### 8. HST Pin

When turning on the system, be sure to set the  $\overline{\text{HST}}$  pin to "H" level. Never set the  $\overline{\text{HST}}$  pin to "L" level while the  $\overline{\text{RST}}$  pin is in "L" level.

#### 9. CLK Pin

### **■ BLOCK DIAGRAM**

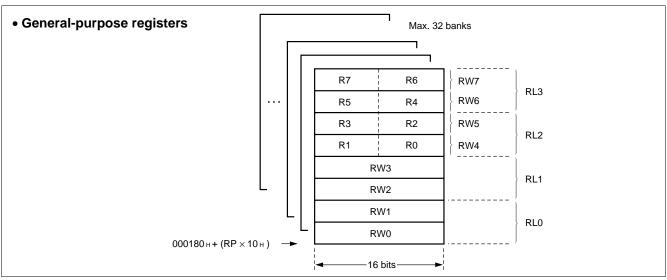

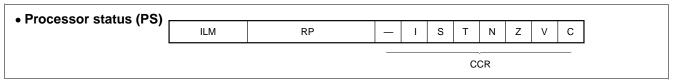

### ■ F<sup>2</sup>MC-16L CPU PROGRAMMING MODEL

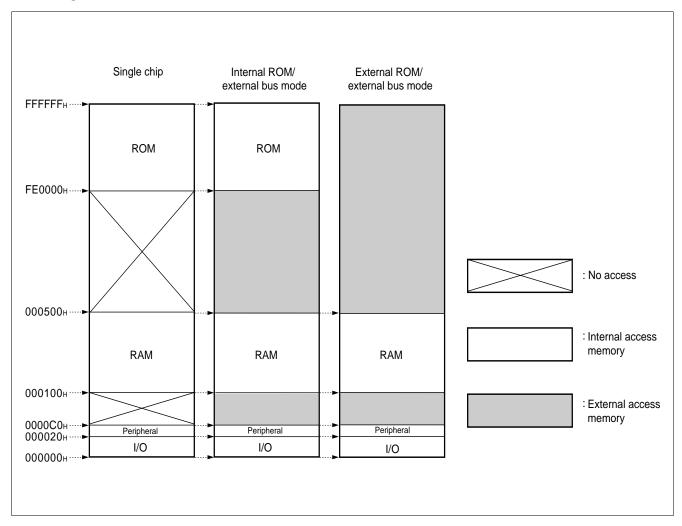

## **■ MEMORY MAP**

## ■ I/O MAP

| Address                  | Register<br>name | Register                                         | Read/<br>write | Resource name              | Initial value |

|--------------------------|------------------|--------------------------------------------------|----------------|----------------------------|---------------|

| 000000н                  | PDR0             | Port 0 data register                             | R/W            | Port 0                     | XXXXXXX       |

| 000001н                  | PDR1             | Port 1 data register                             | R/W            | Port 1                     | XXXXXXX       |

| 000002н                  | PDR2             | Port 2 data register                             | R/W            | Port 2                     | XXXXXXX       |

| 000003н                  | PDR3             | Port 3 data register                             | R/W            | Port 3                     | XXXXXXX       |

| 000004н                  | PDR4             | Port 4 data register                             | R/W            | Port 4                     | XXXXXXX       |

| 000005н                  | PDR5             | Port 5 data register                             | R/W            | Port 5                     | XXXXXXX—      |

| 000006н                  | PDR6             | Port 6 data register                             | R/W            | Port 6                     | 111111        |

| 000007н                  | PDR7             | Port 7 data register                             | R/W            | Port 7                     | XXXXXX        |

| 000008н                  | PDR8             | Port 8 data register                             | R/W            | Port 8                     | XXX           |

| 000009н<br>to<br>00000Fн |                  | (Vacancy)                                        |                |                            |               |

| 000010н                  | DDR0             | Port 0 direction register                        | R/W            | Port 0                     | 00000000      |

| 000011н                  | DDR1             | Port 1 data direction register                   | R/W            | Port 1                     | 00000000      |

| 000012н                  | DDR2             | Port 2 direction register                        | R/W            | Port 2                     | 00000000      |

| 000013н                  | DDR3             | Port 3 direction register                        | R/W            | Port 3                     | 00000000      |

| 000014н                  | DDR4             | Port 4 data direction register                   | R/W            | Port 4                     | 00000000      |

| 000015н                  | DDR5             | Port 5 data direction register                   | R/W            | Port 5                     | 000000-       |

| 000016н                  | ADER             | Analog input enable register                     | R/W            | Analog input enabled       | 111111        |

| 000017н                  | DDR7             | Port 7 data direction register                   | R/W            | Port 7                     | 000000        |

| 000018н                  | DDR8             | Port 8 data direction register                   | R/W            | Port 8                     | 000           |

| 000019н<br>to<br>00001Fн |                  | (Vacancy)                                        |                |                            |               |

| 000020н                  | SCR1             | Serial control status register 1                 | R/W            |                            | 10000000      |

| 000021н                  | SSR1             | Serial status register 1                         | R/W            | 8/16-bit I/O simple serial | 00            |

| 000022н                  | SDR1L            | Serial data register 1 (L)                       | R/W            | interface ch. 1            | XXXXXXX       |

| 000023н                  | SDR1H            | Serial data register 1 (H)                       | R/W            |                            | XXXXXXX       |

| 000024н<br>to<br>000027н |                  | (Vacancy)                                        |                |                            |               |

| 000028н                  | UMC0             | Mode control register 0                          | R/W            |                            | 00000100      |

| 000029н                  | USR0             | Status register 0                                | R/W            |                            | 00010000      |

| 00002Ан                  | UIDR0/<br>UODR0  | Input data register 0/<br>output data register 0 | R/W            | UART ch. 0                 | xxxxxxx       |

| 00002Вн                  | URD0             | Rate and data register 0                         | R/W            |                            | 0000000       |

| 00002Сн                  |                  |                                                  |                |                            |               |

| to<br>00002Fн            |                  | (Vacancy)                                        |                |                            |               |

| Address                  | Register name | Register                                      | Read/<br>write | Resource name                | Initial value |  |  |

|--------------------------|---------------|-----------------------------------------------|----------------|------------------------------|---------------|--|--|

| 000030н                  | ENIR          | DTP/interrupt enable register                 | R/W            |                              | 0000          |  |  |

| 000031н                  | EIRR          | DTP/interrupt source register                 | R/W            | DTP/external interrupt       | 0000          |  |  |

| 000032н                  | ELVR          | Request level setting register                | R/W            | morrapt                      | 00000000      |  |  |

| 000033н<br>to            |               | (Vacancy)                                     |                |                              |               |  |  |

| 00003Fн                  |               |                                               |                |                              |               |  |  |

| 000040н                  | TMCSR0        | Timer control status register #0              | R/W            | =                            | 0000000       |  |  |

| 000041н                  |               | ŭ                                             | R/W            |                              | XXXX0000      |  |  |

| 000042н                  | TMR0          | 16-bit timer register #0                      | R              | 16-bit timer #0              | XXXXXXX       |  |  |

| 000043н                  |               | . o on anno regione no                        | R              |                              | XXXXXXX       |  |  |

| 000044н                  | TMRLR0        | 16-bit reload register #0                     | W              | _                            | XXXXXXX       |  |  |

| 000045н                  | TWITTER       | To bit foldad fogister #0                     | W              |                              | XXXXXXX       |  |  |

| 000046н                  |               | (Managar)                                     |                |                              |               |  |  |

| 000047н                  |               | (Vacancy)                                     |                |                              |               |  |  |

| 000048н                  | TMCCD4        | Timer central status register #1              | R/W            |                              | 00000000      |  |  |

| 000049н                  | TMCSR1        | Timer control status register #1              | R/W            | -                            | XXXX0000      |  |  |

| 00004Ан                  | TMD4          | 40.1343                                       | R              | 16-bit timer #1              | XXXXXXXX      |  |  |

| 00004Вн                  | TMR1          | 16-bit timer register #1                      | R              |                              | XXXXXXXX      |  |  |

| 00004Сн                  | TMDI D4       | MRLR1 16-bit reload register #1               | W              |                              | XXXXXXXX      |  |  |

| 00004Дн                  | TMRLR1        |                                               | W              |                              | XXXXXXXX      |  |  |

| 00004Ен                  |               | 0.6                                           |                | 1                            |               |  |  |

| 00004Fн                  |               | (Vacancy)                                     |                |                              |               |  |  |

| 000050н                  | T1400D0       | <del></del>                                   | R/W            |                              | 00000000      |  |  |

| 000051н                  | TMCSR2        | Timer control status register #2              | R/W            | =                            | XXXX0000      |  |  |

| 000052н                  |               |                                               | R              | -                            | XXXXXXXX      |  |  |

| 000053н                  | TMR2          | 16-bit timer register #2                      | R              | 16-bit timer #2              | XXXXXXXX      |  |  |

| 000054н                  |               |                                               | W              | =                            | XXXXXXXX      |  |  |

| 000055н                  | TMRLR2        | 16-bit reload register #2                     | W              | _                            | XXXXXXXX      |  |  |

| 000056н<br>to<br>00005Fн |               | (Vacancy)                                     |                |                              | 1             |  |  |

| 000060н                  | IODO          | Innut conture register 2                      | R              |                              | XXXXXXX       |  |  |

| 000061н                  | ICP0          | Input capture register 0                      | R              | -                            | XXXXXXX       |  |  |

| 000062н                  | 1054          |                                               | R              | 16-bit input capture 0 and 1 | XXXXXXX       |  |  |

| 000063н                  | ICP1          | Input capture register 1                      | R              | _ capture o and i            | XXXXXXX       |  |  |

| 000064н                  | ICS0          | Input capture control status register 0 and 1 | R/W            |                              | 00000000      |  |  |

| 000065н                  |               | (Vacancy)                                     | <u> </u>       | 1                            | 1             |  |  |

(Continued)

| Address                  | Register name | Register                                                 | Read/<br>write | Resource name                             | Initial value |

|--------------------------|---------------|----------------------------------------------------------|----------------|-------------------------------------------|---------------|

| 000066н                  | ICD2          | Input conture register 2                                 | R              |                                           | XXXXXXX       |

| 000067н                  | ICP2          | Input capture register 2                                 | R              | 1                                         | XXXXXXXX      |

| 000068н                  | ICP3          | Input conture register 2                                 | R              | 16-bit input capture 2 and 3              | XXXXXXXX      |

| 000069н                  | ICP3          | Input capture register 3                                 | R              |                                           | XXXXXXX       |

| 00006Ан                  | ICS1          | Input capture control status register 2 and 3            | R/W            |                                           | 00000000      |

| 00006Вн                  |               | (Vacancy)                                                |                | -1                                        |               |

| 00006Сн                  | TCDT          | Timer data register                                      | R/W            |                                           | 00000000      |

| 00006Dн                  | ICDI          | Timer data register                                      | R/W            | 16-bit free-run<br>timer                  | 00000000      |

| 00006Ен                  | TCCS          | Timer control status register                            | R/W            |                                           | 00000000      |

| 00006Fн                  |               | (Vacancy)                                                |                | -1                                        |               |

| 000070н                  | ADCS1         | A/D converter control register 1                         | R/W            |                                           | 000-0000      |

| 000071н                  | ADCS2         | A/D converter control register 2                         | R/W            |                                           | -00000        |

| 000072н                  | ADCT1         | Conversion time setting register 1                       | R/W            |                                           | XXXXXXX       |

| 000073н                  | ADCT2         | Conversion time setting register 2                       | R/W            | 8/10-bit A/D<br>converter                 | XXXXXXX       |

| 000074н                  | ADTL0         | A/D data register 0 (L)                                  | R              |                                           | XXXXXXX       |

| 000075н                  | ADTH0         | A/D data register 0 (H)                                  | R              |                                           | XX            |

| 000076н                  | ADTL1         | A/D data register 1 (L)                                  | R              |                                           | XXXXXXXX      |

| 000077н                  | ADTH1         | A/D data register 1 (H)                                  | R              |                                           | XX            |

| 000078н                  | ADTL2         | A/D data register 2 (L)                                  | R              |                                           | XXXXXXXX      |

| 000079н                  | ADTH2         | A/D data register 2 (H)                                  | R              |                                           | XX            |

| 00007Ан                  | ADTL3         | A/D data register 3 (L)                                  | R              |                                           | XXXXXXXX      |

| 00007Вн                  | ADTH3         | A/D data register 3 (H)                                  | R              |                                           | XX            |

| 00007Сн<br>to<br>00008Fн |               | (Vacancy)                                                |                |                                           |               |

| 000090н<br>to<br>00009Ен |               | (System reserved ar                                      | rea)*1         |                                           |               |

| 00009Fн                  | DIRR          | Delayed interrupt source generation/<br>release register | R/W            | Delayed interrupt<br>generation<br>module | 0             |

| 0000А0н                  | STBYC         | Standby control register R/W                             |                | Low-power consumption mode                | 0001XXXX      |

| 0000АЗн                  | MACR          | Middle address control register                          | W              |                                           | *2            |

| 0000А4н                  | HACR          | Upper address control register                           | W              | External pin                              | *2            |

| 0000А5н                  | EPCR          | External pin control register                            | W              |                                           | *2            |

| 0000А8н                  | WTC           | Watchdog timer control register                          | R/W            | Watchdog timer                            | XXXXXXX       |

| 0000А9н                  | TBTC          | Timebase timer control register                          | R/W            | Timebase timer                            | 0XX00000      |

(Continued)

### (Continued)

| Address                  | Register<br>name | Register                      | Read/<br>write | Resource name | Initial value |

|--------------------------|------------------|-------------------------------|----------------|---------------|---------------|

| 0000АЕн                  | FMCS             | Control status register       | R/W            | Flash memory  | 000X00        |

| 0000В0н                  | ICR00            | Interrupt control register 00 | R/W*3          |               | 00000111      |

| 0000В1н                  | ICR01            | Interrupt control register 01 | R/W*3          |               | 00000111      |

| 0000В2н                  | ICR02            | Interrupt control register 02 | R/W*3          |               | 00000111      |

| 0000ВЗн                  | ICR03            | Interrupt control register 03 | R/W*3          |               | 00000111      |

| 0000В4н                  | ICR04            | Interrupt control register 04 | R/W*3          | -             | 00000111      |

| 0000В5н                  | ICR05            | Interrupt control register 05 | R/W*3          | -             | 00000111      |

| 0000В6н                  | ICR06            | Interrupt control register 06 | R/W*3          |               | 00000111      |

| 0000В7н                  | ICR07            | Interrupt control register 07 | R/W*3          | Interrupt     | 00000111      |

| 0000В8н                  | ICR08            | Interrupt control register 08 | R/W*3          | controller    | 00000111      |

| 0000В9н                  | ICR09            | Interrupt control register 09 | R/W*3          |               | 00000111      |

| 0000ВАн                  | ICR10            | Interrupt control register 10 | R/W*3          | -             | 00000111      |

| 0000ВВн                  | ICR11            | Interrupt control register 11 | R/W*3          | -             | 00000111      |

| 0000ВСн                  | ICR12            | Interrupt control register 12 | R/W*3          | -             | 00000111      |

| 0000ВДн                  | ICR13            | Interrupt control register 13 | R/W*3          | -             | 00000111      |

| 0000ВЕн                  | ICR14            | Interrupt control register 14 | R/W*3          | -             | 00000111      |

| 0000ВFн                  | ICR15            | Interrupt control register 15 | R/W*3          | 1             | 00000111      |

| 0000С0н<br>to<br>0000FFн |                  | (External                     | area)*³        |               |               |

### Explanation of read/write

R/W: Readable and writable

R : Read only W : Write only

### Explanation of initial values

- 0: The initial value of this bit is "0".

- 1: The initial value of this bit is "1".

- X: The initial value of this bit is undefined.

- -: This bit is unused. No initial value is defined.

- \*1: Access prohibited.

- \*2: The initial values are changed depending on a bus mode.

- \*3: The only area available for the external access below address 0000FFH is this area. Addresses not explained in the table are "(reserved area)"; accesses to these areas are handled accesses to internal areas. No access signal is generated for the external bus.

Note: Do not use any "(Vacancy)".

### **■ ELECTRICAL CHARACTERISTICS**

## 1. Absolute Maximum Ratings

(AVss = Vss = 0.0 V)

| Parameter                              | Symbol        | Va          | lue       | Unit  | Remarks |

|----------------------------------------|---------------|-------------|-----------|-------|---------|

| Farameter                              | Syllibol      | Min.        | Max.      | Oiiit | Remarks |

|                                        | Vcc           | Vss - 0.3   | Vss + 7.0 | V     |         |

| Power supply voltage                   | AVcc          | Vcc - 0.3   | Vcc + 7.0 | V     |         |

| Power supply voltage                   | AVRH          | Vss - 0.3   | Vss+ 7.0  | V     | *1      |

|                                        | AVRL          | Vss-0.3     | Vss + 7.0 | V     |         |

| Input voltage                          | Vı            | Vss-0.3     | Vcc + 0.3 | V     | *2      |

| Output voltage                         | Vo            | Vss-0.3     | Vcc + 0.3 | V     | *2      |

| "L" level maximum output current       | loL           | _           | 15        | mA    |         |

| "L" level average output current       | Iolav         | _           | 4         | mA    |         |

| "L" level total maximum output current | ΣΙοι          |             | 100       | mA    |         |

| "L" level total average output current | ΣΙοιαν        |             | 50        | mA    |         |

| "H" level maximum output current       | Іон           |             | -15       | mA    |         |

| "H" level average output current       | <b>І</b> онаv |             | -4        | mA    |         |

| "H" level total maximum output current | ΣІон          |             | -100      | mA    |         |

| "H" level total average output current | ΣΙομαν        |             | -50       | mA    |         |

| Power consumption                      | PD            |             | +600      | mW    |         |

| Operating temperature                  | TA            | 0           | +70       | °C    |         |

| Storage temperature                    | Tstg          | <b>–</b> 55 | +125      | °C    |         |

<sup>\*1:</sup> AVcc, AVRH and AVRL must not exceed Vcc.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>\*2:</sup> V<sub>I</sub> and V<sub>O</sub> must not exceed V<sub>CC</sub> + 0.3 V.

### 2. Recommended Operating Conditions

(AVss = Vss = 0.0 V)

| Parameter                | Symbol            | Va      | lue       | Unit | Remarks                     |

|--------------------------|-------------------|---------|-----------|------|-----------------------------|

| Parameter                | Symbol            | Min.    | Max.      | Unit | Remarks                     |

| Dower supply voltage     | Vcc               | 4.5     | 5.5       | V    | Normal operation            |

| Power supply voltage     | Vcc               | 3.0     | 5.5       | V    | Maintaining the stop status |

| (II III I I I I          | V <sub>IH1</sub>  | 0.7 Vcc | Vcc + 0.3 | V    | CMOS input                  |

|                          | VIH2              | 2.2     | Vcc + 0.3 | V    | TTL input                   |

| "H" level input voltage  | V <sub>IH1S</sub> | 0.8 Vcc | Vcc + 0.3 | V    | Hysteresis input            |

|                          | Vінм              | Vss-0.3 | Vcc + 0.3 | V    | MD0 to MD2                  |

|                          | VIL1              | Vss-0.3 | 0.3 Vcc   | V    | CMOS input                  |

| "I " lovel input veltage | VIL2              | Vss-0.3 | 0.8       | V    | TTL input                   |

| "L" level input voltage  | VIL1S             | Vss-0.3 | 0.2 Vcc   | V    | Hysteresis input            |

|                          | VILM              | Vss-0.3 | Vss + 0.3 | V    | MD0 to MD2                  |

| Operating temperature    | TA                | 0       | +70       | °C   |                             |

WARNING: Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

### 3. DC Characteristics

$(AVcc = Vcc = 5.0 V \pm 10\%, AVss = Vss = 0.0 V, T_A = 0^{\circ}C to +70^{\circ}C)$

| D                                 | 0                | <b>D</b> :              | 0 1111                                   |           | Value |      | 11   | D                                          |

|-----------------------------------|------------------|-------------------------|------------------------------------------|-----------|-------|------|------|--------------------------------------------|

| Parameter                         | Symbol           | Pin name                | Condition                                | Min.      | Тур.  | Max. | Unit | Remarks                                    |

| Vib input voltage                 | VID              | _                       | _                                        | 11.5      | _     | 12.5 | V    |                                            |

| "H" level output voltage          | Vон              | All ports except port 6 | Vcc = 4.5 V<br>Іон = -4.0 mA             | Vcc - 0.5 | _     | _    | V    |                                            |

| "L" level output voltage          | Vol              | All ports               | Vcc = 4.5 V<br>loL = 4.0 mA              | _         | _     | 0.4  | V    |                                            |

|                                   | I <sub>IH1</sub> | Except RST              | Vcc = 5.5 V<br>Vін = 0.7 Vcc             | _         | _     | -10  | μА   | CMOS<br>input                              |

| "H" level input<br>current        | I <sub>IH2</sub> | _                       | Vcc = 5.5 V<br>Vін = 2.2 Vcc             | _         | _     | -10  | μА   | TTL input                                  |

|                                   | Іінз             | _                       | Vcc = 5.5 V<br>Vін = 0.8 Vcc             | _         | _     | -10  | μΑ   | Hysteresis input                           |

|                                   | IIL1             | Except RST              | Vcc = 5.5 V<br>Vін = 0.3 Vcc             | _         | _     | 10   | μА   | CMOS<br>input                              |

| "L" level input<br>current        | I <sub>IL2</sub> | _                       | Vcc = 5.5 V<br>Vін = 0.8 Vcc             | _         | _     | 10   | μА   | TTL input                                  |

|                                   | Іігз             | _                       | Vcc = 5.5 V<br>ViH = 0.2 Vcc             | _         | _     | 10   | μА   | Hysteresis input                           |

| Pull-up resistor                  | RPULL            | RST                     | _                                        | 22        | _     | 110  | KΩ   |                                            |

|                                   | Icc1             | Vcc                     | CPU normal mode                          | _         | _     | 130  | mA   | Flash<br>memory<br>read state              |

| Power supply current*1            | lcc2             | Vcc                     | internal 20 MHz<br>operation             | _         | _     | 150  | mA   | Flash<br>memory<br>program/<br>erase state |

|                                   | Iccs             | Vcc                     | CPU sleep mode internal 20 MHz operation | _         | _     | 40   | mA   |                                            |

|                                   | Іссн             | Vcc                     | CPU stop mode T <sub>A</sub> = +25°C     | _         | _     | 100  | μА   |                                            |

| Input capacitance                 | Cin              | Other than<br>Vcc, Vss  |                                          | _         | 10    |      | pF   |                                            |

| Open-drain output leakage current | ILEAK            | Port 6                  | _                                        | _         |       | 10   | μА   |                                            |

| Low Vcc voltage*2                 | VLKO             | _                       |                                          | 3.2       | _     | 4.2  | V    |                                            |

<sup>\*1:</sup> Because the current values are tentative values, they are subject to change without notice due to our efforts to improve the characteristics of these devices.

<sup>\*2:</sup> To prevent improper commands from being activated during rise and fall of Vcc, the internal Vcc detection circuit of the flash memory allows only read accesses and ignores write accesses while Vcc is lower than VLKO.

## 4. Flash Memory Program/Erase Characteristics

$(AVcc = Vcc = 5.0 V \pm 10\%, AVss = Vss = 0.0 V, T_A = 0^{\circ}C to +70^{\circ}C)$

| Parameter           | Condition                                             |      | Value |       | Unit   | Remarks                                                   |

|---------------------|-------------------------------------------------------|------|-------|-------|--------|-----------------------------------------------------------|

| Parameter           | Condition                                             | Min. | Тур.  | Max.  | Offic  | Remarks                                                   |

| Sector erase time   | T <sub>A</sub> = +25°C,<br>Vcc = 5.0 V,               | _    | 1.5   | 13.5  | sec    | Except for the write time before internal erase operation |

| Chip erase time     | 100 cycles                                            | _    | _     | 27.0  | sec    | Except for the write time before internal erase operation |

| Byte program time   | _                                                     | _    | 16    | 1000* | μs     | Except for the over head time of the system               |

| Chip program time   | T <sub>A</sub> = +25°C,<br>Vcc = 5.0 V,<br>100 cycles | _    | 2.1   | 12.5  | sec    | Except for the over head time of the system               |

| Erase/program cycle | _                                                     | 100  | _     | _     | cycles |                                                           |

<sup>\*:</sup> The internal automatic algorithm continues operations for up to 48 ms, for each 1-byte writing operation.

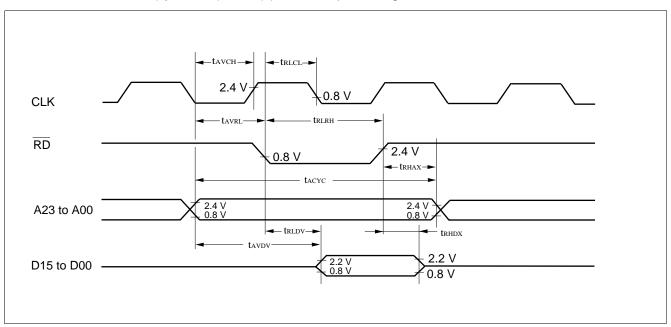

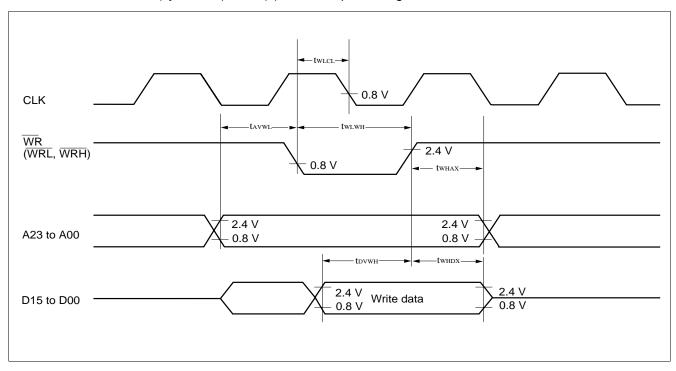

### 5. AC Characteristics

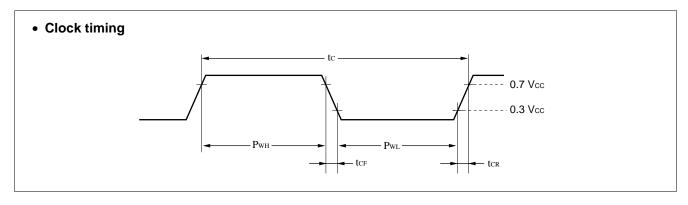

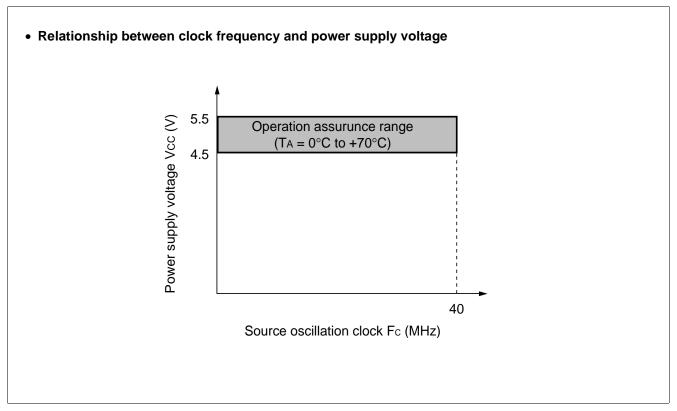

## (1) Clock Timing

$(AVss = Vss = 0.0 \text{ V}, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                       | Symbol Din  | Pin name     | Condition | Value        |      | Unit | Remarks |

|---------------------------------|-------------|--------------|-----------|--------------|------|------|---------|

| Parameter                       | Symbol      | riii iiaiiie | Condition | Min.         | Max. | Onit | Remarks |

| Clock frequency                 | Fc          | X0, X1       |           | _            | 40   | MHz  |         |

| Clock cycle time                | <b>t</b> c  | X0, X1       |           | <b>1/F</b> c | _    | ns   |         |

| Input clock pulse width         | Pwh,<br>PwL | X0           | _         | 10           | _    | ns   |         |

| Input clock rising/falling time | tcr,<br>tcf | X0           |           | _            | 8    | ns   |         |

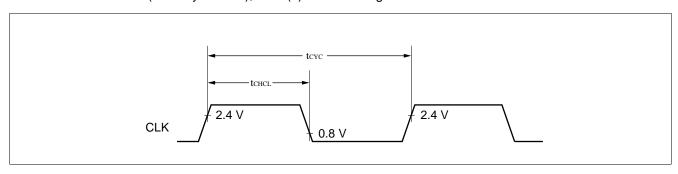

### (2) Clock Output Timing

$(AVcc = Vcc = 5.0 \text{ V} \pm 10\%, AVss = Vss = 0.0 \text{ V}, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                         | Symbol        | Pin name Con | Condition | Va            | lue           | Unit  | Remarks |

|-----------------------------------|---------------|--------------|-----------|---------------|---------------|-------|---------|

|                                   | Symbol        |              | Condition | Min.          | Max.          | Offic | Remarks |

| Cycle time                        | tcyc          | CLK          |           | 2 tc*         | _             | ns    |         |

| $CLK \uparrow \to CLK \downarrow$ | <b>t</b> CHCL | CLK          | _         | 1 tcyc/2 - 20 | 1 tcyc/2 + 20 | ns    |         |

<sup>\*:</sup> For information on tc (clock cycle time), see "(1) Clock Timing."

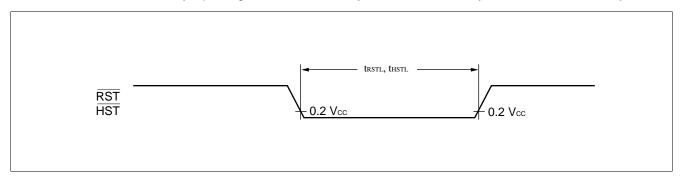

### (3) Reset and Hardware Standby Input

(AVcc = Vcc =  $5.0 \text{ V} \pm 10\%$ , AVss = Vss = 0.0 V, TA =  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ )

| Parameter                   | Symbol Pin name |               | Condition | Val             | lue  | Unit  | Remarks     |

|-----------------------------|-----------------|---------------|-----------|-----------------|------|-------|-------------|

| Parameter                   | Syllibol        | r III IIaiiie | Condition | Min.            | Max. | Oilit | IVellial KS |

| Reset input time            | <b>t</b> rstl   | RST           |           | 5 tcyc*         | _    | ns    |             |

| Hardware standby input time | <b>t</b> HSTL   | HST           | _         | 5 <b>t</b> cyc* | _    | ns    |             |

<sup>\*:</sup> For information on tcyc (cycle time), see "(2) Clock Output Timing."

Note: When hardware standby input is given, the machine cycle is simultaneously selected to be divide-by-32.

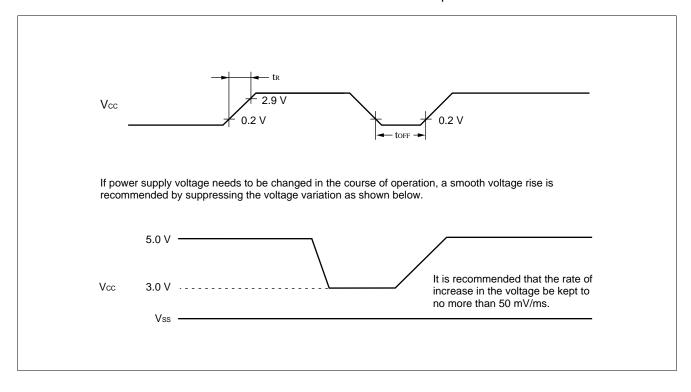

### (4) Power on Supply Specifications (Power-on Reset)

$(AVss = Vss = 0.0 \text{ V}, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                 | Symbol Pin name |             | Condition | Value |      | Unit | Remarks |  |

|---------------------------|-----------------|-------------|-----------|-------|------|------|---------|--|