# SECTION 3 MC68HC705C8 FUNCTIONAL DATA

The MC68HC705C8 microcontroller (MCU) is a member of the M68HC05 Family of low-cost, single-chip microcontrollers.

The HCMOS technology used on the MC68HC705C8 combines smaller size and higher speeds with the low power and high noise immunity of CMOS.

An additional advantage of CMOS is that circuitry is fully static. CMOS microcontrollers may be operated at any clock rate less than the guaranteed maximum. This feature may be used to conserve power since power consumption increases with higher clock frequencies. Static operation may also be advantageous during product development.

Two software-controlled power-saving modes, WAIT and STOP, are available to conserve additional power. These modes make the MC68HC705C8 especially attractive for automotive and battery-driven applications.

# 3.1 MCU DESCRIPTION

The hardware and software highlights of the MC68HC705C8 are as follows:

## **Hardware Features**

- HCMOS Technology

- 8-Bit Architecture

- Power-Saving Stop, Wait, and Data Retention Modes

- 24 Bidirectional I/O Lines

- 7 Input-Only Lines

- 2 Timer I/O Pins

- 2.1 MHz Internal Operating Frequency, 5 Volts; 1.0 MHz, 3 Volts

- Internal 16-Bit Timer

- Serial Communications Interface (SCI) System

- Serial Peripheral Interface (SPI) System

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-1

**■ 6367248 0149786 602 ■**

3-2

- Ultraviolet (UV) light EPROM or One-Time Programmable ROM (OTPROM)

- Selectable Memory Configurations

- Computer Operating Properly (COP) Watchdog System

- Clock Monitor

- On-Chip Bootstrap Firmware for Programming

- Software-Programmable External Interrupt Sensitivity

- External Pin, Timer, SCI, and SPI Interrupts

- Master Reset and Power-On Reset

- Single 3- to 6-Volt Supply (2-Volt Data Retention Mode)

- On-Chip Oscillator

- 40-Pin Dual-in-Line Package or

- 44-Lead PLCC (Plastic Leaded Chip Carrier) Package

## Software Features

- Upward Software Compatible with the M146805 CMOS Family

- Efficient Instruction Set

- Versatile Interrupt Handling

- True Bit Manipulation

- Addressing Modes with Indexed Addressing for Tables

- Memory-Mapped I/O

- Two Power-Saving Standby Modes

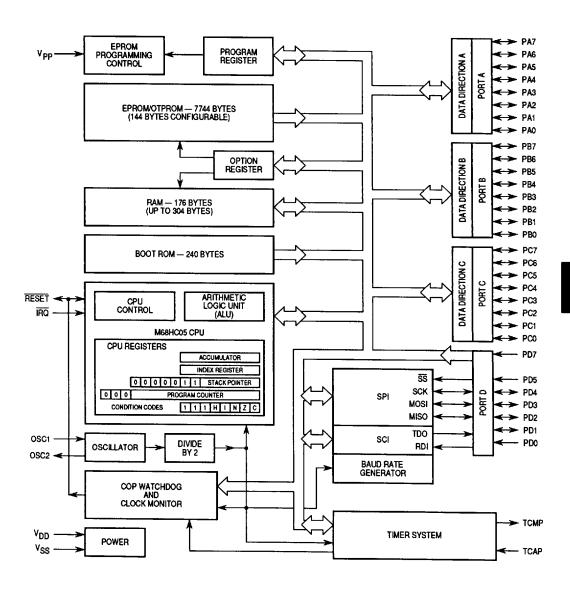

Figure 3-1 shows the MC68HC705C8 MCU block diagram.

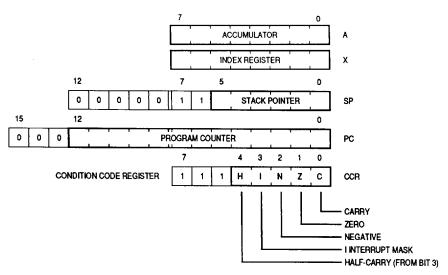

The central processor unit (CPU) contains the 8-bit arithmetic logic unit, accumulator, index register, condition code register, stack pointer, program counter, and CPU control logic.

Major peripheral functions are provided on-chip. On-chip memory systems include bootstrap read-only memory (ROM), programmable ROM (EPROM or OTPROM), and random-access memory (RAM).

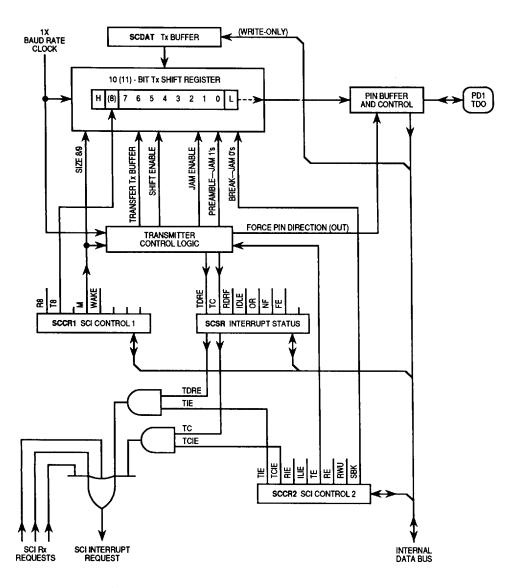

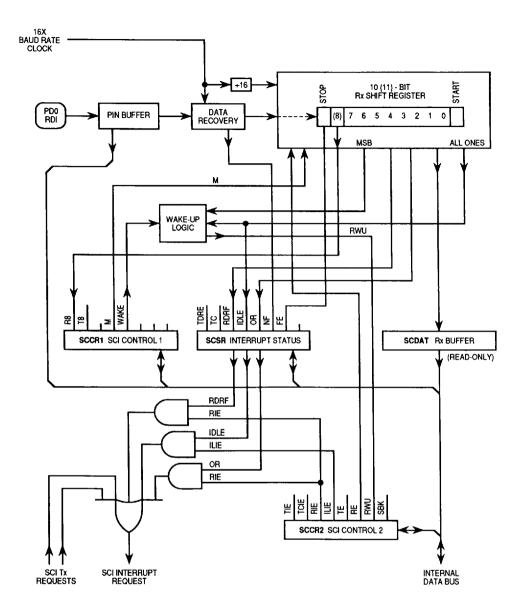

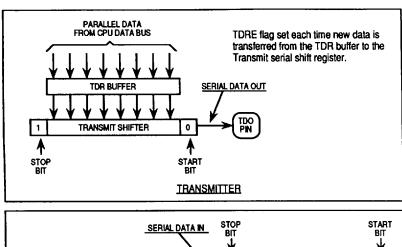

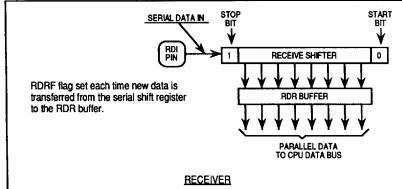

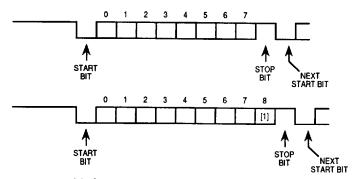

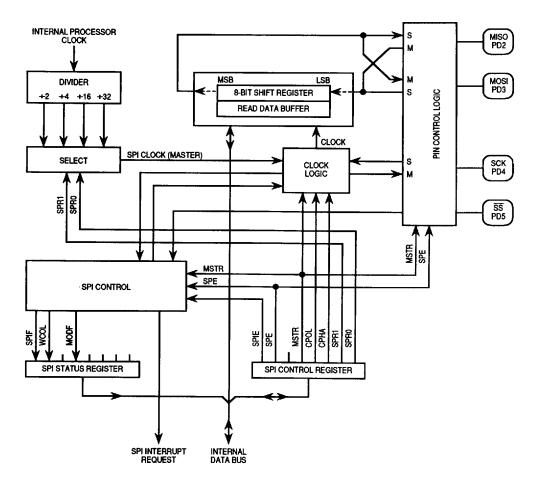

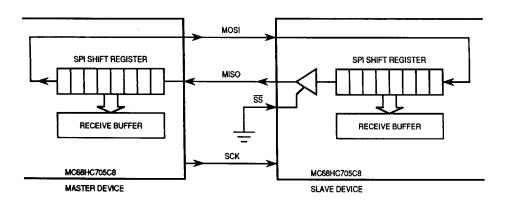

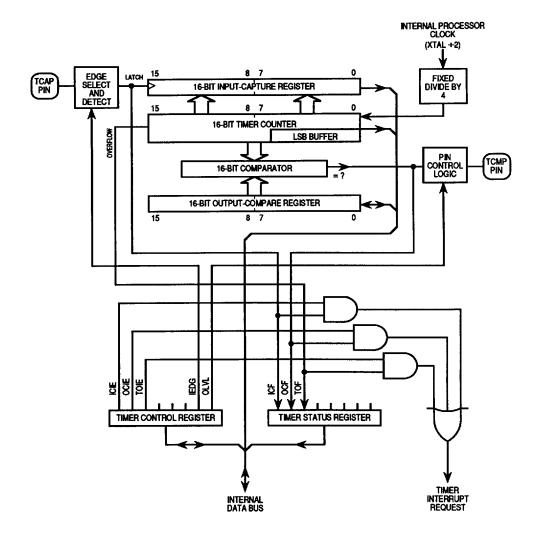

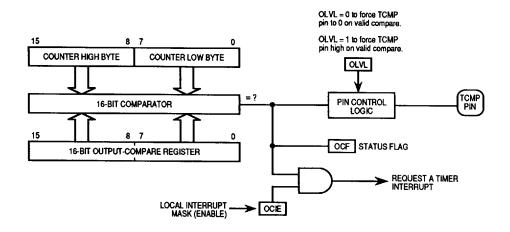

On-chip I/O devices include an asynchronous serial communications interface (SCI), a separate serial peripheral interface (SPI), and a 16-bit programmable timer system.

Self-monitoring circuitry is included on-chip to protect against system errors. A computer operating properly (COP) watchdog system protects against software failures. A clock monitor system generates a system reset if the clock is lost or runs too slow. An illegal opcode detection circuit provides a non-maskable interrupt if an illegal opcode is detected.

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0149787 549 **■**

Figure 3-1. MC68HC705C8 Microcontroller Block Diagram

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-3

**■** 6367248 D149788 485 ■

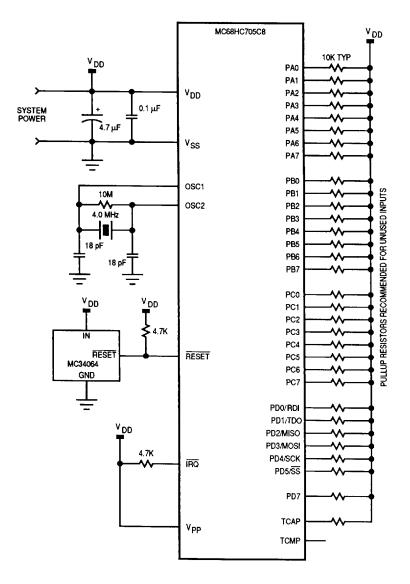

## 3.2 PINS AND CONNECTIONS

The following paragraphs discuss the MCU pin assignments, pin functions, and basic connections.

Because the MC68HC705C8 is a CMOS device, unused input pins must be terminated to avoid oscillation, noise, and added supply current. The preferred method of terminating pins that can be configured for input or output is with individual pullup or pulldown resistors for each unused pin.

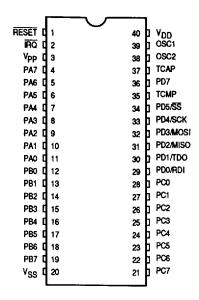

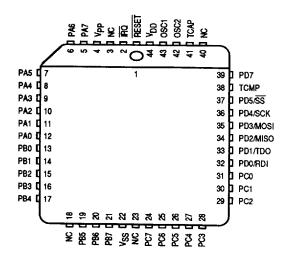

Pin assignments are shown in Figure 3-2. Mechanical data and ordering information can be found in BR594/D, the *MC68HC705C8 Technical Summary*, available separately.

# 3.2.1 Pin Functions

# V<sub>DD</sub> and V<sub>SS</sub>

Power is supplied to the MCU using these two pins. V<sub>DD</sub> is power and V<sub>SS</sub> is ground. The MCU can operate from a single 5-volt (nominal) power supply.

# Vpp

3-4

The Vpp pin is used when programming the one-time programmable ROM (OTPROM) or EPROM. Programming voltage (14.75 Vdc) is applied to this pin when programming the PROM. Normally, this pin is connected to VDD.

#### CAUTION

Do not connect Vpp pin to VSS (GND). It will damage the MCU.

# **IRQ** (Maskable Interrupt Request)

IRQ is a software programmable option which provides two different choices of interrupt triggering sensitivity. These options are 1) negative edge-sensitive triggering only, or 2) both negative edge-sensitive and level-sensitive triggering.

In the latter case, either a negative edge or a low level input to the  $\overline{IRQ}$  pin will produce an interrupt. The MCU completes the current instruction before it responds to the interrupt request. When the  $\overline{IRQ}$  pin goes low, a

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0149789 311 **■**

40-Pin Dual-In-Line Package

44-Lead PLCC Package

Figure 3-2. Pin Assignments

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-5

■ 6367248 0149790 033 ■

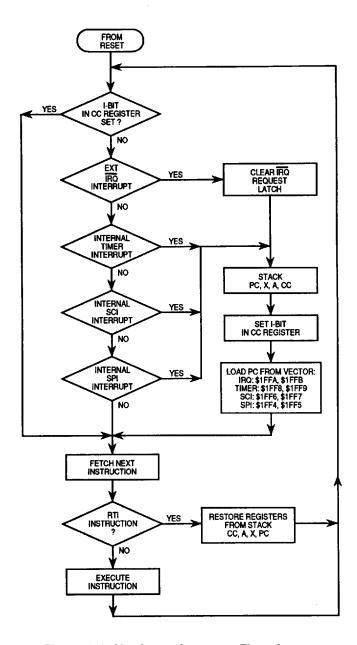

small synchronization delay occurs, and a logic one is latched internally to signify an interrupt has been requested. When the MCU completes its current instruction, the interrupt latch is tested. If the interrupt latch contains a logic one and the interrupt mask bit (I bit) in the condition code register is clear, the MCU then begins the interrupt sequence.

If the option is selected to include level-sensitive triggering, then the  $\overline{IRQ}$  input requires an external resistor to  $V_{DD}$  for "wired-OR" operation. See **3.4.7 Interrupts** for more detail concerning interrupts.

#### RESET

The RESET pin is an active-low bidirectional control signal. As an input, the RESET pin initializes the MCU to a known startup state. As an opendrain output, the RESET pin indicates an internal MCU failure detected by the computer operating properly (COP) watchdog timer or clock monitor circuitry.

This RESET pin is significantly different from the RESET signal used on other Motorola M68HC05 Family devices. Refer to **3.4.4 Resets** and **3.4.7 Interrupts** before designing circuitry to generate or monitor the RESET signal.

#### **TCAP**

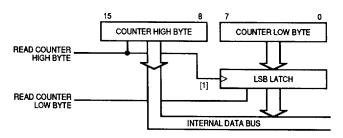

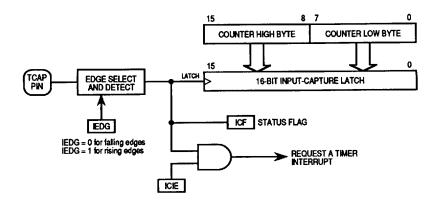

The TCAP pin provides the input to the input-capture feature for the onchip programmable timer system. Refer to input-capture register in 3.8 PROGRAMMABLE TIMER.

#### **TCMP**

3-6

The TCMP pin provides an output for the output-compare feature of the on-chip timer system. Refer to output-compare register in **3.8 PROGRAMM-ABLE TIMER**.

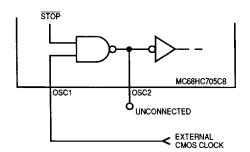

#### OSC1,OSC2

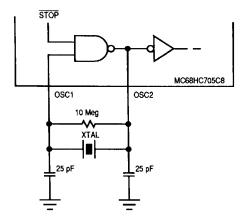

The MC68HC705C8 can accept either a crystal, ceramic resonator, or external input to control the internal oscillator. The internal processor clock is derived by dividing the oscillator frequency (fosc) by two.

The circuit shown in Figure 3-3(a) is recommended when using a crystal. The internal oscillator is designed to interface with an AT-cut parallel resonant quartz crystal or a ceramic resonator up to 4 MHz. The crystal and components should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time.

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

🖿 6367248 Ol4979l T7T 🖿

(a) Crystal/Ceramic Resonator Oscillator Connections

(b) External Clock Source Connections

Figure 3-3. Oscillator Connections

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-7

3-8

A ceramic resonator may be used in place of the crystal in cost-sensitive applications. The circuit in Figure 3-3(a) is recommended when using a ceramic resonator or a crystal. The manufacturer of the particular ceramic resonator being considered should be consulted for specific information.

An external clock may be applied to the OSC1 input with the OSC2 pin not connected, as shown in Figure 3-3(b).

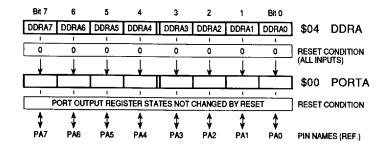

## PA7-PA0

These eight I/O lines comprise port A. Each port A pin can be software programmed to act as an input or output.

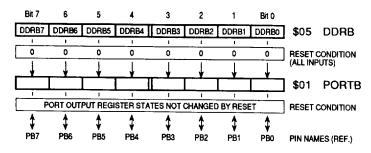

#### PB7-PB0

These eight lines comprise port B. Each port B pin can be software programmed to act as an input or output.

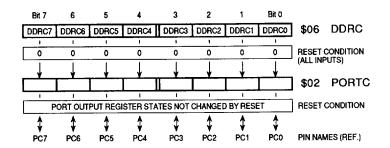

## PC7-PC0

These eight lines comprise port C. Each port C pin can be software programmed to act as an input or output.

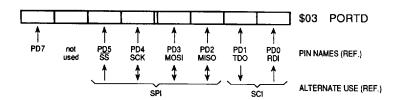

## PD5-PD0, PD7

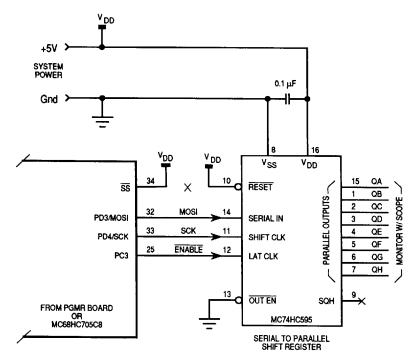

These seven lines comprise port D. During power-on or reset, these seven pins are configured as inputs. When the SPI system is enabled, four of these lines, MISO/PD2, MOSI/PD3, SCK/PD4, and SS/PD5, are used by the SPI system. When the SCI receiver is enabled, the PD0/RDI pin becomes the receive data input to the SCI. When the SCI transmitter is enabled, the PD1/TD0 pin becomes the transmit data output for the SCI.

# 3.2.2 Typical Basic Connections

There are MCU basic connections that can be used as the starting point for any application to minimize the time required to create a prototype system.

Figure 3-4 is the schematic diagram for a simple MC68HC705C8 system. This circuit can be used as the basis for any MC68HC705C8 application. In most cases, the circuitry for the power supply and oscillator can be used as shown in this diagram. All unused inputs are terminated in an appropriate manner.

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0149793 842 **■**

Figure 3-4. Typical Basic Connections

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-9

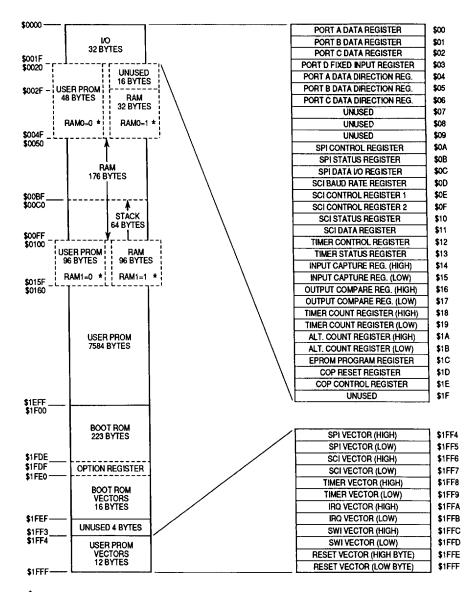

## 3.3 ON-CHIP MEMORY

The MC68HC705C8 memory includes 176 to 304 bytes of random-access memory (RAM), 240 bytes of read-only memory (ROM), and 7600 to 7744 bytes of programmable memory (EPROM or OTPROM).

# 3.3.1 Memory Types

RAM means that any word in the memory may be accessed without having to go through all the other words to get to it. RAM is a volatile form of memory in that all the memory content is lost when the power is removed from the chip. RAM contents may be retained by keeping at least 2 volts on VDD. Power requirements in this standby mode are very small.

ROM is very similar to RAM except, unlike RAM, it is not possible to change the contents of ROM after it is manufactured. This type memory is useful only for storage of information or programs.

The special bootstrap mode allows programs to be downloaded through the on-chip serial communications interface (SCI) into internal RAM to be executed. The bootloaded program is used for a variety of tasks such as loading calibration values into internal EPROM or performing diagnostics on a finished module.

The MC68HC705C8 on-chip ROM is called the bootloader ROM. This ROM controls the loading process of the special bootstrap mode.

Erasable programmable ROM (EPROM) is nonvolatile memory that can be programmed in the field by the user. Nonvolatile memories retain their contents even when no power is applied. Once it has been programmed, the EPROM cannot be written into, but it can be read from as many times as necessary. However, EPROM can be erased by ultraviolet light and reprogrammed.

OTPROM is the same as EPROM except it can be programmed only once and cannot be erased.

# 3.3.2 Memory Map

3-10

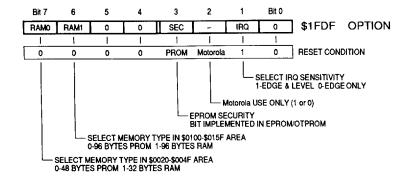

The MC68HC705C8 MCU contains four selectable memory configurations as shown in Figure 3-5. The memory configurations are accessed via the option

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0149795 615 **■**

<sup>\*</sup> Refer to 3.10.4 OPTION REGISTER for an explanation of software-selectable memory configurations.

Figure 3-5. MC68HC705C8 Memory Map

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-11

register (\$1FDF) RAM0 and RAM1 bits. During reset, the RAM0 and RAM1 control bits are forced to 0. RAM0 and RAM1 bit states determine the amount of RAM and PROM, which can be selected as follows:

| RAM0 | RAM1 | RAM Bytes | PROM Bytes |

|------|------|-----------|------------|

| 0    | 0    | 176       | 7744       |

| 1    | 0    | 208       | 7696       |

| 0    | 1    | 272       | 7648       |

| 1    | 1    | 304       | 7600       |

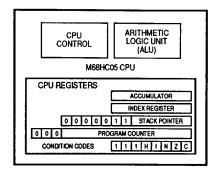

## 3.4 CENTRAL PROCESSOR UNIT

The MC68HC705C8 CPU is responsible for executing all software instructions in their programmed sequence for a specific application.

The CPU block diagram is shown in Figure 3-6.

Figure 3-6. M68HC05 CPU Block Diagram

# 3.4.1 Registers

The CPU contains five registers as shown in Figure 3-7. Registers in the CPU are memories inside the microprocessor (not part of the memory map).

#### Accumulator (A)

The accumulator is an 8-bit general-purpose register used to hold operands, results of the arithmetic calculations, and data manipulations. It is also directly accessible to the CPU for nonarithmetic operations. The accumulator is used during the execution of a program when the contents

3-12 M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0349797 498 **■**

Figure 3-7. Programming Model

of some memory location are loaded into the accumulator. Also, the store instruction causes the contents of the accumulator to be stored at some prescribed memory location.

# Index Register (X)

The index register is used for indexed modes of addressing or may be used as an auxiliary accumulator. This 8-bit register can be loaded either directly or from memory, have its contents stored in memory, or its contents can be compared to memory.

In indexed instructions, the X register provides an 8-bit value that is added to an instruction-provided value to create an effective address. The instruction-provided value can be 0, 1, or 2 bytes long.

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-13

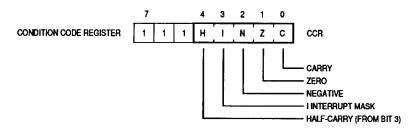

# **Condition Code Register (CCR)**

The condition code register contains five status indicators that reflect the results of arithmetic and other operations of the CPU. The five flags are half-carry (H), negative (N), zero (Z), overflow (V), and carry/borrow (C).

Half-Carry Bit (H) — The half-carry flag is used for binary-coded decimal (BCD) arithmetic operations and is affected by the ADD or ADC addition instructions. The H bit is set to a one when a carry occurs between bits 3 and 4.

**Interrupt Mask Bit (I)** — The interrupt mask bit disables all maskable interrupt sources when the I bit is set. Clearing this bit enables the interrupts. When any interrupt occurs, the I bit is automatically set after the registers are stacked but before the interrupt vector is fetched.

If an external interrupt occurs while the I bit is set, the interrupt is latched and processed after the I bit is cleared; therefore, no interrupts from the IRQ pin are lost because of the I bit being set.

After an interrupt has been serviced, a return from interrupt (RTI) instruction causes the registers to be restored to their previous values. Normally, the I bit would be zero after an RTI was executed. After any reset, I is set and can only be cleared by a software instruction.

**Negative (N)** — The N bit is set to one when the result of the last arithmetic, logical, or data manipulation is negative (bit 7 of the MSB in the result is a logic one).

The N bit has other uses. By assigning an often-tested flag bit to the MSB of a register or memory location, you can test this bit simply by loading the accumulator with the contents of that location.

3-14

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 D149799 260 **■**

**Zero (Z)** — The Z bit is set to one when the result of the last arithmetic, logical, or data manipulation is zero.

**Carry/Borrow (C)** — The C bit is used to indicate whether or not there was a carry from an addition or a borrow as a result of a subtraction. Shift and rotate instructions operate with and through the carry bit to facilitate multiple word shift operations. This bit is also affected during bit test and branch instructions.

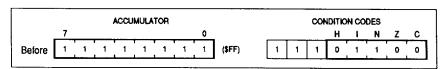

The following illustration is an example of the way condition code bits are affected by arithmetic operations.

#### Assume Initial Values in Accumulator and Condition Codes:

Execute the Following Instruction:

---- AB 02 ADD #2

Add 2 to Accumulator

Condition Codes and Accumulator Reflect the Results of the Add Instruction:

- H- Set because there was a carry from bit 3 to bit 4 of the accumulator.

- I No change.

- N- Clear because result is not negative (bit 7 of accumulator is 0).

- Z- Clear because result is not zero.

- C Set because there was a carry out of bit 7 of the accumulator.

The H bit is not useful after this operation because the accumulator was not a valid BCD value before the operation.

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-15

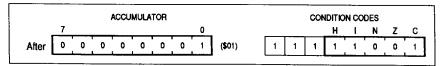

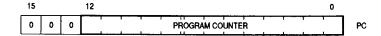

# **Program Counter (PC)**

The program counter is a 13-bit register that contains the address of the next instruction or instruction operand to be fetched by the processor.

Normally, the program counter advances one memory location at a time as instructions and instruction operands are fetched.

Jump, branch, and interrupt operations cause the program counter to be loaded with a memory address other than that of the next sequential location.

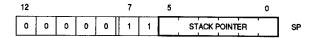

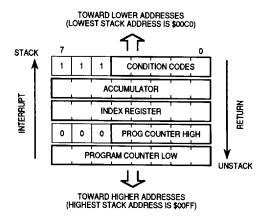

## Stack Pointer (SP)

The stack pointer is a 13-bit register that contains the address of the next free location on the stack. During an MCU reset or the reset stack pointer (RSP) instruction, the stack pointer is set to location \$00FF. The stack pointer is then decremented as data is pushed onto the stack and incremented as data is pulled from the stack.

When accessing memory, the seven MSBs of the SP are permanently set to 0000011. These seven bits are appended to the six LSB bits to produce an address within the range of \$00FF to \$00CO. Subroutines and interrupts may use up to 64 (decimal) locations. If 64 locations are exceeded, the stack pointer wraps around and loses the previously stored information. A subroutine call occupies two locations on the stack; an interrupt uses five locations.

3-16

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

# 3.4.2 Arithmetic/Logic Unit (ALU)

The arithmetic/logic unit (ALU) is used to perform the arithmetic and logical operations defined by the instruction set.

The various binary arithmetic operations circuits decode the instruction in the instruction register and set up the ALU for the desired function. Most binary arithmetic is based on the addition algorithm, and subtraction is carried out as negative addition. Multiplication is not performed as a discrete instruction but as a chain of addition and shift operations within the ALU under control of CPU control logic. The multiply instruction (MUL) requires 11 internal processor cycles to complete this chain of operations.

## 3.4.3 CPU Control

The CPU control circuitry sequences the logic elements of the ALU to carry out the required operations.

## 3.4.4 Resets

Reset is used to force the MCU system to a known starting address. Peripheral systems and many control and status bits are also forced to a known state as a result of reset.

The following four conditions can cause reset in the MC68HC705C8 MCU:

- 1) External, active-low input signal on the RESET pin.

- 2) Internal power-on reset (POR) condition.

- 3) Internal computer operating properly (COP) watchdog system reset condition.

- 4) Internal clock monitor reset condition.

- **3.4.4.1 POWER-ON RESET.** The power-on reset occurs when a positive transition is detected on V<sub>DD</sub>. The power-on reset is used strictly for power turn-on conditions and should not be used to detect any drops in the power supply voltage. There is no provision for a power-down reset.

The power-on circuitry provides for a 4064 cycle delay from the time that the oscillator becomes active. If the external RESET pin is low at the end of the 4064 delay timeout, the processor remains in the reset condition until RESET goes high.

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-17

**6367248 0149802 685**

The following internal actions occur as the result of any MCU reset:

- 1) All data direction registers are cleared to zero (input).

- 2) Stack pointer configured to \$00FF.

- 3) I bit in the condition code register to logic one.

- 4) External interrupt latch cleared.

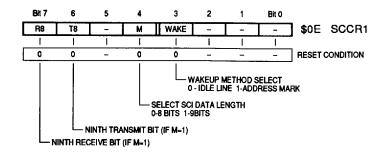

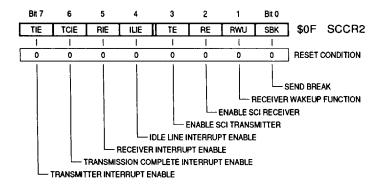

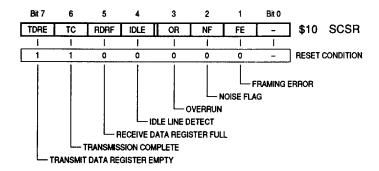

- 5) SCI disabled (serial control bits TE = 0 and RE = 0). Other SCI bits cleared by reset include: TIE, TCIE, RIE, ILIE, RWU, SBK, RDRF, IDLE, OR, NF, and FE.

- 6) Serial status bits TDRE and TC set.

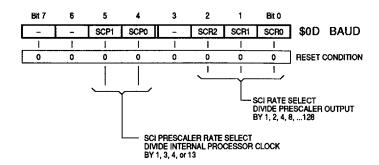

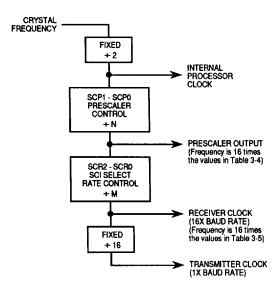

- 7) SCI prescaler and rate control bits SCP0, SCP1 cleared.

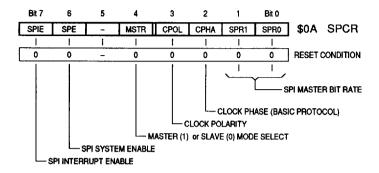

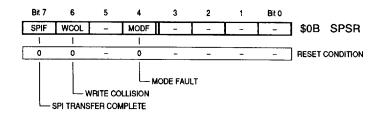

- 8) SPI disable (serial output enable control bit SPE = 0). Other SPI bits cleared by reset include: SPIE, MSTR, SPIF, WCOL, and MODF.

- 9) All serial interrupt enable bits cleared (SPIE, TIE, and TCIE).

- 10) SPI system configured as slave (MSTR = 0).

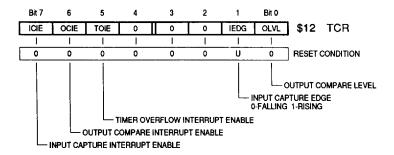

- 11) Timer prescaler reset to zero state.

Timer counter configured to \$FFFC.

Timer output compare (TCMP) bit reset to zero.

All timer interrupt enable bits cleared (ICIE, OCIE, and TOIE) to disable timer interrupts.

The OLVL timer bit is also cleared by reset.

- 12) STOP latch cleared.

- 13) WAIT latch cleared.

- 14) Internal address bus forced to restart vector (on exit from reset, upper byte of program counter is loaded from \$1FFE, and lower byte of program counter is loaded from \$1FFF).

- 3.4.4.2 COMPUTER OPERATING PROPERLY (COP) WATCHDOG TIMER RESET. The COP watchdog timer system is intended to detect software errors. When the COP is being used, software is responsible for keeping a free-running watchdog timer from timing out. If the watchdog timer times out, it is an indication that software is no longer being executed in the intended sequence; thus, a system reset is initiated.

3-18

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

Since the COP timer relies on the internal bus clock in order to detect a software failure, a clock monitor is also included to guard against a failure of the clock. When the COP timer is enabled, the clock monitor should also be enabled since the COP timer cannot detect failures of the internal bus clock.

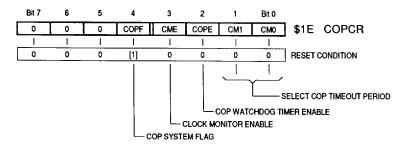

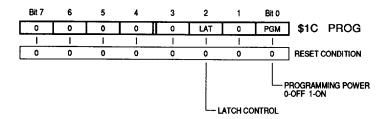

The COP control register (\$1E), as shown below, is used to control the COP watchdog timer and clock monitor functions.

[1] - Cleared on external or POR reset, set on COP or clock monitor fail resets.

COPF — Computer Operating Properly Flag

- 1 = COP or clock monitor reset has occurred

- 0 = No COP or clock monitor reset has occurred Reading the COP control register clears COPF.

CME — Clock Monitor Enable

- 1 = Clock monitor enabled

- 0 = Clock monitor disabled

CME is readable and writable at any time.

COPE — Computer Operating Properly Enable

- 1 = COP timeout enabled

- 0 = COP timeout disabled

CM1, CM0 — Computer Operating Properly Mode

These two bits are used to select the COP watchdog timeout period (see Table 3-1).

The actual timeout period is dependent on the system bus clock frequency, but, for reference purposes, Table 3-1 shows the relationship between the CM1 and CM0 select bits and the COP timeout period for various system

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-19

**■** 6367248 0149804 458 **■**

3-20

Table 3-1. COP Timeout Period versus CM1 and CM0

| CM1 | СМО | E/2 <sup>15</sup><br>Div.<br>By | XTAL = 4.0 MHz<br>E = 2.0 MHz<br>Timeout | XTAL = 3.5796<br>E = 1.7897 MHZ<br>Timeout | XTAL = 2.0 MHz<br>E = 1.0 MHz<br>Timeout | XTAL = 1.0 MHz<br>E = 0.5 MHz<br>Timeout |

|-----|-----|---------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|

| 0   | 0   | 1                               | 16.38 ms                                 | 18.31 ms                                   | 32.77 ms                                 | 65.54 ms                                 |

| 0   | 1   | 4                               | 65.54 ms                                 | 73.24 ms                                   | 131.07 ms                                | 262.14 ms                                |

| 1   | 0   | 16                              | 262.14 ms                                | 292.95 ms                                  | 524.29 ms                                | 1.048 s                                  |

| 1   | 1   | 64                              | 1.048 s                                  | 1.172 s                                    | 2.097 s                                  | 4.194 s                                  |

clock frequencies ("E" stands for the system bus clock). The default reset condition of the COP mode bits (CM1 and CM0) is cleared, which corresponds to the shortest timeout period.

The COP reset register (\$1D) is used to keep the COP watchdog timer from timing out.

| Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |            |

|-------|---|---|---|---|---|---|-------|------------|

|       |   |   |   |   |   |   |       | \$1D COPRR |

The sequence required to reset the COP watchdog timer is:

- 1) Write \$55 to the COP reset register at location \$1D.

- 2) Write \$AA to the same address location.

Both write operations must occur in the correct order prior to timeout, but any number of instructions may be executed between the two write operations. The elapsed time between adjacent software reset sequences must never be greater than the COP timeout period.

Upon detection of a timeout condition, the COP watchdog timer (if enabled by COPE = 1) will cause a system reset to be generated. This reset is issued to the external system via the bidirectional RESET pin for four bus cycles.

**3.4.4.3 CLOCK MONITOR RESET.** When a clock failure is detected by the clock monitor (and CME = 1), a system reset will be generated.

When CME is set, the clock monitor detects the absence of the internal bus clock for more than a certain period of time. When CME is cleared, the clock monitor is disabled. The timeout period is dependent on processing parameters and will be between 5 and 100  $\mu s$ . Thus, a bus clock rate of 200 kHz or more will never cause a clock monitor failure, and a bus clock rate of 10 kHz or less will definitely cause a clock monitor reset.

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

MOTOROLA

**■** 6367248 0149805 394 **■**

A clock monitor reset is issued to the external system via the bidirectional RESET pin for four bus cycles. The clock monitor does not have a separate reset vector.

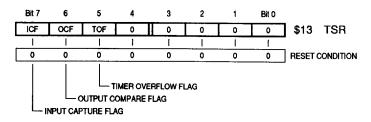

Special considerations are needed when using the STOP instruction with the clock monitor. Since the STOP instruction causes the clocks to be halted, the clock monitor will generate a reset sequence (if enabled by CME = 1) at the time the STOP instruction is entered.

# 3.4.5 Addressing Modes

The power of any computer lies in its ability to access memory. The addressing modes of the CPU provide that capability. The addressing modes define the manner in which an instruction is to obtain the data required for its execution. Because of different addressing modes, an instruction may access the operand in one of up to six different ways. In this manner, the addressing modes expand the basic 62 M68HC05 Family instructions into 210 distinct opcodes.

The M68HC05 addressing modes that are used to reference memory are inherent, immediate, extended, direct, indexed (no offset, 8-bit offset, and 16-bit offset), and relative. One- and two-byte direct addressing instructions access all data bytes in most applications. Extended addressing uses three-byte instructions to reach data anywhere in memory space. The various addressing modes make it possible to locate data tables, code conversion tables, and scaling tables anywhere in the memory space. Short indexed accesses are single-byte instructions; whereas, the longest instructions (three bytes) permit accessing tables anywhere in memory.

A general description and examples of the various modes of addressing are provided in the following paragraphs. The term effective address (EA) is used to indicate the memory address where the argument for an instruction is fetched or stored. More details on addressing modes and a description of each instruction is available in Appendix A.

The information provided in the program assembly examples uses several symbols to identify the various types of numbers that occur in a program. These symbols include:

- 1. A blank or no symbol indicates a decimal number.

- 2. A \$ immediately preceding a number indicates it is a hexadecimal number; e.g., \$24 is 24 in hexadecimal or the equivalent of 36 in decimal.

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-21

**■ 6367248 0149806 220 ■**

3. A # indicates immediate operand and the number is found in the location following the opcode. A variety of symbols and expressions can be used following the character # sign. Since not all assemblers use the same syntax rules and special characters, refer to the documentation for the particular assembler that will be used.

| Prefix | Definition             |

|--------|------------------------|

| None   | Decimal                |

| \$     | Hexadecimal            |

| (a     | Octal                  |

| %      | Binary                 |

| ,      | Single ASCII Character |

For each addressing mode, an example instruction is explained in detail. These explanations describe what happens in the CPU during each processor clock cycle of the instruction. Numbers in square brackets [ ] refer to a specific CPU clock cycle.

3.4.5.1 INHERENT ADDRESSING MODE. In inherent addressing mode, all information required for the operation is already inherently known to the CPU, and no external operand from memory or from the program is needed. The operands (if any) are only the index register and accumulator. These are always one byte instructions.

# **Example Program Listing:**

0200 4c

INCA

Increment accumulator

#### **Execution Sequence:**

\$0200 \$4C [1], [2], [3]

# Explanation:

- [1] CPU reads opcode \$4C increment accumulator

- [2], [3] CPU reads accumulator value, adds one to it, stores the new value in the accumulator, and adjusts condition code flag bits as necessary.

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

3-22

The following is a list of all M68HC05 instructions that can use the inherent addressing mode.

| Instruction                            | Mnemonic   |

|----------------------------------------|------------|

| Arithmetic Shift Left                  | ASLA, ASLX |

| Arithmetic Shift Right                 | ASRA, ASRX |

| Clear Carry Bit                        | CLC        |

| Clear Interrupt Mask Bit               | CLI        |

| Clear                                  | CLRA, CLRX |

| Complement                             | COMA, COMX |

| Decrement                              | DECA, DECX |

| Increment                              | INCA, INCX |

| Logical Shift Left                     | LSLA, LSLX |

| Logical Shift Right                    | LSRA, LSRX |

| Multiply                               | MUL        |

| Negate                                 | NEGA, NEGX |

| No Operation                           | NOP        |

| Rotate Left thru Carry                 | ROLA, ROLX |

| Rotate Right thru Carry                | RORA, RORX |

| Reset Stack Pointer                    | RSP        |

| Return from Interrupt                  | RTI        |

| Return from Subroutine                 | RTS        |

| Set Carry Bit                          | SEC        |

| Set Interrupt Mask Bit                 | SEI        |

| Enable IRQ, Stop Oscillator            | STOP       |

| Software Interrupt                     | SWI        |

| Transfer Accumulator to Index Register | TAX        |

| Test for Negative or Zero              | TSTA, TSTX |

| Transfer Index Register to Accumulator | TXA        |

| Enable Interrupt, Halt Processor       | WAIT       |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-23

3-24

3.4.5.2 IMMEDIATE ADDRESSING MODE. In the immediate addressing mode, the operand is contained in the byte immediately following the opcode. This mode is used to hold a value or constant which is known at the time the program is written and which is not changed during program execution. These are two-byte instructions, one for the opcode and one for the immediate data byte.

# Example Program Listing:

0200 a6 02 LDA #\$02 Load accumulator w/ immediate value

# Execution Sequence:

| \$0200 | \$A6 | [1] |

|--------|------|-----|

| \$0201 | \$02 | [2] |

# **Explanation:**

- [1] CPU reads opcode \$A6 load accumulator with the value immediately following the opcode.

- [2] CPU then reads the immediate data \$02 from location \$0201 and loads \$02 into the accumulator.

The following is a list of all M68HC05 instructions that can use the immediate addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Bit Test Memory with Accumulator     | BIT      |

| Compare Accumulator with Memory      | CMP      |

| Compare Index Register with Memory   | CPX      |

| Exclusive OR Memory with Accumulator | EOR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Inclusive OR                         | ORA      |

| Subtract with Carry                  | SBC      |

| Subtract                             | SUB      |

|                                      |          |

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

■ TET PO8P4G 8457248 ■■

3.4.5.3 EXTENDED ADDRESSING MODE. In the extended addressing mode, the address of the operand is contained in the two bytes following the opcode. Extended addressing references any location in the MCU memory space including I/O, RAM, ROM, and EPROM. Extended addressing mode instructions are three bytes, one for the opcode and two for the address of the operand.

# Example Program Listing:

0200 c6 06 e5 LDA \$06E5 Load accumulator from extended addr

## **Execution Sequence:**

\$0200 \$C6 [1] \$0201 \$06 [2] \$0202 \$E5 [3] and [4]

## Explanation:

- [1] CPU reads opcode \$C6 load accumulator using extended addressing mode.

- [2] CPU then reads \$06 from location \$0201. This \$06 is interpreted as the high-order half of an address.

- [3] CPU then reads \$E5 from location \$0202. This \$E5 is interpreted as the low-order half of an address.

- [4] CPU internally appends \$06 to the \$E5 read to form the complete address (\$06E5). The CPU then reads whatever value is contained in the location \$06E5 into the accumulator.

The following is a list of all M68HC05 instructions that can use the extended addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Bit Test Memory with Accumulator     | BIT      |

| Compare Acumulator with Memory       | CMP      |

| Compare Index Register with Memory   | CPX      |

| Exclusive OR Memory with Accumulator | EOR      |

| Jump                                 | JMP      |

| Jump to Subroutine                   | JSR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Inclusive OR                         | ORA      |

| Subtract with Carry                  | SBC      |

| Store Accumulator in Memory          | STA      |

| Store Index Register in Memory       | STX      |

| Subtract                             | SUB      |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-25

**■** 6367248 0149810 751 **■**

3.4.5.4 DIRECT ADDRESSING MODE. The direct addressing mode is similar to the extended addressing mode except the upper byte of the operand address is assumed to be \$00. Thus, only the lower byte of the operand address needs to be included in the instruction. Direct addressing allows you to efficiently address the lowest 256 bytes in memory. This area of memory is called the direct page and includes on-chip RAM and I/O registers. Direct addressing is efficient in both memory and time. Direct addressing mode instructions are usually two bytes, one for the opcode and one for the low-order byte of the operand address.

# **Example Program Listing:**

0200 b6 50 LDA \$50 Load accumulator from direct address

## **Execution Sequence:**

\$0200 \$B6 [1] \$0201 \$50 [2] and [3]

## Explanation:

- [1] CPU reads opcode \$B6 load accumulator using direct addressing mode.

- [2] CPU then reads \$50 from location \$0201. This \$50 is interpreted as the low-order half of an address. In direct addressing mode, the high-order half of the address is assumed to be \$00.

- [3] CPU internally appends \$00 to the \$50 read in the second cycle to form the complete address (\$0050). The CPU then reads whatever value is contained in the location \$0050 into the accumulator.

3-26

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

The following is a list of all M68HC05 instructions that can use the direct addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Arithmetic Shift Left                | ASL      |

| Arithmetic Shift Right               | ASR      |

| Clear Bit in Memory                  | BCLR     |

| Bit Test Memory with Accumulator     | BIT      |

| Branch if Bit n is Clear             | BRCLR    |

| Branch if Bit n is Set               | BRSET    |

| Set Bit in Memory                    | BSET     |

| Clear                                | CLR      |

| Compare Accumulator with Memory      | CMP      |

| Complement                           | COM      |

| Compare Index Register with Memory   | CPX      |

| Decrement                            | DEC      |

| Exclusive OR Memory with Accumulator | EOR      |

| Increment                            | INC      |

| Jump                                 | JMP      |

| Jump to Subroutine                   | JSR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Logical Shift Left                   | LSL      |

| Logical Shift Right                  | LSR      |

| Negate                               | NEG      |

| Inclusive OR                         | ORA      |

| Rotate Left thru Carry               | ROL      |

| Rotate Right thru Carry              | ROR      |

| Subtract with Carry                  | SBC      |

| Store Accumulator in Memory          | STA      |

| Store Index Register in Memory       | STX      |

| Subtract                             | SUB      |

| Test for Negative or Zero            | TST      |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-27

**■** 6367248 0149812 524 **■**

- 3.4.5.5 INDEXED ADDRESSING MODE. In the indexed addressing mode, the effective address is variable and depends upon two factors: 1) the current contents of the index (X) register and 2) the offset contained in the byte(s) following the opcode. Three types of indexed addressing exist in the MCU: no offset, 8-bit offset, and 16-bit offset. A good assembler should use the indexed addressing mode that requires the least number of bytes to express the offset.

- 3.4.5.5.1 Indexed, No Offset. In the indexed, no-offset addressing mode, the effective address of the instruction is contained in the 8-bit index register. Thus, this addressing mode can access the first 256 memory locations. These instructions are only one byte.

**Example Program Listing:**

0200 f6 LDA ,X

Load accumulator from location pointed to by index reg (no offset)

**Execution Sequence:**

\$0200 \$F6 [1], [2], [3]

## Explanation:

- [1] CPU reads opcode \$F6 load accumulator using indexed, no offset, addressing mode.

- [2] CPU forms a complete address by adding \$0000 to the contents of the index register.

- [3] CPU then reads the contents of the addressed location into the accumulator.

3-28

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

The following is a list of all M68HC05 instructions that can use the indexed, no-offset addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Arithmetic Shift Left                | ASL      |

| Arithmetic Shift Right               | ASR      |

| Bit Test Memory with Accumulator     | BIT      |

| Clear                                | CLR      |

| Compare Accumulator with Memory      | CMP      |

| Complement                           | COM      |

| Compare Index Register with Memory   | CPX      |

| Decrement                            | DEC      |

| Exclusive OR Memory with Accumulator | EOR      |

| Increment                            | INC      |

| Jump                                 | JMP      |

| Jump to Subroutine                   | JSR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Logical Shift Left                   | LSL      |

| Logical Shift Right                  | LSR      |

| Negate                               | NEG      |

| Inclusive OR                         | ORA      |

| Rotate Left thru Carry               | ROL      |

| Rotate Right thru Carry              | ROR      |

| Subtract with Carry                  | SBC      |

| Store Accumulator in Memory          | STA      |

| Store Index Register in Memory       | STX      |

| Subtract                             | SUB      |

| Test for Negative or Zero            | TST      |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-29

■ 6367248 D149814 3T7 ■

**3.4.5.5.2 Indexed, 8-Bit Offset.** In the indexed, 8-bit offset addressing mode, the effective address is obtained by adding the contents of the byte following the opcode to the contents of the index register. This mode of addressing is useful for selecting the kth element in a 'n' element table. To use this mode, the table must begin in the lowest 256 memory locations, and may extend through the first 511 memory locations (1FE is the last location which the instruction may access). Indexed 8-bit offset addressing can be used for ROM, RAM, or I/O. This is a two-byte instruction with the offset contained in the byte following the opcode. The content of the index register (X) is not changed. The offset byte supplied in the instruction is an unsigned 8-bit integer.

# **Example Program Listing:**

0200 e6 05 LDA \$5,X Load accumulator from location pointed to by index reg (X) + \$05

## **Execution Sequence:**

\$0200 \$E6 [1] \$0201 \$05 [2], [3], [4]

## Explanation:

- [1] CPU reads opcode \$E6 load accumulator using indexed, 8-bit offset addressing mode.

- [2] CPU then reads \$05 from location \$0201. This \$05 is interpreted as the low-order half of a base address. The high-order half of the base address is assumed to be \$00.

- [3] CPU will add the value in the index register to the base address \$0005. The results of this addition is the address that the CPU will use in the load accumulator operation.

- [4] The CPU will then read the value from this address and load this value into the accumulator.

3-30

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

The following is a list of all M68HC05 instructions that can use the indexed, 8-bit offset addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Arithmetic Shift Left                | ASL      |

| Arithmetic Shift Right               | ASR      |

| Bit Test Memory with Accumulator     | BIT      |

| Clear                                | CLR      |

| Compare Accumulator with Memory      | CMP      |

| Complement                           | COM      |

| Compare Index Register with Memory   | CPX      |

| Decrement                            | DEC      |

| Exclusive OR Memory with Accumulator | EOR      |

| Increment                            | INC      |

| Jump                                 | JMP      |

| Jump to Subroutine                   | JSR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Logical Shift Left                   | LSL      |

| Logical Shift Right                  | LSR      |

| Negate                               | NEG      |

| Inclusive OR                         | ORA      |

| Rotate Left thru Carry               | ROL      |

| Rotate Right thru Carry              | ROR      |

| Subtract with Carry                  | SBC      |

| Store Accumulator in Memory          | STA      |

| Store Index Register in Memory       | STX      |

| Subtract                             | SUB      |

| Test for Negative or Zero            | TST      |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-31

■ 6367248 O149816 17T **■**

3.4.5.5.3 Indexed, 16-Bit Offset. In the indexed, 16-bit offset addressing mode, the effective address is the sum of the contents of the 8-bit index register and the two bytes following the opcode. The content of the index register is not changed. These instructions are three bytes, one for the opcode and two for a 16-bit offset.

# **Example Program Listing:**

```

0200 d6 07 00 LDA \$0700,X Load accumulator from location pointed to by index reg (X) + \$0700

```

## **Execution Sequence:**

```

$0200 $D6 [1]

$0201 $07 [2]

$0202 $00 [3], [4], [5]

```

## **Explanation:**

- [1] CPU reads opcode \$D6 load accumulator using indexed, 16-bit offset addressing mode.

- [2] CPU then reads \$07 from location \$0201. This \$07 is interpreted as the high-order half of a base address.

- [3] CPU then reads \$00 from location \$0202. This \$00 is interpreted as the low-order half of a base address.

- [4] CPU will add the value in the index register to the base address \$0700. The results of this addition is the address that the CPU will use in the load accumulator operation.

- [5] The CPU will then read the value from this address and load this value into the accumulator.

3-32

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

🚃 6367248 Ol49817 OO6 🖿

The following is a list of all M68HC05 instructions that can use the indexed, 16-bit offset addressing mode.

| Instruction                          | Mnemonic |

|--------------------------------------|----------|

| Add with Carry                       | ADC      |

| Add                                  | ADD      |

| Logical AND                          | AND      |

| Bit Test Memory with Accumulator     | BIT      |

| Compare Accumulator with Memory      | CMP      |

| Compare Index Register with Memory   | CPX      |

| Exclusive OR Memory with Accumulator | EOR      |

| Jump                                 | JMP      |

| Jump to Subroutine                   | JSR      |

| Load Accumulator from Memory         | LDA      |

| Load Index Register from Memory      | LDX      |

| Inclusive OR                         | ORA      |

| Subtract with Carry                  | SBC      |

| Store Accumulator in Memory          | STA      |

| Store Index Register In Memory       | STX      |

| Subtract                             | SUB      |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-33

**■** 6367248 0149818 T42 **■**

3.4.5.6 RELATIVE ADDRESSING MODE. The relative addressing mode is used only for branch instructions. Branch instructions, other than the branching versions of bit-manipulation instructions, generate two machine-code bytes: one for the opcode and one for the relative offset. Because it is desirable to branch in either direction, the offset byte is a signed twos-complement offset with a range of -127 to +128 bytes (with respect to the address of the instruction immediately following the branch instruction). If the branch condition is true, the contents of the 8-bit signed byte following the opcode (offset) are added to the contents of the program counter to form the effective branch address; otherwise, control proceeds to the instruction immediately following the branch instruction.

A programmer specifies the destination of a branch as an absolute address (or label which refers to an absolute address). The Motorola assembler calculates the 8-bit signed relative offset, which is placed after the branch opcode in memory.

# Example Program Listing:

0200 27 rr

BEQ DEST

Branch to DEST if Z=1 (branch if equal or zero)

# Execution Sequence:

\$0200 \$27 [1] \$0201 \$rr [2], [3]

## Explanation:

- [1] CPU reads opcode \$27 branch if Z = 1, (relative addressing mode).

- [2] CPU reads the offset, \$rr.

- [3] CPU internally tests the state of the Z bit and causes a branch if Z is set.

3-34

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**---** 6367248 0149819 989 **---**

The following is a list of all M68HC05 instructions that can use the relative addressing mode.

| Instruction                         | Mnemonic |

|-------------------------------------|----------|

| Branch if Carry Clear               | BCC      |

| Branch is Carry Set                 | BCS      |

| Branch if Equal                     | BEQ      |

| Branch if Half-Carry Clear          | BHCC     |

| Branch if Half-Carry Set            | BHCS     |

| Branch if Higher                    | BHI      |

| Branch if Higher or Same            | BHS      |

| Branch if Interrupt Line is High    | BIH      |

| Branch if Interrupt Line is Low     | BIL      |

| Branch if Lower                     | BLO      |

| Branch if Lower or Same             | BLS      |

| Branch if Interrupt Mask is Clear   | BMC      |

| Branch if Minus                     | вмі      |

| Branch if Interrupt Mask Bit is Set | BMS      |

| Branch if Not Equal                 | BNE      |

| Branch if Plus                      | BPL      |

| Branch Always                       | BRA      |

| Branch if Bit n is Clear            | BRCLR    |

| Branch if Bit n is Set              | BRSET    |

| Branch Never                        | BRN      |

| Branch to Subroutine                | BSR      |

- 3.4.5.7 BIT TEST AND BRANCH INSTRUCTIONS. These instructions use direct addressing mode to specify the location being tested and relative addressing to specify the branch destination. This applications guide treats these instructions as direct addressing mode instructions. Some older Motorola documents call the addressing mode of these instructions BTB for bit test and branch.

- **3.4.5.8 INSTRUCTIONS ORGANIZED BY TYPE**. Tables 3-2 through 3-5 show the MC68HC05 instruction set displayed by instruction type.

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-35

■ 6367248 O14982O 6TO ■

Table 3-2. Register/Memory Instructions

3-36

|                                             |       |            |            |             |       |            |             |        |            | Addressing Modes | DoM gi      | 8                      |             |      |                           |        |                        |                            |             |

|---------------------------------------------|-------|------------|------------|-------------|-------|------------|-------------|--------|------------|------------------|-------------|------------------------|-------------|------|---------------------------|--------|------------------------|----------------------------|-------------|

|                                             |       | =          | mmediate   |             |       | Direct     |             | Ü      | Extended   |                  | -3          | Indexed<br>(No Offset) | <b>a</b>    | - 😸  | Indexed<br>(8-Bit Offset) | £      | ]<br> - ( <del>j</del> | Indexed<br>(16-Bit Offset) | et)         |

| Function                                    | Mnem. | op<br>code | #<br>Bytes | #<br>Cycles | o o o | #<br>Bytes | #<br>Cycles | o og   | #<br>Bytes | #<br>Cycles      | Op-<br>code | #<br>Bytes             | #<br>Cycles | o po | #<br>Bytes                | Cycles | op.                    | Bytes                      | #<br>Cycles |

| Load A from Memory                          | ΓDA   | A6         | 2          | 2           | B6    | 2          | 3           | 90     | ဗ          | 4                | F6          | -                      | е           | 93   | 2                         | 4      | 8                      | 8                          | 5           |

| Load X from Memory                          | rΩX   | AE         | 2          | 2           | æ     | 2          | က           | 끙      | က          | 4                | 쁀           | -                      | ٣           | H    | 2                         | 4      | 퓝                      | 3                          | 5           |

| Store A in Memory                           | STA   | 1          | 1          | 1           | 87    | 2          | 4           | Ω      | 8          | 2                | 73          | -                      | 4           | E7   | 2                         | 2      | 6                      | 8                          | 9           |

| Store X in Memory                           | STX   | ŀ          | -          | Ι           | BF    | 2          | 4           | Ç.     | 3          | 5                | Ħ           | -                      | 4           | 岀    | 2                         | 2      | 늄                      | 3                          | 9           |

| Add Memory to A                             | ADD   | AB         | 2          | 2           | 88    | 2          | 3           | CB     | 3          | 4                | FB          | -                      | е           | BB   | 2                         | 4      | 80                     | က                          | 5           |

| Add Memory and<br>Carry to A                | ADC   | A9         | 2          | 2           | B9    | 2          | 3           | ට      | 3          | 4                | F9          | 1                      | 3           | E3   | 2                         | 4      | 6Q                     | 8                          | 5           |

| Subtract Memory                             | SUB   | A0         | 2          | 2           | B0    | 2          | 3           | ပ္     | 3          | 4                | F0          | 1                      | 3           | E0   | 2                         | 4      | 00                     | 3                          | 5           |

| Subtract Memory from<br>A with Borrow       | SBC   | A2         | 2          | 2           | B2    | 2          | 3           | C2     | 3          | 4                | F2          | 1                      | 3           | E2   | 2                         | 4      | D2                     | 3                          | 2           |

| AND Memory to A                             | AND   | A4         | 2          | 2           | B4    | 2          | 3           | 75     | 3          | 4                | F4          | 1                      | 3           | E4   | 2                         | 4      | D4                     | 3                          | 5           |

| OR Memory with A                            | ORA   | AA         | 2          | 2           | ВА    | 2          | 3           | CA     | 3          | 4                | FA          | 1                      | 3           | EA   | 2                         | 4      | DA                     | 3                          | 5           |

| Exclusive OR Memory with A                  | EOR   | A8         | 2          | 2           | B8    | 2          | 3           | 8      | 3          | 4                | F8          | -                      | 3           | E8   | 2                         | 4      | BQ                     | က                          | 2           |

| Arithmetic Compare A with Memory            | СМР   | A1         | 2          | 2           | B1    | 2          | က           | ر<br>د | 3          | 4                | F           | ı                      | · 6         | E1   | 2                         | 4      | D1                     | 3                          | 2           |

| Arithmetic Compare X with Memory            | СРХ   | A3         | 2          | 2           | B3    | 2          | 3           | ය      | 3          | 4                | F3          | 1                      | 3           | E3   | 2                         | 4      | D3                     | 3                          | 5           |

| Bit Test Memory with<br>A (Logical Compare) | BIT   | A5         | 2          | 2           | B5    | 2          | 3           | CS     | 3          | 4                | F5          | 1                      | 3           | E5   | 2                         | 4      | DS                     | 3                          | 5           |

| Jump Unconditional                          | JMP   | ı          | 1          | ı           | BC    | 2          | 2           | သ      | 3          | 3                | FC          | 1                      | 2           | EC   | 2                         | 3      | DC                     | 3                          | .4          |

| Jump to Subroutine                          | JSR   | 1          | 1          | 1           | BD    | 2          | 2           | CD     | 3          | 9                | Ð           | 1                      | 5           | ED   | 2                         | 9      | 8                      | 9                          | 7           |

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**■** 6367248 0149821 537 **■**

Table 3-3. Read/Modify-Write Instructions

|                            |       |            |              |             |         |              |             | Addre       | Addressing Modes | lodes       |     |                        |             |             |                           |             |

|----------------------------|-------|------------|--------------|-------------|---------|--------------|-------------|-------------|------------------|-------------|-----|------------------------|-------------|-------------|---------------------------|-------------|

|                            |       |            | Inherent (A) | ह           | 直       | Inherent (X) | g           |             | Direct           |             | - Z | Indexed<br>(No Offset) | ÷           | 1.8)        | Indexed<br>(8-Bit Offset) | )t)         |

| Function                   | Mnem. | op code    | #<br>Bytes   | #<br>Cycles | op code | #<br>Bytes   | #<br>Cycles | Op-<br>code | #<br>Bytes       | #<br>Cycles | Op- | #<br>Bytes             | #<br>Cycles | Op-<br>code | #<br>Bytes                | #<br>Cycles |

| Increment                  | INC   | 40         | -            | 3           | ည္သ     | 1            | က           | 3С          | 2                | 5           | )C  | 1                      | 2           | ပ္ဖ         | 2                         | 6           |

| Decrement                  | DEC   | 4 <b>,</b> | -            | 3           | 5A      | 1            | 3           | 3A          | 2                | 2           | 7A  | -                      | 2           | <b>6</b> A  | 2                         | 9           |

| Clear                      | CLR   | 4F         | -            | 3           | 5F      | -            | 3           | 3F          | 2                | 5           | 7F  | 1                      | 5           | 6F          | 2                         | 9           |

| Complement                 | СОМ   | 43         | -            | 3           | 53      | 1            | 3           | 33          | 2                | 2           | 73  | -                      | 5           | 83          | 2                         | 9           |

| Negate<br>(2's Complement) | NEG   | 40         | 1            | 3           | 20      | 1            | က           | 30          | 2                | 5           | 7.0 | -                      | 2           | 99          | 2                         | 9           |

| Rotate Left Thru Carry     | RCL   | 49         | -            | 3           | 59      | 1            | က           | 39          | 2                | 5           | 79  | 1                      | 2           | 69          | 2                         | 9           |

| Rotate Right Thru Carry    | ROR   | 46         | -            | 3           | 26      | -            | ю           | 36          | 2                | 5           | 76  | 1                      | 5           | 99          | 2                         | 9           |

| Logical Shift Left         | TST   | 48         | -            | 3           | 28      | 1            | 3           | 38          | 2                | 2           | 78  | 1                      | 2           | 88          | 2                         | 9           |

| Logical Shift Right        | LSR   | 44         | -            | 3           | 54      | 1            | 3           | 34          | 2                | 2           | 74  | -                      | 2           | इ           | 2                         | 9           |

| Arithmetic Shift Right     | ASR   | 47         | 1            | 3           | 22      | 1            | 3           | 37          | 2                | 2           | 77  | -                      | 5           | 67          | 2                         | 9           |

| Test for Negative or Zero  | TST   | 4D         | -            | 3           | 2D      | 1            | က           | 3D          | 2                | 4           | 7D  | -                      | 4           | 60          | 2                         | 5           |

| Multiply                   | MUL   | 42         | 1            | 11          | _       | 1            | 1           | -           | ı                | 1           | -   | 1                      | 1           | 1           | ı                         |             |

**MOTOROLA**

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**■** 6367248 0149822 473 **■**

Table 3-4. Branch Instructions

|                                            |          | Relative | Addressi   | ng Mode     |

|--------------------------------------------|----------|----------|------------|-------------|

| Function                                   | Mnemonic | Opcode   | #<br>Bytes | #<br>Cycles |

| Branch Always                              | BRA      | 20       | 2          | 3           |

| Branch Never                               | BRN      | 21       | 2          | 3           |

| Branch IFF Higher                          | вні      | 22       | 2          | 3           |

| Branch IFF Lower or Same                   | BLS      | 23       | 2          | 3           |

| Branch IFF Carry Clear                     | BCC      | 24       | 2          | 3           |

| Branch IFF Higher or Same<br>(Same as BCC) | BHS      | 24       | 2          | 3           |

| Branch IFF Carry Set                       | BCS      | 25       | 2          | 3           |

| Branch IFF Lower<br>(Same as BCS)          | BLO      | 25       | 2          | 3           |

| Branch IFF Not Equal                       | BNE      | 26       | 2          | 3           |

| Branch IFF Equal                           | BEQ      | 27       | 2          | 3           |

| Branch IFF Half-Carry Clear                | BHCC     | 28       | 2          | 3           |

| Branch IFF Half-Carry Set                  | BHCS     | 29       | 2          | 3           |

| Branch IFF Plus                            | BPL      | 2A       | 2          | 3           |

| Branch IFF Minus                           | BMI      | 2B       | 2          | 3           |

| Branch IFF Interrupt Mask Bit is Clear     | вмс      | 2C       | 2          | 3           |

| Branch IFF Interrupt Mask Bit is Set       | BMS      | 2D       | 2          | 3           |

| Branch IFF Interrupt Line is Low           | BIL      | 2E       | 2          | 3           |

| Branch IFF Interrupt Line is High          | BIH      | 2F       | 2          | 3           |

| Branch to Subroutine                       | BSR      | AD       | 2          | 6           |

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

■ 6367248 0149823 30T ■

**Table 3-5. Control Instructions**

|                          |          |        | Inherent   |             |

|--------------------------|----------|--------|------------|-------------|

| Function                 | Mnemonic | Opcode | #<br>Bytes | #<br>Cycles |

| Transfer A to X          | TAX      | 97     | 1          | 2           |

| Transfer X to A          | TXA      | 9F     | 1          | 2           |

| Set Carry Bit            | SEC      | 99     | 1          | 2           |

| Clear Carry Bit          | CLC      | 98     | 1          | 2           |

| Set Interrupt Mask Bit   | SEI      | 9B     | 1          | 2           |

| Clear Interrupt Mask Bit | CLI      | 9A     | 1          | 2           |

| Software Interrupt       | SWI      | 83     | 1          | 10          |

| Return from Subroutine   | RTS      | 81     | 1          | 6           |

| Return from Interrupt    | RTI      | 80     | 1          | 9           |

| Reset Stack Pointer      | RSP      | 9C     | 1          | 2           |

| No-Operation             | NOP      | 9D     | 1          | 2           |

| Stop                     | STOP     | 8E     | 1          | 2           |

| Wait                     | WAIT     | 8F     | 1          | 2           |

MOTOROLA

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

3-39

**■** 6367248 0149824 246 **■**

## 3.4.6 Instruction Set Summary

Computers use an operation code or opcode to give instructions to the CPU. The instruction set for a specific CPU is the set of all opcodes that the CPU knows how to execute. The CPU in the MC68HC705C8 MCU can understand 62 basic instructions, some of which have several variations that require separate opcodes. The M68HC05 instruction set includes 210 unique instruction opcodes.

The following table is an alphabetical listing of the M68HC05 instructions available to the user. In listing all the factors necessary to program, the table uses the following symbols:

#### **Condition Code Symblols**

| Н | <ul><li>Half Carry (Bit 4)</li></ul>       |   | _ | Test and Set if True, |

|---|--------------------------------------------|---|---|-----------------------|

| 1 | <ul> <li>Interrupt Mask (Bit 3)</li> </ul> | - |   | (cleared otherwise)   |

| N | <ul><li>Negate (Sign Bit 2)</li></ul>      |   | _ | Not Affected          |

| Z | — Zero (Bit 1)                             | ? | _ | Load CC from Stack    |

| С | <ul><li>— Carry/Borrow (Bit 0)</li></ul>   | 0 | _ | Cleared               |

|   |                                            | 1 |   | Set                   |

#### **Boolean Operators**

| ( ) | <ul><li>Contents of (i.e., (M)</li></ul> | +        | — | (inclusive) OR    |

|-----|------------------------------------------|----------|---|-------------------|

|     | means the contents                       | $\oplus$ | — | Exclusive OR      |

|     | of memory location                       | _        | _ | NOT               |

|     | M)                                       | -        | _ | Negation          |

|     | <ul><li>is loaded with, 'gets'</li></ul> |          |   | (twos complement) |

| •   | — AND                                    | ×        |   | Multiplication    |

### **MPU Registers**

| Α    | _ | Accumulator         | PC  | <ul> <li>Program Counter</li> </ul>  |

|------|---|---------------------|-----|--------------------------------------|

| ACCA | _ | Accumulator         | PCH | <ul> <li>PC High Byte</li> </ul>     |

| CC   | _ | Condition Code Reg. | PCL | <ul> <li>PC Low Byte</li> </ul>      |

| X    | _ | Index Register      | SP  | <ul> <li>Stack Pointer</li> </ul>    |

| M    | _ | Any memory location | REL | <ul> <li>Relative Address</li> </ul> |

|      |   | (one byte)          |     |                                      |

| Addressing Modes   | (Abbreviation) | Operands |

|--------------------|----------------|----------|

| Inherent           | INH            | none     |

| Immediate          | IMM            | ii       |

| Direct (for bit    | DIR            | dd       |

| test instructions) |                | dd rr    |

| Extended           | EXT            | hh li    |

| Indexed 0 Offset   | IX             | none     |

| Indexed 1-Byte     | IX1            | ff       |

| Indexed 2-Byte     | IX2            | ee ff    |

| Relative           | REL            | rr       |

M68HC05 MICROCONTROLLER APPLICATIONS GUIDE

**MOTOROLA**

**—** 6367248 0149825 182 **—**

# INSTRUCTION ADDRESSING MODES, AND EXECUTION TIMES (Sheet 1 of 4)

| Source<br>Form(s)                                   | Operation                  | Boolean<br>Expression | Addressing<br>Mode for                                          |                                        | Coding ecimal)                         | Bytes                                     | Cycles                          | Co | ndif     | tion     | . Ca     | de       |

|-----------------------------------------------------|----------------------------|-----------------------|-----------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------|---------------------------------|----|----------|----------|----------|----------|

|                                                     |                            | Expression            | Operand                                                         | Opcode                                 | Operand                                |                                           | l                               | н  |          |          | z        |          |

| ADC (opr)                                           | Add with Carry             | ACCA ♦ ACCA + M + C   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                           | A9<br>89<br>C9<br>D9<br>E9             | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>2<br>3<br>3<br>2                     | 2<br>3<br>4<br>5<br>4<br>3      | ** | _        | *        | #        | *        |

| ADD (opr)                                           | Add                        | ACCA ♦ ACCA + M       | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                           | AB<br>BB<br>CB<br>DB<br>EB             | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>2<br>3<br>3<br>2                     | 2<br>3<br>4<br>5<br>4<br>3      | *  | _        | \$       | #        | *        |

| AND (opr)                                           | Logical AND                | ACCA ♦ ACCA ◆ M       | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                           | A4<br>B4<br>C4<br>D4<br>E4             | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>2<br>3<br>3<br>2                     | 2<br>3<br>4<br>5<br>4<br>3      | _  | -        | *        | #        |          |

| ASL (opr)<br>ASLA<br>ASLX<br>ASL (opr)<br>ASL (opr) | Arithmetic Shift Left      | □ • □ □ □ 0 0 C b7 b0 | DIR<br>INH(A)<br>INH(X)<br>IX1<br>IX                            | 38<br>48<br>58<br>68<br>78             | dd<br>ff                               | 2<br>1<br>1<br>2<br>1                     | 5<br>3<br>3<br>6<br>5           | _  |          | #        | *        | ♦¢       |

| ASR (opr)<br>ASRA<br>ASRX<br>ASR (opr)<br>ASR (opr) | Arithmetic Shift Right     | b7 b0 C               | DIR<br>INH(A)<br>INH(X)<br>IX1<br>IX                            | 37<br>47<br>57<br>67<br>77             | dd<br>ff                               | 2<br>1<br>1<br>2                          | 5<br>3<br>6<br>5                | -  |          | 40       | 410      | *        |

| BCC (rel)                                           | Branch if Carry Clear      | ? C ÷ 0               | REL                                                             | 24                                     | rr                                     | 2                                         | 3                               | _  | ⊏        | ㄷ        |          | Ε        |

| BCLR n, (opr)                                       | Clear Bit n in Memory      | Mn <b>♦</b> 0         | DIR(b0) DIR(b1) DIR(b2) DIR(b3) DIR(b4) DIR(b5) DIR(b6) DIR(b7) | 11<br>13<br>15<br>17<br>19<br>18<br>1D | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 5<br>5<br>5<br>5<br>5<br>5<br>5 |    |          |          |          |          |

| BCS (rel)                                           | Branch if Carry Set        | ? C = 1               | REL                                                             | 25                                     | rr                                     | 2                                         | 3                               | L  | ⇇        | _        | 鸉        | Е        |

| BEQ (rel)                                           | Branch if Equal            | ? Z = 1               | REL                                                             | 27                                     | rr                                     | 2                                         | 3                               | t  | t        | 1        | <u> </u> | E        |

| BHCC (rel)                                          | Branch if Half Carry Clear | ? H = 0               | REL                                                             | 28                                     | rr                                     | 2                                         | 3                               | t  | 1        | t        | ┢        | ┢        |

| BHCS (rel)                                          | Branch if Half Carry Set   | ? H = 1               | REL                                                             | 29                                     | rr                                     | 2                                         | 3                               | t  | <u> </u> | _        | ┢        | <u> </u> |

| BHI (rel)                                           | Branch if Higher           | ? (C + Z) – 0         | REL                                                             | 22                                     | rr                                     | 2                                         | 3                               | 1_ | Ι=       | <b>—</b> | <u> </u> | 二        |

| BHS (rei)                                           | Branch if Higher or Same   | ? C - 0               | REL                                                             | 24                                     | rr                                     | 2                                         | 3                               |    | <u> </u> | F        | F        |          |