# QL58x0 Enhanced QuickPCI Target Family Data Sheet

## **Device Highlights**

### **High Performance PCI Controller**

- 33/66 MHz 32-bit PCI Target

- Zero-wait state PCI Target provides up to 264 MBps transfer rates

- Target interface supports retry, disconnect with/without data transfer, and target abort

- · Fully programmable back-end interface

- Independent PCI bus (33/66 MHz) and local bus (up to 160 MHz) clocks

- Fully customizable PCI Configuration Space

- Configurable FIFOs with depths up to 256 words

- Reference design with driver code (Win 95/98/2000/NT 4.0) available

- PCI v2.3 compliant

- Supports Type 0 configuration cycles

- 3.3 V PCI signaling

- 1.8 V supply voltage

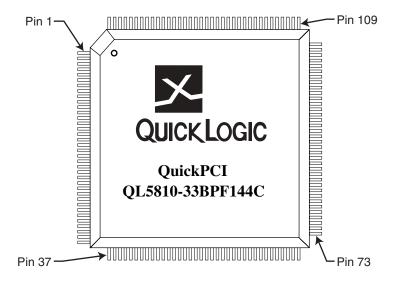

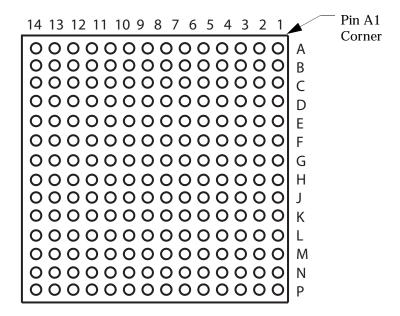

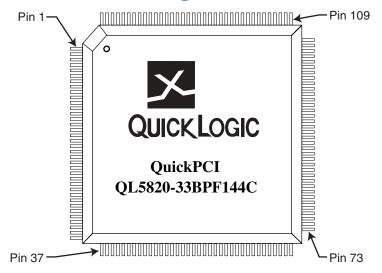

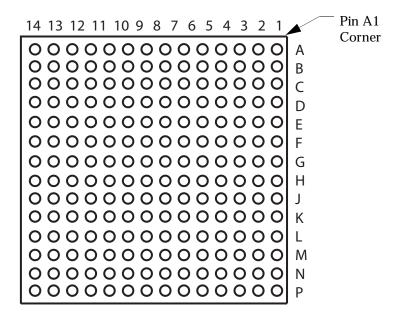

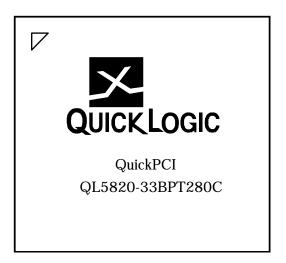

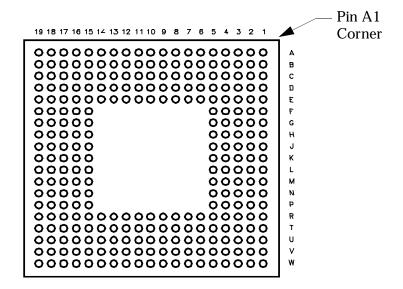

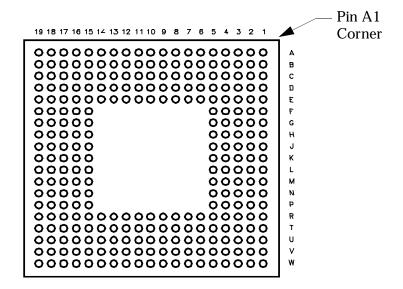

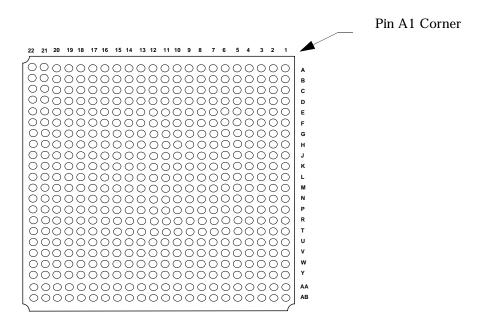

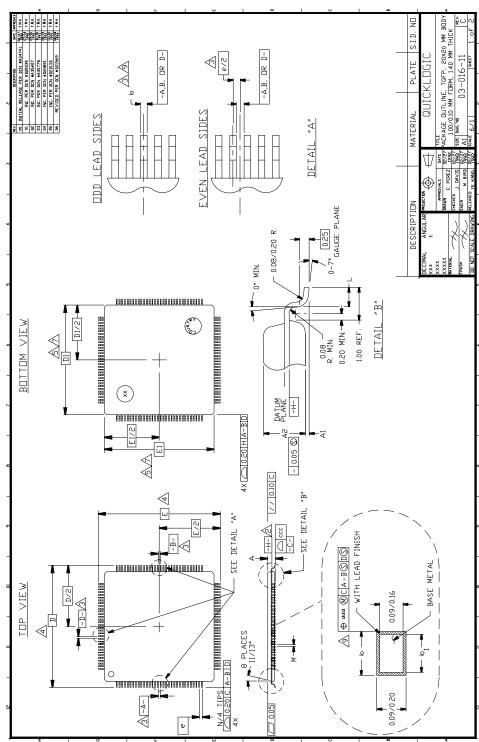

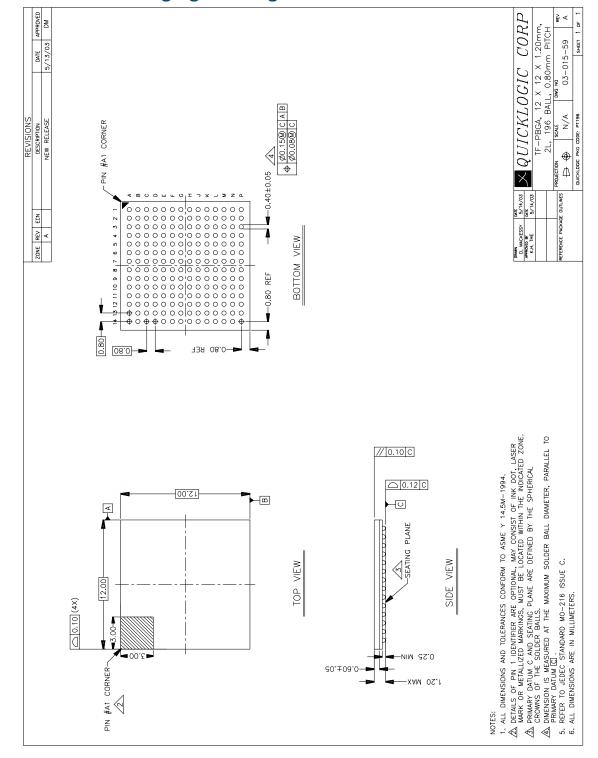

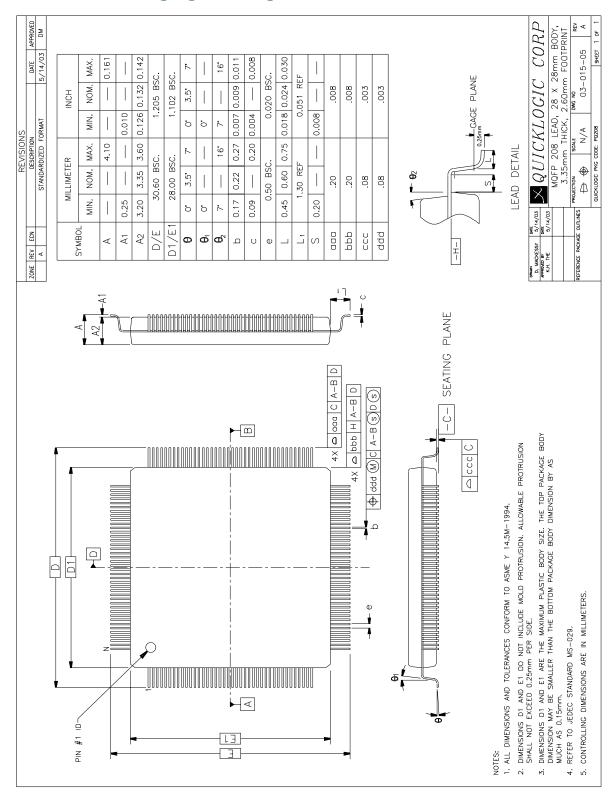

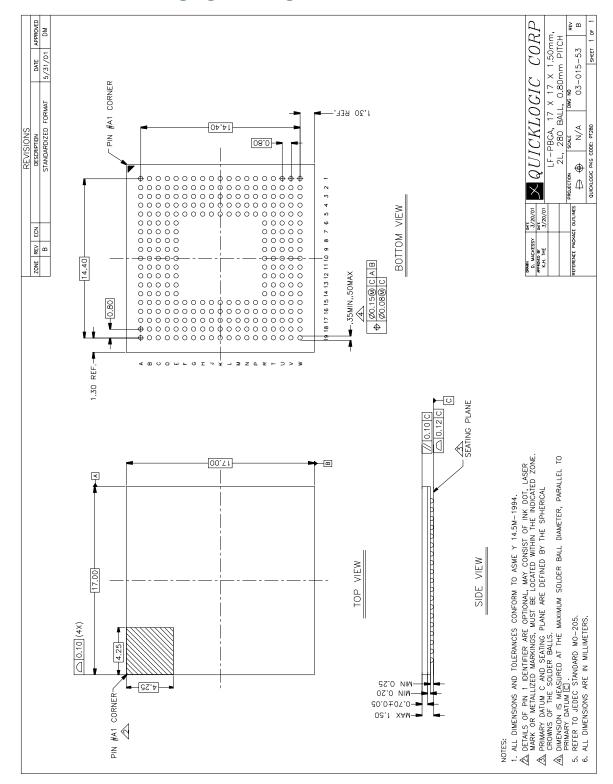

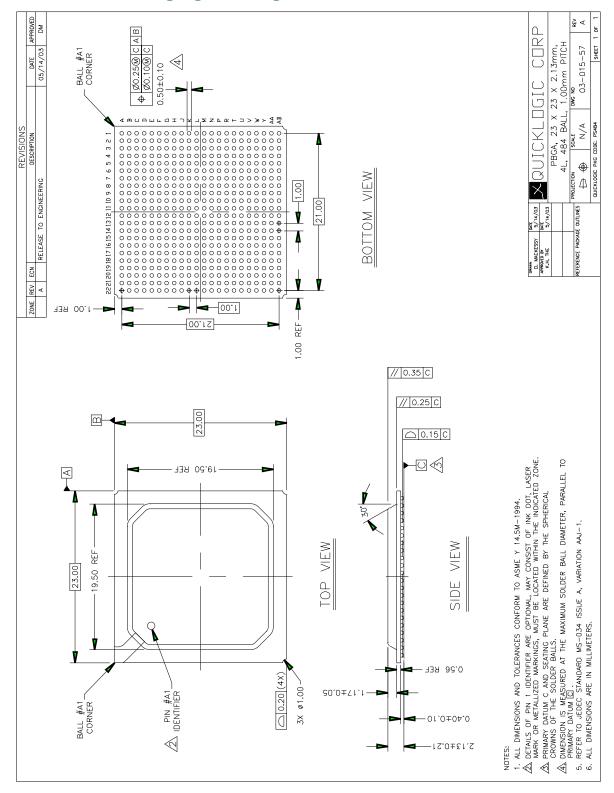

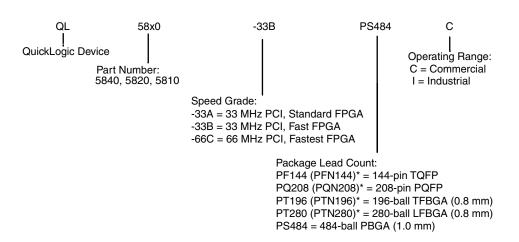

- 484-ball PBGA, 280-ball LFBGA, 208-pin PQFP, 196-ball TFBGA, and 144-pin TQFP packages

- Unlimited/Continuous Burst Transfers supported

### **Extendable PCI Functionality**

- Support for Configuration Space from  $0 \times 40$  to  $0 \times 3FF$

- PCI v2.3 Power Management Spec. compatible

- PCI v2.3 Vital Product Data (VPD) configuration support

### Flexible Programmable Logic

- Up to 1,478 logic cells

- Up to 50,688 RAM bits

- Up to 264 I/O pins

- All back-end interface and glue-logic can be implemented on chip

- Two 32-bit busses interface between the PCI Controller and the Programmable Logic

- Up to twenty-two 2,304 bit dual-port high performance SRAM blocks

- Up to 3,748 flip-flops available

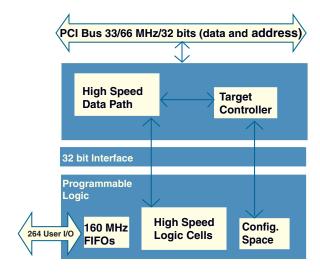

Figure 1: QL58x0 Block Diagram

### **Architecture Overview**

The QL58x0 device family of QuickPCI Embedded Standard Products (ESPs) provides a complete and customizable PCI interface solution combined with programmable logic. Since the QL58x0 devices provide optimized pre-verified PCI cores, the burden of PCI timing closure and PCI protocol compliance has been eliminated and allows for the maximum 32-bit PCI bus bandwidth (264 MBps).

The programmable logic portion of this family contains up to 1,478 QuickLogic Logic Cells and up to 22 QuickLogic Dual-Port RAM Blocks. These configurable RAM blocks can be configured in many width/depth combinations. They can also be combined with logic cells to form FIFOs, or be initialized via Serial EEPROM on power-up and used as ROMs.

The QL58x0 device meets PCI 2.3 electrical and timing specifications and has been fully hardware-tested. The QL58x0 device features 1.8 V operation with multi-volt compatible I/Os. The device can easily operate in 3.3 V embedded systems and is fully compatible with 3.3 V applications.

### **PCI Controller**

The PCI Controller is a 33/66 MHz 32-bit PCI 2.3 compliant Target Controller capable of infinite length Target Write and Read transactions at zero wait states (264 MBps).

The Target interface offers full PCI Configuration Space and flexible target addressing. It supports zero-wait-state target Write and Read operations. It also supports retry, disconnect with/without data transfer, and target abort requested by the back end. Any number of 32-bit BARs may be configured as either memory or I/O space. All required and optional PCI 2.3 Configuration Space registers can be implemented within the programmable region of the device. A reference design of a Target Configuration Space and Addressing module is available and is included in the Quick *Works* design software.

The interface ports are designed for target transactions. The Target Configuration Space and Address Decoding are done in the programmable logic region of the device. These functions are not timing critical, so leaving these elements in the programmable region allows the greatest degree of flexibility to the designer.

**Table 1** shows several commonly implemented IP cores in the programmable logic portion of the Target Controller device. Their respective logic cell utilization and performance information are shown for easy reference. Notice that the Configuration Space and Address Decoding core is labelled as an essential IP core. This IP block is necessary for the Target Controller to be fully functional. The optional IP cores are common interface IP cores made available so that designers may implement according to their design requirements. These optional IP cores do not affect the functionality of the Target Controller.

Table 1: IP Implemented in Programmable Logic

| Essential PCI IP Cores               | Logic Cells | RAM | Performance |

|--------------------------------------|-------------|-----|-------------|

| Configuration Space/Address Decoding | 110         | N/A | 33/66 MHz   |

| Optional IP Cores                    | Logic Cells | RAM | Performance |

| Async 32x32 FIFO                     | 64          | 2   | 210 MHz     |

| Async 128x32 FIFO                    | 88          | 2   | 190 MHz     |

| SDRAM Controller                     | 149         | N/A | 160 MHz     |

| DDR SDRAM Controller                 | 216         | N/A | 100 MHz     |

| Pulse Width Modulation               | 20          | N/A | 303 MHz     |

# **Configuration Space and Address Decode**

The configuration space is completely customizable in the programmable region of the device.

PCI address and command decoding is performed by logic in the programmable section of the device. This allows support for any size of memory or I/O space for back end logic. It also allows the user to implement any subset of the PCI commands supported by the QL58x0. QuickLogic provides a reference Address Register/Counter and Command Decode block.

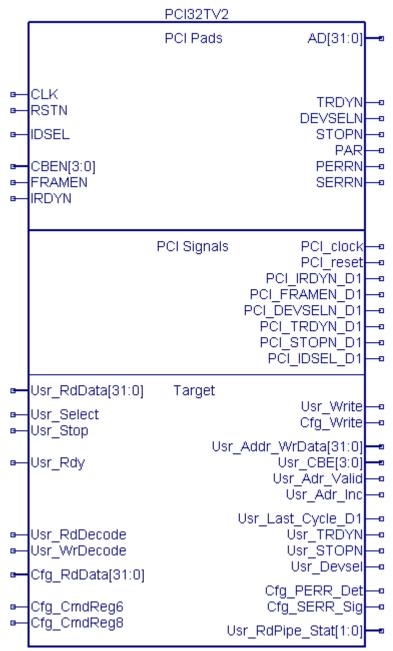

### **PCI Interface Symbol**

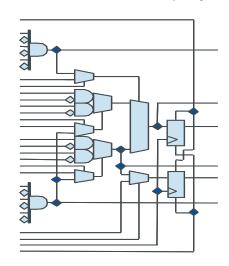

**Figure 2** shows the graphical interface symbol numbers you have to use in your schematic design in order to attach the local interface programmable logic design to the Target PCI core. If you are designing with a top-level Verilog or VHDL file, use a structural instantiation of this PCI32TV2 block instead of a graphical symbol.

Figure 2: PCI Interface Symbol

# **PCI Target Interface**

Table 2: PCI Target Interface

| Signal                | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usr_Addr_WrData[31:0] | 0   | <b>Target address, and target Write data.</b> During all target accesses, the address is presented on Usr_Addr_WrData[31:0]; at the same time, Usr_Adr_Valid is active. During target Write transactions, this port also presents valid Write data to the PCI configuration space or user logic when Usr_Adr_Inc is active.                                                                                                                                                                                                                                                                                                                                                                     |

| Usr_CBE[3:0]          | 0   | PCI command and byte enables. During target accesses, the PCI command is presented on Usr_CBE[3:0]; at the same time, Usr_Adr_Valid is active. This port also presents active-low byte enables to the PCI configuration space or user logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Usr_Adr_Valid         | 0   | Indicates the beginning of a PCI transaction, and that a target address is valid on Usr_Addr_WrData[31:0] and the PCI command is valid on Usr_CBE[3:0]. When this signal is active, the target address must be latched and decoded to determine if this address belongs to the device's memory or I/O space. Also, the PCI command must be decoded to determine the type of PCI transaction. On subsequent clocks of a target access, this signal is low, indicating that address is NOT present on Usr_Addr_WrData[31:0].                                                                                                                                                                      |

| Usr_Adr_Inc           | 0   | Indicates that the target address should be incremented, because the previous data transfer has completed. During burst target accesses, the target address is only presented to the back-end logic at the beginning of the transaction (when Usr_Adr_Valid is active), and must therefore be latched and incremented by four for subsequent data transfers. Note that during target Write transactions, Usr_Adr_Inc indicates valid data on Usr_Addr_WrData[31:0] that must be accepted by the backend logic (regardless of the state of Usr_Rdy). During Read transactions, Usr_Adr_Inc signals to the backend that the PCI core has presented the read data on the PCI bus (TRDYN asserted). |

| Usr_RdDecode          | ı   | This signal should be the combinatorial decode of the "user read" command from Usr_CBE[3:0]. This command may be mapped from any of the PCI Read commands, such as Memory Read, Memory Read Line, Memory Read Multiple, I/O Read, etc. It is internally gated with Usr_Adr_Valid.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Usr_WrDecode          | I   | This signal should be the combinatorial decode of the "user write" command from Usr_CBE[3:0]. This command may be mapped from any of the PCI Write commands, such as Memory Write or I/O Write. It is internally gated with Usr_Adr_Valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Usr_Select            | I   | This signal should be driven active when the address on Usr_Addr_WrData[31:0] has been decoded and determined to be within the address space of the device. Usr_Addr_WrData[31:0] must be compared to each of the valid Base Address Registers in the PCI configuration space. Also, this signal must be gated by the Memory Access Enable or I/O Access Enable registers in the PCI configuration space (Command Register bits 1 or 0 at offset 04h). Internally gated with Usr_Adr_Valid.                                                                                                                                                                                                     |

| Usr_Write             | 0   | This signal is active throughout a "user write" transaction, which has been decoded by Usr_WrDecode at the beginning of the transaction. The Write strobe for individual DWORDs of data (on Usr_Addr_WrData[31:0]) during a user Write transaction should be generated by logically ANDing this signal with Usr_Adr_Inc.                                                                                                                                                                                                                                                                                                                                                                        |

| Cfg_Write             | 0   | This signal is active throughout a "configuration write" transaction. The Write strobe for individual DWORDs of data (on Usr_Addr_WrData[31:0]) during a configuration Write transaction should be generated by logically ANDing this signal with Usr_Adr_Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Cfg_RdData[31:0]      | I   | Data from the PCI configuration registers, required to be presented during PCI configuration reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Usr_RdData[31:0]      | ı   | Data from the back-end user logic required to be presented during PCI user reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 2: PCI Target Interface (Continued)

| Signal               | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cfg_CmdReg6          | I   | Bit 6 from the Command Register in the PCI configuration space (offset 04h). Parity Error Response. If high, the core uses PERRN to report data parity errors. Otherwise it never drives it.                                                                                                                                                                                                                                                                                                                                                                          |

| Cfg_CmdReg8          | I   | Bit 8 from the Command Register in the PCI configuration space (offset 04h). SERRN Enable. If high, the cores uses SERRN to report address parity errors if Cfg_CmdReg6 is high.                                                                                                                                                                                                                                                                                                                                                                                      |

| Cfg_PERR_Det         | 0   | Parity error detected on the PCI bus. When this signal is active, bit 15 of the Status Register must be set in the PCI configuration space (offset 04h).                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cfg_SERR_Sig         | 0   | System error asserted on the PCI bus. When this signal is active, the Signalled System Error bit, bit 14 of the Status Register, must be set in the PCI configuration space (offset 04h).                                                                                                                                                                                                                                                                                                                                                                             |

| Usr_TRDY             | 0   | Inverted copy of the TRDYN signal as driven by the PCI target interface. Valid only within a target access.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Usr_DEVSEL           | 0   | Inverted copy of the DEVSELN signal as driven by the PCI target interface. Valid only within a target access.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Usr_Last_Cycle_D1    | 0   | Active one clock cycle after the last data phase (may not with data transfer) occurs on PCI and inactive one clock cycle afterwards.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Usr_Rdy              | I   | Used to delay (add wait states to) a target PCI transaction when the backend needs additional time to provide data (read) or accept data (write). Subject to PCI latency restrictions.                                                                                                                                                                                                                                                                                                                                                                                |

| Usr_Stop             | I   | Used to prematurely stop a PCI target access on the next PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Usr_STOPN            | 0   | Copy of the STOPN signal as driven by the PCI target interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Usr_RdPipe_Stat[1:0] | 0   | Indicates the number of dwords currently in the read pipeline ("00" = 0 elements, "01" = 1 element, "11" = 2 elements). This value is important at the end of a transaction (i.e., when Usr_Last_Cycle_D1 is active) if non-prefetchable memory is being read. Non-prefetchable memory is defined as registers or memory elements whose value changes when they are read. Examples are status registers which are cleared when they are read, or FIFO memories, since consecutive reads from the same address in these elements may not produce the same data values. |

# **PCI Internal Signals**

Table 3: PCI Internal Signals

| Signal         | I/O | Description                                                        |

|----------------|-----|--------------------------------------------------------------------|

| PCI_clock      | 0   | PCI clock.                                                         |

| PCI_reset      | 0   | PCI reset signal.                                                  |

| PCI_IRDYN_D1   | 0   | Copy of the IRDYN signal from the PCI bus, delayed by one clock.   |

| PCI_FRAMEN_D1  | 0   | Copy of the FRAMEN signal from the PCI bus, delayed by one clock.  |

| PCI_DEVSELN_D1 | 0   | Copy of the DEVSELN signal from the PCI bus, delayed by one clock. |

| PCI_TRDYN_D1   | 0   | Copy of the TRDYN signal from the PCI bus, delayed by one clock.   |

| PCI_STOPN_D1   | 0   | Copy of the STOPN signal from the PCI bus, delayed by one clock.   |

| PCI_IDSEL_D1   | 0   | Copy of the IDSEL signal from the PCI bus, delayed by one clock.   |

Table 4: QL58x0 Target QuickPCI Family Members

|          |                | QL5810 | QL5820  | QL5840  |

|----------|----------------|--------|---------|---------|

| Max      | Max Gates      |        | 188,946 | 320,640 |

| Logi     | ic Cells       | 192    | 575     | 1,472   |

| Max F    | lip-Flops      | 630    | 1,455   | 3,748   |

| Ma       | ax I/O         | 78     | 97      | 264     |

| RAM      | Modules        | 2      | 14      | 22      |

| RA       | RAM Bits       |        | 32,256  | 50,688  |

| F        | PLLs           | -      | -       | 4       |

| E        | CUs            | -      | -       | 12      |

|          | TQFP           | 144    | 144     | -       |

|          | TFBGA (0.8 mm) | 196    | 196     | -       |

| Packages | PQFP           | -      | 208     | 208     |

|          | LFBGA (0.8 mm) | -      | 280     | 280     |

|          | PBGA (1.0 mm)  | -      | -       | 484     |

Table 5: Max I/O per Device/Package Combination

| Device | 144 TQFP | 196 TFBGA | 208 PQFP | 280 LFBGA | 484 PBGA |

|--------|----------|-----------|----------|-----------|----------|

| QL5810 | 54       | 78        | -        | -         | -        |

| QL5820 | 54       | 78        | 97       | 117       | -        |

| QL5840 | -        | -         | 69       | 117       | 264      |

NOTE: All devices support 33 MHz and 66 MHz PCI except QL5840-PQ208 which supports 33 MHz PCI only.

### **QuickWorks Design Software**

The QuickWorks® package provides the most complete ESP and FPGA software solution from design entry to logic synthesis, to place and route, to power calculation, and simulation. The package provides a solution for designers who use third-party tools from Cadence, Mentor, OrCAD, Synopsys, Viewlogic, and other third-party tools for design entry, synthesis, or simulation.

#### **Process Data**

The QL58x0 device family is fabricated on a 0.18  $\mu$ , six layer metal CMOS process. The core voltage is 1.8 V and the I/Os are up to 3.3 V drive/tolerant. The QL58x0 device family product line is available in commercial, industrial, and military temperature grades.

### **Programmable Logic Architectural Overview**

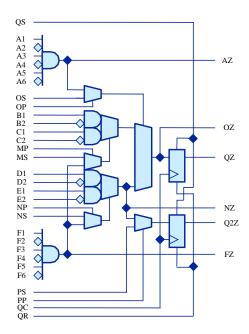

The QL58x0 device family logic cell structure is presented in **Figure 3**. This architectural feature addresses today's register-intensive designs.

| Function            | Description | Slowest Speed Grade | Fastest Speed Grade |

|---------------------|-------------|---------------------|---------------------|

| Multiplexer         | 16:1        | 2.8 ns              | 2.4 ns              |

| Parity Tree         | 24          | 3.4 ns              | 2.9 ns              |

| railly liee         | 36          | 4.6 ns              | 3.9 ns              |

| Counter             | 16 bit      | 275 MHz             | 328 MHz             |

|                     | 32 bit      | 250 MHz             | 300 MHz             |

| 0 1                 | 128 x 32    | 197 MHz             | 235 MHz             |

| Synchronous<br>FIFO | 128 x 64    | 188 MHz             | 266 MHz             |

| 0                   | 256 x 16    | 208 MHz             | 248 MHz             |

| Clock-to-Out        |             | 6.5 ns              | 6 ns                |

| System clock        |             | 200 MHz             | 300 MHz             |

Table 6: Performance Standards<sup>a</sup>

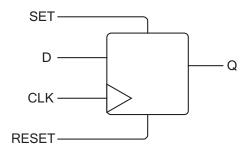

The QL58x0 device family logic cell structure presented in **Figure 3** is a dual register, multiplexer-based logic cell. It is designed for wide fan-in and multiple, simultaneous output functions. Both registers share CLK, SET, and RESET inputs. The second register has a two-to-one multiplexer controlling its input. The register can be loaded from the NZ output or directly from a dedicated input.

**NOTE:** The input PP is not an "input" in the classical sense. It is a static input to the logic cell and selects which path (NZ or PS) is used as an input to the Q2Z register. All other inputs are dynamic and can be connected to multiple routing channels.

The complete logic cell consists of two six-input AND gates, four two-input AND gates, seven two-to-one multiplexers, and two D flip-flops with asynchronous SET and RESET controls. The cell has a fan-in of 30 (including register control lines), fits a wide range of functions with up to 17 simultaneous inputs, and has six outputs (four combinatorial and two registered). The high logic capacity and fan-in of the logic cell accommodates many user functions with a single level of logic delay while other architectures require two or more levels of delay.

a. Performance standards for worst-case commercial conditions.

Figure 3: QL58x0 Device Family Logic Cell

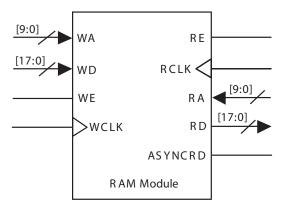

### **RAM Modules**

The QL58x0 device family includes up to 24 dual-port 2,304-bit RAM modules for implementing RAM, ROM, and FIFO functions. Each module is user-configurable into two different block organizations and can be cascaded horizontally to increase their effective width, or vertically to increase their effective depth as shown in **Figure 5**.

MODE[1:0] ASYNCRD

WA[7:0] RA[7:0]

WD[17:0] RD[17:0]

WE RE

WCLK RCLK

Figure 4: 2,304-bit RAM Module

The number of RAM modules varies from 4 to 24 blocks for a total of 9.2 K to 55.3 K bits of RAM. Using the two "mode" pins, designers can configure each module into 128 x 18 and 256 x 9. The blocks are also easily cascadable to increase their effective width and/or depth (see **Figure 5**).

WDATA

RAM

Module

(2,304 bits)

RADDR

RAM

Module

(2,304 bits)

RAM

Module

(2,304 bits)

RDATA

Figure 5: Cascaded RAM Modules

The RAM modules are dual-port, with completely independent READ and WRITE ports and separate READ and WRITE clocks. The READ ports support asynchronous and synchronous operation, while the WRITE ports support synchronous operation. Each port has 18 data lines and 8 address lines, allowing word lengths of up to 18 bits and address spaces of up to 256 words. Depending on the mode selected, however, some higher order data or address lines may not be used.

The Write Enable (WE) line acts as a clock enable for synchronous write operation. The Read Enable (RE) acts as a clock enable for synchronous READ operation (ASYNCRD input low), or as a flow-through enable for asynchronous READ operation (ASYNCRD input high).

Designers can cascade multiple RAM modules to increase the depth or width allowed in single modules by connecting corresponding address lines together and dividing the words between modules.

A similar technique can be used to create depths greater than 256 words. In this case address signals higher than the MSB are encoded onto the write enable (WE) input for WRITE operations. The READ data outputs are multiplexed together using encoded higher READ address bits for the multiplexer SELECT signals.

The RAM blocks can be loaded with data generated internally (typically for RAM or FIFO functions) or with data from an external PROM (typically for ROM functions).

© 2005 QuickLogic Corporation

# **Embedded Computational Unit (ECU)**

Traditional Programmable Logic architectures do not implement arithmetic functions efficiently or effectively—these functions require high logic cell usage while garnering only moderate performance results.

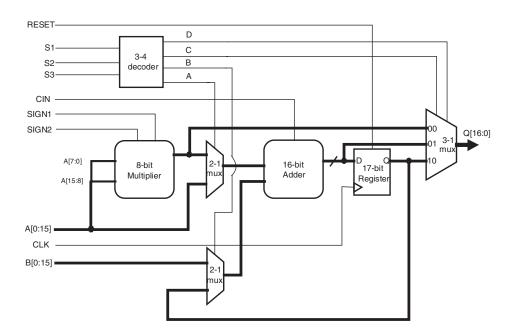

The QL58x0 device family architecture allows for functionality above and beyond that achievable using programmable logic devices. By embedding a dynamically reconfigurable computational unit, the QL58x0 device family can address various arithmetic functions efficiently. This approach offers greater performance and utilization than traditional programmable logic implementations. The embedded block is implemented at the transistor level as shown in **Figure 6**.

Figure 6: ECU Block Diagram

The QL58x0 device family ECU blocks (**Table 7**) are placed next to the SRAM circuitry for efficient memory/instruction fetch and addressing for DSP algorithmic implementations.

Device

ECUs

QL5840

12

QL5820

0

QL5810

0

Table 7: QL58x0 Device Family ECU Blocks

Up to twelve 8-bit MAC functions can be implemented per cycle for a total of 1 billion MACs/s when clocked at 100 MHz. Additional multiply-accumulate functions can be implemented in the programmable logic.

The modes for the ECU block are dynamically re-programmable through the programmable logic.

Table 8: ECU Mode Select Criteria

|    | Instruction |    | Operation                          | ECU P           | erformance <sup>a</sup> , -8 \ | NCC             |

|----|-------------|----|------------------------------------|-----------------|--------------------------------|-----------------|

| S1 | S2          | S3 | Operation                          | t <sub>PD</sub> | t <sub>su</sub>                | t <sub>co</sub> |

| 0  | 0           | 0  | Multiply                           | 6.6 ns max      |                                |                 |

| 0  | 0           | 1  | Multiply-Add                       | 8.8 ns max      |                                |                 |

| 0  | 1           | 0  | Accumulate <sup>b</sup>            |                 | 3.9 ns min                     | 1.2 ns max      |

| 0  | 1           | 1  | Add                                | 3.1 ns max      |                                |                 |

| 1  | 0           | 0  | Multiply (registered) <sup>c</sup> |                 | 9.6 ns min                     | 1.2 ns max      |

| 1  | 0           | 1  | Multiply- Add (registered)         |                 | 9.6 ns min                     | 1.2 ns max      |

| 1  | 1           | 0  | Multiply - Accumulate              |                 | 9.6 ns min                     | 1.2 ns max      |

| 1  | 1           | 1  | Add (registered)                   |                 | 3.9 ns min                     | 1.2 ns max      |

a.  $t_{\mbox{\footnotesize{PD}}},\,t_{\mbox{\footnotesize{SU}}}$  and  $t_{\mbox{\footnotesize{CO}}}$  do not include routing paths in/out of the ECU block.

**NOTE:** Timing numbers in **Table 8** represent -8 Worst Case Commercial conditions.

b. Internal feedback path in ECU restricts max clk frequency to 238 MHz.

c. B [15:0] set to zero.

# **Phase Locked Loop (PLL) Information**

Instead of requiring extra components, designers simply need to instantiate one of the pre-configured models (described in this section). The QuickLogic built-in PLLs support a wider range of frequencies than many other PLLs. These PLLs also have the ability to support different ranges of frequency multiplications or divisions, driving the device at a faster or slower rate than the incoming clock frequency. When PLLs are cascaded, the clock signal must be routed off-chip through the PLLPAD\_OUT pin prior to routing into another PLL; internal routing cannot be used for cascading PLLs.

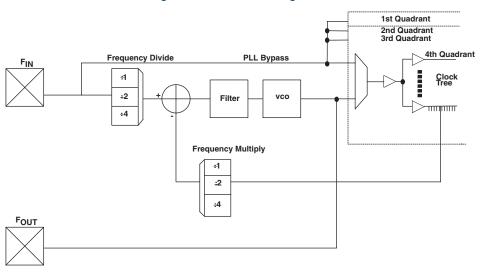

Figure 7 illustrates a QuickLogic PLL.

Figure 7: PLL Block Diagram

$F_{in}$  represents a very stable high-frequency input clock and produces an accurate signal reference. This signal can either bypass the PLL entirely, thus entering the clock tree directly, or it can pass through the PLL itself.

Within the PLL, a voltage-controlled oscillator (VCO) is added to the circuit. The external  $F_{\rm in}$  signal and the local VCO form a control loop. The VCO is multiplied or divided down to the reference frequency, so that a phase detector (the crossed circle in **Figure 7**) can compare the two signals. If the phases of the external and local signals are not within the tolerance required, the phase detector sends a signal through the charge pump and loop filter (**Figure 7**). The charge pump generates an error voltage to bring the VCO back into alignment, and the loop filter removes any high frequency noise before the error voltage enters the VCO. This new VCO signal enters the clock tree to drive the chip's circuitry.

$F_{out}$  represents the clock signal emerging from the output pad (the output signal PLLPAD\_OUT is explained in **Table 10**). The PLL always drives the PLLPAD\_OUT signal, regardless of whether the PLL is configured for on-chip use. The PLLPAD\_OUT will not oscillate if PLL\_RESET is asserted, or if the PLL is powered down.

Most QuickLogic products contain four PLLs. The PLL presented in **Figure 7** controls the clock tree in the fourth quadrant of its FPGA. QuickLogic PLLs compensate for the additional delay created by the clock tree itself, as previously noted, by subtracting the clock tree delay through the feedback path.

### **PLL Modes of Operation**

QuickLogic PLLs have eight modes of operation, based on the input frequency and desired output frequency—**Table 9** indicates the features of each mode.

NOTE: "HF" stands for "high frequency" and "LF" stands for "low frequency."

Table 9: PLL Mode Frequencies

| PLL Model   | Output Frequency | Input Frequency Range | Output Frequency Range |

|-------------|------------------|-----------------------|------------------------|

| PLL_HF      | Same as input    | 66 MHz-220 MHz        | 66 MHz-220 MHz         |

| PLL_LF      | Same as input    | 25 MHz-66 MHz         | 25 MHz-66 MHz          |

| PLL_MULT2HF | 2x               | 33 MHz-110 MHz        | 66 MHz-220 MHz         |

| PLL_MULT2LF | 2x               | 12.5 MHz-33 MHz       | 25 MHz-66 MHz          |

| PLL_DIV2HF  | 1/2x             | 220 MHz-440 MHz       | 110 MHz-220 MHz        |

| PLL_DIV2LF  | 1/2x             | 50 MHz-220 MHz        | 25 MHz-110 MHz         |

| PLL_MULT4   | 4x               | 12.5 MHz-50 MHz       | 50 MHz-200 MHz         |

| PLL_DIV4    | 1/4x             | 100 MHz-440 MHz       | 25 MHz-110 MHz         |

The input frequency can range from 12.5 MHz to 440 MHz, while output frequency ranges from 25 MHz to 220 MHz. When adding PLLs to the top-level design, be sure that the PLL mode matches the desired input and output frequencies.

### **PLL Signals**

**Table 10** summarizes the key signals in QuickLogic PLLs.

Table 10: QuickLogic PLL Signals

| Signal Name | Description                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLCLK_IN   | Input clock signal                                                                                                                                                                                                                           |

| PLL_RESET   | <b>Active High Reset</b> If PLL_RESET is asserted, then CLKNET_OUT and PLLPAD_OUT are reset to 0. This signal must be asserted and then released in order for the LOCK_DETECT to work.                                                       |

| ONn_OFFCHIP | This is a reserved signal. It can be connected to VCC or GND.                                                                                                                                                                                |

| CLKNET_OUT  | Out to internal gates This signal bypasses the PLL logic before driving the internal gates. Note that this signal cannot be used in the same quadrant where the PLL signal is used (PLLCLK_OUT).                                             |

| PLLCLK_OUT  | Out from PLL to internal gates This signal can drive the internal gates after going through the PLL.                                                                                                                                         |

| PLLPAD_OUT  | Out to off-chip This outgoing signal is used off-chip. The PLLPAD_OUT is always active, driving the PLL-derived clock signal out through the pad. The PLLPAD_OUT will not oscillate if PLL_RESET is asserted, or if the PLL is powered down. |

| LOCK_DETECT | Active High Lock detection signal  NOTE: For simulation purposes, this signal gets asserted after 10 clock cycles. However, it can take a maximum of 200 clock cycles to sync with the input clock upon release of the PLL_RESET signal.     |

**NOTE:** Because PLLCLK\_IN and PLL\_RESET signals have PLL\_INPAD, and PLLPAD\_OUT has OUTPAD, you do not need to add additional pads to your design.

### I/O Cell Structure

The QL58x0 device family features a variety of distinct I/O pins to maximize performance, functionality, and flexibility with bi-directional I/O pins and input-only pins. All input and I/O pins are 1.8 V, 2.5 V, and 3.3 V tolerant and comply with the specific I/O standard selected. For single ended I/O standards, VCCIO specifies the input tolerance and the output drive. For voltage referenced I/O standards (e.g SSTL), the voltage supplied to the INREF pins in each bank specifies the input switch point. For example, the VCCIO pins must be tied to a 3.3 V supply to provide 3.3 V compliance. The QL58x0 device family can also support the LVDS and LVPECL I/O standards with the use of external resistors (see **Table 11**).

| I/O Standard | Reference Voltage | Output Voltage | Application          |

|--------------|-------------------|----------------|----------------------|

| LVTTL        | n/a               | 3.3 V          | General Purpose      |

| LVCMOS25     | n/a               | 2.5 V          | General Purpose      |

| LVCMOS18     | n/a               | 1.8 V          | General Purpose      |

| PCI          | n/a               | 3.3 V          | PCI Bus Applications |

| GTL+         | 1                 | n/a            | Backplane            |

| SSTL3        | 1.5               | 3.3 V          | SDRAM                |

| SSTL2        | 1.25              | 2.5 V          | SDRAM                |

Table 11: I/O Standards and Applications

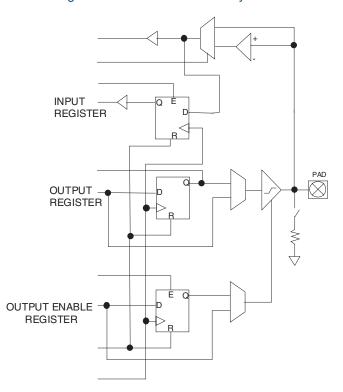

As designs become more complex and requirements more stringent, several application-specific I/O standards have emerged for specific applications. I/O standards for processors, memories, and a variety of bus applications have become commonplace and a requirement for many systems. In addition, I/O timing has become a greater issue with specific requirements for setup, hold, clock to out, and switching times. The QL58x0 device family has addressed these new system requirements and now includes a completely new I/O cell which consists of programmable I/Os as well as a new cell structure consisting of three registers—Input, Output, and OE.

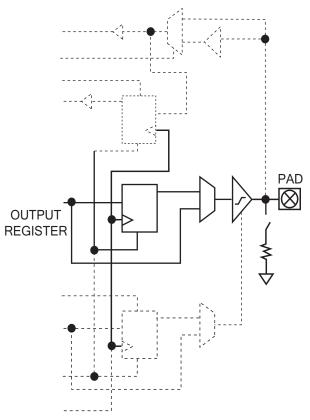

The QL58x0 device family offers banks of programmable I/Os that address many of the bus standards that are popular today. As shown in **Figure 8** each bi-directional I/O pin is associated with an I/O cell which features an input register, an input buffer, an output register, a three-state output buffer, an output enable register, and 2 two-to-one output multiplexers.

Figure 8: QL58x0 Device Family I/O Cell

The bi-directional I/O pin options can be programmed for input, output, or bi-directional operation. As shown in **Figure 8**, each bi-directional I/O pin is associated with an I/O cell which features an input register, an input buffer, an output register, a three-state output buffer, an output enable register, and 2 two-to-one multiplexers. The select lines of the two-to-one multiplexers are static and must be connected to either VCC or GND.

For input functions, I/O pins can provide combinatorial, registered data, or both options simultaneously to the logic array. For combinatorial input operation, data is routed from I/O pins through the input buffer to the array logic. For registered input operation, I/O pins drive the D input of input cell registers, allowing data to be captured with fast, predictable set-up times without consuming internal logic cell resources. The comparator and multiplexer in the input path allows for native support of I/O standards with reference points offset from traditional ground.

For output functions, I/O pins can receive combinatorial or registered data from the logic array. For combinatorial output operation, data is routed from the logic array through a multiplexer to the I/O pin. For registered output operation, the array logic drives the D input of the output cell register which in turn drives the I/O pin through a multiplexer. The multiplexer allows either a combinatorial or a registered signal to be driven to the I/O pin. The addition of an output register will also decrease the Tco. Since the output register does not need to drive the routing the length of the output path is also reduced, and static timing analysis becomes very predictable.

The three-state output buffer controls the flow of data from the array logic to the I/O pin and allows the I/O pin to act as an input and/or output. The buffer's output enable can be individually controlled by the logic cell array or any pin (through the regular routing resources), or it can be bank-controlled through one of the global networks. The signal can also be either combinatorial or registered. This is identical to that of the flow for the output cell. For combinatorial control operation, data is routed from the logic array through a multiplexer to the three-state control. The IOCTRL pins can directly drive the OE and CLK signals for all I/O cells within the same bank.

© 2005 QuickLogic Corporation

For registered control operation, the array logic drives the D input of the OE cell register which in turn drives the three-state control through a multiplexer. The multiplexer allows either a combinatorial or a registered signal to be driven to the three-state control.

When I/O pins are unused, the OE controls can be permanently disabled, allowing the output cell register to be used for registered feedback into the logic array.

I/O cell registers are controlled by clock, clock enable, and reset signals, which can come from the regular routing resources, from one of the global networks, or from two IOCTRL input pins per bank of I/O's. The CLK and RESET signals share common lines, while the clock enables for each register can be independently controlled. I/O interface support is programmable on a per bank basis.

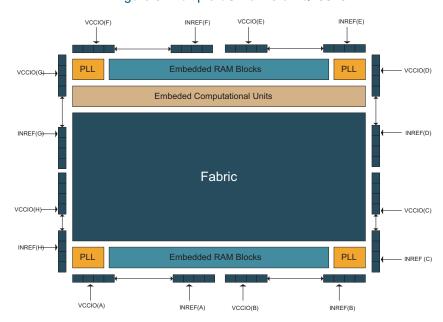

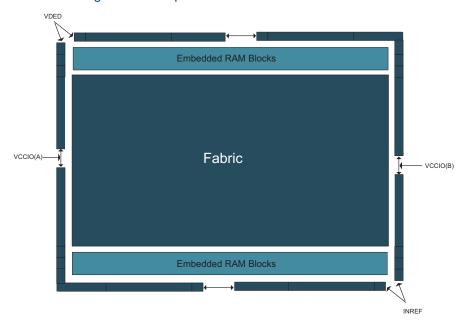

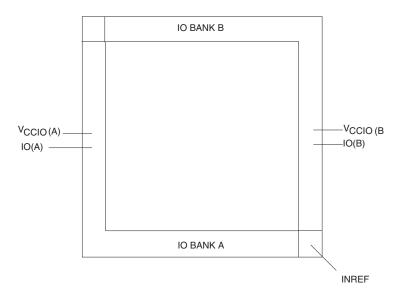

The two larger QL58x0 devices contain eight I/O banks. **Figure 9** illustrates the I/O bank configurations for QL5840. The two smaller QL58x0 devices contain two I/O banks per device. **Figure 10** illustrates the I/O bank configurations for QL5820 and QL5810.

Each I/O bank is independent of other I/O banks and each I/O bank has its own VCCIO and INREF supply inputs. A mixture of different I/O standards can be used on the device; however, there is a limitation as to which I/O standards can be supported within a given bank. Only standards that share a common VCCIO and INREF can be shared within the same bank (e.g., PCI and LVTTL). In the case of the QL5820 and QL5810, only one voltage-referenced standard can be used. The two I/O banks, A and B, share the INREF pin.

Figure 9: Multiple I/O Banks on QL5840

Figure 10: Multiple I/O Banks on QL5820 and 5810

# **Programmable Slew Rate**

Each I/O has programmable slew rate capability—the slew rate can be either fast or slow. The slower rate can be used to reduce the switching times of each I/O.

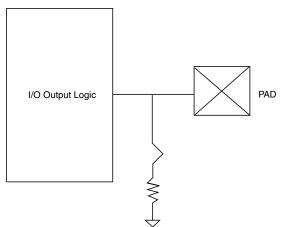

### **Programmable Weak Pull-Down**

A programmable Weak Pull-Down resistor is available on each I/O. The I/O Weak Pull-Down eliminates the need for external pull down resistors for used I/Os as shown in **Figure 11**. The spec for pull-down current is maximum of  $150~\mu A$  under worst case condition.

Figure 11: Programmable I/O Weak Pull-Down

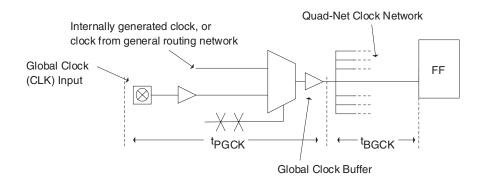

### **Clock Networks**

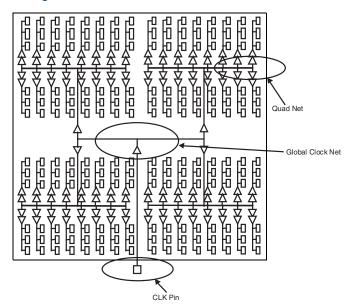

### **Global Clocks**

There are a maximum of seven global clock networks in each QL58x0 device. Global clocks can drive logic cells and I/O registers, ECUs, and RAM blocks in the device. All global clocks have access to a Quad Net (local clock network) connection with a programmable connection to the logic cell's register clock input.

Figure 12: Global Clock Architecture

### **Quad-Net Network**

There are five Quad-Net local clock networks in each quadrant for a total of 20 in a device. Each Quad-Net is local to a quadrant. Before driving the column clock buffers, the quad-net is driven by the output of a mux which selects between the CLK pin input and an internally generated clock source (see **Figure 13**).

Figure 13: Global Clock Structure

© 2005 QuickLogic Corporation www.quicklogic.com

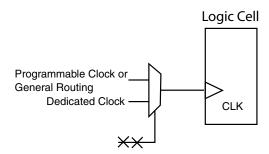

#### **Dedicated Clock**

There is one dedicated clock in the larger device of the QL58x0 family (QL5840). This clock connects to the clock input of the Logic Cell and I/O registers, and RAM blocks through a hardwired connection and is multiplexed with the programmable clock input. The dedicated clock provides a fast global network with low skew. Users have the ability to select either the dedicated clock or the programmable clock (**Figure 14**).

Figure 14: Dedicated Clock Circuitry within Logic Cell

**NOTE:** For more information on the clocking capabilities of the QL58x0 Enhanced QuickPCI Family, see QuickLogic Application Note 68 at <a href="http://www.quicklogic.com/images/appnote68.pdf">http://www.quicklogic.com/images/appnote68.pdf</a>.

#### I/O Control and Local Hi-Drives

Each bank of I/Os has two input-only pins that can be programmed to drive the RST, CLK, and EN inputs of I/Os in that bank. These input-only pins also serve as high drive inputs to a quadrant. These buffers can be driven by the internal logic both as an I/O control or high drive. For I/O constrained designs, these pins can be used for general purpose inputs. To provide more general purpose I/Os in the 208 PQFP package, the I/O controls pins are not bonded out. The performance of these resources is presented in **Table 12**.

Table 12: I/O Control Network/Local High-Drive

| Destination<br>TT, 25 C, 2.5 V | From Pad | From Array |

|--------------------------------|----------|------------|

| I/O (far)                      | 1.00 ns  | 1.14 ns    |

| I/O (near)                     | 0.63 ns  | 0.78 ns    |

| Skew                           | 0.37 ns  | 0.36 ns    |

**Table 13** shows the total number of I/O control pins per device/package combination. These pins are not bonded out in the smaller devices and packages. This increases the number of bi-directional user I/Os available.

Table 13: I/O Control Pins per Device/Package Combination

| Device | 144 TQFP | 196 TFBGA | 208 PQFP | 280 LFBGA | 484 BGA |

|--------|----------|-----------|----------|-----------|---------|

| QL5810 | -        | -         | -        | -         | -       |

| QL5820 | -        | -         | -        | -         | -       |

| QL5840 | -        | -         | -        | 16        | 16      |

# **Programmable Logic Routing**

QL58x0 devices are engineered with six types of routing resources as follows: short (sometimes called segmented) wires, dual wires, quad wires, express wires, distributed networks, and default wires. Short wires span the length of one logic cell, always in the vertical direction. Dual wires run horizontally and span the length of two logic cells. Short and dual wires are predominantly used for local connections. Default wires supply VCC and GND (Logic '1' and Logic '0') to each column of logic cells.

Quad wires have passive link interconnect elements every fourth logic cell. As a result, these wires are typically used to implement intermediate length or medium fan-out nets.

Express lines run the length of the device uninterrupted. Each of these lines has a higher capacitance than a quad, dual, or short wire, but less capacitance than shorter wires connected to run the length of the device. The resistance will also be lower because the express wires don't require the use of pass links. Express wires provide higher performance for long routes or high fan-out nets.

Distributed networks are described in **Clock Networks** on page 19. These wires span the programmable logic and are driven by quad-net buffers.

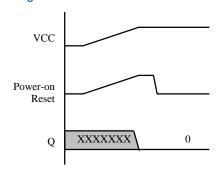

# **Global Power-On Reset (POR)**

The QL58x0 device family features a global power-on reset. This reset is hardwired to all registers and resets them to Logic '0' upon power-up of the device. In QuickLogic devices, the asynchronous Reset input to flip-flops has priority over the Set input; therefore, the Global POR will reset all flip-flops during power-up. If you want to set the flip-flops to Logic '1', you must assert the "Set" signal after the Global POR signal has been deasserted.

Figure 15: Power-On Reset

### **Low Power Mode**

Quiescent power consumption of all QL58x0 family devices can be reduced significantly by de-activating the charge pumps inside the architecture. By applying 3.3 V to the VPUMP pin, the internal charge pump is de-activated—this effectively reduces the static and dynamic power consumption of the device. The QL58x0 device family is fully functional and operational in the Low Power mode. Users who have a 3.3 V supply available in their system should take advantage of this low power feature by tying the VPUMP pin to 3.3 V. Otherwise, if a 3.3 V supply is not available, this pin should be tied to ground.

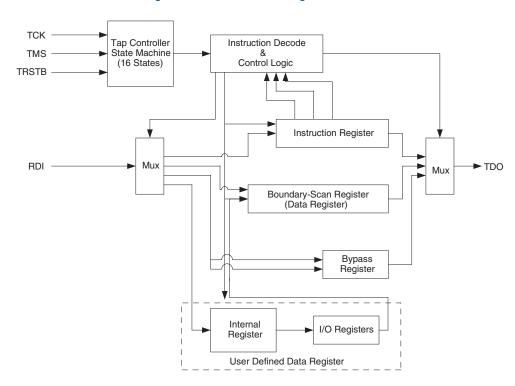

# Joint Test Access Group (JTAG) Information

Figure 16: JTAG Block Diagram

Microprocessors and Application Specific Integrated Circuits (ASICs) pose many design challenges, one problem being the accessibility of test points. JTAG formed in response to this challenge, resulting in IEEE standard 1149.1, the Standard Test Access Port and Boundary Scan Architecture.

The JTAG boundary scan test methodology allows complete observation and control of the boundary pins of a JTAG-compatible device through JTAG software. A Test Access Port (TAP) controller works in concert with the Instruction Register (IR), which allow users to run three required tests along with several user-defined tests.

JTAG tests allow users to reduce system debug time, reuse test platforms and tools, and reuse subsystem tests for fuller verification of higher level system elements.

The 1149.1 standard requires the following three tests:

22

- Extest Instruction. The Extest Instruction performs a printed circuit board (PCB) interconnect test. This test places a device into an external boundary test mode, selecting the boundary scan register to be connected between the TAP Test Data In (TDI) and Test Data Out (TDO) pins. Boundary scan cells are preloaded with test patterns (through the Sample/Preload Instruction), and input boundary cells capture the input data for analysis.

- **Sample/Preload Instruction.** The Sample/Preload Instruction allows a device to remain in its functional mode, while selecting the boundary scan register to be connected between the TDI and TDO pins. For this test, the boundary scan register can be accessed through a data scan operation, allowing users to sample the functional data entering and leaving the device.

• **Bypass Instruction.** The Bypass Instruction allows data to skip a device boundary scan entirely, so the data passes through the bypass register. The Bypass instruction allows users to test a device without passing through other devices. The bypass register is connected between the TDI and TDO pins, allowing serial data to be transferred through a device without affecting the operation of the device.

### **JTAG BSDL Support**

- BSDL-Boundary Scan Description Language

- Machine-readable data for test equipment to generate testing vectors and software

- BSDL files available for all device/package combinations from QuickLogic

- Extensive industry support available and ATVG (Automatic Test Vector Generation)

### **Security Links**

There are several security links to disable reading logic from the array, and to disable JTAG access to the device. Programming these optional links completely disables access to the device from the outside world and provides an extra level of design security not possible in SRAM-based FPGAs. The option to program these links is selectable through QuickWorks in the Tools/Options/Device Programming window in SpDE.

### **Power-Up Loading Link**

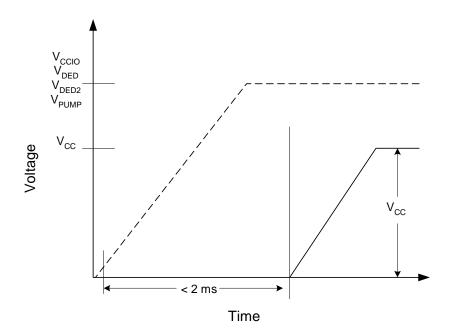

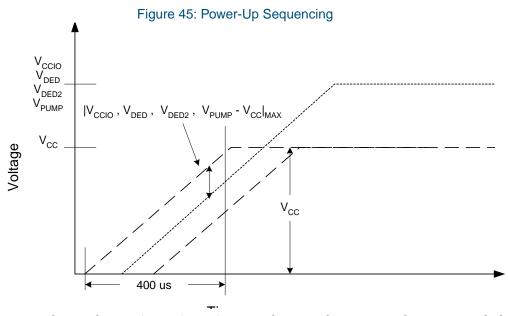

The flexibility link enables Power-Up Loading of the Embedded RAM blocks. If the link is programmed, the Power-Up Loading state machine is activated during power-up of the device. The state machine communicates with an external EPROM via the JTAG pins to download memory contents into the on-chip RAM. If the link is not programmed, Power-Up Loading is not enabled and the JTAG pins function as they normally would. The option to program this link is selectable through QuickWorks in the Tools/Options/Device Programming window in SpDE. For more information on Power-Up Loading, see QuickLogic Application Note 55 at <a href="http://www.quicklogic.com/images/appnote55.pdf">http://www.quicklogic.com/images/appnote55.pdf</a>. See the Power-Up Loading power-up sequencing requirement for proper functionality in Figure 17.

Figure 17: Required Power-Up Sequence When Using Power-Up Loading

To use the power-up loading function in QL58x0, designers must ensure that  $V_{CC}$  begins to ramp within a maximum of 2 ms of  $V_{CCIO}$ ,  $V_{DED}$ ,  $V_{DED2}$ , and  $V_{PUMP}$

<u>www.quicklogic.com</u> © 2005 QuickLogic Corporation

# **Electrical Specifications**

### **DC Characteristics**

The DC Specifications are provided in Table 14 through Table 18.

Table 14: Absolute Maximum Ratings

| Parameter     | Value                   | Parameter                                  | Value              |

|---------------|-------------------------|--------------------------------------------|--------------------|

| VCC Voltage   | -0.5 V to 2.0 V         | Latch-up Immunity                          | ±100 mA            |

| VCCIO Voltage | -0.5 V to 4.0 V         | DC Input Current                           | ±20 mA             |

| INREF Voltage | 0.5 V to VCCIO          | Leaded Package<br>Storage Temperature      | -65° C to + 150° C |

| Input Voltage | -0.5 V to VCCIO + 0.5 V | Laminate Package (BGA) Storage Temperature | -55° C to + 125° C |

Table 15: Recommended Operating Range

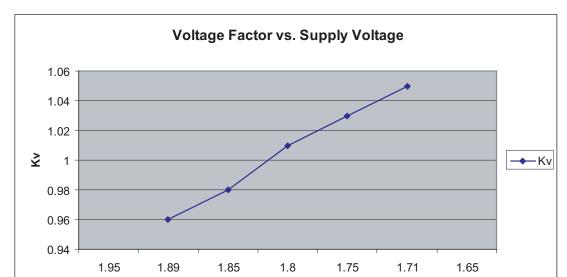

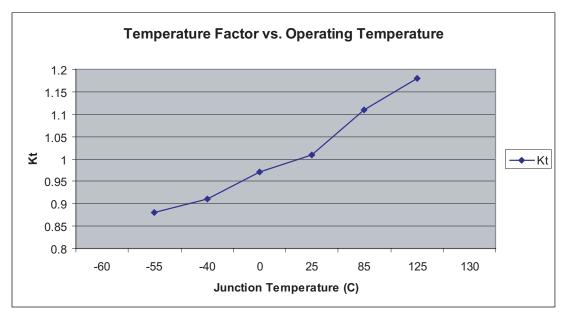

| Symbol      | Parameter                   |                  | Military |      | Industrial |      | Commercial |      | Unit |

|-------------|-----------------------------|------------------|----------|------|------------|------|------------|------|------|

| Зушьог      |                             | ameter           | Min      | Max  | Min        | Max  | Min        | Max  |      |

| VCC         | Supply Voltage              |                  | 1.71     | 1.89 | 1.71       | 1.89 | 1.71       | 1.89 | V    |

| VCCIO       | I/O Input Tolerance Voltage |                  | 1.71     | 3.60 | 1.71       | 3.60 | 1.71       | 3.60 | V    |

| TJ          | Junction Temperature        |                  | -55      | 125  | -40        | 100  | 0          | 85   | °C   |

| K Delay Fac |                             | -33A Speed Grade | 0.49     | 1.57 | 0.50       | 1.51 | 0.54       | 1.47 | n/a  |

|             | Delay Factor                | -33B Speed Grade | 0.48     | 1.40 | 0.50       | 1.34 | 0.53       | 1.31 | n/a  |

|             | -66C Speed Grade            |                  | 0.45     | 1.32 | 0.47       | 1.26 | 0.50       | 1.23 | n/a  |

Table 16: DC Characteristics

| Symbol             | Parameter                                 | Conditions                                      | Min       | Max            | Units    |

|--------------------|-------------------------------------------|-------------------------------------------------|-----------|----------------|----------|

| l <sub>l</sub>     | I or I/O Input Leakage Current            | VI = VCCIO or GND                               | -1        | 1              | μA       |

| l <sub>oz</sub>    | 3-State Output Leakage Current            | VI = VCCIO or GND                               | -         | 1              | μA       |

| Cı                 | I/O Input Capacitance                     | -                                               | -         | 8              | pF       |

| C <sub>CLOCK</sub> | Clock Input Capacitance                   | -                                               | -         | 8              | pF       |

| I <sub>os</sub>    | Output Short Circuit Current <sup>a</sup> | VO = GND<br>VO = VCC                            | -15<br>40 | -180<br>210    | mA<br>mA |

| I <sub>REF</sub>   | Quiescent Current on INREF                | -                                               | -10       | 10             | μA       |

| I <sub>PD</sub>    | Current on programmable pull-down         | VCC = 1.8 V                                     | -         | 50             | μA       |

| I <sub>PUMP</sub>  | Quiescent Current on VPUMP                | VPUMP= 3.3 V                                    | -         | 10             | μA       |

| I <sub>PLL</sub>   | Quiescent Current on each VCCPLL          | 2.5 V<br>3.3 V                                  | -         | 3              | mA       |

| I <sub>VCCIO</sub> | Quiescent Current on VCCIO                | VCCIO = 3.6 V<br>VCCIO = 2.5 V<br>VCCIO = 1.8 V | -         | 20<br>10<br>10 | μΑ       |

a. Only one output at a time. Duration should not exceed 30 seconds.

Table 17: Quiescent ICC Characteristics

| Device                 | VPUMP = 0 V | <b>VPUMP = 3.3 V</b> |

|------------------------|-------------|----------------------|

| QL5810                 | -           | -                    |

| QL5820                 | -           | -                    |

| QL5840 <sup>a, b</sup> | 2 mA        | -                    |

a. For -33B/-66C commercial grade devices only. Maximum Quiescent ICC is 3 mA for all industrial grade devices and 5 mA for all military devices.

b. Quiescent ICC is for current drawn by VCC and VDED. If any PLLs are used, see **Table 16** for current drawn by each PLL.

INREF V<sub>IL</sub> V<sub>IH</sub> V<sub>OL</sub> V<sub>OH</sub> loL I<sub>OH</sub> **Symbol** V<sub>MIN</sub>  $V_{MAX}$ V<sub>MIN</sub> V<sub>MIN</sub>  $V_{MAX}$ V<sub>MAX</sub> V<sub>MIN</sub> mΑ mΑ **V**<sub>MAX</sub> VCCIO + 0.3LVTTL n/a n/a -0.3 8.0 2.2 0.4 2.4 2.0 -2.0 VCCIO + 0.3 LVCMOS2 -0.3 0.7 1.7 0.7 1.7 -2.0 n/a n/a 2.0 LVCMOS18 -0.3 0.63 1.2 VCCIO + 0.3 0.7 1.7 -2.0 n/a n/a 2.0 GTL+ 0.88 1.12 -0.3 INREF - 0.2 INREF + 0.2 VCCIO + 0.3 0.6 n/a 40 n/a PCI 0.3 x VCCIO VCCIO + 0.5 | 0.1 x VCCIO | 0.9 x VCCIO n/a -0.3  $0.6 \times V_{CCIO}$ 1.5 -0.5 n/a SSTL2 1.15 -0.3 INREF - 0.18 INREF + 0.18 VCCIO + 0.30.74 1.76 1.35 7.6 -7.6 SSTL3 1.3 1.7 -0.3 INREF - 0.2 INREF + 0.2 VCCIO + 0.31.10 1.90

Table 18: DC Input and Output Levels<sup>a</sup>

**NOTE:** All CLK, IOCTRL, and PLLIN pins are clamped to the VDED rail. Therefore, these pins can be driven up to VDED. All JTAG inputs are clamped to the VDED2 rail. These JTAG input pins can only be driven up to VDED2.

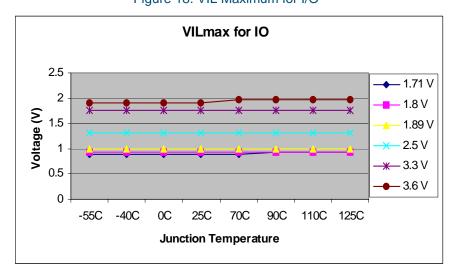

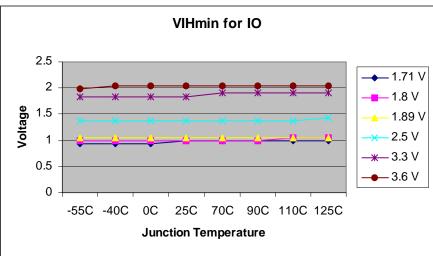

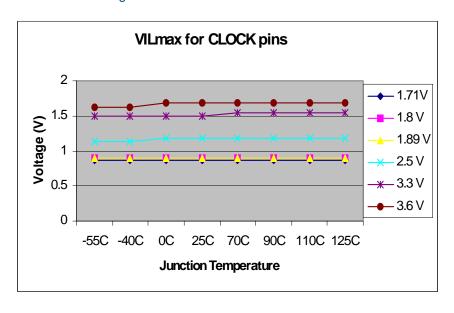

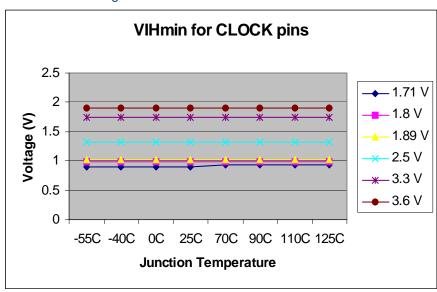

Figure 18 through Figure 21 show the VIL and VIH characteristics for I/O and clock pins.

Figure 18: VIL Maximum for I/O

© 2005 QuickLogic Corporation www.quicklogic.com

a. The data provided in Table 18 represents the JEDEC and PCI specification. QuickLogic devices either meet or exceed these requirements. For data specific to QuickLogic I/Os, see Table 22 through Table 28, Figure 8 and Figure 11, and Figure 39 through Figure 42.

Figure 19: VIH Minimum for I/O

www.quicklogic.com © 2005 QuickLogic Corporation

Figure 21: VIH Minimum for CLOCK Pins

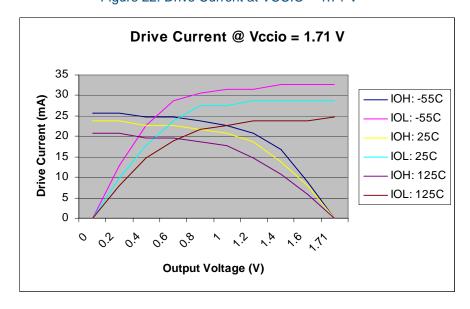

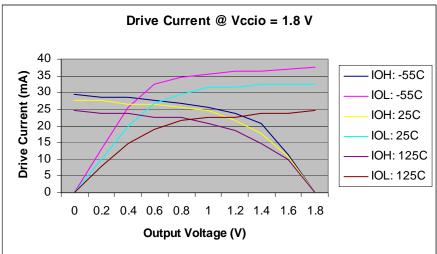

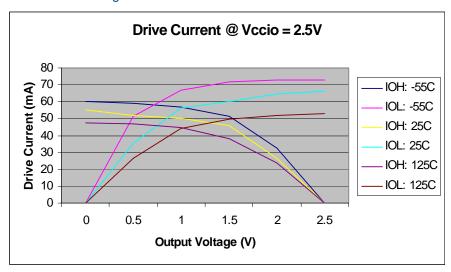

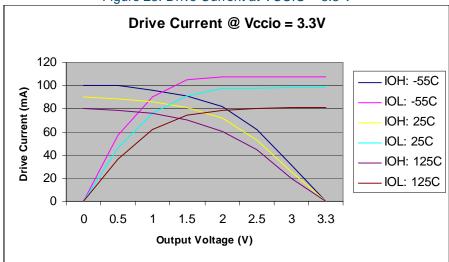

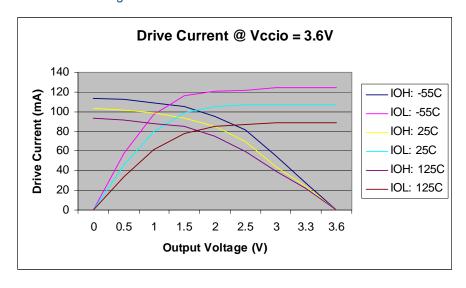

**Figure 22** through **Figure 26** show the output drive characteristics for the I/Os across various voltages and temperatures.

Figure 22: Drive Current at VCCIO = 1.71 V

© 2005 QuickLogic Corporation www.quicklogic.com

Figure 23: Drive Current at VCCIO = 1.8 V

www.quicklogic.com © 2005 QuickLogic Corporation

Figure 25: Drive Current at VCCIO = 3.3 V

© 2005 QuickLogic Corporation www.quicklogic.com

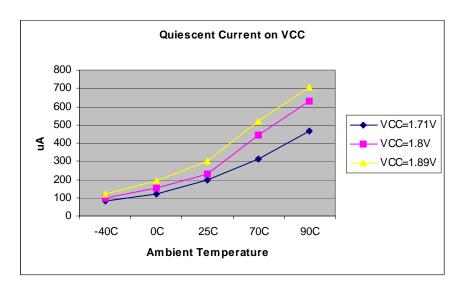

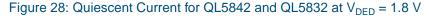

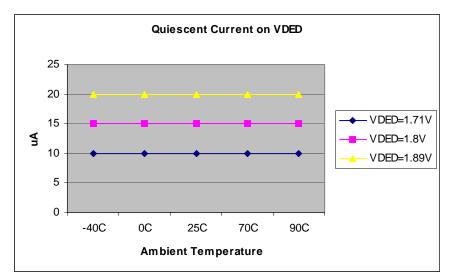

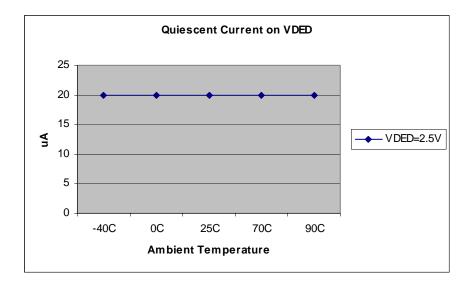

Figure 27 through Figure 30 show the quiescent current for the QL5842 and QL5832 for each of the voltage supplies, across voltage and temperature. Quiescent current on  $V_{\rm CC}$  is a function of device utilization. The numbers in the following graphs were taken from 100% utilized designs.

Figure 27: Quiescent Current on V<sub>CC</sub> for QL5842 and QL5832

www.quicklogic.com © 2005 QuickLogic Corporation

Figure 29: Quiescent Current for QL5842 and QL5832 at  $V_{DED}$  = 3.3 V

Figure 30: Quiescent Current for QL5842 and QL5832 at  $V_{\rm DED}$  = 2.5 V

© 2005 QuickLogic Corporation www.quicklogic.com

### **AC Characteristics**

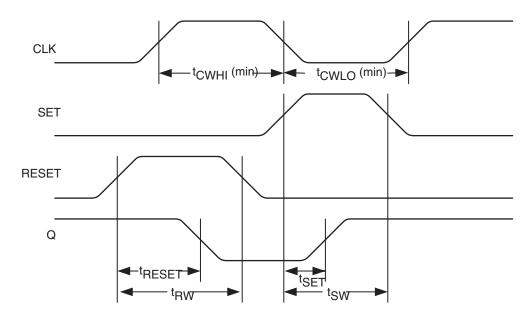

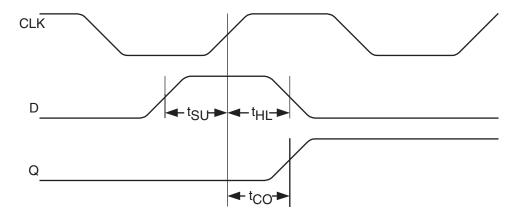

The AC Specifications (at VCC = 1.8 V, TA =  $25^{\circ}$  C, Worst Case Corner, Speed Grade = -8 (K = 1.01)) are provided from **Table 19** through **Table 28**. Logic Cell diagrams and waveforms are provided from **Figure 31** through **Figure 42**.

Figure 31: QL58x0 Device Family Logic Cell

Table 19: Logic Cells

| Cumbal             | Dovomotor                                                                                                       |         | Value   |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------|---------|---------|--|--|

| Symbol             | Parameter Parameter                                                                                             | Min     | Max     |  |  |

| t <sub>PD</sub>    | Combinatorial Delay of the longest path: time taken by the combinatorial circuit to output                      | 0.28 ns | 0.98 ns |  |  |

| t <sub>SU</sub>    | Setup time: time the synchronous input of the flip-flop must be stable before the active clock edge             | 0.10 ns | 0.25 ns |  |  |

| t <sub>HL</sub>    | Hold time: time the synchronous input of the flip-flop must be stable after the active clock edge               | 0 ns    | 0 ns    |  |  |

| t <sub>co</sub>    | Clock-to-out delay: the amount of time taken by the flip-flop to output after the active clock edge.            | 0.22 ns | 0.52 ns |  |  |

| t <sub>CWHI</sub>  | Clock High Time: required minimum time the clock stays high                                                     | 0.46 ns | 0.46 ns |  |  |

| t <sub>CWLO</sub>  | Clock Low Time: required minimum time that the clock stays low                                                  | 0.46 ns | 0.46 ns |  |  |

| t <sub>SET</sub>   | Set Delay: time between when the flip-flop is "set" (high) and when the output is consequently "set" (high)     | 0.69 ns | 0.69 ns |  |  |

| t <sub>RESET</sub> | Reset Delay: time between when the flip-flop is "reset" (low) and when the output is consequently "reset" (low) | 1.09 ns | 1.09 ns |  |  |

| t <sub>SW</sub>    | Set Width: time that the SET signal must remain high/low                                                        | 0.3 ns  | 0.3 ns  |  |  |

| t <sub>RW</sub>    | Reset Width: time that the RESET signal must remain high/low                                                    | 0.3 ns  | 0.3 ns  |  |  |

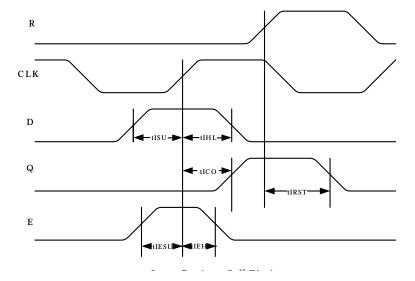

Figure 32: Logic Cell Flip-Flop

Figure 33: Logic Cell Flip-Flop Timings—First Waveform

Figure 34: Logic Cell Flip-Flop Timings—Second Waveform

© 2005 QuickLogic Corporation www.quicklogic.com

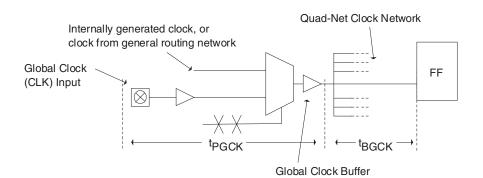

Table 20: QL58x0 Device Family Global Clock Delay

| Clock Segment     | Parameter                                       | Value |         |  |

|-------------------|-------------------------------------------------|-------|---------|--|

| Clock Segment     | Faiailietei                                     | Min   | Max     |  |

| t <sub>PGCK</sub> | Global clock pin delay to quad net              | -     | 1.92 ns |  |

| t <sub>BGCK</sub> | Global clock tree delay (quad net to flip-flop) | -     | 0.28 ns |  |

**NOTE:** When using a PLL, t<sub>PGCK</sub> and t<sub>BGCK</sub> are effectively zero due to delay adjustment by Phase Locked Loop feedback path.

Figure 35: Global Clock Structure Timing Elements

Figure 36: Dual-Port SRAM Cell

www.quicklogic.com © 2005 QuickLogic Corporation

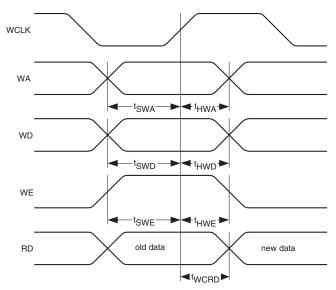

Table 21: RAM Cell Synchronous Write Timing

| Cumbal            | Parameter -                                                                                                  |         | Value   |  |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------|---------|--|

| Symbol            |                                                                                                              |         | Max     |  |

| RAM Cell S        | ynchronous Write Timing                                                                                      |         |         |  |

| t <sub>SWA</sub>  | WA setup time to WCLK: time the WRITE ADDRESS must be stable before the active edge of the WRITE CLOCK       | 0.47 ns | -       |  |

| t <sub>HWA</sub>  | WA hold time to WCLK: time the WRITE ADDRESS must be stable after the active edge of the WRITE CLOCK         | 0 ns    | -       |  |

| t <sub>SWD</sub>  | WD setup time to WCLK: time the WRITE DATA must be stable before the active edge of the WRITE CLOCK          | 0.48 ns | -       |  |

| t <sub>HWD</sub>  | WD hold time to WCLK: time the WRITE DATA must be stable after the active edge of the WRITE CLOCK            | 0 ns    | -       |  |

| t <sub>SWE</sub>  | WE setup time to WCLK: time the WRITE ENABLE must be stable before the active edge of the WRITE CLOCK        | 0 ns    | -       |  |

| t <sub>HWE</sub>  | WE hold time to WCLK: time the WRITE ENABLE must be stable after the active edge of the WRITE CLOCK          | 0 ns    | -       |  |

| t <sub>WCRD</sub> | WCLK to RD (WA = RA): time between the active WRITE CLOCK edge and the time when the data is available at RD | -       | 3.79 ns |  |

Figure 37: RAM Cell Synchronous Write Timing

© 2005 QuickLogic Corporation <u>www.quicklogic.com</u>

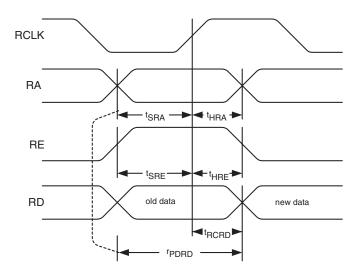

Table 22: RAM Cell Synchronous and Asynchronous Read Timing

| Cumbal            | Devenuelos                                                                                           |         | Value   |  |

|-------------------|------------------------------------------------------------------------------------------------------|---------|---------|--|

| Symbol            | Parameter Parameter                                                                                  | Min     | Max     |  |

| RAM Cell          | Synchronous Read Timing                                                                              |         |         |  |

| t <sub>SRA</sub>  | RA setup time to RCLK: time the READ ADDRESS must be stable before the active edge of the READ CLOCK | 0.43 ns | -       |  |

| t <sub>HRA</sub>  | RA hold time to RCLK: time the READ ADDRESS must be stable after the active edge of the READ CLOCK   | 0 ns    | -       |  |

| t <sub>SRE</sub>  | RE setup time to WCLK: time the READ ENABLE must be stable before the active edge of the READ CLOCK  | 0.21 ns | -       |  |

| t <sub>HRE</sub>  | RE hold time to WCLK: time the READ ENABLE must be stable after the active edge of the READ CLOCK    | 0 ns    | -       |  |

| t <sub>RCRD</sub> | RCLK to RD: time between the active READ CLOCK edge and the time when the data is available at RD    | -       | 2.25 ns |  |

| RAM Cell          | Asynchronous Read Timing                                                                             |         |         |  |

| r <sub>PDRD</sub> | RA to RD: time between when the READ ADDRESS is input and when the DATA is output                    | -       | 1.99 ns |  |

Figure 38: RAM Cell Synchronous and Asynchronous Read Timing

<u>www.quicklogic.com</u> © 2005 QuickLogic Corporation

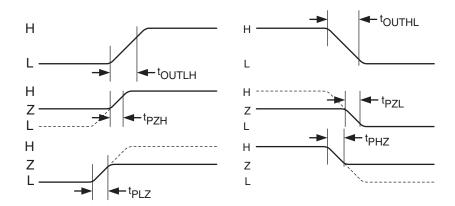

Figure 39: QL58x0 Device Family I/O Cell Output Path

Figure 40: QL58x0 Device Family I/O Cell Output Enable Timing

© 2005 QuickLogic Corporation www.quicklogic.com

Table 23: QL58x0 Device Family I/O Cell Output Timing

| Symbol             | Parameter                                               | Va  | alue (ns)                           |

|--------------------|---------------------------------------------------------|-----|-------------------------------------|

| Output Regis       | ter Cell Only                                           | Min | Max                                 |

| t <sub>OUTLH</sub> | Output Delay low to high (90% of H)                     | -   | 2.95                                |

| t <sub>OUTHL</sub> | Output Delay high to low (10% of L)                     | -   | 2.49                                |

| t <sub>PZH</sub>   | Output Delay tri-state to high (90% of H)               | -   | 3.93                                |

| t <sub>PZL</sub>   | Output Delay tri-state to low (10% of L)                | -   | 2.84                                |

| t <sub>PHZ</sub>   | Output Delay high to tri-State                          | -   | 3.62                                |

| t <sub>PLZ</sub>   | Output Delay low to tri-State                           | -   | 3.4                                 |

| t <sub>COP</sub>   | Clock-to-out delay (does not include clock tree delays) | -   | 3.3 (fast slew)<br>5.49 (slow slew) |

Table 24: Output Slew Rates @ VCCIO = 3.3 V, T = 25° C

|              | Fast Slew | Slow Slew |

|--------------|-----------|-----------|

| Rising Edge  | 2.8 V/ns  | 1.0 V/ns  |

| Falling Edge | 2.86 V/ns | 1.0 V/ns  |

Table 25: Output Slew Rates @ VCCIO = 2.5 V, T = 25° C

|              | Fast Slew | Slow Slew |

|--------------|-----------|-----------|

| Rising Edge  | 1.7 V/ns  | 0.6 V/ns  |

| Falling Edge | 1.9 V/ns  | 0.6 V/ns  |

Table 26: Output Slew Rates @ VCCIO = 1.8 V, T = 25° C

|              | Fast Slew | Slow Slew |

|--------------|-----------|-----------|

| Rising Edge  | -         | -         |

| Falling Edge | -         | -         |

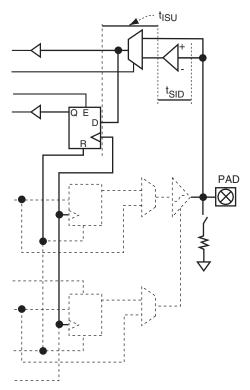

Figure 41: QL58x0 Device Family I/O Cell Input Path

Figure 42: QL58x0 Device Family Input Register Cell Timing

Table 27: I/O Input Register Cell Timing

| Symbol            | Parameter                                                                                                                      |         | Value   |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|---------|--|

| Syllibol          | Falanietei                                                                                                                     | Min     | Max     |  |

| t <sub>ISU</sub>  | Input register setup time: time the synchronous input of the flip-flop must be stable before the active clock edge             | 2.15 ns | -       |  |

| t <sub>IHL</sub>  | Input register hold time: time the synchronous input of the flip-flop must be stable after the active clock edge               | 0 ns    | -       |  |

| t <sub>ICO</sub>  | Input register clock-to-out: time taken by the flip-flop to output after the active clock edge                                 | -       | 0.3 ns  |  |

| t <sub>IRST</sub> | Input register reset delay: time between when the flip-flop is "reset" (low) and when the output is consequently "reset" (low) | -       | 0.82 ns |  |

| t <sub>IESU</sub> | Input register clock enable setup time: time "enable" must be stable before the active clock edge                              |         | -       |  |

| t <sub>IEH</sub>  | Input register clock enable hold time: time "enable" must be stable after the active clock edge                                | 0 ns    | -       |  |

Table 28: I/O Input Buffer Delays

| Symbol                      | Parameter                                                                          | Value |         |

|-----------------------------|------------------------------------------------------------------------------------|-------|---------|

| Symbol                      | To get the total input delay add this delay to t <sub>ISU</sub>                    | Min   | Max     |

| t <sub>SID</sub> (LVTTL)    | SID (LVTTL) LVTTL input delay: Low Voltage TTL for 3.3 V applications              |       | 0.82 ns |

| t <sub>SID</sub> (LVCMOS2)  | LVCMOS2 input delay: Low Voltage CMOS for 2.5 V and lower applications             | -     | 0.82 ns |

| t <sub>SID</sub> (LVCMOS18) | LVCMOS18 input delay: Low Voltage CMOS for 1.8 V applications                      | -     | -       |

| t <sub>SID</sub> (GTL+)     | GTL+ input delay: Gunning Transceiver Logic                                        | -     | 0.94 ns |

| t <sub>SID</sub> (SSTL3)    | t <sub>SID</sub> (SSTL3) SSTL3 input delay: Stub Series Terminated Logic for 3.3 V |       | 0.94 ns |

| t <sub>SID</sub> (SSTL2)    | t <sub>SID</sub> (SSTL2) SSTL2 input delay: Stub Series Terminated Logic for 2.5 V |       | 0.94 ns |

# **Package Thermal Characteristics**

Thermal Resistance Equations:

$$\begin{array}{l} \theta_{JC} = & (\text{T}_{J} - \text{T}_{C})/\text{P} \\ \theta_{JA} = & (\text{T}_{J} - \text{T}_{A})/\text{P} \\ \text{P}_{MAX} = & (\text{T}_{JMAX} - \text{T}_{AMAX})/ & \theta_{JA} \end{array}$$

#### Parameter Description:

$\theta_{\text{JC}}\!\!:$  Junction-to-case thermal resistance

$\theta_{\text{JA}}$ : Junction-to-ambient thermal resistance

T<sub>J</sub>: Junction temperature

T<sub>A</sub>: Ambient temperature

P: Power dissipated by the device while operating

P<sub>MAX</sub>: The maximum power dissipation for the device

T<sub>JMAX</sub>: Maximum junction temperature

T<sub>AMAX</sub>: Maximum ambient temperature