# TSB43CA43A/TSB43CB43A/TSB43CA42 iceLynx-Micro IEEE 1394a-2000 Consumer Electronics Solution ABBREVIATED DATA MANUAL

SLLS546 - February 2003

Texas Instruments Incorporated, Copyright 2003

For more information and/or a complete data manual on this product, contact the Texas Instruments Product Information Center (PIC). Local PIC contact numbers are listed on http://www.ti.com/corp/technical\_support.htm

TSB43Cx43A/ TSB43CA42 TEXAS INSTRUMENTS

## TI iceLynx-Micro™ IEEE 1394a-2000 Consumer Electronics Solution

Rev. 1.7

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other guality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Customers are responsible for their applications using TI components. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval. license, warranty or endorsement thereof. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use. Resale of TI's products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use. Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265 Copyright \_ 2003, Texas Instruments Incorporated

PRODUCTION DATA information is current as of public date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### TI iceLynx-Micro™ IEEE 1394a-2000 **Consumer Electronics Solution** Rev. 1.7

**TEXAS INSTRUMENTS**

| Table of Contents                                                           |      |

|-----------------------------------------------------------------------------|------|

| 1 Hardware IC Characteristics                                               | 8    |

| 1.1 Feature List                                                            |      |

| 1.1.1 1394 Features                                                         | 9    |

| 1.1.2 DTLA Encryption Support for MPEG2-DVB, DSS, DV, and Audio(TSB43CA43A  | &    |

| TSB43CA42 Only)                                                             |      |

| 1.1.3 High Speed Data Interface (HSDI)                                      | 9    |

| 1.1.4 External CPU Interface                                                | 9    |

| 1.1.5 Internal ARM7                                                         | 10   |

| 1.1.6 Data Buffers                                                          |      |

| 1.1.7 Hardware Packet Formatting for the Following Standards                | 10   |

| 1.1.8 Additional Features                                                   | 10   |

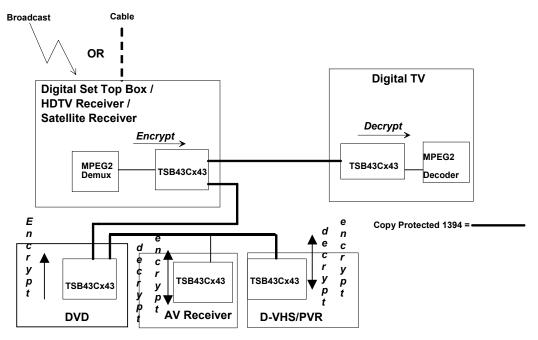

| 1.2 Application Diagram                                                     | 11   |

| 1.3 Block Diagram                                                           | 12   |

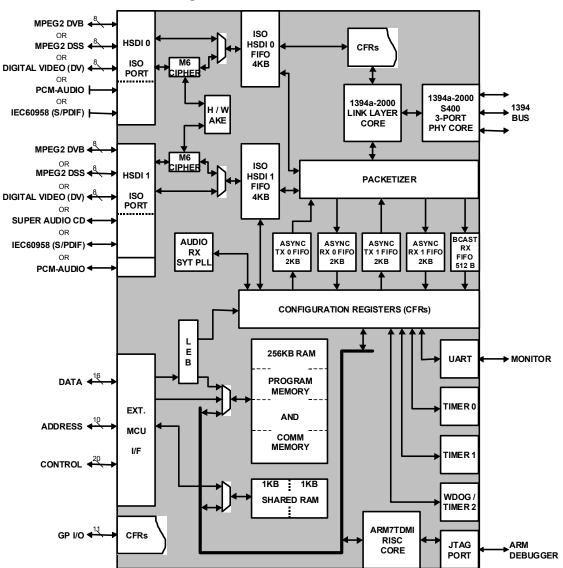

| 1.3.1 TSB43Cx43A Block Diagram                                              | 12   |

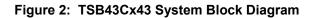

| 1.3.2 TSB43CA42 Block Diagram                                               |      |

| 1.4 Pin Out                                                                 |      |

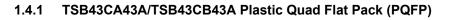

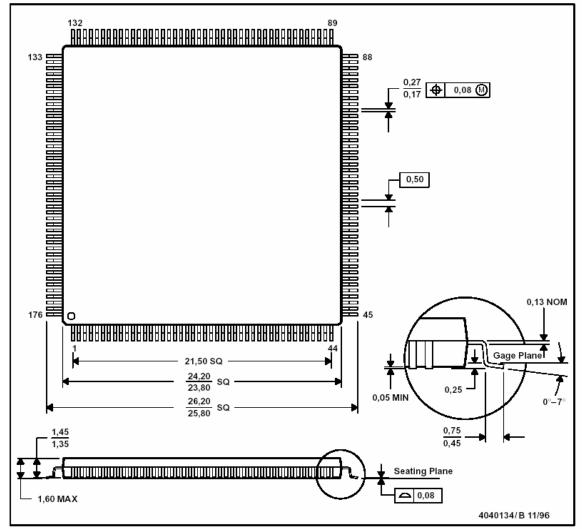

| 1.4.1 TSB43CA43A/TSB43CB43A Plastic Quad Flat Pack (PQFP)                   |      |

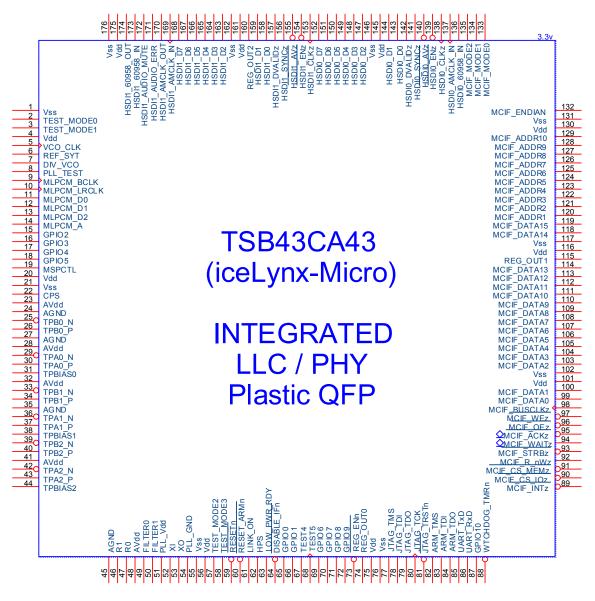

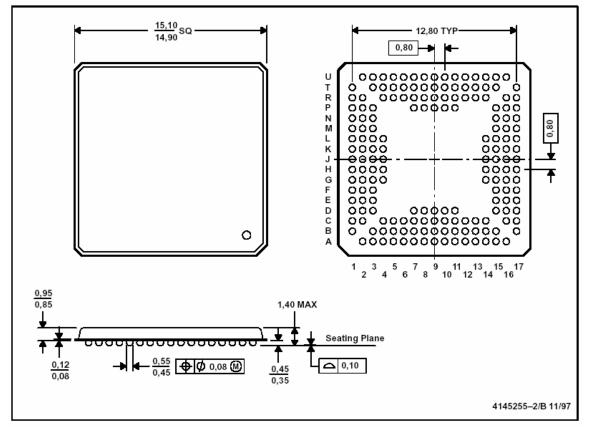

| 1.4.2 TSB43CA43A/TSB43CB43A Micro-Star Ball Grid Array (μ*BGA)              | 15   |

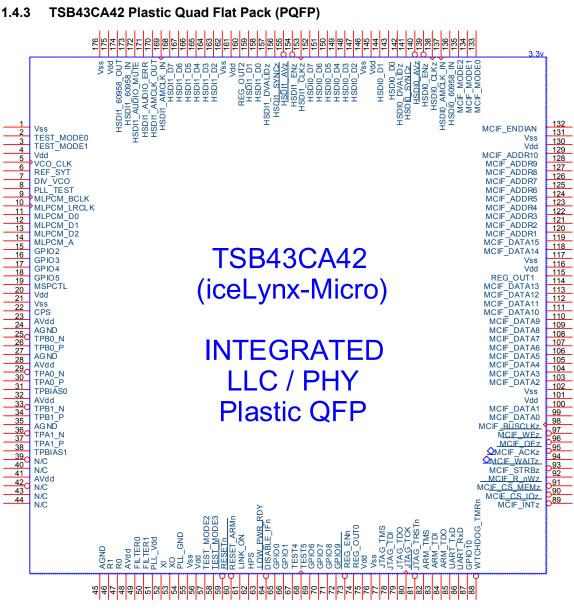

| 1.4.3 TSB43CA42 Plastic Quad Flat Pack (PQFP)                               | 16   |

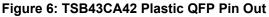

| 1.4.4 TSB43CA42 Micro-Star Ball Grid Array (μ*BGA)                          | 17   |

| 1.5 Pin Description                                                         |      |

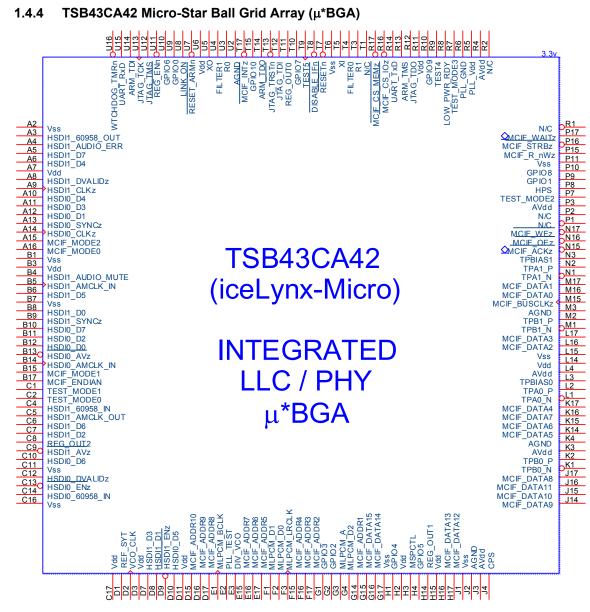

| 1.6 Memory Map                                                              | 30   |

| 1.7 DTCP Encryption – Hardware Implementation (TSB43CA43A & TSB43CA42 Only) | 31   |

| 1.8 Program Memory                                                          |      |

| 1.8.1 Overview/Description                                                  |      |

| 1.8.2 External CPU (Parallel Mode)                                          | 31   |

| 1.9 External CPU Interface                                                  | 32   |

| 1.9.1 Overview/Description                                                  | 32   |

| 1.9.2 Endian Setting (Parallel and Memory Accesses)                         | 34   |

| 1.9.2.1 Parallel Mode and Memory Access                                     | 34   |

| 1.9.3 Ex-CPU Access                                                         | 35   |

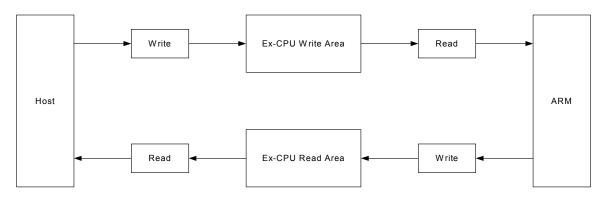

| 1.9.3.1 Ex-CPU and ARM Communication Sequence in Parallel Ex-CPU I/F Mode   | 36   |

| 1.9.3.1.1 Ex-CPU Read                                                       | 36   |

| 1.9.3.1.2 Ex-CPU Write                                                      |      |

| 1.9.3.1.3 Ex-CPU Access Limitation                                          | 37   |

| 1.9.4 Ex-CPU Timing                                                         | 38   |

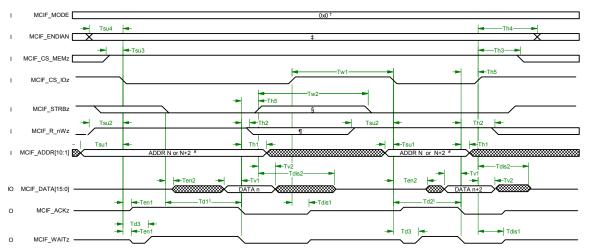

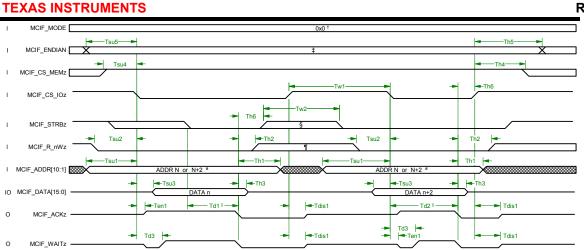

| 1.9.4.1 I/O Type-0 68K + Wait                                               | 38   |

| 1.9.4.2 I/O TYPE-1 SH3 SRAM-like + WAIT                                     |      |

| 1.9.4.3 I/O TYPE-2 M16C SRAM-like + WAIT                                    | 46   |

| 1.9.4.4 I/O TYPE-3 MPC850                                                   | 50   |

| 1.9.4.5 Memory Type                                                         | 54   |

| 1.9.5 DES Encryption                                                        | 57   |

| 1.10 Integrated CPU                                                         | . 58 |

| 1.10.1 Description/Overview                                                 | 58   |

| 1.10.2 Interaction with External CPU                                        | . 59 |

| 1.10.3 External Interrupts                                                  | 59   |

| 1.10.4 Timer                                                                | 59   |

| 1.11 High Speed Data Interface                                              | 60   |

| 1.11.1 Overview/Description                                                 | 60   |

|                                                                             |      |

PRODUCTION DATA information is current as of public date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### TI iceLynx-Micro™ IEEE 1394a-2000 **Consumer Electronics Solution** Rev. 1.7

TE

**TSB43CA42**

| EAS INSTRUMENTS                                                                    |    |

|------------------------------------------------------------------------------------|----|

| 1.11.2 Frame Sync Detection Circuit                                                | 62 |

| 1.11.3 HSDI Pass Through Function                                                  |    |

| 1.11.4 HSDI Maximum Clock Rates and Through-Put                                    | 63 |

| 1.11.5 HSDI Mode Settings                                                          | 64 |

| 1.11.6 HSDI Transmit Modes                                                         |    |

| 1.11.6.1 TX Mode 1: Serial Burst I/F (MPEG2)                                       |    |

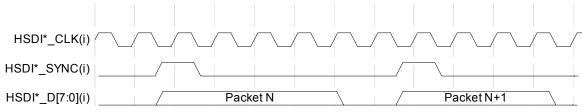

| 1.11.6.2 TX Mode 2: Serial Video Burst I/F (MPEG2) with Frame Sync Detect Circuit  | 66 |

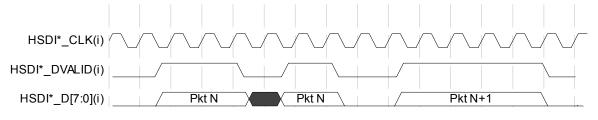

| 1.11.6.3 TX Mode 3: Serial Video Burst I/F (MPEG2) Clock Active Only When Data Is  |    |

| Valid                                                                              | 66 |

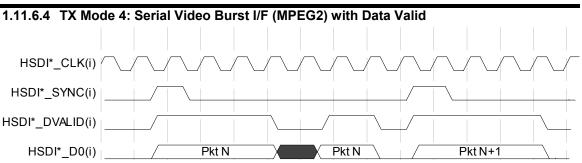

| 1.11.6.4 TX Mode 4: Serial Video Burst I/F (MPEG2) with Data Valid                 | 67 |

| 1.11.6.5 TX Mode 5: Parallel Burst Video I/F (MPEG2)                               | 67 |

| 1.11.6.6 TX Mode 6: Parallel Video Burst I/F (MPEG2) with Frame Sync Detect Circui | t  |

|                                                                                    | 67 |

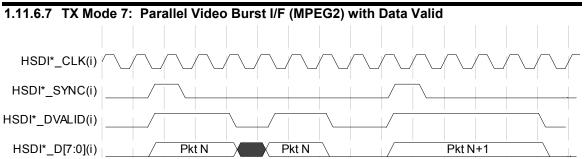

| 1.11.6.7 TX Mode 7: Parallel Video Burst I/F (MPEG2) with Data Valid               | 68 |

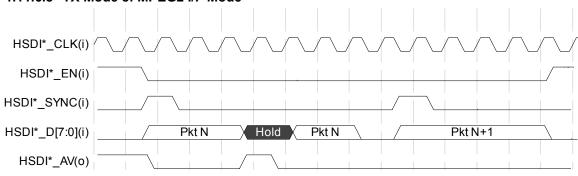

| 1.11.6.8 TX Mode 8: MPEG2 I/F Mode                                                 | 68 |

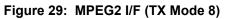

| 1.11.6.9 TX Mode 9: DV I/F Mode                                                    | 69 |

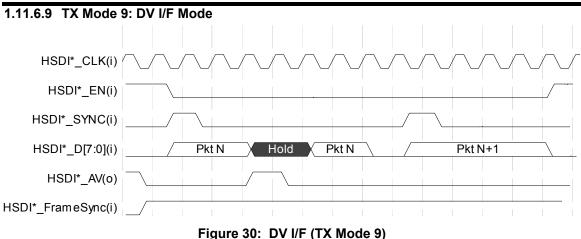

| 1.11.7 HSDI Receive Modes                                                          | 69 |

| 1.11.7.1 RX Mode 1: Serial Burst Video I/F (MPEG2)                                 | 69 |

| 1.11.7.2 RX Mode 2: Parallel Burst Video I/F (MPEG2)                               | 70 |

| 1.11.7.3 RX Mode 3: Parallel Burst Video I/F (MPEG2) Mode                          |    |

| 1.11.7.4 RX Mode 4: Parallel Burst Video I/F (DV) Mode                             |    |

| 1.11.7.5 HSDI A/C Timing                                                           |    |

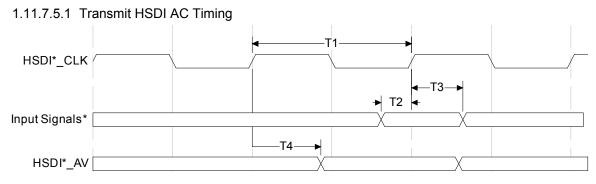

| 1.11.7.5.1 Transmit HSDI AC Timing                                                 | 71 |

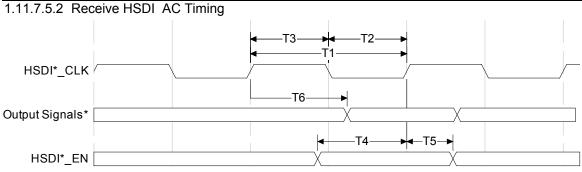

| 1.11.7.5.2 Receive HSDI AC Timing                                                  |    |

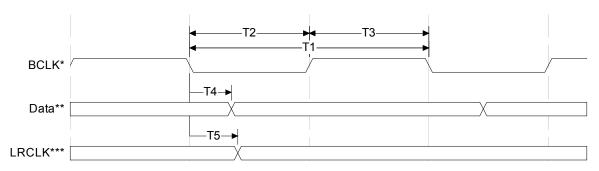

| 1.11.8 Audio Interface on HSDI                                                     |    |

| 1.11.8.1 HSDI0                                                                     |    |

| 1.11.8.2 HSDI1                                                                     |    |

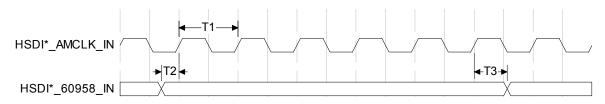

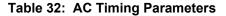

| 1.11.8.3 IEC60958 I/F AC Timing Characteristic                                     |    |

| 1.12 UART Interface                                                                |    |

| 1.12.1 UART Registers                                                              |    |

| 1.12.2 UART Baud Rate                                                              |    |

| 1.13 JTAG – Boundary Scan and ARM                                                  |    |

| 1.14 Integrated 3-Port PHY                                                         | 79 |

| 1.14.1 3 Port PHY                                                                  | 79 |

| 1.14.2 PHY Registers                                                               |    |

| 1.14.3 PHY Application Information                                                 |    |

| 1.14.3.1 PHY Reference Documents                                                   | 89 |

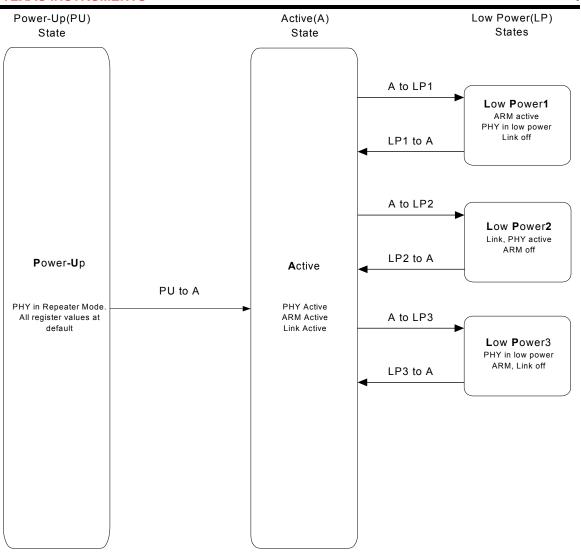

| 1.15 Power Management                                                              |    |

| 1.15.1 PU to A (Power Up State to Active State)                                    | 91 |

| 1.15.2 A to LP1 (Active State to Low Power 1 State)                                |    |

| 1.15.3 LP1 to A (Low Power 1 State to Active State)                                |    |

| 1.15.4 A to LP2 (Active State to Low Power 2 State)                                |    |

| 1.15.5 LP2 to A (Low Power 2 State to Active State)                                |    |

| 1.15.6 A to LP4 (Low Power 3 State to Active State)                                |    |

| 1.15.7 LP4 to A (Low Power 3 State to Active State)                                |    |

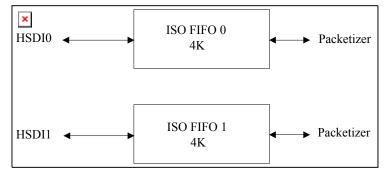

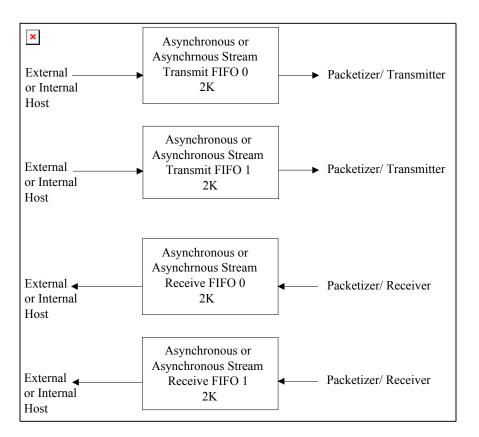

| 1.16 16.5K Byte Memory - FIFO                                                      |    |

| 1.16.1 Overview/Description                                                        |    |

| 1.16.2 Isochronous FIFOs 0 and 1:                                                  | 94 |

| 1.16.3 Asynchronous/Asynchronous Stream FIFOs:                                     |    |

| 1.16.4 Broadcast Receive FIFO:                                                     |    |

| 1.16.5 FIFO Priority                                                               |    |

| 1.16.6 FIFO Monitoring                                                             |    |

|                                                                                    | 00 |

PRODUCTION DATA information is current as of public date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

## TI iceLynx-Micro™ IEEE 1394a-2000 Consumer Electronics Solution

Rev. 1.7

| Т | EXA  | S INSTRUMENTS                                                                 | F   |

|---|------|-------------------------------------------------------------------------------|-----|

|   | 1.17 | GPIO Configurations                                                           | 97  |

|   | 1.   | 17.1 GPIO Setup                                                               | 97  |

|   | 1.18 | B IEEE 1394a-2000 Requirements                                                | 98  |

|   |      | 18.1 Features                                                                 |     |

|   |      | 18.2 Cycle Master                                                             |     |

| 2 | Ap   | ppendix A: Configuration Registers                                            |     |

|   | 2.1  | Configuration Registers                                                       |     |

|   | 2.2  | Description Notes                                                             |     |

|   | 2.3  | CFR Address Ranges (Offset from CFR Base Address)                             |     |

|   | 2.4  | Register Access                                                               |     |

| 3 |      | eneral Information                                                            |     |

|   | 3.1  | Package Size                                                                  |     |

|   | 3.2  | Operating Voltage                                                             |     |

|   | 3.3  | Operating Temperature                                                         |     |

| 4 |      | bsolute Maximum Ratings Over Operating Temperature Ranges†                    |     |

|   | 4.1  | Recommended Operating Conditions (Analog IEEE 1394 I/F)                       |     |

|   | 4.2  | Electrical Characteristics Over Recommended Ranges of Operating Conditions (u |     |

|   |      | erwise noted)                                                                 | 104 |

|   | 4.3  | Thermal Characteristics                                                       |     |

|   | 4.4  | Switching Characteristics for PHY Port Interface                              |     |

| _ | 4.5  | Operating, Timing, and Switching Characteristics of XI                        |     |

| 5 |      | eset Power States                                                             |     |

| 6 |      | onfiguration Register Map                                                     |     |

| 7 |      | echanical Data                                                                |     |

|   | 7.1  |                                                                               |     |

|   | 7.2  | Microstar BGA Package Dimensions                                              | 108 |

PRODUCTION DATA information is current as of public date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### **TSB43CA42**

### TI iceLynx-Micro<sup>™</sup> IEEE 1394a-2000 Consumer Electronics Solution Rev. 1.7

**TEXAS INSTRUMENTS**

| ist | Of | Figu | es |

|-----|----|------|----|

|     |    |      |    |

| Figure 1. TSB43Cx43 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

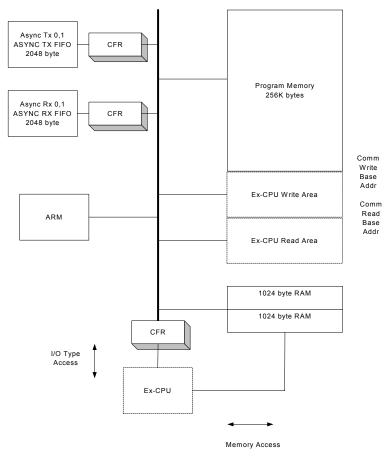

| Figure 2: TSB43Cx43 System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

| Figure 3: TSB43CA42 System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

| Figure 4: TSB43CA43A Plastic QFP Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

| Figure 5: TSB43CA43A μ*BGA Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

| Figure 6: TSB43CA42 Plastic QFP Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

| Figure 7: TSB43CA42 μ*BGA Pin Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

| Figure 8: TSB43Cx43 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

| Figure 10: Ex-CPU Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

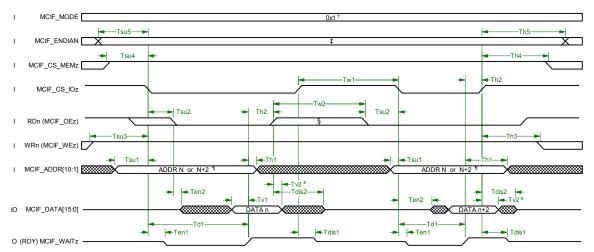

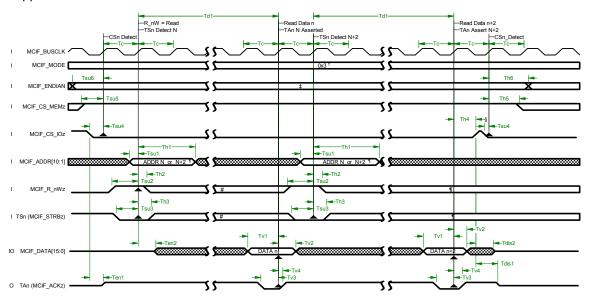

| Figure 11: I/O Type-0 68K + Wait Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |

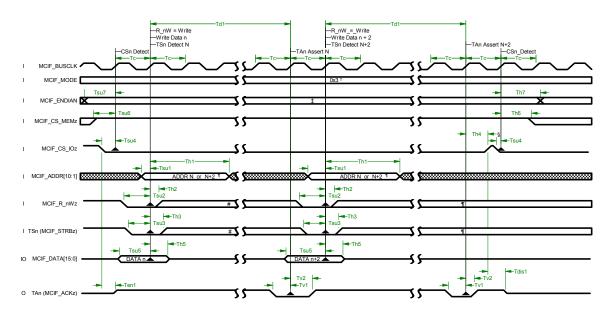

| Figure 12: I/O Type-0 68K + Wait Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 40                                                                                                                                                         |

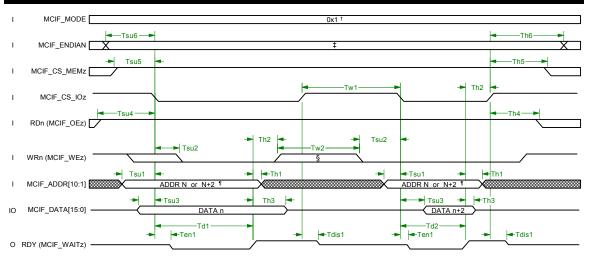

| Figure 13: I/O TYPE-1 SH3 Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

| Figure 14: I/O TYPE-1 SH3 Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

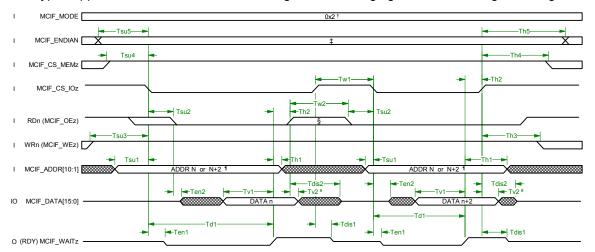

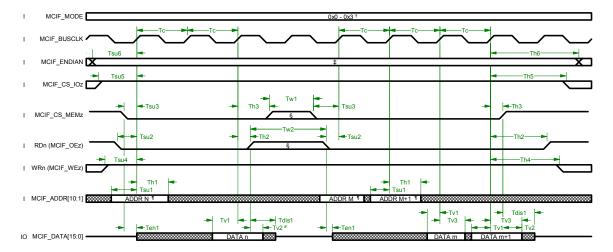

| Figure 15: I/O TYPE-2 M16C SRAM-like + WAIT Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |

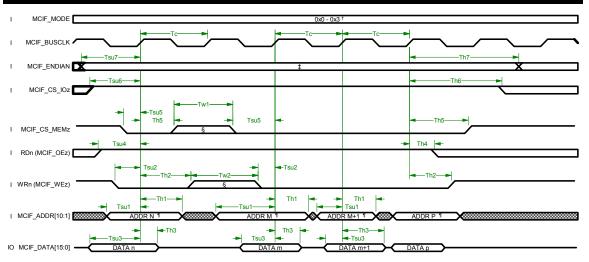

| Figure 16: I/O TYPE-2 M16C SRAM-like + WAIT Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

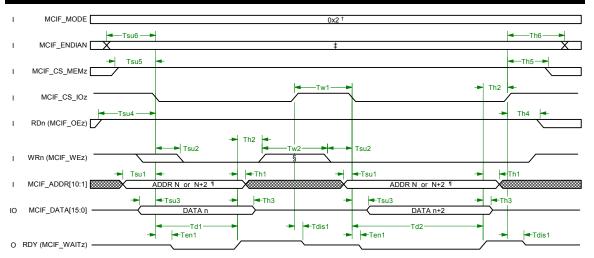

| Figure 17: I/O TYPE-3 MPC850 Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

| Figure 18: I/O TYPE-3 MPC850 Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

| Figure 20: Memory Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

| Figure 21: Memory Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

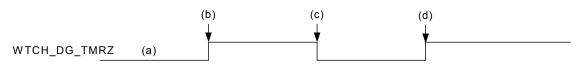

| Figure 26: WatchDog Timer Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

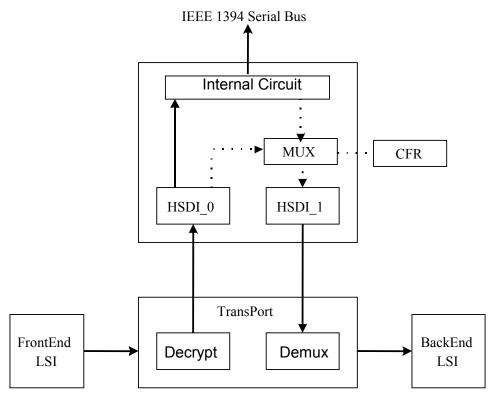

| Figure 27: Data Pass-Through Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |

| Figure 28: MPEG2 Serial Burst I/F (TX Mode 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |

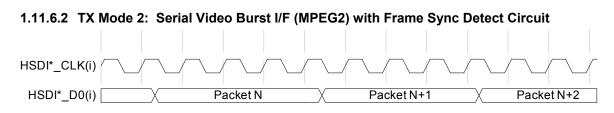

| Figure 29: MPEG2 Serial Video Burst I/F with Frame Sync Detect Circuit (TX Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

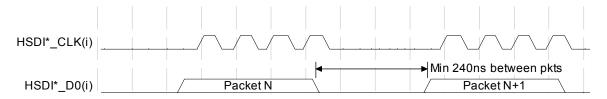

| Figure 30: MPEG2 Serial Video Burst I/F Clock Active Only When Data Is Valid (TX Mode 3)<br>Figure 31: MPEG2 Serial Video Burst I/F with Data Valid (TX Mode 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

| FIGURE 31° IMPEGZ SEDALVIGEO BUISLI/E WIID DAIA VAIIO (TX MODE 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 07                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 67                                                                                                                                                         |

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 67<br>. 67                                                                                                                                                 |

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)<br>Figure 34: MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 67<br>. 67<br>. 68                                                                                                                                         |

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)<br>Figure 34: MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)<br>Figure 35: MPEG2 I/F (TX Mode 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 67<br>. 67<br>. 68<br>. 68                                                                                                                                 |

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)<br>Figure 34: MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)<br>Figure 35: MPEG2 I/F (TX Mode 8)<br>Figure 36: DV I/F (TX Mode 9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 67<br>. 67<br>. 68<br>. 68<br>. 69                                                                                                                         |

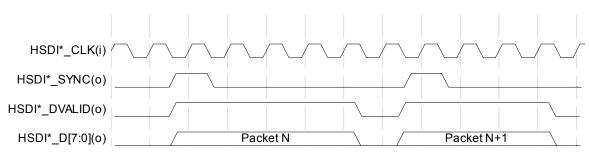

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)<br>Figure 34: MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)<br>Figure 35: MPEG2 I/F (TX Mode 8)<br>Figure 36: DV I/F (TX Mode 9)<br>Figure 37: MPEG2 Serial Burst Video I/F (RX Mode 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69                                                                                                                 |

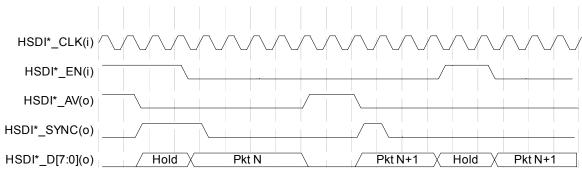

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 69<br>. 70                                                                                                 |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70                                                                                                 |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)         Figure 40:       DV Parallel Burst Video I/F (RX Mode 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70                                                                                         |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70                                                                                         |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)         Figure 40:       DV Parallel Burst Video I/F (RX Mode 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70<br>. 70                                                                         |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)         Figure 40:       DV Parallel Burst Video I/F (RX Mode 4)         Figure 41:       Transmit HSDI AC Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72                                                                                 |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)         Figure 40:       DV Parallel Burst Video I/F (RX Mode 4)         Figure 41:       Transmit HSDI AC Timing         Figure 42:       Receive HSDI AC Timing         Figure 43:       Example 1 Sampling frequency (fs): 192kHz, Master clock frequency: 256fs         Figure 44:       Example 2 Sample frequency (fs): 48kHz, Master clock frequency: 768fs                                                                                                                                                                                                                                                    | . 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75                                                                         |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 3)         Figure 40:       DV Parallel Burst Video I/F (RX Mode 4)         Figure 41:       Transmit HSDI AC Timing         Figure 42:       Receive HSDI AC Timing         Figure 43:       Example 1 Sampling frequency (fs): 192kHz, Master clock frequency: 256fs         Figure 44:       Example 2 Sample frequency (fs): 48kHz, Master clock frequency: 768fs                                                                                                                                                                                                                                                    | . 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75                                                                         |

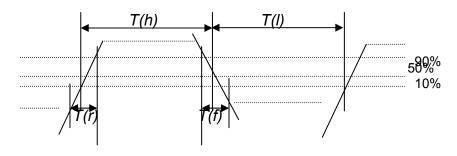

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 67<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75<br>. 75<br>. 76                                                         |

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)         Figure 39:       MPEG2 Parallel Burst Video I/F (RX Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 70<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75<br>. 75<br>. 76<br>. 76                                         |

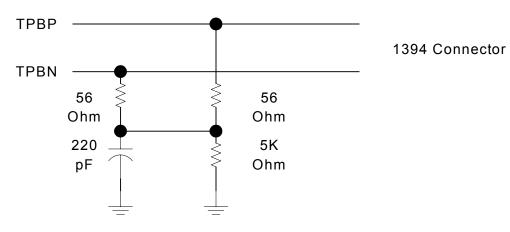

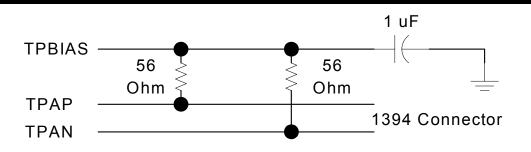

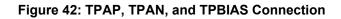

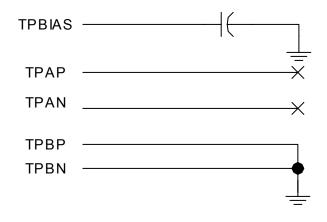

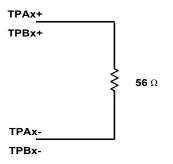

| Figure 32: MPEG2 Parallel Burst Video I/F (TX Mode 5)<br>Figure 33: MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)<br>Figure 34: MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)<br>Figure 35: MPEG2 I/F (TX Mode 8)<br>Figure 36: DV I/F (TX Mode 9)<br>Figure 37: MPEG2 Serial Burst Video I/F (RX Mode 1)<br>Figure 38: MPEG2 Parallel Burst Video I/F (RX Mode 2)<br>Figure 39: MPEG2 Parallel Burst Video I/F (RX Mode 2)<br>Figure 40: DV Parallel Burst Video I/F (RX Mode 3)<br>Figure 41: Transmit HSDI AC Timing<br>Figure 42: Receive HSDI AC Timing<br>Figure 43: Example 1 Sampling frequency (fs): 192kHz, Master clock frequency: 256fs<br>Figure 44: Example 2 Sample frequency (fs): 48kHz, Master clock frequency: 768fs<br>Figure 45: AC timing characteristic on receiving<br>Figure 46: AC timing characteristic on transmitting.<br>Figure 47: TPBP and TPBN Connection                                                                                                                                                                                                                                           | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 70<br>. 70<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75<br>. 75<br>. 76<br>. 86                                 |

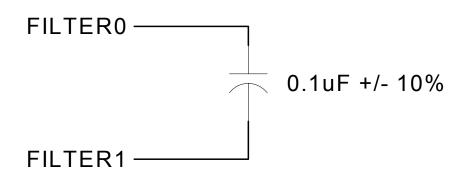

| Figure 32:       MPEG2 Parallel Burst Video I/F (TX Mode 5)         Figure 33:       MEPG2 Parallel Video Burst I/F with Frame Sync Detect Circuit (TXMode 6)         Figure 34:       MPEG2 Parallel Video Burst I/F with Data Valid (TX Mode 7)         Figure 35:       MPEG2 I/F (TX Mode 8)         Figure 36:       DV I/F (TX Mode 9)         Figure 37:       MPEG2 Serial Burst Video I/F (RX Mode 1)         Figure 38:       MPEG2 Parallel Burst Video I/F (RX Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 67<br>. 67<br>. 68<br>. 68<br>. 69<br>. 70<br>. 70<br>. 70<br>. 70<br>. 70<br>. 70<br>. 71<br>. 72<br>. 75<br>. 76<br>. 86<br>. 87                         |