SBOS254A - JULY 2002 - REVISED NOVEMBER 2002

# Dual, VARIABLE GAIN AMPLIFIER with Input Buffer

### **FEATURES**

- GAIN RANGE: 27dB to 45dB

- 30MHz BANDWIDTH

- LOW CROSSTALK: 65dB at Max Gain, 5MHz

- HIGH-SPEED VARIABLE GAIN ADJUST

- POWER SHUTDOWN MODE

- HIGH IMPEDANCE INPUT BUFFER

### **APPLICATIONS**

- ULTRASOUND SYSTEMS

- WIRELESS RECEIVERS

- TEST EQUIPMENT

- RADAR

### DESCRIPTION

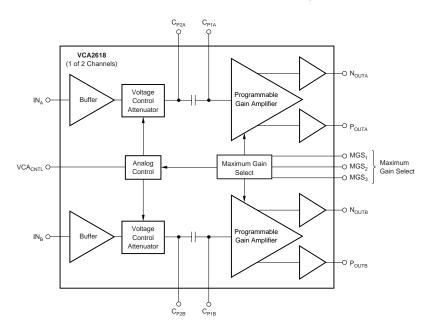

The VCA2618 is a highly integrated, dual receive channel, Variable Gain Amplifier (VGA) with analog gain control.

The VCA2618's VGA section consists of two parts: the Voltage Controlled Attenuator (VCA) and the Programmable Gain Amplifier (PGA). The gain and gain range of the PGA can be digitally programmed. The combination of these two programmable elements results in a variable gain ranging from 0dB up to a maximum gain as defined by the user through external connections. The single-ended unity gain input buffer provides predictable high input impedance. The output of the VGA can be used in either a single-ended or differential mode to drive high-performance Analog-to-Digital (A/D) converters. A separate power-down pin reduces power consumption.

The VCA2618 also features low crosstalk and outstanding distortion performance. The combination of low noise and gain range programmability make the VCA2618 a versatile building block in a number of applications where noise performance is critical. The VCA2618 is available in a TQFP-32 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Power Supply (+V <sub>S</sub> ) |                                   |

|---------------------------------|-----------------------------------|

| Analog Input                    |                                   |

| Logic Input                     | -0.3V to (+V <sub>S</sub> + 0.3V) |

| Case Temperature                |                                   |

| Junction Temperature            | +150°C                            |

| Storage Temperature             | –40°C to +150°C                   |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT  | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|----------|-----------------------|--------------------------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| VCA2618Y | TQFP-32 Surface-Mount | PBS                                  | –40°C to +85°C                    | VCA2618Y           | VCA2618YT          | Tape and Reel, 250           |

| "        |                       | "                                    | "                                 | "                  | VCA2618YR          | Tape and Reel, 2000          |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

### **ELECTRICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $V_{DD} = 5V$ , load resistance = 500 $\Omega$  on each output to ground differential output (2Vp-p), MGS = 111, and  $f_{IN} = 5MHz$ , unless otherwise noted.

| PARAMETER                                  | CONDITIONS                                            | MIN  | ТҮР        | MAX          | UNITS  |

|--------------------------------------------|-------------------------------------------------------|------|------------|--------------|--------|

| BUFFER                                     |                                                       |      |            |              |        |

| Input Resistance                           |                                                       |      | 600        |              | kΩ     |

| Input Capacitance                          |                                                       |      | 5          |              | pF     |

| Input Bias Current                         |                                                       |      | 1          |              | nA     |

| Maximum Input Voltage                      |                                                       |      | 1          |              | Vp-p   |

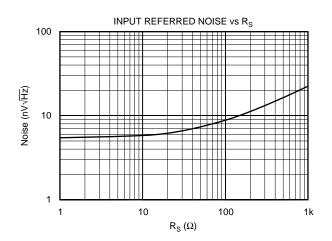

| Input Voltage Noise                        | PGA Gain = 45dB, $R_s = 50\Omega$                     |      | 5.4        |              | nV/√Hz |

| Input Current Noise                        | Independent of Gain                                   |      | 350        |              | fA/√Hz |

| Noise Figure                               | $R_F = 550\Omega$ , PGA Gain = 45dB, $R_S = 75\Omega$ |      | 13         |              | dB     |

| Bandwidth                                  |                                                       |      | 100        |              | MHz    |

| PROGRAMMABLE VARIABLE GAIN A               | MPLIFIER                                              |      |            |              |        |

| Peak Input Voltage                         |                                                       |      | 1          |              | Vp-р   |

| -3dB Bandwidth                             |                                                       |      | 30         |              | MHz    |

| Slew Rate                                  |                                                       |      | 300        |              | V/µs   |

| Output Signal Range                        | $R_L \ge 500\Omega$ Each Side to Ground               |      | 2.5 ±1     |              | V      |

| Output Impedance                           |                                                       |      | 1          |              | Ω      |

| Output Short-Circuit Current               |                                                       |      | ±40        |              | mA     |

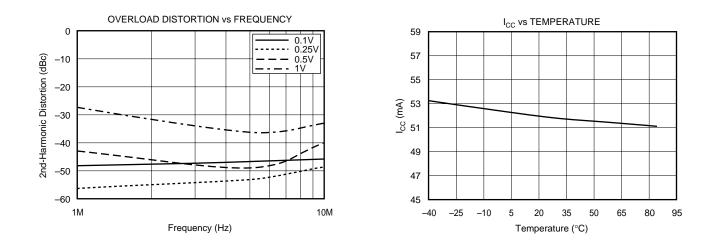

| 3rd-Harmonic Distortion                    | $V_{OUT} = 2Vp-p, VCA_{CNTL} = 3.0V$                  | -45  | -50        |              | dBc    |

| 2nd-Harmonic Distortion                    | $V_{OUT} = 2Vp-p, VCA_{CNTL} = 3.0V$                  | -42  | -50        |              | dBc    |

| 2nd-Harmonic Distortion                    | $V_{OUT} = 2Vp-p, VCA_{CNTL} = 3.0V, MGS = 011$       |      | -60        |              | dBc    |

| Overload Performance (2nd-Harmonic         | Input Signal = 1Vp-p, VCA <sub>CNTL</sub> = 2V        |      | -40 to -45 |              | dB     |

| Distortion)                                |                                                       |      |            |              |        |

| Time Delay                                 |                                                       |      | 5          |              | ns     |

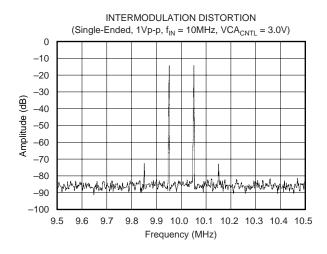

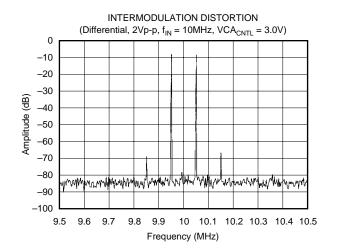

| IMD, 2-Tone                                | $V_{OUT} = 2Vp-p, f = 9.95MHz$                        |      | -59        |              | dBc    |

| Crosstalk                                  |                                                       |      | 65         |              | dB     |

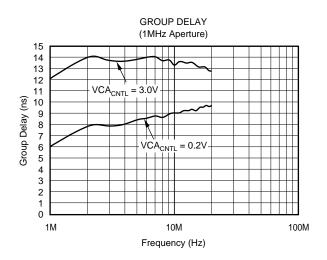

| Group Delay Variation                      | 1MHz < f < 10MHz, Full Gain Range                     |      | 13         |              | ns     |

| ACCURACY                                   |                                                       |      |            |              |        |

| Gain Slope                                 | VCA <sub>CNTL</sub> = 0.2V to 3.0V                    |      | 16         |              | dB/V   |

| Gain Error                                 |                                                       |      |            | <u>±2(1)</u> | dB     |

| Output Offset Voltage                      |                                                       |      | ±50        |              | mV     |

| GAIN CONTROL INTERFACE                     |                                                       |      |            |              |        |

| Input Voltage (VCA <sub>CNTL</sub> ) Range |                                                       |      | 0.2 to 3.0 |              | V      |

| Input Resistance                           |                                                       |      | 1          |              | MΩ     |

| Response Time                              | 45dB Gain Change                                      |      | 0.2        |              | μs     |

| POWER SUPPLY                               |                                                       |      |            |              |        |

| Specified Operating Range                  |                                                       | 4.75 | 5.0        | 5.25         | V      |

| Power Dissipation                          | Operating, Each Channel                               |      | 120        | 150          | mW     |

| Power-Down                                 |                                                       |      | 9.2        |              | mW     |

NOTE: (1) Referenced to best fit dB-linear curve.

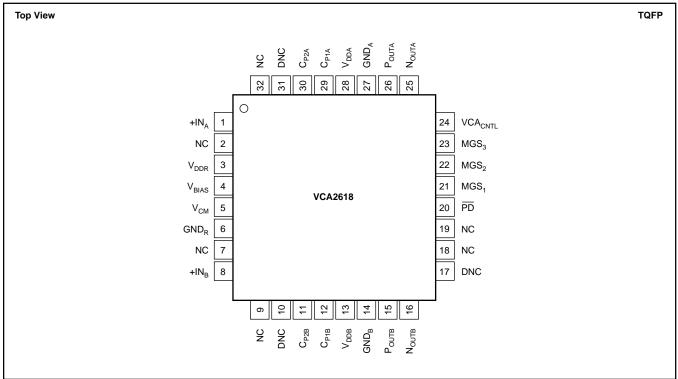

### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN | DESIGNATOR        | DESCRIPTION                  | PIN | DESIGNATOR          | DESCRIPTION                   |

|-----|-------------------|------------------------------|-----|---------------------|-------------------------------|

| 1   | +IN <sub>A</sub>  | Noninverting Input Channel A | 17  | DNC                 | Do Not Connect                |

| 2   | NC                | No Internal Connection       | 18  | NC                  | No Internal Connection        |

| 3   | V <sub>DDR</sub>  | Internal Reference Supply    | 19  | NC                  | No Internal Connection        |

| 4   | V <sub>BIAS</sub> | Bias Voltage                 | 20  | PD                  | Power-Down (Active LOW)       |

| 5   | V <sub>CM</sub>   | Common-Mode Voltage          | 21  | MGS <sub>1</sub>    | Maximum Gain Select 1 (MSB)   |

| 6   | GND <sub>R</sub>  | Internal Reference Ground    | 22  | MGS <sub>2</sub>    | Maximum Gain Select 2         |

| 7   | NC                | Not Connected                | 23  | MGS <sub>3</sub>    | Maximum Gain Select 3 (LSB)   |

| 8   | +IN <sub>B</sub>  | Noninverting Input Channel B | 24  | VCA <sub>CNTL</sub> | VCA Analog Control            |

| 9   | NC                | No Internal Connection       | 25  | N <sub>OUTA</sub>   | Negative VCA Output Channel A |

| 10  | DNC               | Do Not Connect               | 26  | POUTA               | Positive VCA Output Channel A |

| 11  | C <sub>P2B</sub>  | Coupling Capacitor Channel B | 27  | GND <sub>A</sub>    | Ground Channel A              |

| 12  | C <sub>P1B</sub>  | Coupling Capacitor Channel B | 28  | V <sub>DDA</sub>    | +5V Supply Channel A          |

| 13  | V <sub>DDB</sub>  | +5V Supply Channel B         | 29  | C <sub>P1A</sub>    | Coupling Capacitor Channel A  |

| 14  | GND <sub>B</sub>  | Ground Channel B             | 30  | C <sub>P2A</sub>    | Coupling Capacitor Channel A  |

| 15  | POUTB             | Positive Output Channel B    | 31  | DNC                 | Do Not Connect                |

| 16  | N <sub>OUTB</sub> | Negative Output Channel B    | 32  | NC                  | No Internal Connection        |

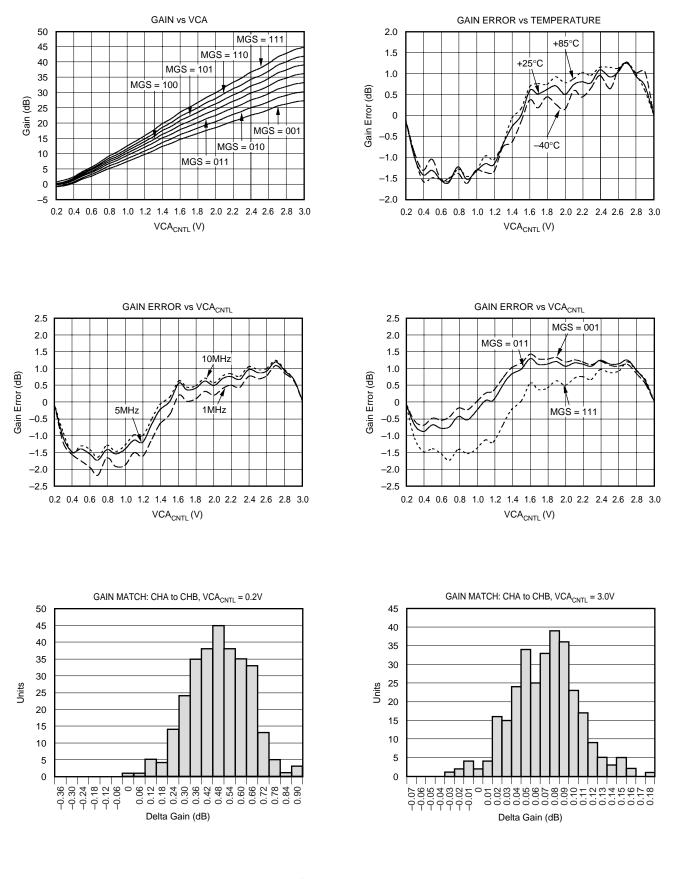

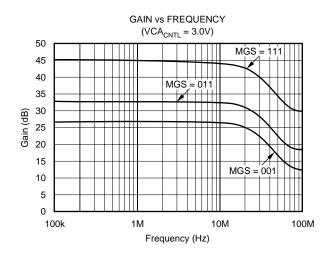

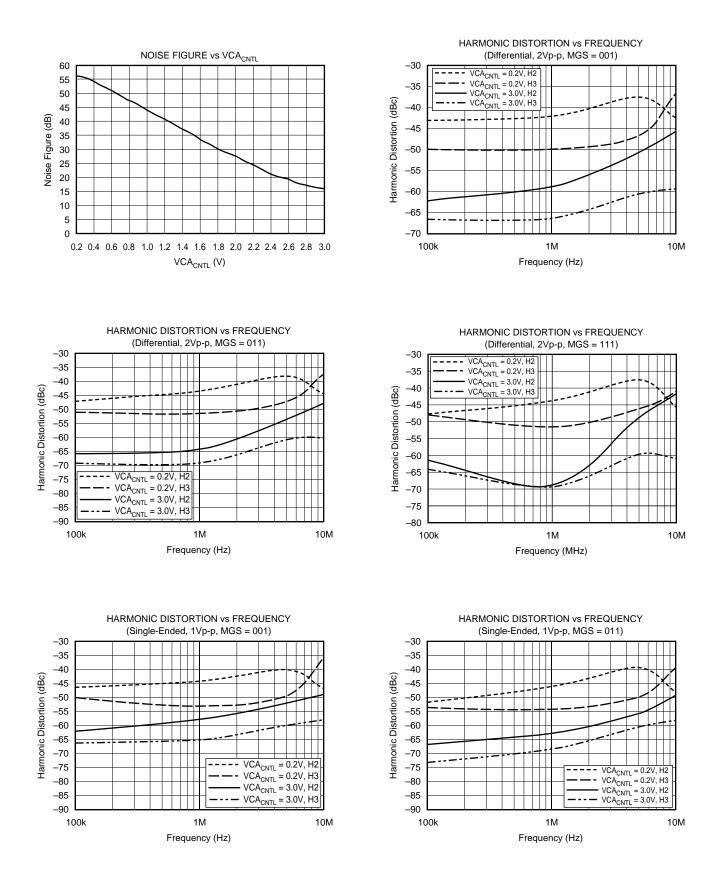

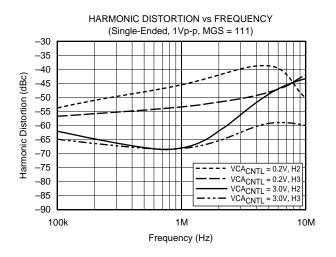

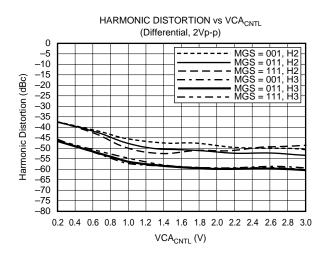

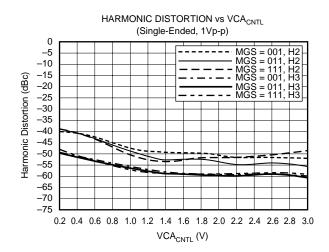

## **TYPICAL CHARACTERISTICS**

NOISE FIGURE vs R<sub>S</sub> Noise Figure (dB) 1k  $\mathsf{R}_{\mathsf{S}}(\Omega)$

At  $T_A = +25^{\circ}$ C,  $V_{DD} = 5$ V, load resistance = 500 $\Omega$  on each output to ground, differential output (2Vp-p) MGS = 111, and  $f_{IN} = 5$ MHz, unless otherwise noted.

CROSS TALK vs FREQUENCY (Differential, 2Vp-p, MGS = 011) 0 -10  $VCA_{CNTRL} = 0V$ -20 -30 Cross Talk (dB) -40 VCA<sub>CNTRL</sub> = 1.5V -50 -60 -70  $VCA_{CNTRL} = 3.0V$ -80 -90 6 21 1 11 16 Frequency (MHz)

### **OVERVIEW**

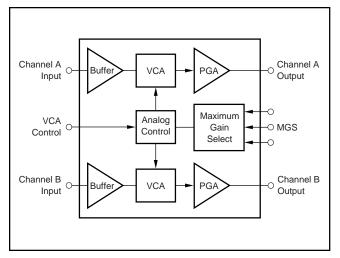

The VCA2618 is a dual-channel, VGA consisting of three primary blocks, an Input Buffer, a VCA, and a PGA. All stages are AC coupled, with the coupling into the PGA stage being made variable by placing an external capacitor between the  $C_{P1}$  and  $C_{P2}$  pins. This will be discussed further in the PGA section. By using the internal coupling into the PGA, the result is a high-pass filter characteristic with cutoff at approximately 75kHz. The output PGA naturally rolls off at around 30MHz, making the usable bandwidth of the VCA2618 between 75kHz and 30MHz.

FIGURE 1. Simplified Block Diagram of the VCA2618.

### **INPUT BUFFER**

The input buffer is a unity gain amplifier (gain of +1) with a bandwidth of 100MHz with an input resistance of approximately  $600k\Omega$ . The input buffer isolates the circuit driving the VCA2618 inputs from the internal VCA block, which would present a varying impedance to the input circuitry. To allow symmetrical operation of the input buffer, the input to the buffer must be AC coupled through an external capacitor. The recommended value of the capacitor is  $0.01\mu$ F. It should be noted that if the capacitor value were increased, the

power-on time of the VCA2618 would be increased. If a decrease in the power-on time is needed, the value can be decreased to no less than 100pF.

#### **VOLTAGE-CONTROLLED ATTENUATOR**

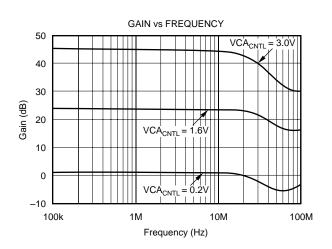

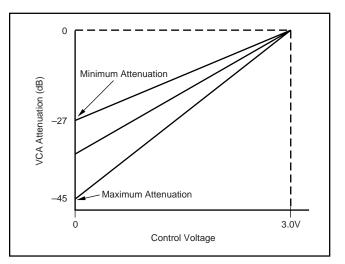

The magnitude of the VCA input signal from the input buffer is reduced by a programmable attenuation factor, set by the analog VCA Control Voltage (VCA<sub>CNTL</sub>) at pin 24. The maximum attenuation is programmable by using the three MGS bits (pins 21, 22, and 23). Figure 2 illustrates this dual-adjust characteristic.

FIGURE 2. Swept Attenuator Characteristic.

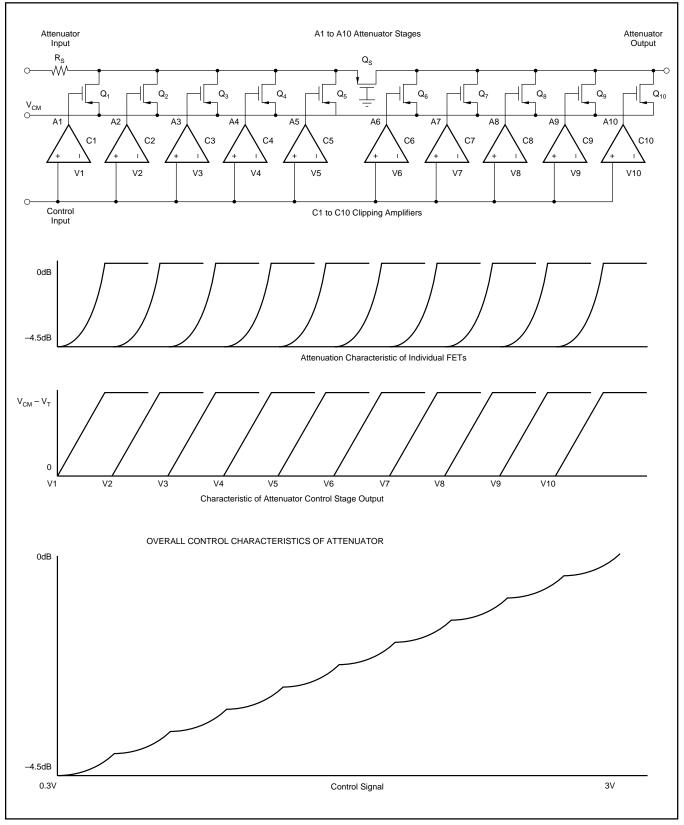

The MGS bits adjust the overall range of attenuation and maximum gain while the VCA<sub>CNTL</sub> voltage adjusts the actual attenuation factor. At any given maximum gain setting, the analog variable gain characteristic is linear in dB as a function of the control voltage, and is created as a piecewise approximation of an ideal dB-linear transfer function. The VCA control circuitry is common to both channels of the VCA2618. The range for the VCA<sub>CNTL</sub> input spans from 0V to 3V. Although overdriving the VCA<sub>CNTL</sub> input above the recommended 3V maximum will not damage the part, this condition should be avoided.

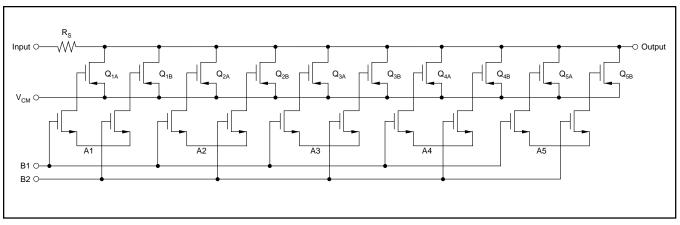

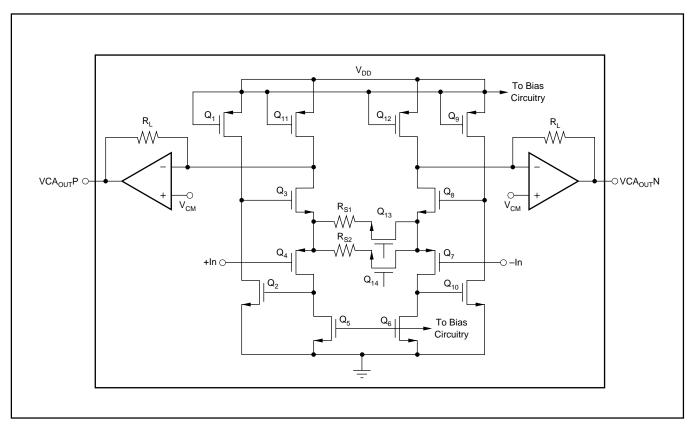

FIGURE 3. Programmable Attenuator Section.

FIGURE 4. Piecewise Approximation to Logarithmic Control Characteristics.

#### **PGA POST-AMPLIFIER**

Figure 5 shows a simplified circuit diagram of the PGA block. As stated before, the input to the PGA is AC coupled by an internal capacitor. Provisions are made so that an external capacitor can be placed in parallel with the internal capacitor, thus lowering the usable low-frequency bandwidth. The lowfrequency bandwidth is set by the following equation:

$$\frac{1}{\left(2 \bullet \pi \bullet 500 \mathrm{k}\Omega \bullet \left(220 \mathrm{pF} + \mathrm{C}_{\mathrm{EXTERNAL}}\right)\right)}$$

where C<sub>EXTERNAL</sub> is the external capacitor value in farads.

Care should be taken to avoid using too large a value of capacitor, as this can increase the power-on delay time.

As described previously, the PGA gain is programmed with the same MGS bits that control the VCA maximum attenuation factor. Specifically, the maximum PGA gain at each MGS setting is the inverse (reciprocal) of the maximum VCA attenuation at that setting. Therefore, the VCA + PGA overall gain will always be 0dB (unity) when the analog VCA<sub>CNTL</sub> input is set to 0V (the maximum attenuation for VCA). For VCA<sub>CNTL</sub> = 3V (no attenuation), the VCA + PGA gain will be controlled by the programmed PGA gain (27dB to 45dB in 3dB steps). For clarity, the gain and attenuation factors are detailed in Table I.

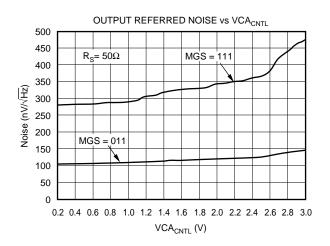

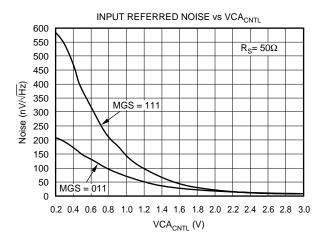

The PGA architecture converts the single-ended signal from the VCA into a differential signal. Low input noise was also a requirement of the PGA design due to the large amount of signal attenuation that can be asserted before the PGA. At minimum VCA attenuation (used for small input signals), the

| MGS<br>SETTING | ATTENUATOR GAIN<br>VCA <sub>CNTL</sub> = 0V to 3V | ATTENUATOR +<br>DIFFERENTIAL PGA GAIN |

|----------------|---------------------------------------------------|---------------------------------------|

| 000            | Not Valid                                         | Not Valid                             |

| 001            | -27dB to 0dB                                      | 0dB to 27dB                           |

| 010            | -30dB to 0dB                                      | 0dB to 30dB                           |

| 011            | -33dB to 0dB                                      | 0dB to 33dB                           |

| 100            | -36dB to 0dB                                      | 0dB to 36dB                           |

| 101            | -39dB to 0dB                                      | 0dB to 39dB                           |

| 110            | -42dB to 0dB                                      | 0dB to 42dB                           |

| 111            | -45dB to 0dB                                      | 0dB to 45dB                           |

TABLE I. MGS Settings.

input buffer noise dominates; at maximum VCA attenuation (large input signals), the PGA noise dominates. Note that if the PGA output is used single-ended, the apparent gain will be 6dB lower.

#### LAYOUT CONSIDERATIONS

The VCA2618 is an analog amplifier capable of high gain. When working on a PCB layout for the VCA2618, it is recommended to utilize a solid ground plane that is connected to analog ground. This helps to maximize the noise performance of the VCA2618.

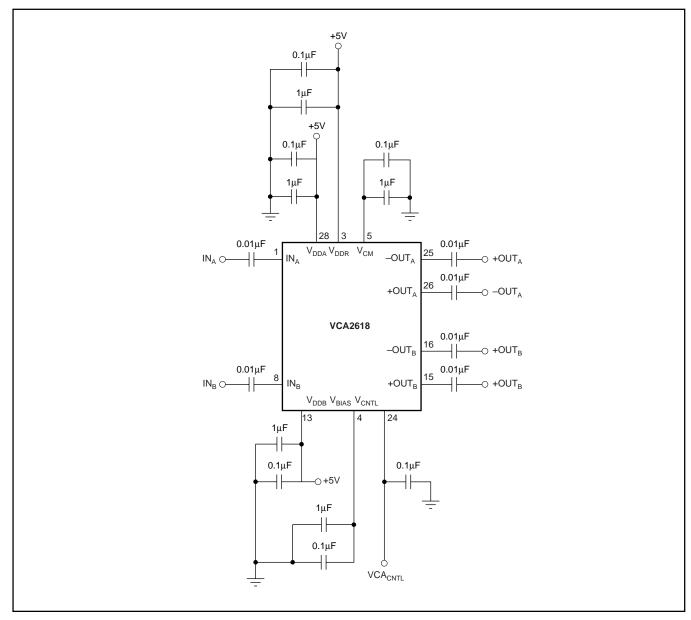

Adequate power-supply decoupling must be used in order to achieve the best possible performance. Decoupling capacitors on the VCA<sub>CNTL</sub> voltage should also be used to help minimize noise. Recommended values can be obtained from the layout diagram of Figure 6.

FIGURE 5. Simplified Block Diagram of the PGA Section with the VCA2618.

FIGURE 6. VCA2618 Layout.

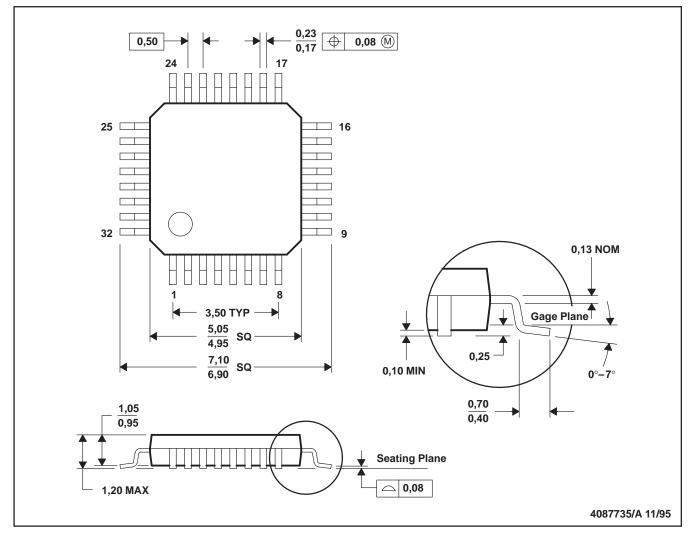

### PBS (S-PQFP-G32)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated