## **General Description**

The MAX9471/MAX9472 multipurpose clock generators are ideal for consumer and communication applications. The MAX9471/MAX9472 feature two buffered phase-locked loop (PLL) outputs that can be independently set from 4MHz to 200MHz. These devices also provide one (MAX9472) or two (MAX9471) buffered outputs of the reference clock.

The MAX9471 outputs a set of MPEG/AC3 audio and video frequencies most commonly used in consumer applications. The MAX9472 outputs a set of common audio frequencies. These frequencies are selected through an  $I^2C^{\dagger}$  interface (MAX9471) or by setting the three-level FS pins. The MAX9471/MAX9472 feature a one-time-programmable (OTP) ROM, allowing one-time programming of the two PLL outputs.

The MAX9471/MAX9472 include two basic configurations. In one configuration, the OTP ROM sets PLL1 output to any frequency between 4MHz to 200MHz, and the I<sup>2</sup>C interface (MAX9471) or programmable pins set the PLL2 output frequency to a set of audio and video frequencies. In the other configuration, the OTP ROM sets both PLL1 and PLL2 frequencies to fixed values between 4MHz to 200MHz. In both cases, the reference output is available, but the OTP ROM can disable it.

The OTP ROM on the MAX9471/MAX9472 is factory set based on the customer requirements. Contact the factory for samples with preferred frequencies.

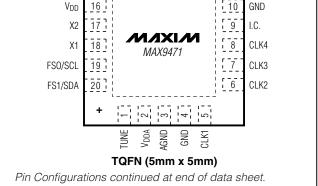

The devices operate from a 3.3V supply and are specified over the -40°C to +85°C extended temperature range. The MAX9471 is available in a 20-pin TQFN package. The MAX9472 is available in a 14-pin TSSOP package.

Digital TVs Communication Systems Data Networking Systems Set-Top Boxes Home Entertainment Centers Multimedia PCs

†Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

#

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

**Applications**

### **Features**

- 5MHz to 50MHz Input Clock Reference

- Crystal or Input-Clock-Based Reference

- Two Fractional-N Feedback PLLs (4MHz to 200MHz) with Buffered Outputs

- Two Buffered Outputs of Reference Clock

- OTP for Factory-Preset PLL Frequencies Available (Contact Factory)

- Programmable Through I<sup>2</sup>C Interface or Three-Level Logic Pins for Video or Audio Clocks

- ♦ Low-RMS Jitter PLL (14ps for 45MHz)

- Integrated VCXO with ±200ppm Tuning Range

- Available in 20-Pin TQFN and 14-Pin TSSOP Packages

- +3.3V Supply

- ♦ -40°C to +85°C Temperature Range

## Ordering Information

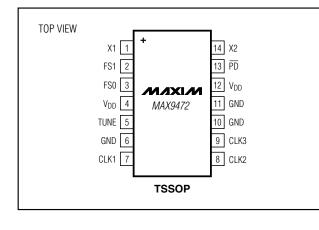

**Pin Configurations**

| PART          | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|---------------|----------------|-----------------|-------------|

| MAX9471ETP+** | -40°C to +85°C | 20 TQFN-EP*     | T2055-5     |

| MAX9472EUD+** | -40°C to +85°C | 14 TSSOP        | U14-2       |

\*EP = Exposed pad.

TOP VIEW

\*\*Marking is for samples only. Contact factory for ordering information. +Denotes lead-free package.

####

\_\_\_\_ Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND             | 0.3V to +4.0V                  |

|------------------------------------|--------------------------------|

| VDDA to AGND                       | 0.3V to +4.0V                  |

| AGND to GND                        | 0.3V to +0.3V                  |

| All Other Pins to GND              | 0.3V to V <sub>DD</sub> + 0.3V |

| Short-Circuit Duration             |                                |

| (all LVCMOS outputs)               | Continuous                     |

| ESD Protection (Human Body Model). |                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = V_{DDA} = +3.0V \text{ to } +3.6V \text{ and } T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ . Typical values at  $V_{DD} = V_{DDA} = 3.3V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                        | SYMBOL                            | CONDITIONS                                                    | MIN                      | ТҮР | MAX                      | UNITS |  |

|--------------------------------------------------|-----------------------------------|---------------------------------------------------------------|--------------------------|-----|--------------------------|-------|--|

| LVCMOS INPUTS (PD, X1 as a reference INPUT CLK)  |                                   |                                                               |                          |     |                          |       |  |

| Input High Level                                 | VIH1                              |                                                               | 2.0                      |     | V <sub>DD</sub>          | V     |  |

| Input Low Level                                  | VIL1                              |                                                               | 0                        |     | 0.8                      | V     |  |

| Input Current High Level                         | liH1                              | V <sub>IN</sub> = V <sub>DD</sub>                             |                          |     | 20                       | μΑ    |  |

| Input Current Low Level                          | lı∟1                              | V <sub>IN</sub> = 0                                           | -20                      |     |                          | μA    |  |

| THREE-LEVEL INPUTS (FS0, FS                      | S1, FS2, as FS                    | 62 = open)                                                    |                          |     |                          |       |  |

| Input High Level                                 | VIH2                              |                                                               | 2.5                      |     |                          | V     |  |

| Input Low Level                                  | V <sub>IL2</sub>                  |                                                               |                          |     | 0.8                      | V     |  |

| Input Open Level                                 | V <sub>IO2</sub>                  |                                                               | 1.27                     |     | 2.10                     | V     |  |

| Input Current                                    | IIL2, IIH2                        | $V_{IL2} = 0 \text{ or } V_{IH2} = V_{DD}$                    | -10                      |     | +10                      | μΑ    |  |

| SERIAL INTERFACE (SCL, SDA                       | (Note 2) (MA                      | X9471)                                                        |                          |     |                          |       |  |

| Input High Level                                 | V <sub>IH</sub>                   |                                                               | 0.7 x<br>V <sub>DD</sub> |     |                          | V     |  |

| Input Low Level                                  | VIL                               |                                                               |                          |     | 0.3 x<br>V <sub>DD</sub> | V     |  |

| Input-Leakage Current                            | l <sub>IH</sub> , l <sub>IL</sub> |                                                               | -1                       |     | +1                       | μΑ    |  |

| Low-Level Output                                 | Vol                               | I <sub>SINK</sub> = 4mA                                       |                          |     | 0.4                      | V     |  |

| Input Capacitance                                | CI                                | (Note 3)                                                      |                          | 8.4 |                          | рF    |  |

| CLOCK OUTPUTS (CLK_)                             |                                   |                                                               |                          |     |                          |       |  |

| Output High Level                                | V <sub>OH</sub>                   | I <sub>OH</sub> = -4mA                                        | V <sub>DD</sub> -<br>0.6 |     |                          | V     |  |

| Output Low Level                                 | VOL                               | $I_{OL} = 4mA$                                                |                          |     | 0.4                      | V     |  |

| POWER SUPPLIES                                   | •                                 | 1                                                             |                          |     |                          |       |  |

| Digital Power-Supply Voltage                     | V <sub>DD</sub>                   |                                                               | 3.0                      |     | 3.6                      | V     |  |

| Analog Power-Supply Voltage                      | Vdda                              |                                                               | 3.0                      |     | 3.6                      | V     |  |

| Total Current for Digital and<br>Analog Supplies | IDC                               | CLK1 at 125MHz and CLK2 at 74.1758MHz; all outputs not loaded |                          | 12  |                          | mA    |  |

| Total Power-Down Current                         | IPD                               | $\overline{PD} = low$                                         |                          | 60  |                          | μA    |  |

## **AC ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = V<sub>DDA</sub> = +3.0V to +3.6V, T<sub>A</sub> = -40°C to +25°C. Typical values are at V<sub>DD</sub> = V<sub>DDA</sub> = 3.3V, T<sub>A</sub> = +25°C with  $f_{XTL}$  = 27MHz, unless otherwise noted.) (Note 3)

| PARAMETER                 | SYMBOL            | CONDITIONS                                                                                | MIN  | ТҮР  | MAX | UNITS |

|---------------------------|-------------------|-------------------------------------------------------------------------------------------|------|------|-----|-------|

| OUTPUT CLOCKS (CLK1, CLK2 | 2)                |                                                                                           |      |      |     | •     |

| Minimum Frequency Range   | fout              | $f_{IN} = 5MHz$ to $50MHz$                                                                | 4    |      |     | MHz   |

| Maximum Frequency Range   | fout              | $f_{IN} = 5MHz$ to 50MHz, $C_L < 5pF$                                                     | 133  | 200  |     | MHz   |

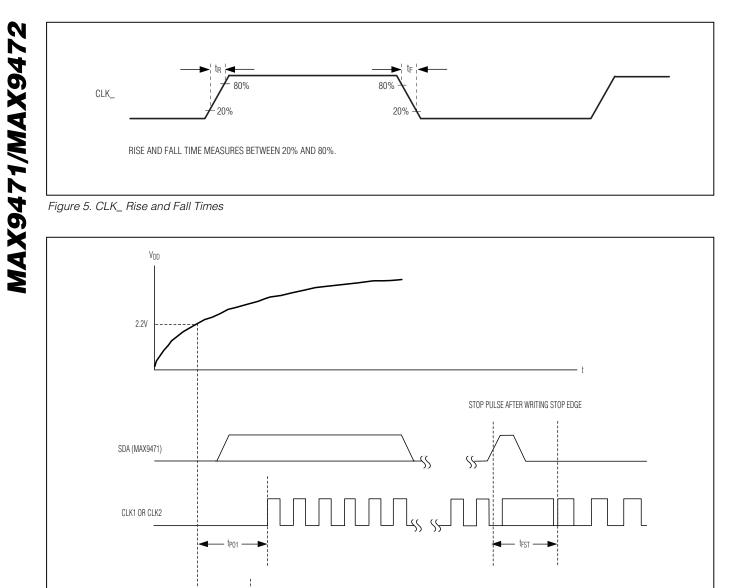

| Clock Rise Time           | t <sub>R</sub>    | 20% to 80% of V <sub>DD</sub> , $C_L$ = 10pF,<br>f <sub>OUT</sub> = 74.1758MHz (Figure 5) |      | 1.4  |     | ns    |

| Clock Fall Time           | t <sub>F</sub>    | 80% to 20% of $V_{DD}$ , $C_L = 10$ pF,<br>f <sub>OUT</sub> = 74.1758MHz (Figure 5)       |      | 1.2  |     | ns    |

| Duty Cycle                |                   | $f_{OUT} = 74.1758MHz, C_L = 10pF$                                                        | 42   | 50   | 58  | %     |

|                           |                   | 125MHz, $C_L = 5pF$ , $f_{IN} = 27MHz$                                                    |      | 26.3 |     |       |

| Output Period Jitter      | JP                | $\begin{array}{l} 74.1758MHz,C_L=10pF,\\ f_{IN}=27MHz \end{array}$                        |      | 33.6 |     | RMSps |

| Soft Power-On Time        | tfst              | SDA from low to high,<br>$f_{OUT} = 71.1758MHz$ , $f_{IN} = 13MHz$<br>(Figure 6)          | 1    |      | ms  |       |

| Hard Power-On Time        | tPO1              | (Figure 6)                                                                                | 15   |      | ms  |       |

| VCXO CLOCKS (CLK3, CLK4)  |                   | ·                                                                                         |      |      |     | •     |

| Crystal Frequency         | fxtl              |                                                                                           |      | 27   |     | MHz   |

| Crystal Accuracy          |                   |                                                                                           |      | ±30  |     | ppm   |

| Tuning Voltage Range      | V <sub>TUNE</sub> |                                                                                           | 0.0  |      | 3.0 | V     |

| VCXO Tuning Range         |                   | $V_{TUNE} = 0$ to 3V, $C_1 = C_2 = 4.0$ pF                                                | ±150 | ±200 |     | ppm   |

| TUNE Input Impedance      | Z <sub>TUNE</sub> |                                                                                           |      | 95   |     | kΩ    |

| Output CLK Accuracy       |                   | $V_{TUNE} = 1.5V, C_1 = C_2 = 4.0pF$                                                      |      | ±50  |     | ppm   |

| Output Duty Cycle         |                   | C <sub>L</sub> = 10pF load, CLK3                                                          | 40   | 50   | 60  | %     |

| Output Period Jitter      |                   | $C_L = 10 pF$                                                                             |      | 36   |     | RMSps |

| Output Rise Time          | t <sub>R</sub>    | 20% to 80% of V <sub>DD</sub> (Figure 5), $C_L$ = 10pF                                    | 1.4  |      | ns  |       |

| Output Fall Time          | t⊨                | 80% to 20% of V <sub>DD</sub> (Figure 5), $C_L$ = 10pF                                    | 1.4  |      | ns  |       |

## SERIAL-INTERFACE TIMING CHARACTERISTICS (MAX9471)

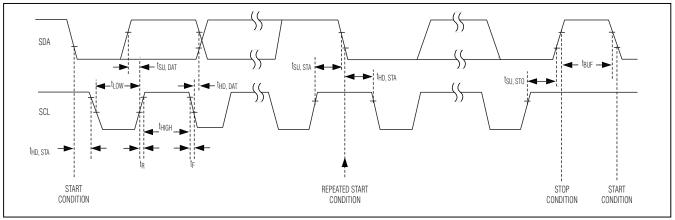

$(V_{DD} = V_{DDA} = +3.3V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 1, Figure 2)

| PARAMETER                                          | SYMBOL              | CONDITIONS   | MIN           | ТҮР | МАХ | UNITS |

|----------------------------------------------------|---------------------|--------------|---------------|-----|-----|-------|

| Serial Clock                                       | fscl                |              |               |     | 400 | kHz   |

| Bus Free Time Between STOP<br>and START Conditions | t <sub>BUF</sub>    |              | 1.3           |     |     | μs    |

| Hold Time, Repeated START<br>Condition             | <sup>t</sup> HD,STA |              | 0.6           |     |     | μs    |

| Repeated START Condition<br>Setup Time             | tsu,sta             |              | 0.6           |     |     | μs    |

| STOP Condition Setup Time                          | tsu,sto             |              | 0.6           |     |     | μs    |

| Data Hold Time                                     | thd,dat             | (Note 4)     | 15            |     | 900 | ns    |

| Data Setup Time                                    | tsu,dat             |              | 100           |     |     | ns    |

| SCL Clock Low Period                               | tlow                |              | 1.3           |     |     | μs    |

| SCL Clock High Period                              | thigh               |              | 0.7           |     |     | μs    |

| Rise Time of SDA and SCL,<br>Receiving             | t <sub>R</sub>      | (Notes 3, 5) | 20 +<br>0.1Cb |     | 300 | ns    |

| Fall Time of SDA and SCL,<br>Receiving             | tF                  | (Notes 3, 5) | 20 +<br>0.1Cb |     | 300 | ns    |

| Fall Time of SDA, Transmitting                     | tf,tx               | (Notes 3, 6) | 20 +<br>0.1Cb |     | 250 | ns    |

| Pulse Width of Spike Suppressed                    | tsp                 | (Notes 3, 7) | 0             |     | 50  | ns    |

| Capacitive Load for Each<br>Bus Line               | Cb                  | (Note 3)     |               |     | 400 | pF    |

Note 1: All parameters are tested at TA = +25°C. Specifications over temperature are guaranteed by design.

Note 2: No high-output level is specified, only the output resistance to the bus. Pullup resistors on the bus provide the high-level voltage.

Note 3: Guaranteed by design.

Note 4: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

Note 5:  $C_b$  = total capacitance of one bus line in pF. t<sub>R</sub> and t<sub>F</sub> measured between 0.3 x V<sub>DD</sub> and 0.7 x V<sub>DD</sub>.

Note 6: Bus sink current is less than 6mA. C<sub>b</sub> is the total capacitance of one bus line in pF. t<sub>R</sub> and t<sub>F</sub> are measured between 0.3 x V<sub>DD</sub> and 0.7 x V<sub>DD</sub>.

Note 7: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

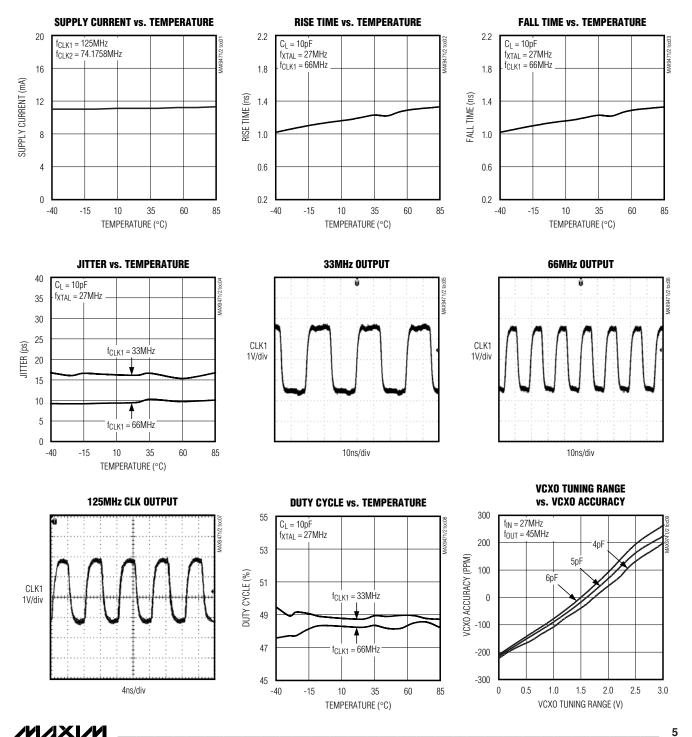

## **Typical Operating Characteristics**

(V<sub>DD</sub> = V<sub>DDA</sub> = +3.3V, T<sub>A</sub> = +25°C, f<sub>XTL</sub> = 27MHz, unless otherwise noted.)

MAX9471/MAX9472

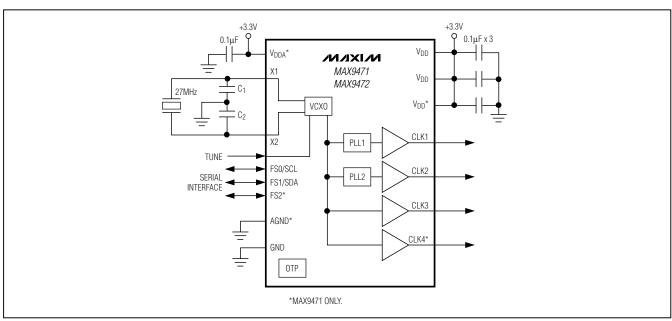

## **Typical Operating Circuit/Block Diagram**

## **Pin Description**

| PIN        |           |                  | FUNCTION                                                                                                                |  |

|------------|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| MAX9471    | MAX9472   | NAME             | FUNCTION                                                                                                                |  |

| 1          | 5         | TUNE             | VCXO Tune Voltage Input. If using a reference clock input, connect TUNE to VDD.                                         |  |

| 2          | —         | V <sub>DDA</sub> | Analog Power Supply. Bypass to GND with a 0.1µF capacitor.                                                              |  |

| 3          | —         | AGND             | Analog Ground                                                                                                           |  |

| 4, 10, 11  | 6, 10, 11 | GND              | Ground                                                                                                                  |  |

| 5          | 7         | CLK1             | Output Clock 1. PLL1 buffered output.                                                                                   |  |

| 6          | 8         | CLK2             | Output Clock 2. PLL2 buffered output.                                                                                   |  |

| 7          | 9         | CLK3             | Output Clock 3. VCXO buffered output.                                                                                   |  |

| 8          | —         | CLK4             | Output Clock 4. VCXO buffered output.                                                                                   |  |

| 9          | —         | I.C.             | Internally Connected. Leave unconnected.                                                                                |  |

| 12, 13, 16 | 4, 12     | V <sub>DD</sub>  | Power Supply. Bypass to GND with a 0.1µF capacitor.                                                                     |  |

| 14         | —         | FS2              | Function Select 2                                                                                                       |  |

| 15         | 13        | PD               | Active-Low, Power-Down Input. Pull high for normal operation, drive PD low to place MAX9471/MAX9472 in power-down mode. |  |

| 17         | 14        | X2               | Crystal Connection 2. Leave open if using a reference clock.                                                            |  |

| 18         | 1         | X1               | Crystal Connection 1 or Reference Clock Input                                                                           |  |

| 19         | _         | FS0/SCL          | Function Select 0/Serial Clock. Set FS2 high to place the device in I <sup>2</sup> C mode (see Table 1).                |  |

| 20         |           | FS1/SDA          | Function Select 1/Serial Data. Set FS2 high to place the device in I <sup>2</sup> C mode (see Table 1).                 |  |

| _          | 2         | FS1              | Function Select 1                                                                                                       |  |

|            | 3         | FS0              | Function Select 0                                                                                                       |  |

| EP         |           | EP               | Exposed Pad (MAX9471 only). Connect EP to GND.                                                                          |  |

MAX9471/MAX9472

# **Detailed Description**

The MAX9471/MAX9472 have two programmable fractional-N feedback PLLs so that almost any frequencies between 4MHz to 200MHz can be generated. The MAX9471 provides four outputs: two for the PLLs and two for the reference clock. The MAX9472 provides three outputs: two for the PLLs and one for the reference clock. The crystal frequency can be between 5MHz and 30MHz. The internal VCXO has a fine-tuning range of  $\pm$ 200ppm.

Power-Down

Driving  $\overline{\text{PD}}$  low places the MAX9471/MAX9472 in power-down mode.  $\overline{\text{PD}}$  overrides all other functions, setting all outputs to high impedance and shutting down the two PLLs. Every output has an 80k $\Omega$  (typ) internal pulldown resistor.

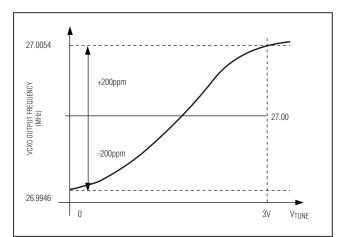

#### Voltage-Controlled Crystal Oscillator (VCXO)

The MAX9471/MAX9472s' internal VCXO produces a reference clock for the PLLs used to generate the output clocks. The oscillator uses a crystal clock as the base frequency reference and has a voltage-controlled tuning input for micro adjustment in a range of  $\pm$ 200ppm. The tuning voltage V<sub>TUNE</sub> can vary from 0V to 3V as shown in Figure 1. The crystal should be AT cut and oscillate on its fundamental mode with  $\pm$ 30ppm accuracy. The crystal should be less than 10pF, including board parasitic capacitance. To achieve up to  $\pm$ 200ppm pullability, the crystal-loading capacitance should be less than 14pF. The VCXO is a free-running oscillator. It starts oscillating with an internal POR signal and can be disabled by PD. VCXO settles at approximately 5ms at power-on and 10µs at a change of the V<sub>TUNE</sub> voltage.

Figure 1. VCXO Tuning Range for a 27MHz Crystal

Choosing different  $C_1$  and  $C_2$  capacitors allows flexibility for centering the various crystals. See the *Typical Operating Characteristics* for an example.

To use the MAX9471/MAX9472 as a synthesizer with an input reference clock, connect the input clock to X1 and TUNE to  $V_{DD}$ , and leave X2 unconnected. This configuration is for applications where the micro tuning is not needed, and there is a system reference clock available.

#### **One-Time Programmable Memory**

The MAX9471/MAX9472 feature a factory-configurable, OTP memory for nonvolatile applications allowing for simple and permanent clock generation. Contact the factory for presetting the MAX9471/MAX9472 to requested frequencies.

Using OTP, the MAX9471/MAX9472 can be configured to two different configurations. One configuration is to have PLL1 set to any frequency between 4MHz to 200MHz and select the PLL2's frequency by I<sup>2</sup>C (MAX9471) or programmable pins. The second configuration is to preset the frequencies in PLL1 and PLL2 to fixed values between 4MHz to 200MHz. In both cases, the reference output is available, but it can be disabled by OTP. At power-up, all the outputs are enabled.

#### **Frequency Selection of CLK2 Output**

The OTP ROM can set PLL2's output to be selectable from a group of frequencies that are common for MPEG video and audio applications. The frequency selection can be done by the FS\_ inputs or through the I<sup>2</sup>C interface (MAX9471). For the MAX9471, pull FS2 high (Table 1) to select the PLL2 frequency through the I<sup>2</sup>C interface. Otherwise, the frequencies are selected according to Table 2. For the MAX9471, Table 3 shows the mappings for I<sup>2</sup>C programming.

#### Serial Interface (MAX9471)

The MAX9471 can be programmed through a 2-wire,  $I^2C$ -compatible serial interface. The device is activated after power-up and FS2 = high. The device operates as a slave that sends and receives data through clock line SCL and data line SDA for bidirectional communication with the master. A master (typically a microcontroller) initiates all data transfers to and from the MAX9471 and

# Table 1. Mode Selection by FS2(MAX9471 Only)

| FS2         | MODE                     |

|-------------|--------------------------|

| Low or open | Pin programmable         |

| High        | I <sup>2</sup> C enabled |

| FS2               | FS1   | FS0      | FREQUENCY (MHz)                                      |  |  |  |  |

|-------------------|-------|----------|------------------------------------------------------|--|--|--|--|

| AUDIO FREQUENCIES |       |          |                                                      |  |  |  |  |

| Open              | Open  | Open     | 4.096                                                |  |  |  |  |

| Open              | Open  | Low      | 6.144                                                |  |  |  |  |

| Open              | Open  | High     | 8.1920                                               |  |  |  |  |

| Open              | Low   | High     | 11.2896                                              |  |  |  |  |

| Open              | Low   | Open     | 12.2880                                              |  |  |  |  |

| Open              | Low   | Low      | 16.3840                                              |  |  |  |  |

| Open              | High  | High     | 22.5792                                              |  |  |  |  |

| Open              | High  | Open     | 24.5760                                              |  |  |  |  |

| Open              | High  | Low      | 9.216                                                |  |  |  |  |

| Low               | Open  | High     | 16.9344                                              |  |  |  |  |

| Low               | Open  | Open     | 18.4320                                              |  |  |  |  |

| Low               | Open  | Low      | 33.8688                                              |  |  |  |  |

| Low               | High  | High     | 36.864                                               |  |  |  |  |

|                   | VIDEC | FREQUENC | IES                                                  |  |  |  |  |

| Low               | Low   | Low      | 74.1758241                                           |  |  |  |  |

| Low               | Low   | High     | 74.25                                                |  |  |  |  |

| Low               | Low   | Open     | 54.054                                               |  |  |  |  |

| High              | х     | Х        | Disable three-level pins and enable I <sup>2</sup> C |  |  |  |  |

# Table 2. MAX9471/MAX9472 FrequencySelection at CLK2

## Table 3. MAX9471 I<sup>2</sup>C Frequency Selection at CLK2 (FS2 = High)

| A4 | A3                | A2 | A1 | FREQUENCY (MHz) |  |  |  |  |  |  |

|----|-------------------|----|----|-----------------|--|--|--|--|--|--|

|    | AUDIO FREQUENCIES |    |    |                 |  |  |  |  |  |  |

| 0  | 0                 | 0  | 0  | 4.096           |  |  |  |  |  |  |

| 0  | 0                 | 0  | 1  | 6.144           |  |  |  |  |  |  |

| 0  | 0                 | 1  | 0  | 8.1920          |  |  |  |  |  |  |

| 0  | 0                 | 1  | 1  | 11.2896         |  |  |  |  |  |  |

| 0  | 1                 | 0  | 0  | 12.2880         |  |  |  |  |  |  |

| 0  | 1                 | 0  | 1  | 16.3840         |  |  |  |  |  |  |

| 0  | 1                 | 1  | 0  | 22.5792         |  |  |  |  |  |  |

| 0  | 1                 | 1  | 1  | 24.5760         |  |  |  |  |  |  |

| 1  | 0                 | 0  | 0  | 9.216           |  |  |  |  |  |  |

| 1  | 0                 | 0  | 1  | 16.9344         |  |  |  |  |  |  |

| 1  | 0                 | 1  | 0  | 18.4320         |  |  |  |  |  |  |

| 1  | 0                 | 1  | 1  | 33.8688         |  |  |  |  |  |  |

| 1  | 1                 | 0  | 0  | 36.864          |  |  |  |  |  |  |

|    | VIDEO FREQUENCIES |    |    |                 |  |  |  |  |  |  |

| 1  | 1                 | 0  | 1  | 74.1758241      |  |  |  |  |  |  |

| 1  | 1                 | 1  | 0  | 74.25           |  |  |  |  |  |  |

| 1  | 1                 | 1  | 1  | 54.054          |  |  |  |  |  |  |

\*MAX9472 can be programmed to FS2 = open settings only.

Figure 2. I<sup>2</sup>C Timing Diagram

generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open-drain output. A pullup resistor, typically 4.7k $\Omega$ , is required on SDA. The SCL line operates only as an

input. A pullup resistor, typically 4.7k $\Omega$ , is required on SCL if there are multiple masters on the 2-wire bus, or if the master in a single-master system has an open-drain SCL output. Figure 2 is the I<sup>2</sup>C timing diagram.

#### **Device Address**

The default I<sup>2</sup>C address for the MAX9471 is factory set to 1100111. Contact factory for different addresses.

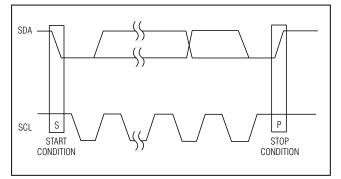

#### START and STOP Conditions

Both SCL and SDA remain high when the interface is not busy. The active master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 3).

Figure 3. START and STOP Diagram

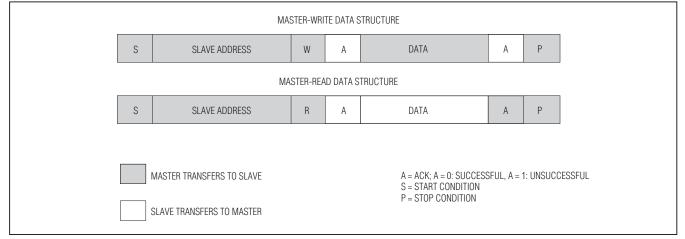

Following the START condition, each SCL clock pulse transfers 1 bit. Between a START and a STOP, multiple bits are transferred on the 2-wire bus. The first 7 bits are for the device address. Bit 8 indicates the writing (low) or reading (high) operation ( $R/\overline{W}$ ). Bit 9 is the ACK for the address and operation type. The next 8 bits (bit 10 to bit 17) form the content byte. The next bit, bit 18, is the ACK for the content byte. The master always transfers the first 8 bits (address +  $R/\overline{W}$ ). The slave (MAX9471) may receive a content byte from the bus or transfer a content byte to the bus. The ACK bits are transmitted by the address or content recipient. A low-ACK bit indicates a successful transfer; otherwise, a high-ACK bit indicates an unsuccessful transfer. More content bytes can be continuously transferred until the master sends a STOP. For the MAX9471 data writing, after the 9 bits with the slave ID. R/W. and ACK. 1 data byte is sent to the MAX9471 from the master. Figure 4 shows the structure of the data transfer. Figure 5 shows CLK\_ rise and fall times.

Data Transfer and ACK

Figure 4. Serial-Interface Data Structure

Figure 6. VCXO and PLL Timing Diagram

• t<sub>PO2</sub> –

CLK3 OR CLK4

### **Applications Information**

#### **Crystal Selection**

When using a crystal with the MAX9471/MAX9472s' internal oscillator, connect the crystal to X1 and X2. Choose an AT-cut crystal that oscillates on its fundamental mode with ±30ppm and loading capacitance less than 14pF. To achieve a wide VCXO tuning range, select a crystal with motional capacitance greater than 7fF and connect 6pF or less shunt capacitors at X1 and X2 to ground. When the VCXO is used as an oscillator, select both shunt capacitors to be approximately 13pF. The optimal shunt capacitors for achieving minimum frequency offset can be determined experimentally.

#### Board Layout Considerations and Bypassing

The MAX9471/MAX9472s' oscillator frequencies make proper layout important to ensure stability. For best performance, place components as close as possible to the device.

Digital or AC transient signals on GND can create noise at the clock output. Return GND to the highest quality ground available. Bypass each  $V_{DD}$  and  $V_{DDA}$  with a 0.1µF capacitor, placed as close as possible to the device. Careful PC board ground layout minimizes crosstalk between the outputs and digital inputs.

# **Pin Configurations (continued)**

## \_Chip Information

PROCESS: CMOS

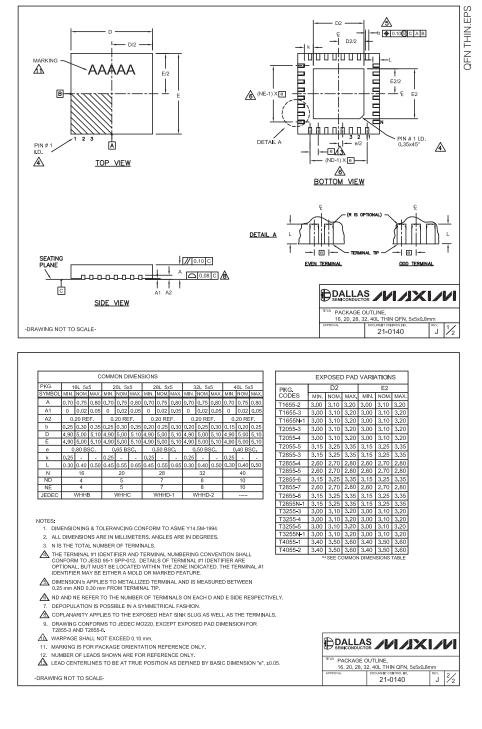

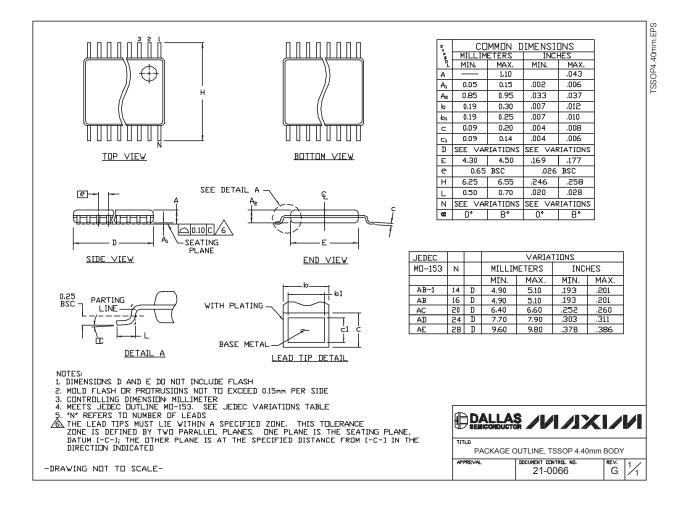

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages</u>.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

is a registered trademark of Maxim Integrated Products, Inc.