# 3.3/2.5-V Phase-lock Loop Clock Driver

# HITACHI

ADE-205-222E (Z) 6th. Edition July 1999

### Description

The HD74CDC857 is a high-performance, low-skew, low-jitter, phase locked loop clock driver. It is specifically designed for use with DDR (Double Data Rate) synchronous DRAMs.

#### Features

- Supports 100 MHz to 150 MHz operation range \*1

- Distributes one differential clock input pair to ten differential clock outputs pairs

- SSTL\_2 (Stub Series Terminated Logic) differential inputs and LVCMOS reset (G) input

- Supports spread spectrum clock

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input

- Supports both 3.3 V/2.5V analog supply voltage (AV<sub>CC</sub>), and 2.5 V  $V_{DDO}$

- No external RC network required

- Sleep mode detection

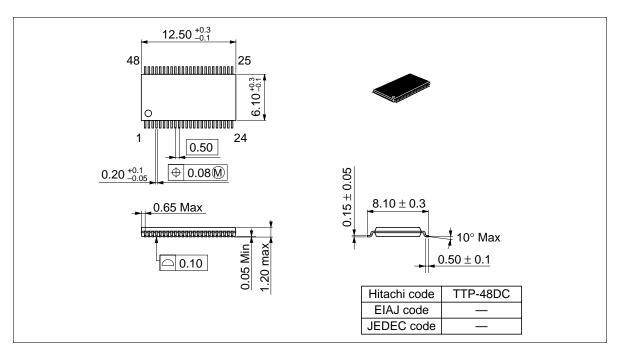

- 48pin TSSOP (Thin Shrink Small Outline Package)

- Note: 1. 200 MHz (Max) ver. will be available by 4Q/'99

### **Function Table**

| Inputs |          |       | : | Outpu | ıts |       |       | : | PLL |

|--------|----------|-------|---|-------|-----|-------|-------|---|-----|

| G      | CLK      | CLK   |   | Y     | Ŷ   | FBOUT | FBOUT | - |     |

| L      | L        | Н     | : | Z     | Z   | Z     | Z     | : | off |

| L      | Н        | L     | : | Z     | Z   | Z     | Z     | : | off |

| Н      | L        | Н     |   | L     | Н   | L     | Н     | : | run |

| Н      | Н        | L     |   | Н     | L   | Н     | L     | : | run |

| Х      | 0 MHz    | 0 MHz | : | Z     | Z   | Z     | Z     | : | off |

|        | 1° 1 1 1 |       |   |       |     |       |       |   |     |

H: High level

L: Low level

Z : High impedance

X : Don't care

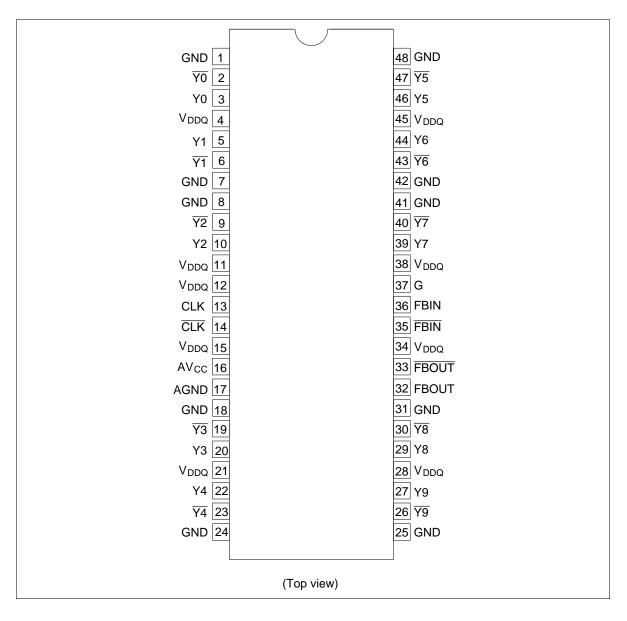

#### **Pin Arrangement**

### **Absolute Maximum Ratings**

| ltem                                                               | Symbol                                                         | Ratings                          | Unit | Conditions               |

|--------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------|------|--------------------------|

| Supply voltage                                                     | V <sub>DDQ</sub>                                               | -0.5 to 4.6                      | V    |                          |

| Input voltage                                                      | V                                                              | -0.5 to 4.6                      | V    |                          |

| Output voltage <sup>*1</sup>                                       | Vo                                                             | –0.5 to V <sub>DDQ</sub><br>+0.5 | V    |                          |

| Input clamp current                                                | I <sub>IK</sub>                                                | -50                              | mA   | V <sub>1</sub> < 0       |

| Output clamp current                                               | Ι <sub>οκ</sub>                                                | -50                              | mA   | V <sub>0</sub> < 0       |

| Continuous output current                                          | I <sub>o</sub>                                                 | ±50                              | mA   | $V_{o} = 0$ to $V_{DDQ}$ |

| Supply current through each $V_{DDQ}$ or GND                       | $\mathbf{I}_{\text{VDDQ}} \text{ or } \mathbf{I}_{\text{GND}}$ | ±100                             | mA   |                          |

| Maximum power dissipation<br>at Ta = $55^{\circ}$ C (in still air) |                                                                | 0.7                              | W    |                          |

| Storage temperature                                                | T <sub>stg</sub>                                               | -65 to +150                      | °C   |                          |

Notes: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

1. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

### **Recommended Operating Conditions**

| Item                                            | Symbol           | Min                           | Тур  | Max                           | Unit | Conditions                                  |

|-------------------------------------------------|------------------|-------------------------------|------|-------------------------------|------|---------------------------------------------|

| Supply voltage                                  | $AV_{cc}$ (1)    | 2.3                           | _    | 2.7                           | V    | $f_{\rm CLK}$ = 100 to 150 MHz              |

|                                                 | $AV_{CC}$ (2)    | 3.0                           | _    | 3.6                           | _    | $f_{CLK} = 130 \text{ to } 150 \text{ MHz}$ |

| Output supply voltage                           | V <sub>DDQ</sub> | 2.3                           | _    | 2.7                           | V    |                                             |

| DC input signal voltage *1                      |                  | -0.3                          | _    | $V_{DDQ}$ +0.3                | V    | All pins                                    |

| High level input voltage                        | $V_{\text{IHD}}$ | 1.7                           | _    | _                             | V    |                                             |

| Low level input voltage                         | V <sub>ILD</sub> |                               | —    | 0.8                           | V    |                                             |

| High level input voltage                        | V <sub>IHG</sub> | 1.7                           | _    | $V_{DDQ}$ +0.3                | V    | G input pin                                 |

| Low level input voltage                         | V <sub>ILG</sub> | -0.3                          | _    | 0.7                           | V    | G input pin                                 |

| Differential input signal voltage <sup>*2</sup> | V <sub>ID</sub>  | 0.36                          | _    | $V_{DDQ}$ +0.6                | V    | DC                                          |

|                                                 |                  | 0.7                           | _    | $V_{DDQ}$ +0.6                | _    | AC                                          |

| Differential cross point voltage '3             |                  | 0.5×V <sub>ddq</sub><br>-0.35 | _    | 0.5×V <sub>ddq</sub><br>+0.35 | V    |                                             |

| Reference voltage *4                            | V <sub>ref</sub> | 1.15                          | 1.25 | 1.35                          | V    | $Vref = 0.5 \times V_{\rm DDQ}$             |

| Output current                                  | I <sub>OH</sub>  | -7                            | _    | -30                           | mA   |                                             |

|                                                 | I <sub>OL</sub>  | 7                             | _    | 30                            | _    |                                             |

| Input slew rate                                 | SR               | 1                             | _    | _                             | V/ns |                                             |

| Operating temperature                           | T <sub>a</sub>   | 0                             | _    | 70                            | °C   |                                             |

Notes: Unused inputs must be held high or low to prevent them from floating.

Feedback inputs (FBIN, FBIN) may float when the device is in low power mode.

1. DC input signal voltage specifies the allowable dc execution of differential input.

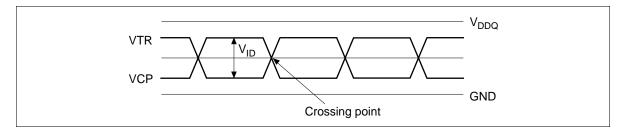

2. Differential input signal voltage specifies the differential voltage |VTR–VCP| required for switching, where VTR is the true input level and VCP is the complementary input level.

3. Differential cross point voltage is expected to track variations of V<sub>DDQ</sub> and is the voltage at which the differential signals must be crossing. (See figure1-1)

V<sub>ref</sub> is the reference DC level, when using single clock input. When CLK (pin#13) is single ended input, CLK (pin#14) must be set V<sub>ref</sub>. (See figure1-2)

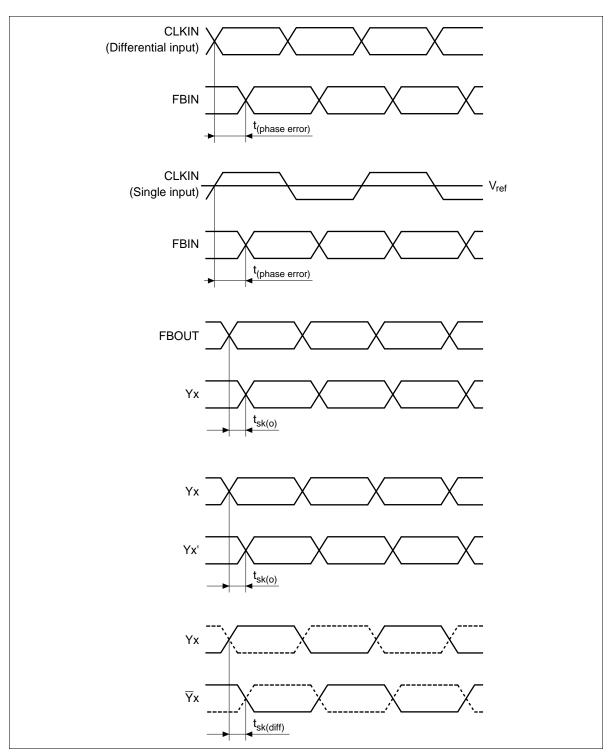

Figure 1-1 Differential input levels

Figure 1-2 Single input levels

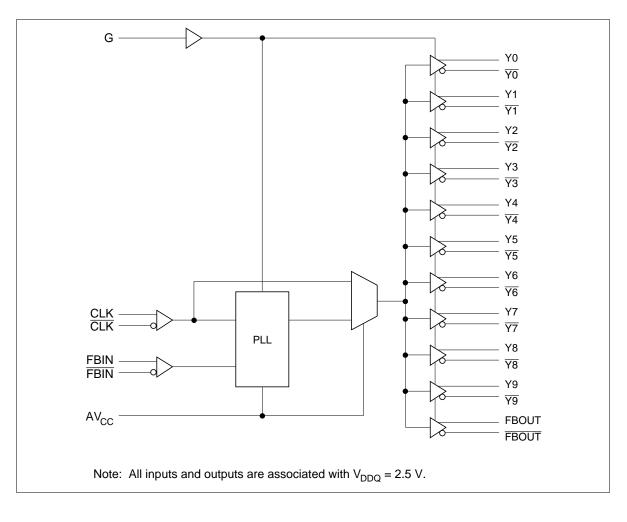

### Logic Diagram

# **Pin Function**

| Pin name         | No.                                        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------|--------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AGND             | 17                                         | Ground | Analog ground. AGND provides the ground reference for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| AV <sub>cc</sub> | 16                                         | Power  | Analog power supply. $AV_{cc}$ provides the power reference for the analog circuitry. In addition, $AV_{cc}$ can be used to bypass the PLL for test purposes. When $AV_{cc}$ is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs.                                                                                                                                                                                             |  |  |  |

| CLK, <u>CLK</u>  | 13, 14                                     | I      | Clock input. CLK provides the clock signal to be distributed by the HD74CDC857 clock driver. CLK is used to provide the reference signal to the integrated PLL that generates the clock output signals. CLK must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the circuit is powered up and a valid CLK signal is applied, a stabilization time is required for the PLL to phase lock the feedback signal to its reference signal. |  |  |  |

| FBIN, FBIN       | 35, 36                                     | I      | Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hard-wired to FBOUT to complete the PLL. The integrated PLL synchronizes CLK and FBIN so that there is nominally zero phase error between CLK and FBIN.                                                                                                                                                                                                                         |  |  |  |

| FBOUT, FBOUT     | 32, 33                                     | 0      | Feedback output. FBOUT is dedicated for external feedback. It switches at the same frequency as CLK. When externally wired to FBIN, FBOUT completes the feedback loop of the PLL.                                                                                                                                                                                                                                                                                   |  |  |  |

| G                | 37                                         | I      | Output bank enable. G is the output enable for all outputs. When G is low, VCO will stop and all outputs are disabled to a high impedance state. When G will be returned high, PLL will resynchroniz to CLK frequency and all outputs are enabled.                                                                                                                                                                                                                  |  |  |  |

| GND              | 1, 7, 8, 18,<br>24, 25, 31,<br>41, 42, 48  | Ground | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| V <sub>DDQ</sub> | 4, 11, 12,<br>15, 21, 28,<br>34, 38, 45    | Power  | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Y                | 3, 5, 10, 20,<br>22, 27, 29,<br>39, 44, 46 | 0      | Clock outputs. These outputs provide low-skew copies of CLK.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Ŷ                | 2, 6, 9, 19,<br>23, 26, 30,<br>40, 43, 47  | 0      | Clock outputs. These outputs provide low-skew copies of $\overline{\text{CLK}}$ .                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

### **Electrical Characteristics**

| Item                                          | Symbol          | Min                  | Typ <sup>⁺1</sup> | Max  | Unit | Test Conditions                                                  |

|-----------------------------------------------|-----------------|----------------------|-------------------|------|------|------------------------------------------------------------------|

| Input clamp CLK, CLK<br>voltage FBIN, FBIN, G | V <sub>IK</sub> | _                    | _                 | -1.2 | V    | $I_1 = -18 \text{ mA}, V_{DDQ} = 2.3 \text{ V}$                  |

| Output voltage                                | V <sub>OH</sub> | V <sub>cc</sub> -0.2 | _                 | —    | V    | $I_{_{OH}}$ = –100 $\mu A,V_{_{CC}}$ = 2.3 to 2.7 V              |

|                                               |                 | 1.95                 | _                 | —    |      | $I_{OH} = -8 \text{ mA}, V_{CC} = 2.3 \text{ V}$                 |

|                                               |                 | 1.70                 | —                 | —    |      | $I_{OH} = -16 \text{ mA}, V_{CC} = 2.3 \text{ V}$                |

|                                               | V <sub>OL</sub> | _                    | —                 | 0.2  |      | $I_{_{OL}}$ = 100 $\mu A,V_{_{CC}}$ = 2.3 to 2.7 V               |

|                                               |                 | _                    | _                 | 0.35 |      | $I_{oL}$ = 8 mA, $V_{cc}$ = 2.3 V                                |

|                                               |                 | _                    | —                 | 0.55 |      | $I_{oL} = 16 \text{ mA}, V_{cc} = 2.3 \text{ V}$                 |

| Input current                                 | $I_1$           | _                    | _                 | ±10  | μΑ   | $V_{I} = 0 \text{ V to } 2.7 \text{ V}, V_{DDQ} = 2.7 \text{ V}$ |

| Input capacitance                             | C               | _                    | _                 | 4    | pF   |                                                                  |

Note: 1. For conditions shown as Min or Max, use the appropriate value specified under recommended operating conditions.

### **Switching Characteristics**

| Item                    | Symbol                     | Min  | Тур | Max               | Unit | Test Conditions                                                 |  |

|-------------------------|----------------------------|------|-----|-------------------|------|-----------------------------------------------------------------|--|

| Cycle to cycle jitter   |                            | -100 | _   | 100               | ps   | See figure 2                                                    |  |

| Phase error time        | t <sub>(phase error)</sub> | -150 |     | 150               | ps   | See figure 2, 3, 4                                              |  |

| Output skew             | t <sub>sk (o)</sub>        | _    |     | 200               | ps   | See figure 2                                                    |  |

| Differential clock skew | $t_{_{sk}(diff)}$          | -100 |     | 100               | ps   | See figure 2                                                    |  |

| Duty cycle              |                            | 45   |     | 55                | %    | See figure 2                                                    |  |

| Output impedance        | Zo                         | _    | 25  | _                 | Ω    | See figure 2                                                    |  |

| Clock frequency         | f <sub>CLK</sub>           | 100  |     | 150 *1            | MHz  | See figure 2, AV <sub>cc</sub> = $2.5\pm0.2$ V                  |  |

|                         |                            | 130  | _   | 150 <sup>*1</sup> |      | See figure 2, $AV_{cc}$ = 2.5±0.2 V<br>or $AV_{cc}$ = 3.3±0.3 V |  |

| Slew rate               |                            | 1.2  |     |                   | V/ns | See figure 2                                                    |  |

| Stabilization time      |                            |      |     | 0.1               | ms   | See figure 2, 3                                                 |  |

Note: 1. 200 MHz (Max) ver. will be available by 4Q/'99.

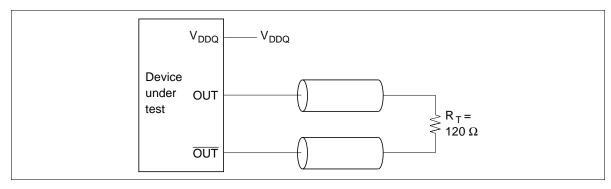

Differential clock outputs are directly terminated by a 120  $\Omega$  resistor. Figure 2 is typical usage conditions of outputs load.

Figure 2 Differential signal using direct termination resistor

Figure 3 CLKIN waveforms

Figure 4 Timings

### **Package Dimensions**

Unit : mm

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109 URL NorthAmerica http:semiconductor.hitachi.com/ http://www.hitachi-eu.com/hel/ecg Europe http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKong) http://www.hitachi.com.hk/eng/bo/grp3/index.htm http://www.hitachi.co.jp/Sicd/indx.htm Japan For further information write to: Hitachi Semiconductor Hitachi Europe GmbH Hitachi Asia Pte. Ltd. (America) Inc. Electronic components Group 16 Collyer Quay #20-00 179 East Tasman Drive, Dornacher Straße 3 Hitachi Tower San Jose,CA 95134 D-85622 Feldkirchen, Munich Singapore 049318 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Germany Tel: 535-2100 Tel: <49> (89) 9 9180-0 Fax: 535-1533 Fax: <49> (89) 9 29 30 00 Hitachi Asia Ltd. Hitachi Europe Ltd. Taipei Branch Office Electronic Components Group. Whitebrook Park 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105) Lower Cookham Road Tel: <886> (2) 2718-3666 Maidenhead Fax: <886> (2) 2718-8180 Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.