# **VGA Port Companion Circuit**

#### Features

- Single-chip solution for the VGA port interface

- Includes ESD protection, level shifting, and RGB termination

- Seven channels of ESD protection for all VGA port connector pins, meeting IEC-61000-4-2 Level-4 ESD requirements (8kV contact discharge)

- Very low loading capacitance from ESD protection diodes on VIDEO lines; 4pF typical

- 75Ω termination resistors for VIDEO lines (matched to 1% typ.)

- TTL to CMOS level-translating buffers with powerdown mode for HSYNC and VSYNC lines

- Bi-directional level shifting N-channel FETs provided for DDC\_CLK & DDC\_DATA channels

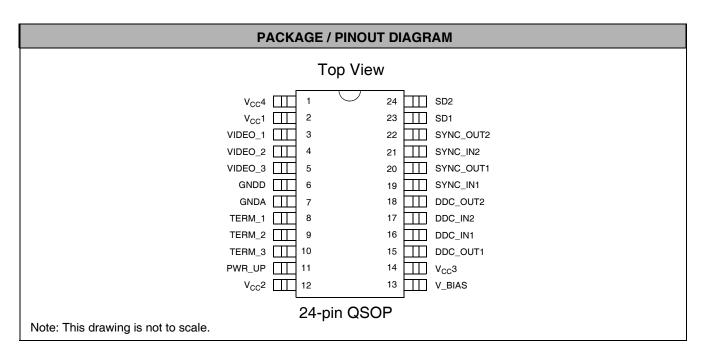

- Compact 24-pin QSOP package

- Lead-free version available

# Applications

- Notebook computers with VGA port

- Desktop PCs with VGA port

## **Product Description**

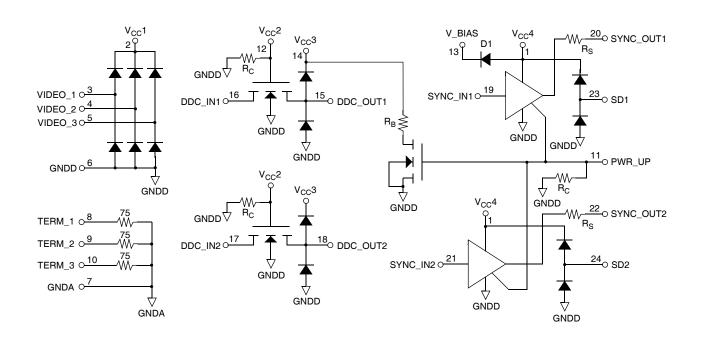

The PACVGA203 incorporates seven channels of ESD protection for all signal lines commonly found in a VGA port. ESD protection is implemented with current steering diodes designed to safely handle the high surge currents encountered with IEC-61000-4-2 Level-4 ESD Protection (8kV contact discharge). When a channel is subjected to an electrostatic discharge, the ESD current pulse is diverted via the protection diodes into either the positive supply rail or ground where it may be safely dissipated. Separate positive supply rails are provided for the VIDEO, DDC and SYNC channels to facilitate interfacing with low voltage Video Controller ICs and provide design flexibility in multi-supply-voltage environments.

Two non-inverting drivers provide buffering for the HSYNC and VSYNC signals from the Video Controller IC (SYNC\_IN1, SYNC\_IN2). These buffers accept TTL input levels and convert them to CMOS output levels that swing between Ground and  $V_{CC}4$  (cont'd next page).

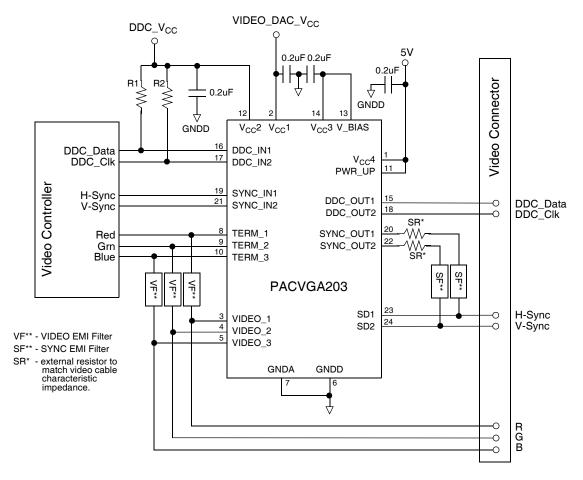

#### Simplified Electrical Schematic

### Product Description (cont'd)

These drivers have nominal  $15\Omega$  output impedance (R<sub>S</sub>) which can be combined with an external resistor to match the characteristic impedance of the HSYNC & VSYNC lines of the video cables typically used in PC applications. Two N-channel FETs provide the level shifting function required when the DDC controller is operated at a lower supply voltage than the monitor. Three 75 $\Omega$  resistors suitable for terminating the video signals from the video DAC are also provided. These resistors have separate input pins to allow insertion of additional EMI filtering, if required, between the termination point and the ESD protection diodes. These resistors are matched to better than 2% for excellent signal level matching of the R/G/B signals.

When the PWR\_UP input is driven LOW, the SYNC inputs can be floated without causing the SYNC buffers to draw any current from the  $V_{CC}4$  supply. When the PWR\_UP input is LOW the SYNC outputs are driven LOW.

$V_{CC}$ 3 can be derived from  $V_{CC}$ 4, if desired, by connecting  $V_{CC}$ 3 to  $V_B$ IAS. In applications where  $V_{CC}$ 4 may be powered down, diode D1 blocks any DC current paths from the DDC\_OUT pins back to the powered down  $V_{CC}$ 4 rail via the top ESD protection diodes.

The PACVGA203 device is housed in a 24-pin QSOP package and is available with optional lead-free finishing.

# **Ordering Information**

| PART NUMBERING INFORMATION |         |                     |              |                     |              |

|----------------------------|---------|---------------------|--------------|---------------------|--------------|

|                            |         | Standar             | rd Finish    | Lead-fre            | e Finish     |

|                            |         | Ordering Part       |              | Ordering Part       |              |

| Pins                       | Package | Number <sup>1</sup> | Part Marking | Number <sup>1</sup> | Part Marking |

| 24                         | QSOP-24 | PACVGA203Q          | PACVGA203Q   | PACVGA203QR         | PACVGA203QR  |

Note 1: Parts are shipped in Tape & Reel form unless otherwise specified.

| PIN DESCRIPTIONS |                              |                                                                                                                                                                              |  |  |  |  |

|------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LEAD(s)          | NAME                         | DESCRIPTION                                                                                                                                                                  |  |  |  |  |

| 1                | V <sub>CC</sub> 4            | Positive voltage supply pin. This is an isolated $V_{CC}$ pin for the SYNC_1, SYNC_2, SD1 and SD2 circuits.                                                                  |  |  |  |  |

| 2                | V <sub>CC</sub> 1            | Positive voltage supply pin. This is an isolated $V_{CC}$ pin for the VIDEO_1, VIDEO_2 and VIDEO_3 ESD circuits.                                                             |  |  |  |  |

| 3-5              | VIDEO_1, VIDEO_2,<br>VIDEO_3 | RGB Video Protection Channels. These pins tie to the RGB video lines (for example, the Blue signal) between the VGA controller device and the video connector.               |  |  |  |  |

| 6                | GNDD                         | Digital Ground reference supply pin.                                                                                                                                         |  |  |  |  |

| 7                | GNDA                         | Ground reference supply pin for TERM_1, TERM_2 and TERM_3 pins.                                                                                                              |  |  |  |  |

| 8-10             | TERM_1, TERM_2,<br>TERM_3    | RGB Video Termination Channels. These pins tie to the RGB video lines (for example, the Blue signal) providing a $75\Omega$ termination to GNDA for the given video channel. |  |  |  |  |

| 11               | PWR_UP                       | Sync Signal Output 1. Ties to the video connector side of one of the sync lines (for example the Horizontal Sync signal).                                                    |  |  |  |  |

| 12               | V <sub>CC</sub> 2            | Positive voltage supply pin. This is an isolated $V_{CC}$ pin for the DDC_IN1 and DDC_IN2 input circuits. Defines the logic one level for the DDC_OUTn outputs.              |  |  |  |  |

| 13               | V_BIAS                       | Used to derive V <sub>CC3</sub> from V <sub>CC4</sub> input.                                                                                                                 |  |  |  |  |

| 14               | V <sub>CC</sub> 3            | Positive voltage supply pin. This is an isolated $V_{CC}$ pin for the DDC_OUT1 and DDC_OUT2 ESD protection circuits.                                                         |  |  |  |  |

| 15               | DDC_OUT1                     | DDC Signal Output 1. Connects to the connector side of one of the DDC signals (for example, the bidirectional DDC_Data serial line).                                         |  |  |  |  |

| 16               | DDC_IN1                      | DDC Signal Input 1. Connects to the VGA Controller side of one of the DDC signals (for example, the bidirectional DDC_Data serial line).                                     |  |  |  |  |

| 17               | DDC_IN2                      | DDC Signal Input 2. Connects to the VGA Controller side of one of the DDC signals (for example, the bidirectional DDC_Clk).                                                  |  |  |  |  |

| 18               | DDC_OUT2                     | DDC Signal Output 2. Connects to the connector side of one of the DDC signals (for example, the bidirectional DDC_Clk).                                                      |  |  |  |  |

| 19               | SYNC_IN1                     | Sync Signal Buffer Input 1. Connects to the VGA Controller side of one of the sync lines (for example, the Horizontal Sync signal).                                          |  |  |  |  |

| 20               | SYNC_OUT1                    | Sync Signal Buffer Output 1. Connects to the video connector side of one of the sync lines (for example the Horizontal Sync signal).                                         |  |  |  |  |

| 21               | SYNC_IN2                     | Sync Signal Buffer Input 2. Connects to the VGA Controller side of one of the sync lines (for example, the Vertical Sync signal).                                            |  |  |  |  |

| 22               | SYNC_OUT2                    | Sync Signal Buffer Output 2. Connects to the video connector side of one of the sync lines (for example the Vertical Sync signal).                                           |  |  |  |  |

| 23               | SD1                          | Sync Signal Filter 1. Connects to the video connector side of one of the sync lines (for example the Vertical Sync signal).                                                  |  |  |  |  |

| 24               | SD2                          | Sync Signal Filter 2. Connects to the video connector side of one of the sync lines (for example the Horizontal Sync signal).                                                |  |  |  |  |

# Specifications

| ABSOLUTE MAXIMUM RATINGS                                                                                                                    |                                                                                                                                                                                                                                                                                                                                             |                       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| PARAMETER                                                                                                                                   | RATING                                                                                                                                                                                                                                                                                                                                      | UNITS                 |  |  |  |

| $V_{CC}1, V_{CC}2, V_{CC}3$ , and $V_{CC}4$ Supply Voltage                                                                                  | [GND - 0.5] to +6.0                                                                                                                                                                                                                                                                                                                         | V                     |  |  |  |

| Diode D1 Forward DC Current                                                                                                                 | 100                                                                                                                                                                                                                                                                                                                                         | μA                    |  |  |  |

| Operating Temperature Range                                                                                                                 | -40 to +85                                                                                                                                                                                                                                                                                                                                  | °C                    |  |  |  |

| Storage Temperature Range                                                                                                                   | -65 to +150                                                                                                                                                                                                                                                                                                                                 | °C                    |  |  |  |

| DC Voltage at Inputs<br>VIDEO_1, VIDEO_2, VIDEO_3<br>TERM_1, TERM_2, TERM_3<br>DDC_IN1, DDC_IN2<br>DDC_OUT1, DDC_OUT2<br>SYNC_IN1, SYNC_IN2 | $\begin{array}{c} (\text{GND - } 0.5) \text{ to } (\text{V}_{\text{CC}}\text{1} + 0.5) \\ & -6.0, +6.0 \\ (\text{GND - } 0.5) \text{ to } (\text{V}_{\text{CC}}\text{2} + 0.5) \\ (\text{GND - } 0.5) \text{ to } (\text{V}_{\text{CC}}\text{3} + 0.5) \\ (\text{GND - } 0.5) \text{ to } (\text{V}_{\text{CC}}\text{4} + 0.5) \end{array}$ | V<br>V<br>V<br>V<br>V |  |  |  |

| Package Power Rating                                                                                                                        | 1000                                                                                                                                                                                                                                                                                                                                        | mW                    |  |  |  |

| STANDARD OPERATING CONDITIONS |          |       |  |  |  |

|-------------------------------|----------|-------|--|--|--|

| PARAMETER                     | RATING   | UNITS |  |  |  |

| Operating Temperature Range   | 0 to +70 | °C    |  |  |  |

| ELECTRICAL OPERATING CHARACTERISTICS (SEE NOTE 1) |                                                         |                                                                                                                 |       |                       |       |       |  |

|---------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|-------|--|

| SYMBOL                                            | PARAMETER                                               | CONDITIONS                                                                                                      | MIN   | ТҮР                   | MAX   | UNITS |  |

| I <sub>CC1</sub>                                  | V <sub>CC</sub> 1 Supply Current                        | $V_{CC}$ 1 = 5.0V, VIDEO inputs at $V_{CC}$ 1 or GND level                                                      |       |                       | 10    | μA    |  |

| I <sub>CC2</sub> ,<br>I <sub>CC3</sub>            | V <sub>CC</sub> 2 & V <sub>CC</sub> 3 Supply<br>Current | $V_{CC}2 = V_{CC}3 = 5.0V$                                                                                      |       |                       | 10    | μA    |  |

| I <sub>CC4</sub>                                  | V <sub>CC</sub> 4 Supply Current                        | $V_{CC}4 = 5.0V$ ; SYNC inputs at GND or $V_{CC}4$<br>level; PWR-UP pin at $V_{CC}4$ ; SYNC outputs<br>unloaded |       | 10                    |       | μA    |  |

|                                                   |                                                         | $V_{CC}4 = 5.0V$ ; SYNC inputs at 3.0V; PWR-UP<br>pin at $V_{CC}4$ ; SYNC outputs unloaded                      |       | 200                   |       | μA    |  |

|                                                   |                                                         | V <sub>CC</sub> 4 = 5.0V; PWR-UP input at GND; SYNC outputs unloaded                                            |       |                       | 10    | μA    |  |

| V <sub>BIAS</sub>                                 | V <sub>BIAS</sub> Open Circuit Voltage                  | No external current drawn from $V_{BIAS}$ pin                                                                   |       | V <sub>CC</sub> 4-0.8 |       | V     |  |

| R <sub>T</sub>                                    | Video Termination<br>Resistance                         |                                                                                                                 | 71.25 | 75                    | 78.75 | Ω     |  |

|                                                   | R <sub>T</sub> Resistance Matching                      |                                                                                                                 |       | 1                     | 2     | %     |  |

|                                |                                                              | ELECTRICAL OPERATING CHARACTERISTICS (SEE NOTE 1) (CONT'D)                                                                                       |            |            |                          |          |  |  |

|--------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------------------|----------|--|--|

| SYMBOL                         | PARAMETER                                                    | CONDITIONS                                                                                                                                       | MIN        | TYP        | MAX                      | UNITS    |  |  |

| V <sub>IH</sub>                | Logic High Input Voltage                                     | V <sub>CC</sub> 4 = 5.0V; See Note 2                                                                                                             | 2.0        |            |                          | V        |  |  |

| V <sub>IL</sub>                | Logic Low Input Voltage                                      | V <sub>CC</sub> 4 = 5.0V; See Note 2                                                                                                             |            |            | 0.8                      | V        |  |  |

| V <sub>OH</sub>                | Logic High Output Voltage                                    | I <sub>OH</sub> = -4mA, V <sub>CC</sub> 4 = 5.0V; See Note 2                                                                                     |            | 4.94       |                          | V        |  |  |

| V <sub>OL</sub>                | Logic Low Output Voltage                                     | $I_{OL} = 4mA, V_{CC}4 = 5.0V;$ See Note 2                                                                                                       |            | 0.06       |                          | V        |  |  |

| R <sub>OH</sub>                | Output Resistance                                            | See Note 2                                                                                                                                       |            | 15         |                          | Ω        |  |  |

| R <sub>OL</sub>                |                                                              |                                                                                                                                                  |            | 15         |                          | Ω        |  |  |

| R <sub>B</sub> ,R <sub>P</sub> | Resistor Value                                               | $PWR\_UP = V_{CC}3 = 5.0V$                                                                                                                       | 0.5        | 1.0        | 2.0                      | MΩ       |  |  |

|                                | V <sub>CC</sub> 2 Pull-down Resistor<br>Value                | $V_{CC}2 = 3.0V$                                                                                                                                 | 0.5        | 1.5        | 3.0                      | MΩ       |  |  |

| I <sub>N</sub>                 | Input Current<br>VIDEO inputs<br>HSYNC, VSYNC inputs         | $V_{CC}$ 1= 5.0V; $V_{IN}$ = $V_{CC}$ 1 or GND<br>$V_{CC}$ 4 = 5.0V; $V_{IN}$ = $V_{CC}$ 4 or GND                                                |            |            | <u>+</u> 1<br><u>+</u> 1 | μΑ<br>μΑ |  |  |

|                                | Off-state Leakage Current,<br>Level-shifting NFET            | $      (V_{CC}2 - V_{DDC\_IN}) \leq 0.4V;  V_{DDC\_OUT} = V_{CC}2 \\       (V_{CC}2 - V_{DDC\_OUT}) \leq 0.4V;  V_{DDC\_IN} = V_{CC}2 $          |            |            | 10<br>10                 | μΑ<br>μΑ |  |  |

|                                | Voltage drop across level<br>shifting NFET when turned<br>ON | V <sub>CC</sub> 2= 2.5V; V <sub>S</sub> = GND; I <sub>DS</sub> = 3mA                                                                             |            |            | 0.15                     | V        |  |  |

| C <sub>IN</sub>                | Input Capacitance<br>VIDEO_1,VIDEO_2 &<br>VIDEO_3 inputs     | Note 4 applies for all cases;<br>$V_{CC}1 = 5.0V$ ; $V_{IN} = 2.5V$ ; measured at 1MHz<br>$V_{CC}1 = 2.5V$ ; $V_{IN} = 1.25V$ ; measured at 1MHz | 3.0<br>3.0 | 4.0<br>4.5 | 5.0<br>5.6               | pF<br>pF |  |  |

| FLII                           | SYNC Drivers L => H<br>Propagation Delay                     | $C_{L}$ = 50pF; $V_{CC}$ =5.0V,Input $t_{R}$ and $t_{F}$ $\leq$ 5ns                                                                              |            | 8.0        | 12.0                     | ns       |  |  |

|                                | SYNC Drivers H => L<br>Propagation Delay                     | $C_L$ = 50pF; $V_{CC}{=}5.0V;$ Input $t_R$ and $t_F{}{\leq}5ns$                                                                                  |            | 8.0        | 12.0                     | ns       |  |  |

|                                | SYNC Drivers Output Rise<br>& Fall Times                     | $C_L$ = 50pF; $V_{CC}{=}5.0V;$ Input $t_R$ and $t_F{\leq}5ns$ (measured 10% - 90%)                                                               | 5.0        | 7.0        | 10.0                     | ns       |  |  |

| V <sub>ESD</sub>               | ESD Withstand Voltage                                        | $V_{CC}1 = V_{CC}3 = V_{CC}4 = 5V$ ; Notes 3 & 4                                                                                                 | ±8         |            |                          | kV       |  |  |

Note 1: All parameters specified over standard operating conditions unless otherwise noted.

Note 2: This parameter applies only to the HSYNC and VSYNC channels. HSYNC and VSYNC have 24mA drivers with R<sub>S</sub> added in series to terminate transmission line.

Note 3: Per the IEC-61000-4-2 International ESD Standard, Level 4 contact discharge method. V<sub>CC</sub>1, V<sub>CC</sub>3 and V<sub>CC</sub>4 must be bypassed to GND via a low impedance ground plane with a 0.2uF, low inductance, chip ceramic capacitor at each supply pin. ESD pulse is applied between the applicable pins and GND. ESD pulse can be positive or negative with respect to GND. Applicable pins are: VIDEO\_1, VIDEO\_2, VIDEO\_3, SD1, SD2, DDC\_OUT1 and DDC\_OUT2. All other pins are ESD protected to the industry standard 2kV per the Human Body Model (MIL-STD-883, Method 3015).

Note 4: This parameter is guaranteed by design and characterization.

© 2004 California Micro Devices Corp. All rights reserved.

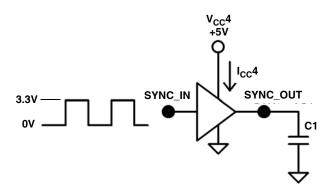

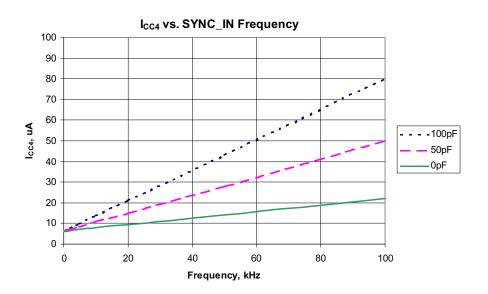

#### **Test Circuit Information**

Average Current through  $V_{CC}4$  (I<sub>CC</sub>4)

The circuit in Figure 1 was used to characterize  $I_{CC}4$  current as SYNC\_IN signal frequency varies. A square wave signal was connected to the input of one of the SYNC buffers (i.e. pin 19 or pin 21). The frequency of this signal was varied between 0 and 100 kHz. The risetime and falltime was kept constant at 10ns. Three different values of C1 were used: 0pF, 50pF and 100pF. The results are plotted in Figure 2.

Figure 1. Sync Buffer I<sub>CC</sub>4 Test Circuit

Figure 2. I<sub>CC</sub>4 vs. SYNC\_IN Frequency Performance Data

# **Application Information**

Figure 3. Typical Connection Diagram

A resistor may be necessary between the  $V_{CC}3$  pin and ground if protection against a stream of ESD pulses is required while the PACVGA203 is in the power-down state. The value of this resistor should be chosen such that the extra charge deposited into the  $V_{CC}3$  bypass capacitor by each ESD pulse will be discharged before the next ESD pulse occurs. The maximum ESD repetition rate specified by the IEC-61000-4-2 standard is one pulse per second. When the PACVGA203 is in the power-up state, an internal discharge resistor is connected to ground via an FET switch for this purpose.

For the same reason,  $V_{CC}1$  and  $V_{CC}4$  may also require bypass capacitor discharging resistors to ground if there are no other components in the system to provide a discharge path to ground.

GNDA, the reference voltage for the  $75\Omega$  resistors is not connected internally to GNDD and should ideally be connected to the ground of the video DAC IC.

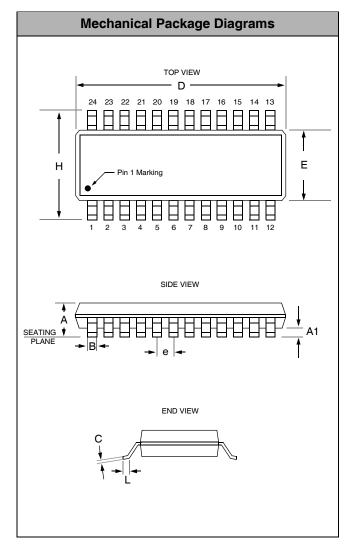

#### **Mechanical Details**

#### **QSOP Mechanical Specifications:**

PACVGA203 devices are packaged in 24-pin QSOP packages. Dimensions are presented below.

For complete information on the QSOP-24 package, see the California Micro Devices QSOP Package Information document.

| PACKAGE DIMENSIONS            |                           |      |           |       |  |

|-------------------------------|---------------------------|------|-----------|-------|--|

| Package                       | QSOP (JEDEC name is SSOP) |      |           |       |  |

| Pins                          |                           | 2    | 24        |       |  |

| Dimensions                    | Millimeters               |      | Inches    |       |  |

| Dimensions                    | Min                       | Max  | Min       | Max   |  |

| Α                             | 1.35                      | 1.75 | 0.053     | 0.069 |  |

| A1                            | 0.10                      | 0.25 | 0.004     | 0.010 |  |

| В                             | 0.20                      | 0.30 | 0.008     | 0.012 |  |

| С                             | 0.18                      | 0.25 | 0.007     | 0.010 |  |

| D                             | 8.56                      | 8.73 | 0.337     | 0.344 |  |

| E                             | 3.81                      | 3.98 | 0.150     | 0.157 |  |

| е                             | 0.64                      | BSC  | 0.025 BSC |       |  |

| Н                             | 5.79                      | 6.19 | 0.228     | 0.244 |  |

| L                             | 0.40                      | 1.27 | 0.016     | 0.050 |  |

| # per tube                    | 55 pcs*                   |      |           |       |  |

| # per tape<br>and reel        | 2500 pcs                  |      |           |       |  |

| Controlling dimension: inches |                           |      |           |       |  |

\* This is an approximate number which may vary.

Package Dimensions for QSOP-24