#### INTRODUCTION

S5T8808A is a superior low-power-programmable PLL frequency synthesizer which can be used in a high performance Wide Area Pager system.

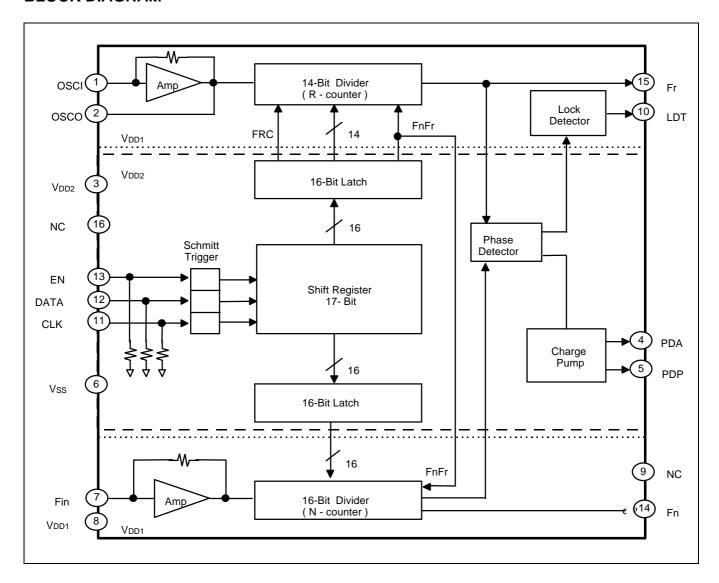

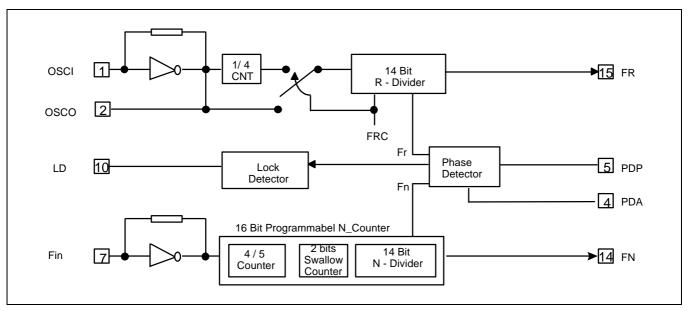

S5T8808A consists of 2 kinds of divider block including a 17bit Shift register, 16-bit Latch, 14/16-bits Counter, Prescaler, and a phase detector block including a Phase detector, Lock detector and a Charge pump.

#### **FEATURES**

- Maximum operating frequency:

120MHz @ 500mV<sub>P-P</sub>, V<sub>DD1</sub> = 0.95V, V<sub>DD2</sub> = 3.0V

165MHz @ 500mV<sub>P-P</sub>, V<sub>DD1</sub> = 1.0V, V<sub>DD2</sub> = 3.0V

- On-chip reference oscillator supports external crystal which oscillates up to 18MHz

- Superior supply current:

$$\begin{aligned} & F_{\text{FIN}} = 90 \text{MHz}, I_{\text{DD1}} = 0.6 \text{mA (Typ.)} \ @ \ V_{\text{DD1}} = 1.0 \text{V}, V_{\text{DD2}} = 3.0 \text{V} \\ & F_{\text{FIN}} = 150 \text{MHz}, I_{\text{DD1}} = 0.9 \text{mA (Typ.)} \ @ \ V_{\text{DD1}} = 1.0 \text{V}, V_{\text{DD2}} = 3.0 \text{V} \end{aligned}$$

- Operating voltage:  $V_{DD1} = 0.95 \sim 2.0 \text{V}$  and  $V_{DD2} = 2.0 \sim 3.3 \text{V}$

- Reference frequency counter divider range: 1 / 28 ~ 1 / 65532 (Multiple 4)

But, the Divider range with FRC\_High state: 1 / 7 ~ 1 / 16383

- RX frequency counter divider range: 1 / 28 ~ 1 / 65535

- Package type: 16–TSSOP (0.65mm)

#### ORDERING INFORMATION

| Device           | Package       | Operating Temperature |  |  |

|------------------|---------------|-----------------------|--|--|

| +S5T8808A01-R0B0 | 16-TSSOP-0044 | −25°C to +75°C        |  |  |

+: New Product

### **BLOCK DIAGRAM**

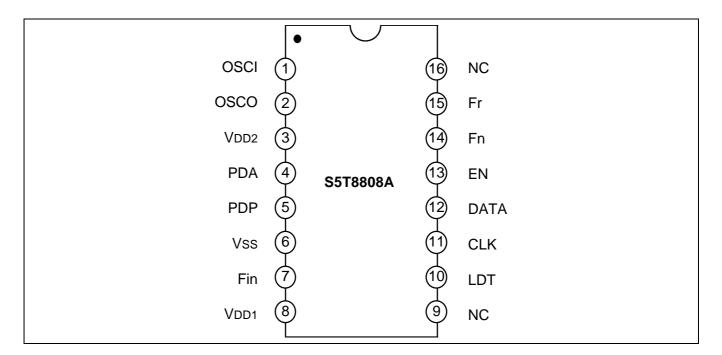

## **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin No | Symbol           | I/O | Description                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1      | OSCI             | I   | These input / output pins generate the reference frequency.                                                                                                                                                                                                                                                                                      |  |  |

| 2      | OSCO             | 0   | In case of OSCI Pin, external reference frequency can be used through the AC coupling.                                                                                                                                                                                                                                                           |  |  |

| 3      | V <sub>DD2</sub> | _   | The highest potential supply terminal that can be supplied up to 2.0 ~ 3.3V, except for $V_{DD1}$ .                                                                                                                                                                                                                                              |  |  |

| 4      | PDA              | 0   | The Output of RX Phase detector terminal for active loop filter There are 3-kinds of output signal states according to Rx Loop Error;  - If Fr > Fn (Fr is leading), the output is negative pulse state,  - If Fr < Fn (Fr is lagging), the output is positive pulse state,  - If Fr = Fn (the same phase), the output is high impedance state.  |  |  |

| 5      | PDP              | 0   | The Output of RX Phase detector terminal for passive loop filter There are 3-kinds of output signal states according to Rx Loop Error;  - If Fr > Fn (Fr is lagging), the output is negative pulse state,  - If Fr < Fn (Fr is leading), the output is positive pulse state,  - If Fr = Fn (the same phase), the output is high impedance state. |  |  |

| 6      | V <sub>SS</sub>  | -   | Ground terminal                                                                                                                                                                                                                                                                                                                                  |  |  |

| 7      | Fin              | ı   | Input terminal for 16 bit Divider from VCO.  Mostly, VCO output should be input through the AC coupling and the minimum input level is 500mV <sub>P-P</sub> (in case of 90MHz)                                                                                                                                                                   |  |  |

| 8      | V <sub>DD1</sub> | _   | Voltage supply terminal for Oscillator and Fin block. This pin can be supplied up to 0.95 ~ 2.0V from V <sub>SS</sub> .                                                                                                                                                                                                                          |  |  |

| 9      | NC               | _   | No Connection                                                                                                                                                                                                                                                                                                                                    |  |  |

| 10     | LDT              | 0   | Lock detector is also on output of the Phase Detector. The LOW state of this output shows unlock status, which is the error width between the Ref. signal and the VCO output signal.                                                                                                                                                             |  |  |

| 11     | CLK              | I   | These pins are controlled by the μ-controller and it also has Schmitt Trigger                                                                                                                                                                                                                                                                    |  |  |

| 12     | DATA             | I   | architecture. Internally biased pull-down.                                                                                                                                                                                                                                                                                                       |  |  |

| 13     | EN               | I   | The features of these pins are as follows: Clock input for 17-bit Shift Register, Serial data input (it include FnFr-on / off and FRC), and Latch enable input (User selectable EN1 or EN2).                                                                                                                                                     |  |  |

| 14     | Fn               | 0   | Output terminal for divider value of N-counter. To control the output On/Off, the FnFr bit of the Reference register can be programmed. When FnFr bit is set to High, this output shows low level.                                                                                                                                               |  |  |

| 15     | Fr               | 0   | Output terminal of divider value of N-counter. To control the output On/Off, the FnFr bit of the Reference register can be programmed. When FnFr bit is set to High, this output shows low level.                                                                                                                                                |  |  |

| 16     | NC               | _   | No Connection. Internally biased pull-up.                                                                                                                                                                                                                                                                                                        |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristic        | Symbol                             | Value                            | Unit |

|-----------------------|------------------------------------|----------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> ~ V <sub>DD2</sub> | −0.3 ~ <b>+</b> 4.0              | V    |

| Input Voltage         | VI                                 | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V    |

| Power Dissipation     | P <sub>D</sub>                     | 350                              | mW   |

| Operating Temperature | T <sub>OPR</sub>                   | −25 ~ <b>+</b> 75                | °C   |

| Storage Temperature   | T <sub>STG</sub>                   | −40 ~ <b>+</b> 125               | °C   |

## **ELECTRICAL CHARACTERISTICS**

(Ta = 25°C,  $V_{DD1}$  = 1.0V,  $V_{DD2}$  = 3.0V, unless otherwise specified)

| Characteristic                   | Symbol           | Test Conditions                                      |                           | Min.                  | Тур. | Max. | Unit |

|----------------------------------|------------------|------------------------------------------------------|---------------------------|-----------------------|------|------|------|

| Operating voltage                | V <sub>DD1</sub> |                                                      |                           | 0.95                  | 1.0  | 2.0  | V    |

|                                  | V <sub>DD2</sub> |                                                      |                           | 2.0                   | 3.0  | 3.3  |      |

| Operating current                | I <sub>DD1</sub> | F <sub>OSCI</sub> = 12.8MHz                          | F <sub>FIN</sub> = 90MHz  | _                     | 0.6  | _    | mA   |

|                                  | I <sub>DD2</sub> | $0.3V_{P-P}$<br>$V_{DD1} = 1.0V$<br>$V_{DD2} = 1.0V$ | F <sub>FIN</sub> = 150MHz | -                     | 0.9  | _    |      |

| Standby current                  | I <sub>SB</sub>  | $V_{DD1} = 0V, V_{DD2} = 0$                          | 3.0V                      | _                     | _    | 10   | μΑ   |

| Input Voltage                    | V <sub>IL</sub>  | -                                                    | -                         | _                     | _    | 0.3  | V    |

| (DATA, CLK, EN, BS)              | V <sub>IH</sub>  | -                                                    |                           | V <sub>DD3</sub> -0.3 | _    | _    |      |

| Input current                    | V <sub>IH</sub>  | $V_{IH} = V_{DD1}$                                   |                           | _                     | _    | 20   | μΑ   |

| (Fin, Xin)                       | V <sub>IL</sub>  | V <sub>IL</sub> = 0V                                 |                           | _                     | _    | 20   |      |

| Input frequency                  | F <sub>FIN</sub> | $F_{FIN} = 0.5V_{P-P}$                               | $V_{DD1} = 0.95V$         | _                     | -    | 120  | MHz  |

|                                  |                  |                                                      | V <sub>DD1</sub> = 1.0V   | _                     | -    | 165  |      |

|                                  | Fosci            | V <sub>OSCI</sub> = 0.5V <sub>P-P</sub>              |                           | 7                     | _    | 18   |      |

| Output current                   | I <sub>OH1</sub> | V <sub>OH</sub> = 0.4V                               |                           | 1.0                   | _    | _    | mA   |

| (PDA, PDP)                       | I <sub>OL1</sub> | $V_{OL} = V_{DD1} - 0.4V$                            |                           | 1.0                   | _    | _    |      |

| Output current                   | I <sub>OH2</sub> | V <sub>OH</sub> = 0.4V                               |                           | 0.1                   | _    | _    | mA   |

| (Fr, Fn, LDT)                    | I <sub>OL2</sub> | V <sub>OL</sub> = V <sub>DD1</sub> - 0.4V            |                           | 0.1                   | -    | _    |      |

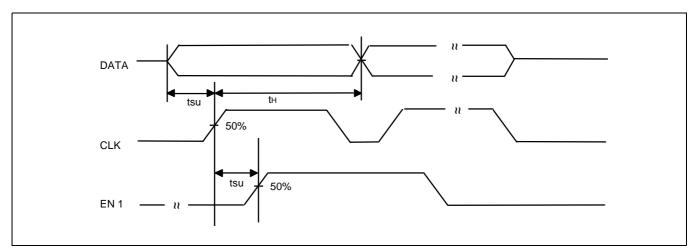

| Setup-time<br>(DATA-CLK, CLK-EN) | ts               | -                                                    |                           | 2                     | _    | _    | μS   |

| Hold time                        | t <sub>H</sub>   | -                                                    |                           | 2                     | _    | _    | μS   |

5

### **FUNCTIONAL DESCTRIPTION**

| Bit         | Bit 16 (ND 15) ~ Bit 1 (ND 0)          | Bit 0 (LSB)                           |  |

|-------------|----------------------------------------|---------------------------------------|--|

| Name        | RxD                                    | PMC                                   |  |

| Description | Rx. Program Data (ND 15 ~ ND 0)        | Program Mode Control                  |  |

| Function    | 16 Bit Programmable Rx. N-Counter Data | 0: Rx. N-Counter<br>1: Ref. R-Counter |  |

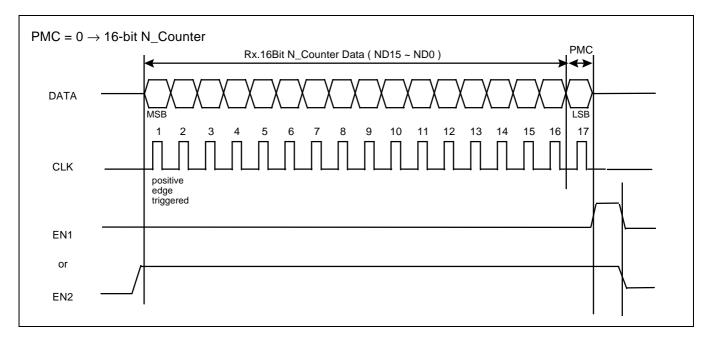

Figure 1. Rx. Register Programming Timing

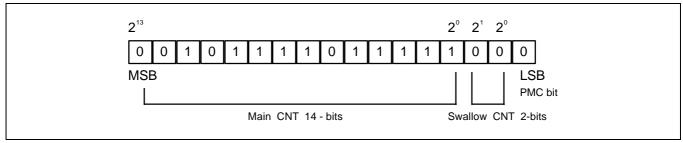

- Programmable N-counter consists of 2-bits Swallow Counter, 4/5 Dual modulars Prescaler and 14-bits Main Counter

- The Divide Ratio is;

$$N = (P + 1) \times S + P (M - S) = PM + S;$$

- P = Dual Modulars Prescaler (4)

- S = 2-bits Swallow Counter value  $(0 \sim 3)$

- M = 14-bits (7 ~ 16383)

- N = Programmable N-Counter value (N > S; 28 ~ 65535)

• Ex 1) In case of 14-bits program, Fc = 325.300MHz, Multiplier = 4, Fin = 75.975MHz [Fin Freq. / Ref. Frequ.] = 75.975MHz / 6.25kHz = 12156

- According to the above equation, 12156/4(P) = 3039 & left = 0 that means, Swallow CNT value is "0", Main CNT value is "3039".

- The PMC bit is Program Control Bit, if [0], the N-Counter will be Enabled.

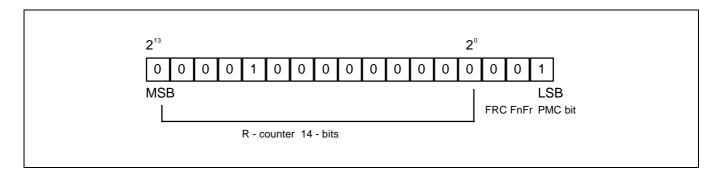

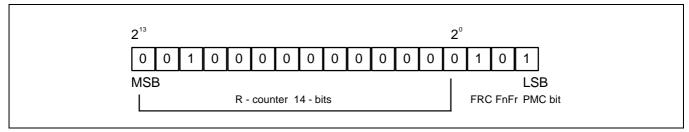

Table 2. R-Counter Register Program Scheme (17 bits)

| Bit         | Bit 16 (RD 13) ~ Bit 3 (RD 0)         | Bit 2                                  | Bit 1                               | Bit 0 (LSB)                           |

|-------------|---------------------------------------|----------------------------------------|-------------------------------------|---------------------------------------|

| Name        | RefD                                  | FRC                                    | FnFr                                | PMC                                   |

| Description | Ref. Program<br>Data (RD 13 ~ RD 0)   | Control Mode                           |                                     | Program mode control                  |

| Function    | 14 Bit Programmable<br>Ref. R-Counter | 0: No FRC (OSCI/4R)<br>1: FRC (OSCI/R) | 0: Fn, Fr function<br>1: Fn, Fr Low | 0: Rx. N-Counter<br>1: Ref. R-Counter |

**Table 3. Control Mode**

| FRC | FnFr | Fn (Pin 14)              | Fr (Pin 15)           |

|-----|------|--------------------------|-----------------------|

| 0   | 0    | Fn out (Fin / N counter) | Fr out (OSCI / 4 x R) |

| 0   | 1    | LOW                      | LOW                   |

| 1   | 0    | Fn out (Fin / N-counter) | Fr out (OSCI / R)     |

| 1   | 1    | LOW                      | LOW                   |

7

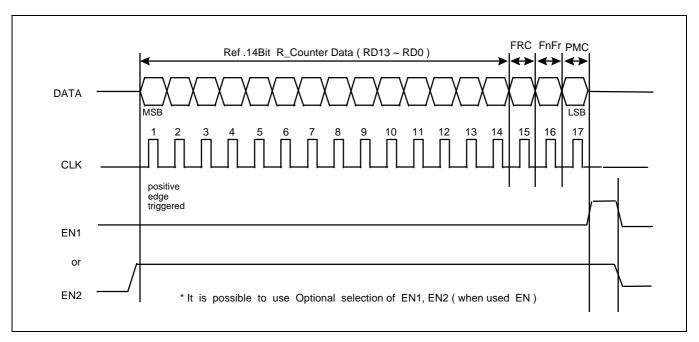

Figure 2. Ref. Register Programming Timing

NOTE: It is possible to use Optional selection of EN1, EN2 (when used EN)

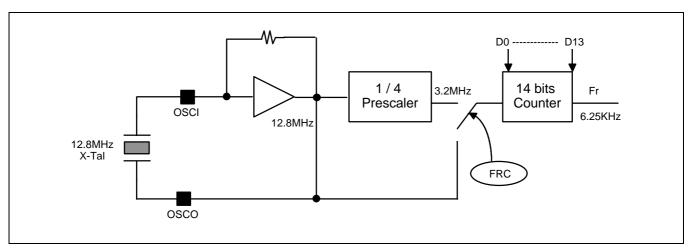

- The Input Reference Frequency (X-tal Oscillator) will divided by 1/4 Prescaler, and then divided by Preprogrammed R-counter value once more.

- Programmable R-Counter consists of Fixed 1/4 Prescaler, 14-bits Programmable Counter When FRC = 0, Fixed 1/4 Prescaler is used and 14-bits counter & can divide Multiple 4 RD = 4, R = 28 (=4 x 7) ~ 65532 -- (Min. Divide value:7)

When FRC = 1, Fixed 1/4 Prescaler isn't used, but using 14-bits counter & Can divide all value RD = R = 7 ~ 16384 [All value] --- (Min. Divide value:7)

• Ex 1) FRC = 0, In case of 14-bits Program, Fosc = 12.8MHz and fixed 1/4 prescaler is used [(Osc. Freg. / Prescaler) / Ref. Freg.] = [(12.8MHz / 4) / 6.25kHz] = 512

Ex 2) FRC = 1, In case of 14-bits Program, Fosc = 12.8MHz and fixed 1/4 prescaler is not used [Osc. Freq. / Ref. Freq.] = [12.8MHz / 6.25kHz] = 2048

<sup>\*</sup> The PMC bit is program Control Bit, if [1], the R-Counter will be Enabled

#### Serial DATA Input Timing & Phase Detector / Lock Detector Output Waveforms

Figure 3. Serial Data Input Timing

9

#### The architecture of R-Count Divider

Figure 4. R-CNT architecture

#### **VCO output Frequency**

$f_{VCO} = N \times f_{VCO} / RD$

f<sub>VCO</sub> = VCO output frequency

f<sub>OSC</sub> = X-tal Oscillator Frequency

RD = Programmable Reference R-counter value

N = Programmable N-counter value

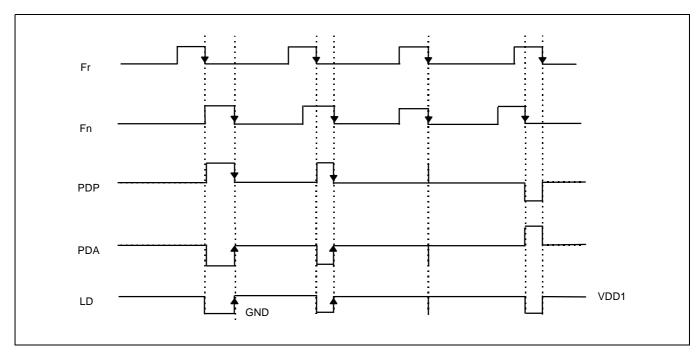

### Phase Detector / Lock Detector

Figure 5. Phase Detector / Lock Detector Block Diagram

Figure 6. Phase Detector / Lock Detector Output Waveforms

#### NOTES:

- 1. Phase detector always compares the Phase difference of N-counter with R-counter, and set to High or Low state as much as the phase difference.

- 2. The LD output set to Low level same as Phase detector error width.

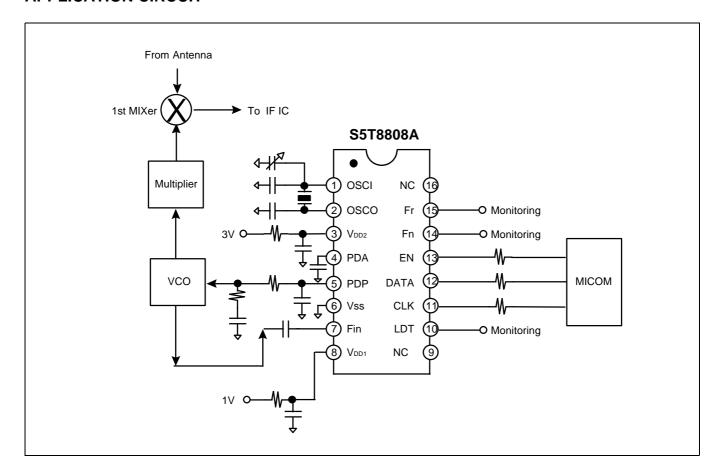

# **APPLICATION CIRCUIT**