# SH3100 Supervisory IC with I<sup>2</sup>C Interface and PWM

#### **POWER MANAGEMENT**

#### Description

The SH3100 is a size, power, and cost-saving solution for microprocessor support functions. It is intended to replace a number of peripheral devices normally used in conjunction with a microprocessor. Its prime function is to provide an accurate and stable clock source which can be started up and shut down very quickly to enable it to be used in a pulsed fashion for very low power applications.

The SH3100 consumes very little power when in standby, and it provides a stable output clock in less than 2µs. This allows it to outperform ceramic resonators and crystals requiring much longer start-up times.

#### **Features**

- Master HFDCO oscillator which can be programmed to between 8MHz and 33.5MHz with 2kHz resolution

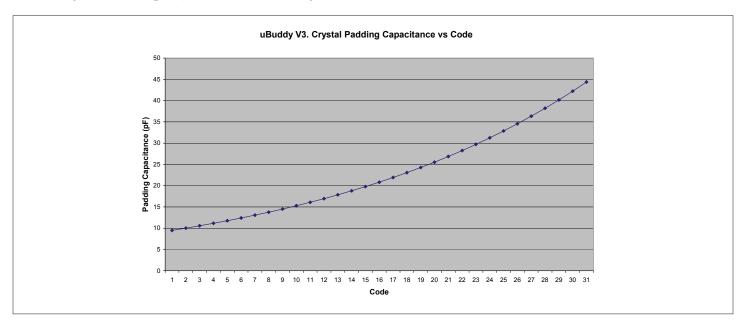

- A 32.768kHz crystal oscillator with 5-bit programmable padding capacitance giving a frequency adjustment resolution of 4ppm

- ◆ Two clock outputs, each of which can be powered inde pendently from VDD or VBAK and can operate either in-phase or in complementary mode

- An internal oscillator which is fuse-calibrated to provide a 32.768kHz clock source, accuracy is better than ±3% over temperature and supply voltage

- ◆ 96-bit electrically programmable non-volatile fuse memory array

- ◆ 7-bit programmable threshold reset comparator (VBO) between 1.7V and 4V with 24mV resolution

- Programmable reset duration between 6ms and 5.3 seconds

- ◆ Less than 10µA standby current and less than 12mA maximum operating current (excluding LDO load)

- ◆ I<sup>2</sup>C interface with 3-bit fuse-settable address complies with I<sup>2</sup>C fast mode specification

- General-purpose 8-bit DAC and Comparator

- ◆ General-purpose PWM & PDM output

- Programmable watchdog counter with a 7.8ms resolution up to 8 seconds delay

- Periodic interrupt timer (PIT) with a 30µs resolution up to 36 hours

- ◆ Real time clock with 1/256 second resolution up to Year 2099

- Spread spectrum option on the output clock

- ◆ Battery backup facility, which maintains register contents less than 2µA consumption

- ◆ 1.7V to 5.5V operating range on the main VDD supply

- ◆ 0.9V to 5.5V operating range on the battery backup supply (VBAK)

- ◆ Edge-triggered, level-sensitive, and toggling interrupt output (INT)

- ◆ General-purpose I/O option on the interrupt pin (INT)

- ◆ Low power, low dropout voltage regulator (LDO) output on PWM pin

- Switched mode boost, bootstrap boost, and buck regulation control

- ◆ 56 bytes of control registers including a 9-byte scratchpad

- ◆ Small 3mm x 3mm 16-lead MLP package

Covered by United States Patent 6,903,986 Semtech, the Semtech logo, MicroBuddy,  $\mu$ Buddy, and  $\mu$ B are marks of Semtech Corporation. All other marks belong to their respective owners.

# Table of Contents

| Description                                                    |        |

|----------------------------------------------------------------|--------|

| Features                                                       | 1      |

| Absolute Maximum Ratings                                       | 4      |

| Current Consumption                                            |        |

| Pin Configuration                                              | 6      |

| Ordering Information                                           | 6      |

| Pin Descriptions                                               | 6, 7   |

| Block Diagram                                                  | 8      |

| Power Supply and Battery Backup                                | 9      |

| VBAK Protection                                                | 10     |

| Operating Modes                                                | 11, 12 |

| Application Diagrams: Modes 1 to 3                             | 13     |

| Application Diagrams: Modes 4 to 6                             | 14     |

| Application Diagrams: Modes 7 to 9                             | 15     |

| Non-Volatile Fuse Memory Registers                             |        |

| SH3100 Default Settings                                        | 18     |

| Register Memory Map                                            | 19     |

| Register Organization                                          |        |

| Register Initialization from Fuses                             |        |

| Multi-Word Registers                                           |        |

| System Management                                              | 20     |

| Register Descriptions                                          |        |

| Applications Information                                       | 48     |

| Initial Power-Up                                               | 48     |

| Standard Operation, VDD settles at greater than programmed VBO | 48     |

| Standard Operation, VDD settles at less than programmed VBO    | 49     |

| Automatic Fan Speed Control Enabled                            | 49     |

| Switching Regulator Modes Enabled                              | 50     |

| Pad Specifications                                             | 51     |

| Standard Digital Input: CLKIN                                  | 51     |

| Tri-State / Analog Input: SNSE                                 | 51     |

| Dual Supply Digital Output: CLKO & CLK1                        | 52     |

| Asymmetric Drive Digital Output: NRST                          |        |

| Dual Drive Digital Bidirectional: INT                          |        |

| I <sup>2</sup> C Communication: SCL & SDA                      |        |

|                                                                |        |

| Multi-Function Output: PWM                                     | 54     |

# Table of Contents (continued)

| Functional Descriptions                                    | 55 |

|------------------------------------------------------------|----|

| 32.768 kHz Crystal Oscillator                              | 55 |

| Plot of Crystal Padding Capacitance versus Adjustment Code | 56 |

| Internal 32.768 kHz Oscillator                             | 56 |

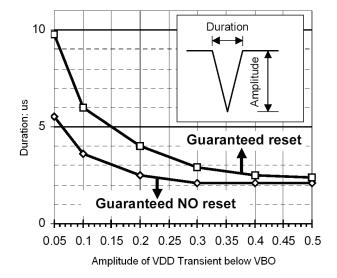

| System Reset - Programmable VDD Threshold (VBO)            | 57 |

| Programmable Reset Duration                                | 58 |

| System Reset - Watchdog Timer (WDT)                        | 59 |

| System Reset - Manual Override                             | 59 |

| Real Time Clock (RTC)                                      | 60 |

| Periodic Interval Timer (PIT)                              | 61 |

| Interrupt Operation                                        | 62 |

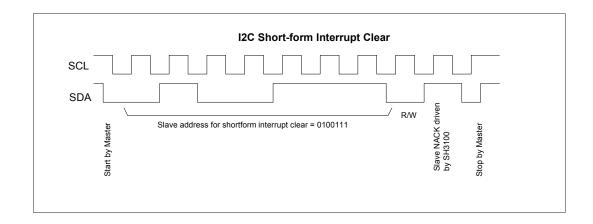

| I <sup>2</sup> C Short-Form Interrupt Clear                | 63 |

| General Purpose 8-Bit DAC & Comparator                     | 64 |

| Temperature Measurement                                    | 65 |

| PWM Operation & Fan Speed Control                          | 66 |

| Auto-PWM Mode (Fan Control Mode)                           | 66 |

| Auto-PWM Engine Features:                                  |    |

| Erratum                                                    | 67 |

| Manual PWM Control                                         | 67 |

| PWM Mode                                                   | 68 |

| Switching Regulator Operation                              | 69 |

| Low Dropout Linear Regulator (LDO)                         | 70 |

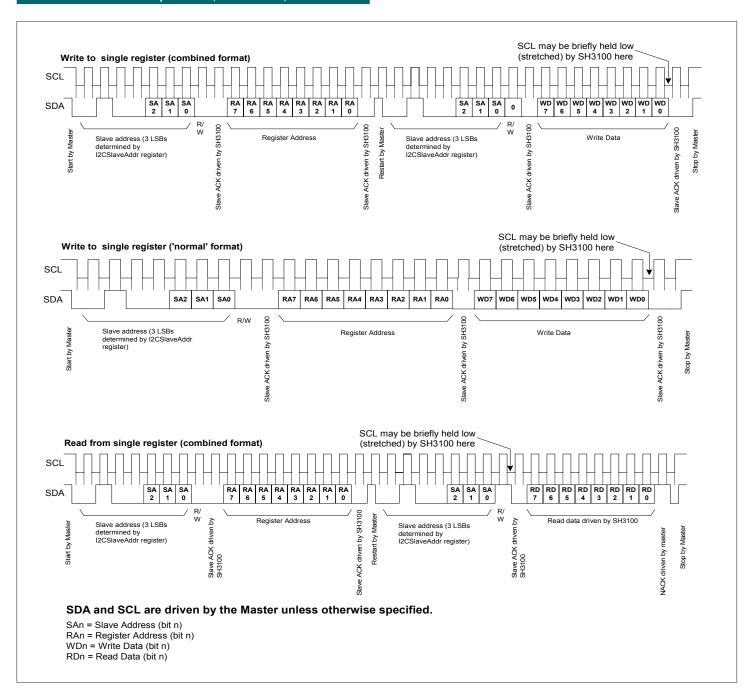

| I <sup>2</sup> C Interface                                 | 71 |

| Combined Write Format                                      | 71 |

| Normal Write Format                                        | 71 |

| Combined Read Format                                       | 72 |

| I <sup>2</sup> C Timing Diagrams                           | 73 |

| High-Frequency Digitally-Controlled Oscillator (HFDCO)     |    |

| Spectrum Spreading                                         | 75 |

| Clock Management & Frequency Locked Loop (FLL)             | 76 |

| CLKO & CLK1 Outputs                                        | 77 |

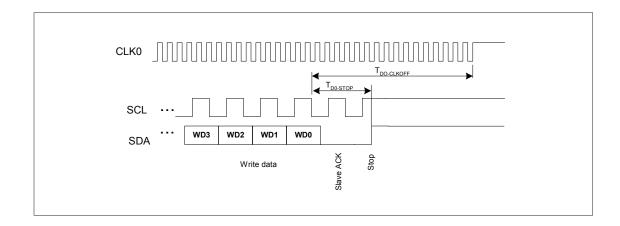

| HFDCO Clock On/Off Control                                 | 78 |

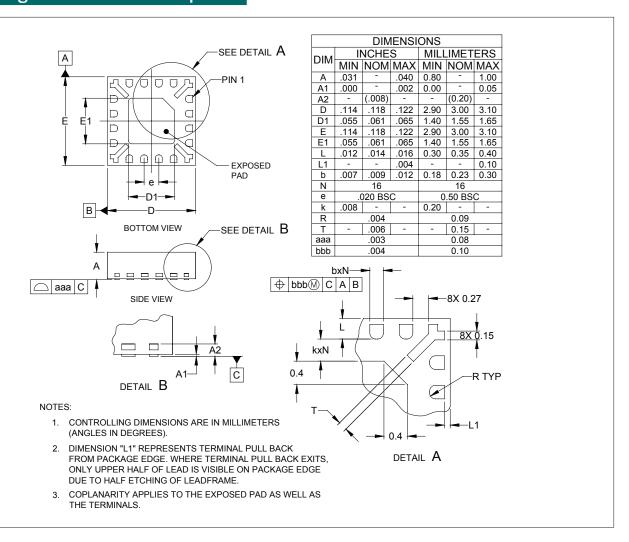

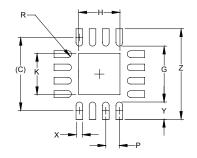

| Outline Drawing and Land Pattern                           | 79 |

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. Exposure to Absolute Maximum rated conditions for extended periods of time may affect device reliability.

| Pin Combination                                                            | Min  | Max        | Units |

|----------------------------------------------------------------------------|------|------------|-------|

| Supply voltages on VDD or VBAK relative to GND                             | 0.5  | 5.5        | V     |

| Supply voltage on VREG when blowing fuses (1 second maximum)               | 3.6  | 3.7        | V     |

| Input voltage on CLKIN & INT                                               | -0.5 | VDD        | V     |

| Input voltage on SDA & SCL                                                 | -0.5 | 5.5        | V     |

| Input voltage on SNSE, XIN, XOUT                                           | -0.5 | VREG + 0.5 | V     |

| Input current on any pin (not VREG)                                        |      | 10         | mA    |

| Input current on VREG                                                      |      | 150        | mA    |

| Ambient operating temperature for full specified performance               | -40  | 85         | °C    |

| Ambient operating temperature for chip operation with de-rated performance | -40  | 125        | °C    |

| Storage temperature                                                        | -50  | 160        | °C    |

#### Notes:

- (1) The SH3100 is an ESD-sensitive device.

- (2) Package ThetaJA is 100°C/Watt. This should be used to determine core temperature increase based on power dissipation.

#### **Current Consumption**

The following table shows the maximum current consumption figures from VDD and VBAK under a number of possible operating conditions.

#### **Battery Backup Modes**

| State            | Condition                                                            | MAX VBAK<br>Current |

|------------------|----------------------------------------------------------------------|---------------------|

| Battery backup 1 | Crystal oscillator and RTC running from VBAK; VDD is zero            | 2µA                 |

| Battery backup 2 | Internal 32.768kHz oscillator and RTC running from VBAK; VDD is zero | 12µA                |

#### **Normal Operating Modes**

| State                       | Condition                                                                                       | MAX VDD<br>Current |

|-----------------------------|-------------------------------------------------------------------------------------------------|--------------------|

| Standby                     | 32.768kHz system clock, programmable reset, RTC and logic enabled                               | 10μΑ               |

| Auto-fan mode               | Automatic fan mode with 32.768kHz output on CLK0; HFDCO disabled                                | 15µA               |

| Switching regulator standby | Switching regulator maintaining 10µA load with occasional active burst to maintain supply level | 20μΑ               |

| LDO standby                 | Standby but with LDO running on no load                                                         | 250µA              |

| Start-up                    | Current consumed during chip startup                                                            | 1mA                |

| Active                      | Up to 33.5MHz output clock enabled on both CLK0 and CLK1; 20pF load on each                     | 12mA               |

| Programming                 | Simultaneous blowing of up to eight fuses                                                       | 100mA              |

Note: At temperatures above 40 °C, the above figures start to increase due to leakage. Expect +2 $\mu$ A at 60 °C, and +6 $\mu$ A at 80 °C.

**Note:** VBAK current in normal operation mode is dependent on clock feedthrough from CLKO & CLK1 to VBAK. Under worst-case conditions with CLK output at 33MHz and VDD = 5.5 V, VBAK input current could be up to 2 $\mu$ A. At lower frequencies, VBAK current drops to approximately 50nA. This effect is related to the same phenomenon as described in the VBAK protection section, and the net feedthrough current on to VBAK may be positive or negative, dependent on VDD and VBAK voltage levels.

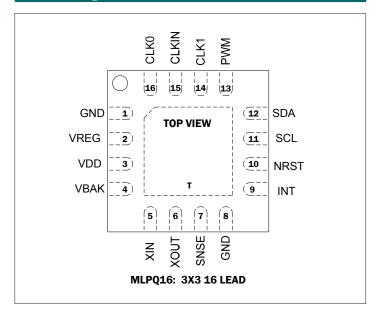

# Pin Configuration

# Ordering Information

| Device                      | Package <sup>(2)</sup>              |  |

|-----------------------------|-------------------------------------|--|

| SH3100IMTR <sup>(1)</sup>   | 46 Dia MI D 20000 V 20000 V 0 00000 |  |

| SH3100IMLTRT <sup>(2)</sup> | 16-Pin MLP 3mm x 3mm x 0.9mm        |  |

#### Notes

- 1) Available in tape and reel packaging only. A reel contains 3000 devices.

- Available in lead-free packaging only. This product is fully WEEE, RoHS and J-TD-020B compliant. This component and all homogenous subcomponents are RoHS compliant.

#### Pin Descriptions

| Pin# | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                     |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                           |

| 2    | VREG     | 1.6V regulated digital supply - generated internally from VDD - collapses to GND during battery backup - may be left unconnected                                                                                                                                                                                                                                                 |

| 3    | VDD      | Main supply (range is 1.7V to 5.5V)                                                                                                                                                                                                                                                                                                                                              |

| 4    | VBAK     | Backup battery supply to maintain register contents and RTC operation when VDD collapses - can be higher or lower than VDD - range is 0.9V to 5.5V - connect to VDD if not used                                                                                                                                                                                                  |

| 5    | XIN      | 32.768kHz crystal oscillator input pin - tie to ground if not used - can be over driven by external clock source up to 250kHz                                                                                                                                                                                                                                                    |

| 6    | XOUT     | 32.768kHz crystal oscillator output pin - leave unconnected if not used                                                                                                                                                                                                                                                                                                          |

| 7    | SNSE     | Sense input for fan speed control - spare analog input for switching regulator feedback or ADC conversion - tri state (low, floating, or high) input pin used to select reset duration                                                                                                                                                                                           |

| 8    | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                           |

| 9    | INT      | Level, edge or toggling interrupt output, general-purpose input/output (GPIO)                                                                                                                                                                                                                                                                                                    |

| 10   | NRST     | Active-low system reset output - strong pull-down - weak pull-up - reset state is valid for VDD levels down to 1V - can be externally over driven to trigger programmed duration reset                                                                                                                                                                                           |

| 11   | SCL      | I <sup>2</sup> C clock - 400kHz fast mode compliant - operates up to 1MHz                                                                                                                                                                                                                                                                                                        |

| 12   | SDA      | I <sup>2</sup> C data - 400kHz fast mode compliant - operates up to 1MHz                                                                                                                                                                                                                                                                                                         |

| 13   | PWM      | General-purpose PWM or PDM output - fan control PWM output - LDO output regulated down from VDD - programmable 3V to 4.5V in 18mV steps - 15mA drive capability - switching regulator control output - drives Inductor directly in bootstrap boost mode, or external switching FETs or bipolar transistors - directly drives inductor in bootstrap boost with internal switching |

# Pin Descriptions (continued)

| Pin# | Pin Name | Pin Function                                                                                                        |

|------|----------|---------------------------------------------------------------------------------------------------------------------|

| 14   | CLK1     | Secondary clock output - can be powered from either VDD or VBAK                                                     |

| 15   | CLKIN    | System clock input - used to detect processor-initiated clock STOP                                                  |

| 16   | CLK0     | Primary clock output - can be powered from either VDD or VBAK                                                       |

| Т    | PAD      | Thermal pad for heatsinking purposes - not connected internally - connect to system ground plane with multiple vias |

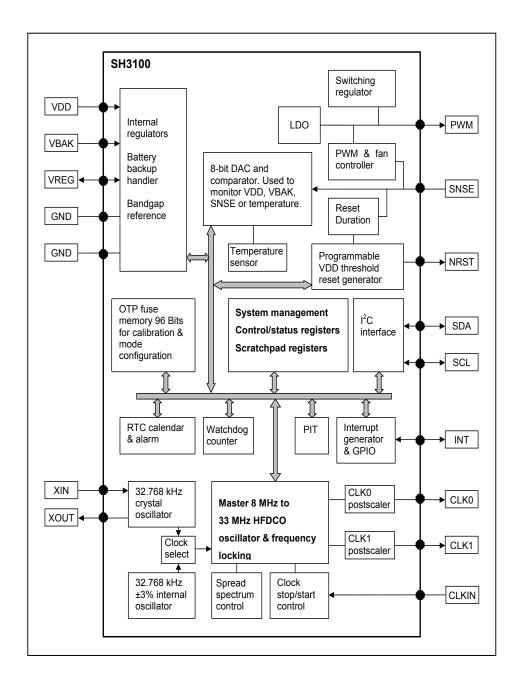

# **Block Diagram**

#### Power Supplies & Battery Backup

The main power supply is between VDD and GND and may have any value between 1.7V and 5.5V for normal operation. In order to guarantee start-up, VDD should initially be taken to at least 100mV above the reset threshold (VBO) in order to overcome the reset threshold hysteresis; e.g., for a VBO level of 2.8V, VDD must initially rise to at least 2.9V for the chip to come out of reset.

The battery backup supply is between VBAK and GND. The SH3100 switches to VBAK, if VDD drops below VBO and VBAK is within its valid operating range of 0.9V to 5.5V for battery backup.

While VBAK is within its valid operating range during battery backup, RTC operation is maintained and those register contents not reset by a VBO reset event (Brownout) are maintained. Any functions not required during battery backup are shut down to save power.

**Note:** If the 32.768kHz system clock output is enabled on CLK1 during battery backup then the maximum VBAK voltage for valid CLK1 output is 4.5V. Battery backup continues for VBAK voltages above 4.5V, but the CLK1 output is no longer guaranteed to function correctly.

When running in battery backup from the 32.768kHz crystal oscillator, full RTC accuracy is maintained down to the minimum VBAK of 0.9V.

When running in battery backup from the internal 32.768kHz oscillator, RTC accuracy is maintained only down to a VBAK level of 1.7V. Below this point, operation continues down to 0.9V, but a flag is set to indicate that the internal oscillator can no longer be guaranteed to be within  $\pm 3\%$  of 32.768kHz.

The minimum VBAK level is guaranteed as 0.9V; however, depending on process variations, operation may continue down to 0.7V before battery back up fails.

An unpowered (cold) chip starts up and initializes only when VDD is applied. Applying only VBAK to a cold chip does not cause it to start up.

Battery backup facility is only enabled once the chip has come out of reset after an initial power-up.

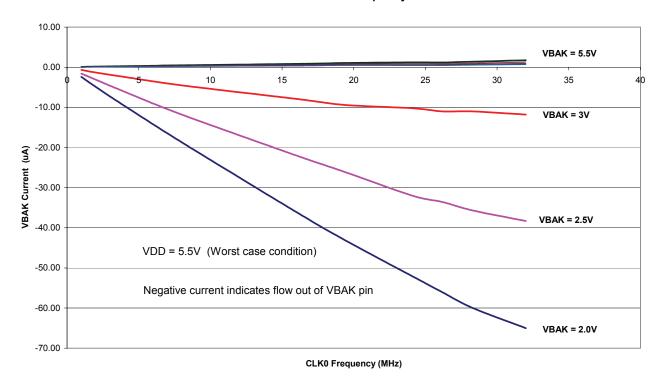

#### **VBAK Protection**

To avoid degradation of Lithium cells connected to VBAK, charging current over the operating lifetime needs to be limited to less than 3% of the cell capacity. It is therefore necessary to limit any current flowing from VDD to VBAK.

On the SH3100, VDD and VBAK have diode protection structures, so VDD and VBAK can independently have any DC voltage between 0 V and 5.5V, and no DC current flows between VDD and VBAK in either direction.

However, since CLKO and CLK1 may be powered either from VDD or VBAK, there is capacitance between CLKO or CLK1 and VBAK, so an AC signal on CLKO or CLK1 powered by VDD would couple some net current through to VBAK. This current coupling is proportional to frequency and to the voltage differential between VDD and VBAK.

The following graph shows the variation in reverse current from VDD to VBAK versus CLK frequency for different settings of VBAK. VDD is fixed at 5.5V, which is the worst-

case condition. Note that as VBAK approaches VDD, the net current changes direction so that it flows into VBAK.

**Note**: If the SH3100 is operated at clock frequencies and supply levels that mean that current flow out of VBAK into the battery would be a problem, then one solution would be to use a series diode between the battery and VBAK to inhibit any reverse current. This lowers the battery voltage by 0.7V on to VBAK; however, since VBAK can go as low as 0.9V, this is unlikely to be a problem for lithium cells.

As additional protection, if the battery is connected in reverse, then a large protection diode between VBAK and GND means that VBAK limits at approximately 0.7V below GND depending on the current flowing through the diode. A safe maximum current through this protection diode is 10mA. The SH3100 continues to function normally (apart from battery backup) while VBAK is negative.

# Operating Modes

The SH3100 is fuse programmed to a default power-up operating mode from a number of possible options. Once the device has been initialized, it is possible to use the I<sup>2</sup>C interface to change between any of the following available modes.

| Mode | LDO | Switching<br>Regulator | Fan<br>Control | Reset<br>Duration | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----|------------------------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | NO  | NO                     | NO             | YES               | Standard operating mode. PWM pin may be used as general-purpose PWM/PDM output. INT defaults to high impedance and may then be programmed by I <sup>2</sup> C access to define an Interrupt function or GPIO as required. Start-up frequency is determined by configuration fuse setting                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2    | YES | NO                     | NO             | NO                | LDO is enabled on PWM pin with default output voltage between 3V and 4.5V as set by fuses. Setting may then be overridden by I <sup>2</sup> C access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3    | NO  | NO                     | YES            | NO                | Automatic fan control is enabled with SNSE input used to detect fan rotation and PWM pin used for fan drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4    | NO  | YES                    | NO             | NO                | Bootstrap boost regulation from an external supply to VDD with internal switching FET and transfer diode on PWM pin. Regulator feedback is determined by the internal VDD divider. The PWM pin is active low during the inductor energize period and floating during the transfer period (to allow current to flow from PWM to VDD through the internal diode). During power up, the PWM pad is clamped to VDD to ensure that the chip can start up with an input battery supply as low as 1.8V. Conversion efficiency is very low due to the relatively high internal switching FET and diode impedances, so this mode is recommended only for powering the SH3100 alone and where energy efficiency is not important |

| 5    | NO  | YES                    | NO             | NO                | Bootstrap boost regulation from an external supply to VDD with external switching FET and transfer diode. Regulator feedback is determined by the internal VDD divider. This is suitable for heavier load requirements and is limited by the capabilities of the external components. The PWM pin drives an external NMOS or NPN switching the inductor to GND, and is High during the inductor energize period and Low during the transfer period (to allow current to flow through the external diode)                                                                                                                                                                                                               |

| 6    | NO  | YES                    | NO             | NO                | Normal boost regulation from VDD to a separate supply with external switching FET and transfer diode. Regulator feedback is input on the SNSE pin. The PWM pin drives an external NMOS or NPN switching the inductor to GND, and is High during the inductor energize period and Low during the transfer period                                                                                                                                                                                                                                                                                                                                                                                                        |

**Note:** The Reset Duration column refers to the option to select Low, Medium or fuse set reset durations by the tristate input SNSE pin. If this option is not available then the reset duration defaults to the fuse setting.

# Operating Modes (continued)

| Mode | LDO | Switching<br>Regulator | Fan<br>Control | Reset<br>Duration | Notes                                                                                                                                                                                                                                                                                                                                                        |  |

|------|-----|------------------------|----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7    | NO  | YES                    | NO             | NO                | Normal boost regulation from VDD to VBAK with external switching FET and transfer diode. Operation is as mode six but regulator feedback is determined by the internal VBAK divider                                                                                                                                                                          |  |

| 8    | NO  | YES                    | NO             | NO                | Buck regulation from VDD to a separate supply with external switching FET and transfer diode. Regulator feedback is input on the SNSE pin. The PWM pin drives an external PMOS or PNP switching the inductor to VDD and is Low during the inductor energize period and High during the transfer period (to allow current to flow through the external diode) |  |

| 9    | NO  | YES                    | NO             | NO                | Buck regulation from VDD to VBAK with external switching FET and transfer diode. Operation is as mode 8 but regulator feedback is determined by the internal VBAK divider                                                                                                                                                                                    |  |

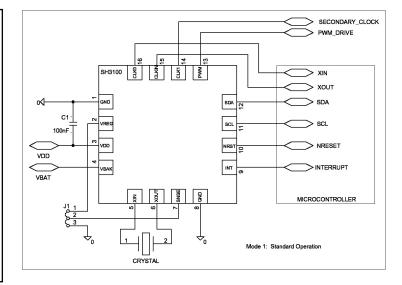

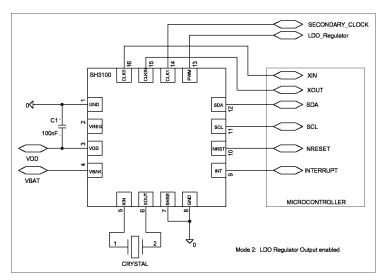

#### Application Diagrams - Modes 1 to 3

#### Mode 1 - Standard operation

No LDO, fan control or switching regulation.

General purpose PWM/PDM output is available

Use with or without external 32.768 kHz crystal

#### **Register settings**

DeviceMode = 000

#### Mode 2 - LDO enabled

As standard operation but with PWM output pin programmed as LDO output. (Linearly regulated down from VDD).

#### **Register settings**

- DeviceMode = 100

- ForcedDACValue = xx (to set LDO voltage)

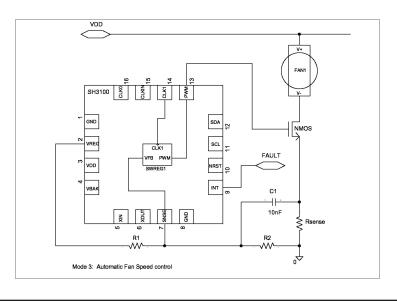

#### Mode 3 - Auto fan speed control

Fan speed is automatically controlled by measuring temperature at regular intervals and adjusting PWM duty cycle according to configurable control parameters.

SNSE pin is monitored to detect possible fan stall

#### Register settings

- DeviceMode = 101

- ComparatorSource = 11 (SNSE)

- CLK1HF/LF = 0

- ForcedDACValue = xx (to override 70 mV SNSE threshold if required)

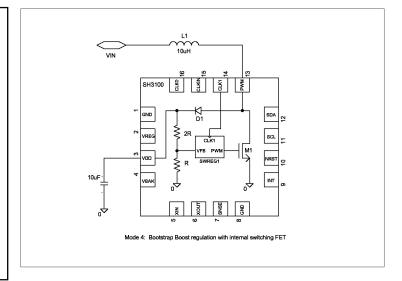

# Application Diagrams - Modes 4 to 6

# Mode 4 – Bootstrap boost regulation using internal switching FET

VDD is stepped up from external supply source using internal switching on PWM.

Starts up with external supply as low as 1.8 V and continue to operate as external supply drops as low as 1 V.

Regulation timing for all switching regulator modes is set by internal programmable HFDCO oscillator.

#### Register settings

- DeviceMode = 001

- ComparatorSource = 00 (VDD)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

# Mode 5 – Bootstrap boost regulation using external switching FET.

VDD is stepped up from external supply source using external switching FET controlled by PWM. Use for higher load requirements.

Regulated output voltage is set by internal DAC8. Feedback is fixed as VDD/3.

1Mohm pull-down resistor is required to indicate external switching configuration to SH3100.

#### Register settings

- DeviceMode = 001

- ComparatorSource = 00 (VDD)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

#

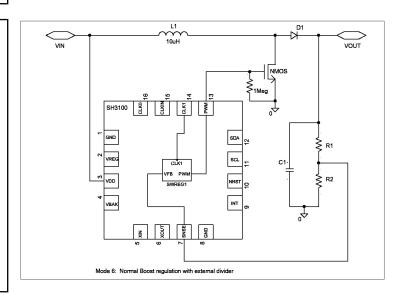

# Mode 6 – Normal boost regulation using external FET & external feedback divider

Regulated supply is stepped up from VDD using external switching FET controlled by PWM.

Regulated output voltage is set by internal DAC8 and feedback on SNSE.

1Mohm resistor indicates external switching and also ensures NMOS is turned off during power up

#### Register settings

- DeviceMode = 001

- ComparatorSource = 11 (SNSE)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

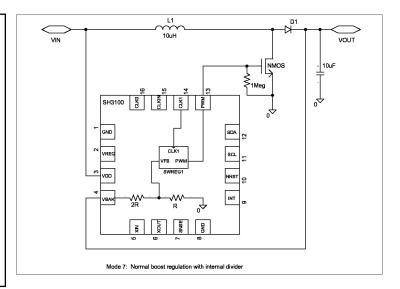

# Application Diagrams - Modes 7 to 9

# Mode 7 – Normal boost regulation using external FET & internal feedback divider

VBAK is stepped up from VDD using external switching FET controlled by PWM.

Regulated output voltage is set by internal DAC8. Feedback is fixed as VBAK/3.

1 MOhm resistor indicates external switching and also ensures NMOS is turned off during power up

#### **Register settings**

- DeviceMode = 001

- ComparatorSource = 01 (VBAK)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

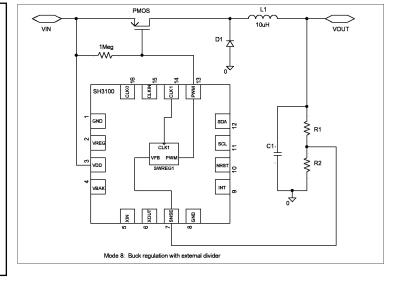

# Mode 8 – Buck regulation using external FET & external feedback divider

Regulated supply is stepped down from VDD using external switching FET controlled by PWM.

Regulated output voltage is set by internal DAC8 and feedback on SNSE.

1 MOhm resistor indicates external switching and also ensures PMOS is turned off during power up

#### **Register settings**

- DeviceMode = 011

- ComparatorSource = 11 (SNSE)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

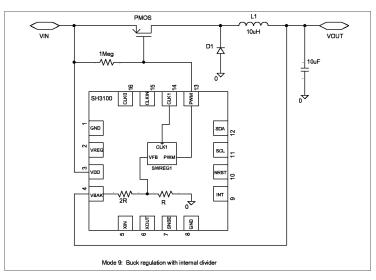

# Mode 9 – Buck regulation using external FET & internal feedback divider

Regulated supply is stepped down from VDD to VBAK using external switching controlled by PWM.

Regulated output voltage is set by internal DAC8. Feedback is fixed as VBAK/3.

1 MOhm resistor indicates external switching and also ensures PMOS is turned off during power up

#### **Register settings**

- DeviceMode = 011

- ComparatorSource = 01 (VBAK)

- CLK1HF/LF = 1

- ForcedDACValue = xx (to set VDD level)

- Set CLK1 frequency as desired

## Non-Volatile Fuse Memory Registers

The 96-bit non-volatile fuse memory contains the calibration and configuration control registers. The transfer column indicates under which conditions the fuse contents are transferred to the chip control registers. Fuses are blown on test and are extremely robust. There is no mechanism to reset fuses once blown. Calibration fuses are always set to obtain the required parametric specifications. Application fuses are set as required.

P Power on reset. (Power first applied) W Watchdog reset event

**B** Brownout (VDD drops below VBO threshold) **R** Forced fuse read initiated by I<sup>2</sup>C access

| Fuse Register                                                                                                              | Туре        | Bits | Range of Values                         | Transfer   |

|----------------------------------------------------------------------------------------------------------------------------|-------------|------|-----------------------------------------|------------|

| Bandgap reference                                                                                                          | Calibration | 4    | Bandgap set to 1.17V ±1%                | P, W, R    |

| Internal 32.768kHz ±2% oscillator                                                                                          | Calibration | 10   | Set to 32.768kHz ±128Hz at 25°C         | P, W, B, R |

| Temperature sensor trim                                                                                                    | Calibration | 4    | Temperature sensor set to ±2°C accuracy | P, W, B, R |

| VDD reset threshold (VBO)                                                                                                  | VBO Reset   | 7    | 1.7V to 4                               | P, W, R    |

| Chip reset duration                                                                                                        | Application | 5    | 6ms to 6 seconds                        | P, W, R    |

| Crystal load capacitance                                                                                                   | Application | 5    | 5pF to 22pF                             | P, R       |

| Master HFDCO clock FLL control<br>Frequency is code x 2.048kHz<br>Accuracy is defined by 32.768kHz source                  | Application | 14   | 8MHz to 33. MHz                         | P, W, B, R |

| Master HFDCO clock start-up frequency<br>Direct HFDCO control if FLL disabled<br>Frequency versus code varies with process | Application | 16   | Nominally 6MHz to 42MHz                 | P, W, B, R |

| CLK0 postscaler                                                                                                            | Application | 3    | 1 to 128                                | P, W, B, R |

| CLK1 postscaler                                                                                                            | Application | 4    | 1 to 32768                              | P, W, R    |

| Spread-spectrum amplitude                                                                                                  | Application | 2    | 32kHz to 128kHz                         | P, W, B, R |

| Spread-spectrum enable                                                                                                     | Application | 1    | On or Off                               | P, W, B, R |

| CLK1 output enable                                                                                                         | Application | 1    | On or Off                               | P, W, R    |

| CLK1 switch to VBAK supply                                                                                                 | Application | 1    | On or Off                               | P, W, R    |

| CLK1 output invert                                                                                                         | Application | 1    | On or Off                               | P, W, R    |

| CLK1 force to 32.768kHz source                                                                                             | Application | 1    | On or Off                               | P, W, R    |

| Chip mode select                                                                                                           | Application | 3    | Normal, boost, buck, LDO, fan control   | P, W, R    |

| I <sup>2</sup> C slave address                                                                                             | Application | 3    | 1 of 8 addresses                        | P, W, B, R |

| Regulator start-up voltage                                                                                                 | Application | 4    | 1.9V to 4.5V                            | P, W, R    |

# Non-Volatile Fuse Memory Registers

| Fuse Register                  | Type        | Bits | Range of Values              | Transfer |

|--------------------------------|-------------|------|------------------------------|----------|

| Comparator input Mux select    | Application | 2    | VDD, VBAK, temperature, SNSE | P, W, R  |

| Application fuse write-protect | Protection  | 1    | On or Off                    | P, W, R  |

| VBO threshold write-protect    | Protection  | 1    | On or Off                    | P, W, R  |

| Calibration fuse write-protect | Protection  | 1    | On or Off                    | P, W, R  |

| Unused                         | Spare       | 2    | N/A                          | N/A      |

# SH3100 Default Settings

During production test, the calibration fuses are set as required to trim out process variations. For this device, the start-up configuration fuses are set as follows:

| ADDR   | Register                       | Bits   | Description                                                                              | Value    | Fuse Setting        |

|--------|--------------------------------|--------|------------------------------------------------------------------------------------------|----------|---------------------|

| 0 x 17 | DAC Value                      | [7:0]  | Sets default value on the 8-bit DAC if the LDO or switching regulator modes are selected | 660mV    | 01101010            |

| 0 x 18 | Device mode                    | [5:3]  | Default start-up operating mode                                                          | Auto-fan | 101                 |

| 0 x 19 | Comparator source              | [1:0]  | Selects comparator source                                                                | SNSE     | 11                  |

| 0 x 20 | CLK0 postscaler                | [2:0]  | Set HFDCO to CLK0 divider ratio                                                          | 8        | 011                 |

|        | CLK1 supply                    | [7]    | Sets CLK1 supply to VDD or VBAK                                                          | VDD      | 0                   |

|        | CLK1 HF/LF                     | [6]    | Sets CLK1 to HF or LF                                                                    | LF       | 0                   |

| 0 x 21 | Invert CLK1                    | [5]    | Inverts CLK1 output                                                                      | Off      | 0                   |

|        | CLK1 enable                    | [4]    | CLK1 output enable                                                                       | Off      | 0                   |

|        | CLK1 postscaler                | [3:0]  | Set HFDCO to CLK1 divider ratio                                                          | 1        | 0000                |

| 0 00   | SS enable                      | [7]    | Enable HFDCO spectrum spreading                                                          | Off      | 0                   |

| 0 x 22 | SS configuration               | [6:5]  | Spectrum spreading bandwidth                                                             | 32kHz    | 00                  |

| 0 x 23 | FLL set frequency (MSB)        | [5:0]  | MSB of the FLL set frequency. Locked to 32.768kHz crystal                                | 8MHz     | 001111              |

| 0x24   | FLL set frequency (LSB)        | [7:0]  | LSB of the FLL set frequency; locked to 32.768kHz crystal                                | 8MHz     | 01000001            |

| 0x30   | Reset threshold                | [6:0]  | VBO reset threshold                                                                      | 2.93V    | 0110010             |

| 0x31   | Reset duration                 | [4:0]  | Reset duration                                                                           | 222ms    | 01101               |

| 0x42   | Xtal padding capacitance trim  | [4:0]  | Crystal load capacitance                                                                 | 11.5pF   | 00110               |

| 0x44   |                                |        | Master HFDCO start-up frequency. Use for                                                 |          | <b>.</b>            |

| 0x45   | HFDCO start-up frequency       | [18:0] | direct HFDCO control if FLL disabled.                                                    | 8 MHz    | Device<br>Dependent |

| 0x46   |                                |        | Frequency versus code varies with process                                                |          |                     |

| 0x47   | I <sup>2</sup> C Slave address | [2:0]  | LSB of I <sup>2</sup> C slave address. (MSB fixed at 0100)                               | 000      | 000                 |

|        | Application fuse protect       | [2]    | Application fuse write protect                                                           | Off      | 0                   |

| 0x49   | VBO reset fuse protect         | [1]    | VBO threshold fuse write protect                                                         | Off      | 0                   |

|        | Calibration fuse protect       | [0]    | Calibration fuse write protect                                                           | On       | 1                   |

#### Register Memory Map

Each register and register group is described in the following register memory map and subsequent register description tables.

#### **Register Organization**

The SH3100 uses a total of 53 8-bit registers, identified by a register name and corresponding hexadecimal register address. They are presented here in ascending order by register address. Some registers carry several individual data fields of various sizes; from single-bit values (e.g. flags), upwards. Several data fields are spread across multiple registers, as shown in the register map. Shaded areas in the map are 'don't care' and writing either 0 or 1 does not affect any function of the device. Cross-hatched areas denote registers which are initialized at startup from the on-chip fuse memory.

**CAUTION!** Do not write to any undefined register addresses, as this may cause the device to operate in a test mode. If an undefined register has been inadvertently addressed, the device should be reset to ensure the undefined registers are at default values.

#### **Register Initialization from Fuses**

Some register bits are initialized from the fuse memory on power-up and following selective reset events. All these bits can be overwritten by software once the reset signal NRST has been negated, unless the relevant write-protect fuse has been set. The fuses define only the default, power-on state of the device. The registers which are fuse-initialized are denoted in the register map with cross-hatching.

#### **Multi-Word Registers**

The RTC, *PeriodicTimer* (PIT), *WakeupTime* and *DCOCode* are multi-byte registers. The least significant byte (LSB) must be the last of the set to be written, after which their combined value takes effect. Conversely, the LSB must be the first byte of these registers to be read.

Because these registers share common resources within the  $I^2C$  interface, it is important that after writing the LSB of one of these registers, neither of the others is accessed for a period to give the internal registers time to update. After writing to the RTC, subsequent writes to the PIT should be delayed by at least 4ms; writes to DCOCode by a period equal to CLKO; and writes to WakeUpTime by 31µs.

#### **Crystal Trim Write Protect**

As an additional measure to protect the crystal loading capacitance from invalid adjustment, each time the value of the *XtalTrim* register is changed, a '0' must first be written to the XtalTrimWP register on the preceding access.

**Note:** If the *AppSpecificWP* bit is set to '1', then the *XtalTrim* fuses cannot be written, but unlike other registers the *XtalTrim* register CAN still be written - as detailed above.

# System Management

| Register Name                              | S                | ᆂ                |                     |                                         |                                     | D                                  | ata Bit                                |                                 |                                           |                           |  |

|--------------------------------------------|------------------|------------------|---------------------|-----------------------------------------|-------------------------------------|------------------------------------|----------------------------------------|---------------------------------|-------------------------------------------|---------------------------|--|

| RO = Read Only<br>R/W = Read/Write         | Address<br>(hex) | Default<br>(hex) | 7 (MSB)             | 6                                       | 5                                   | 4                                  | 3                                      | 2                               | 1                                         | 0 (LSB)                   |  |

| WakeupTime (R/W)                           | 00               | 00               |                     |                                         | •                                   |                                    | oTime[31:24]                           |                                 | <u>'</u>                                  |                           |  |

|                                            | 01               | 00               |                     |                                         |                                     | -                                  | oTime[23:16]                           |                                 |                                           |                           |  |

|                                            | 02               | 00               |                     |                                         |                                     |                                    | pTime[15:8]                            |                                 |                                           |                           |  |

|                                            | <u>03</u>        | 00               |                     |                                         |                                     |                                    | upTime[7:0]                            |                                 |                                           |                           |  |

| PeriodicTimer(RO)                          | 0 <u>6</u>       | 00               |                     |                                         |                                     |                                    | :Timer[31:24]                          |                                 |                                           |                           |  |

|                                            | 07<br>08         | 00               |                     |                                         |                                     |                                    | Timer [23:16]                          |                                 |                                           |                           |  |

|                                            | 09               | 00               |                     |                                         |                                     |                                    | cTimer [15:8]<br>icTimer [7:0]         |                                 |                                           |                           |  |

| RTC. (R/W)                                 | 0B               | 03               |                     | Year (uppe                              | er BCD digit )                      | i ciiodi                           | [1.0]                                  | Year (lowe                      | r BCD digit)                              |                           |  |

|                                            | OC               | 01               | Month<br>(upper BCD |                                         |                                     |                                    |                                        | Month (lower BCD digit)         |                                           |                           |  |

|                                            | OD               | 01               |                     |                                         | Day (upper                          | digit)                             |                                        | Day (lower                      | BCD digit)                                |                           |  |

|                                            | 0E               | 00               |                     |                                         | Hour (upper                         |                                    |                                        |                                 | r BDC digit)                              |                           |  |

|                                            | OF               | 00               |                     | Minu                                    | ites (upper BCD o                   |                                    |                                        |                                 | er BCD digit)                             |                           |  |

|                                            | 10               | 00               |                     | Seco                                    | nds (upper BCD o                    |                                    |                                        | Seconds (lov                    | ver BDC digit)                            |                           |  |

|                                            | 11               | 00               |                     |                                         |                                     |                                    | seconds                                |                                 |                                           |                           |  |

| InterruptEnable (R/W)                      | <u>14</u>        | 00               |                     |                                         | SNSE Fault                          | ADC Done                           |                                        | RTC Alarm                       | Comparator                                | PIT expired               |  |

| InterruptStatus (R/W)                      | 15               | 00               |                     |                                         | SNSE Fault                          | ADC Done                           |                                        | RTC Alarm                       | trigger<br>Comparator<br>trigger          | PIT expired               |  |

| ADCResult (RO)                             | <u>16</u>        | 80               |                     |                                         |                                     | ADC Cor                            | nversion result                        | 1                               |                                           |                           |  |

| ForcedDACValue (R/W)                       | 17               | 64               |                     |                                         |                                     |                                    | orced by software                      |                                 |                                           |                           |  |

| ADCConfig (R/W)                            | <u>18</u>        | 40               | Initiate ADC        | Comparator                              |                                     | Device mode                        | •                                      | DAC clock                       | post-scaler                               | DAC enable                |  |

| Config (R/W)                               | 19               | 00               | Conversion          | polarity<br>Maintain<br>LDO             | Comparator<br>interrupt<br>polarity |                                    | Force DCO On                           | Force<br>internal<br>32.768 kHz | Comparator                                | <br>source select         |  |

| CLKOConfig (R/W)                           | 20               | 30               | CLKO supply         | CLK0                                    | CLK1 = CLK0                         | CLK0                               |                                        | on                              | CLK0 Post-scale                           | r                         |  |

| CLK1Config (R/W)                           | 21               | 00               | CLK1 supply         | HF/LF<br>CLK1                           | Invert CLK1                         | Enable<br>CLK1                     |                                        | CLK1 Po                         | st-scaler                                 |                           |  |

| FLLConfig (R/W)                            | 22               | 00               | SS Enable           | HF/LF                                   | Config                              | Enable                             |                                        | Fine Lock                       | Coarse Lock                               | Enable FLL                |  |

| FLLDivideRatio (R/W)                       | 23               | OF               | J. J. S. Lilable    | X/////////////////////////////////////  | Comig                               |                                    | FLLDivide                              | Ratio[13:8]                     | Coarse Lock                               | Liable i LL               |  |

|                                            | 24               | 41               |                     |                                         |                                     | FLLDivi                            | ideRatio[7:0]                          |                                 |                                           |                           |  |

| ResetThreshold (R/W)                       | 30               | 00               |                     |                                         |                                     |                                    | ResetThresho                           | ld                              |                                           |                           |  |

| ResetDuration (R/W)                        | 31               | 00               |                     |                                         |                                     |                                    |                                        | ResetDuration                   |                                           |                           |  |

| Status (R/W)                               | 32               | 28               | Xtal osc<br>stable  | Comparator<br>o/p                       | RC osc<br>stable                    | Auto-<br>ClkDetect<br>mode         | RTC Invalid                            |                                 | SNSE<br>activity                          | FLL Locked                |  |

| CauseOfReset (R/W)                         | 33               | 09               |                     |                                         |                                     |                                    | VBO                                    | WDT Code<br>violation           | WDT<br>expired                            | PORB                      |  |

| WDTCode (R/W)                              | 34               | 00               |                     |                                         |                                     | Watchdo                            | g refresh code                         | 1                               |                                           | l                         |  |

| WDTConfig (R/W)  WDTPeriod (R/W)           | 35<br>36         | 00               |                     |                                         |                                     | 14                                 | /atchdog timeout                       | AutoWDT-<br>Suspend             | WDT p                                     | rescaler                  |  |

| INTConfig (R/W)                            | 37               | 00               |                     | Edge or                                 | I <sup>2</sup> C                    | Value at IN                        |                                        | GPIO                            | Enable INT                                | Interrupt or              |  |

|                                            |                  |                  |                     | Level                                   | ShortCode<br>Enable                 | pin                                | polariy                                | Direction                       | Toggling                                  | GPIO                      |  |

| MinStartTemp (R/W)                         | 38               | 7B               |                     | DDM                                     | Minimu                              |                                    | rature for fan cor                     |                                 | :- ft1                                    |                           |  |

| DutyCycleStepSize (R/W)                    | 39               | 11               |                     | PDM or<br>PWM                           |                                     |                                    | Duty cycle incren                      | ierit het degree                | in fan control M                          | oue                       |  |

| ManualPWMDutyCycle (R/W)                   | 3A               | 00               |                     |                                         |                                     |                                    |                                        |                                 | PWM Duty                                  | y Cycle[9:8]              |  |

|                                            | 3B               | 00               |                     |                                         |                                     |                                    | uty cycle[7:0]                         |                                 |                                           |                           |  |

| Int32kCoarseTrim (R/W) Int32kFineTrim(R/W) | 40               | 00               |                     |                                         |                                     | Internal 3                         | 2.768 kHz oscilla<br>In                | ternal 32.768 k                 | RATION ONLY Hz oscillator fine ATION ONLY | trim                      |  |

| XtalTrim (R/W)                             | 42               | 00               |                     |                                         |                                     |                                    | Xtal                                   | padding capacit                 |                                           |                           |  |

| BGCode (R/W)                               | 43               | 00               |                     |                                         |                                     |                                    |                                        | Bandgap trim -                  | CALIBRATION ON                            | ILY                       |  |

| DCOCode (R/W)                              | 44               | 00               |                     |                                         |                                     |                                    |                                        | L startup code                  |                                           |                           |  |

|                                            | 45               | 00               |                     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | D00 2                               |                                    |                                        | 2 startup code                  |                                           | 1-10-63                   |  |

| 12001ava Add= (B /M)                       | 46               | 00               |                     |                                         | DCO Bank3 sta                       | artup code[6:3                     | <u> </u>                               |                                 | Bank3 startup co                          |                           |  |

| I2CSlaveAddr (R/W) TempTrim (R/W)          | 47<br>48         | 00               |                     |                                         |                                     |                                    |                                        |                                 | Slave address [:<br>rim - CALIBRATION     |                           |  |

| WriteProtects (R/W)                        | 49               | 10               |                     |                                         |                                     | Xtal Trim<br>WP                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Cal Fuse WP                     | App-<br>Specific<br>Fuse WP               | Reset-<br>Threshold<br>WP |  |

| RTCAlarm/Scratchpad (R/W)                  | 80               | 00               | Y                   | ear (upper BC<br>SP[31:29]              | :D digit )/SP[39:3                  | Month<br>(upper BCI<br>digi)/SP[28 |                                        |                                 | D digit)/SP[35:32<br>CD digit)/SP[27:2    |                           |  |

|                                            | 82               | 00               | SP[23               |                                         | digit)/S                            | per BCD<br>P[21:20]                | -                                      |                                 | O digit)/SP[19:16                         |                           |  |

|                                            | 83               | 00               | SP[1                |                                         | digit)/S                            | pper BCD<br>P[13:12]               |                                        |                                 | OC digit)/SP[11:8                         |                           |  |

|                                            | 84               | 00               | SP[7]               | Minute                                  | s (upper BCD digi                   | t)/SP[6:4]                         |                                        | Minutes (lower                  | BCD digit)/SP[3:                          | UJ                        |  |

# Register Descriptions

## Address(hex): 00

| Register Name | WakeupTime                                     |       | Description | (RW) 8 Most signi<br>of the WakeupTin                                                                                                         |                                                                                         | Default Value:<br>Reset Event: P  |          |  |  |  |

|---------------|------------------------------------------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------|----------|--|--|--|

| Bit 7         | Bit 6                                          | Bit 5 | Bit 4       | Bit 3                                                                                                                                         | Bit 2                                                                                   | Bit 1                             | Bit 0    |  |  |  |

| Bit No.       | Description                                    |       | Bit Value   | Value Description                                                                                                                             |                                                                                         |                                   |          |  |  |  |

| [7:0]         | WakeupTime<br>Most significar<br>4-byte Wakeup | ,     | 00 (hex)    | The Periodic Interinterval of which interval of which in Period = Wakeup Setting Wakeup This register only (address 03) has even if some have | s set by the fou<br>Time/32768.<br>ime to 0 disable<br>takes effect on<br>been written. | es the PIT<br>ce the least signif | gisters. |  |  |  |

# Address(hex): 01

| Register Name | Register Name WakeupTime                         |  | Description | <b>Description</b> (RW) Bits [23:16] of the WakeupTime. |                             |       | Default Value: 0000 0000<br>Reset Event: P |  |  |

|---------------|--------------------------------------------------|--|-------------|---------------------------------------------------------|-----------------------------|-------|--------------------------------------------|--|--|

| Bit 7         | Bit 6 Bit 5                                      |  | Bit 4       | Bit 3                                                   | Bit 2                       | Bit 1 | Bit 0                                      |  |  |

| Bit No.       | Description                                      |  | '           | Bit Value                                               | Value Descri                | ption | I                                          |  |  |

| [7:0]         | WakeupTime Bits [23:16] of the 4-byte WakeupTime |  |             | 00 (hex)                                                | See register 00 description |       |                                            |  |  |

| Register Name | Register Name WakeupTime                        |  | Description | (RW) Bits [15:8<br>WakeupTime. | B] of the                   | Default Value: 0000 0000<br>Reset Event: P |       |  |

|---------------|-------------------------------------------------|--|-------------|--------------------------------|-----------------------------|--------------------------------------------|-------|--|

| Bit 7         | Bit 6 Bit 5                                     |  | Bit 4       | Bit 3                          | Bit 2                       | Bit 1                                      | Bit 0 |  |

| Bit No.       | Description                                     |  |             | Bit Value                      | Value Descri                | ption                                      |       |  |

| [7:0]         | WakeupTime Bits [15:8] of the 4-byte WakeupTime |  |             | 00 (hex)                       | See register 00 description |                                            |       |  |

# Register Descriptions (continued)

## Address(hex): 03

| Register Name | WakeupTime                                    |          | Description | (RW) Least Sig<br>WakeupTime.                                                        | (RW) Least Significant Byte of WakeupTime.                                                                                                           |                                                                                                 | 0000 0000                                                           |  |

|---------------|-----------------------------------------------|----------|-------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| Bit 7         | Bit 6                                         | Bit 5    | Bit 4       | Bit 3                                                                                | Bit O                                                                                                                                                |                                                                                                 |                                                                     |  |

| Bit No.       | Description                                   | 1        | Bit Value   | Value Description                                                                    |                                                                                                                                                      |                                                                                                 |                                                                     |  |

| [7:0]         | WakeupTime<br>Bits [7:0] of the<br>WakeupTime | e 4-byte | 00 (hex)    | Writing to this the PIT after u 61 µs later. It WakeupTime, this period. The written | ificant byte of Wai<br>register loads all<br>p to two periods of<br>is important that<br>RTC, PeriodicTime<br>ne PeriodicTimer i<br>WakeupTime, this | four bytes of Wai<br>of the 32.768 kH<br>no writes or reac<br>er nor DCOCode<br>s reset wheneve | z clock, i.e.<br>ds to either<br>occur during<br>r this register is |  |

#### Address(hex): 06

| Register Name | Register Name PeriodicTimer                       |            | Description                 | (RO) Most Significant Byte of<br>PeriodicTimer.                           |                                                                   | Default Value: 0000 0000<br>Reset Event: P, W, B                                                    |                                           |

|---------------|---------------------------------------------------|------------|-----------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|

| Bit 7         | Bit 6                                             | Bit 5      | Bit 4                       | Bit 3 Bit 2 Bit 1                                                         |                                                                   |                                                                                                     | Bit O                                     |

| Bit No.       | Description                                       | I          | Bit Value Value Description |                                                                           |                                                                   |                                                                                                     |                                           |