TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC93P24FG

Single-Chip DTS Microcontroller (DTS-20)

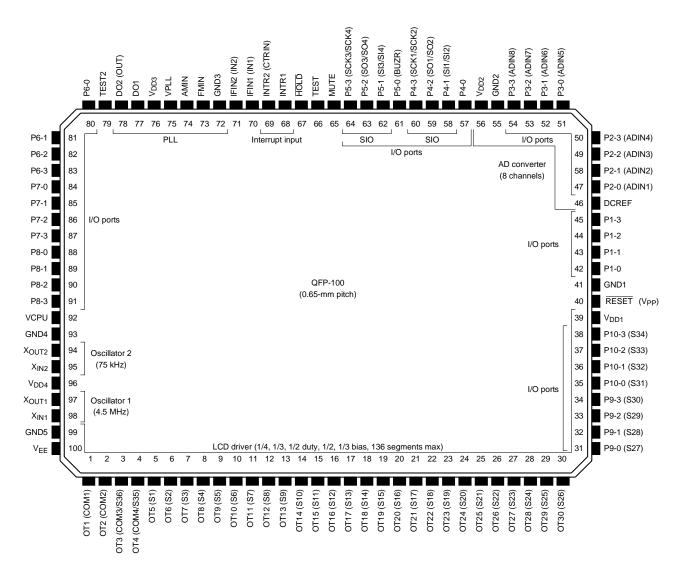

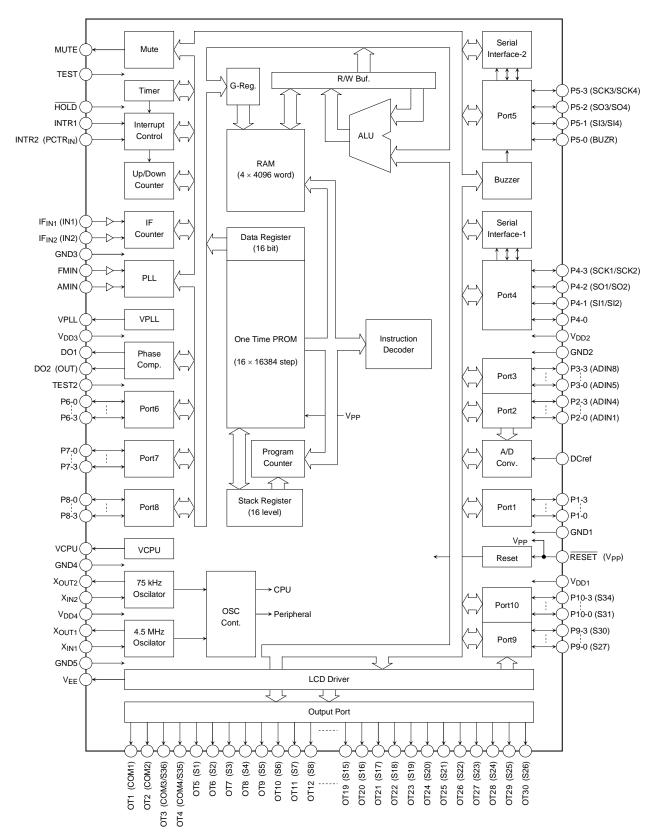

The TC93P24FG is a single-chip digital tuning system (DTS) microcontroller incorporating a 230 MHz prescaler, PLL, and LCD driver. In addition to a 20-bit IF counter, an 8-channel, 8-bit AD converter, two types of serial interface, and buzzer function, the TC9324FG offers a range of functions required for DTS, including an interrupt function, an 8-bit timer-counter, and an 8-bit pulse counter. In addition, the LCD driver features six modes combining 1/4, 1/3, and 1/2 duty and 1/2 and 1/3 bias. This product is suitable for use in a wide variety of DTS systems, from automobile to home audio, including compact stereo systems.

Weight: 1.6 g (typ.)

#### Features

- CMOS DTS microcontroller LSI with built-in 230 MHz prescaler, PLL, and LCD driver

- Operating voltage: PLL operating: VDD = 4.0 to 5.5 V (typ. 5.0 V) PLL off: VDD = 3.5 to 5.5 V (when CPU only operating)

- Crystal oscillator frequency: 4.5 MHz, 75 kHz

- Current dissipation: PLL operating: IDD = 3 mA (typ.) (crystal oscillator frequency 4.5 MHz, VHF mode) PLL off: IDD = 1 mA (typ.) (crystal oscillator frequency 4.5 MHz, CPU only operating) PLL off:IDD = 0.3 mA (typ.) (crystal oscillator frequency 75 kHz, CPU only operating)

- Operating temperature range: Ta = -40 to 85°C

- Program memory (ROM): 16 bits × 16,384 steps

- Data memory (RAM): 4 bits × 4,096 words

- Instruction execution time: 1.78 µs (crystal oscillator frequency 4.5 MHz)

- 40 µs (crystal oscillator frequency 75 kHz)

- Stack levels: 16

- General-purpose IF counter: 20-bit (CMOS input supported)

- AD converter: 8 bits × 8 channels

- LCD driver: 1/4, 1/3, 1/2 duty, 1/2, 1/3 bias modes selectable, 136 segments maximum

- I/O ports: CMOS I/O ports: 40

- Output-only ports: Up to 31. Input-only ports: Up to 5

- Timer-counter: 8-bit (as timer clock: INTR1, INTR2, instruction cycle, 25kHz, or 1 kHz selectable)

- Pulse counter: 8-bit up/down counter (input from INTR2 pin)

- Buzzer: 0.625 to 3 kHz (8 settings)

Four modes: Continuous, Single-Shot, 10-Hz Intermittent, 10-Hz Intermittent at 1-Hz Intervals

- Interrupts: 2 external, 4 internal (three types of serial interface, 8-bit timer)

- Package: QFP-100 (0.65-mm pitch)

#### **Block Diagram**

| Pin No. | Symbol                    | Pin Name                                  | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Remarks                                     |

|---------|---------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 1       | OT1/COM1                  | Output port                               | Output ports. Pins OT1 to OT20 can<br>be incremented by software, allowing<br>easy data access to external<br>RAM/ROM.                                                                                                                                                                                                                                                                                                                                                                          |                                             |

| 2       | OT2/COM2                  | /LCD common output                        | Can be set to LCD driver output by<br>software.<br>At 1/4 duty, controller can display up                                                                                                                                                                                                                                                                                                                                                                                                       | Y VDD                                       |

| 3       | OT3/COM3<br>/S36          | Output port<br>/LCD common output         | to 136 segments using a matrix<br>consisting of COM1 to 4 and SEG1 to<br>34.<br>At 1/3 duty, can display up to 105                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| 4       | OT4/COM4<br>/S35          | /LCD segment output                       | segments using a matrix consisting of<br>COM1 to 3 and SEG1 to 35.<br>At 1/2 duty, can display up to 72<br>segments using a matrix consisting of                                                                                                                                                                                                                                                                                                                                                | r <del>1</del>                              |

| 5~30    | OT5/S1<br>,<br>OT30/S26   | Output port<br>/LCD segment output        | COM1 to 2 and SEG1 to 36.<br>Set to output ports after a system<br>reset or clock stop.                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |

| 31~34   | P9-0/S27<br>,<br>P9-3/S30 | I/O port 9<br>/LCD segment output         | 4-bit CMOS I/O ports.<br>Input and output can be programmed<br>in 1-bit units.<br>These can be set bit by bit to LCD<br>driver output by software.                                                                                                                                                                                                                                                                                                                                              |                                             |

| 35~38   | P10-0/S31<br>P10-3/S34    | I/O port 10<br>/LCD segment output        | After a system reset, set to I/O port<br>input.<br>When a clock stop is executed, the<br>pins used as the LCD driver must be<br>set to output Low level (function as an<br>I/O port).                                                                                                                                                                                                                                                                                                           |                                             |

| 40      | RESET /VPP                | Reset input<br>/Program voltage<br>supply | Device's system reset signal input pin.<br>Setting $\overline{RESET}$ to Low level triggers<br>a reset. When the pin is set to High,<br>the program starts from address 0.<br>Since system reset will start if a<br>voltage beyond 0 V to 3.5 V is<br>supplied to V <sub>DD</sub> pin, this pin is used<br>by fixed at High level.<br>This pin is used as program voltage<br>supply for One Time PROM. In case<br>of writing program into the internal<br>PROM, 12.5 V is supplied to this pin. |                                             |

| 42~45   | P1-0<br>~<br>P1-3         | I/O port 1                                | 4-bit CMOS I/O port.<br>Input and output can be programmed<br>in 1-bit unit.                                                                                                                                                                                                                                                                                                                                                                                                                    | VDD<br>VDD<br>Input<br>Input<br>instruction |

| Pin No. | Symbol                                | Pin Name                                                | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                   | Remarks                                  |

|---------|---------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 46      | DCREF                                 | AD converter<br>reference voltage<br>input              | AD converter reference voltage input pin. Normally apply V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                               | $\bigcirc$ To AD converter               |

| 47~50   | P2-0<br>/ADIN1<br>2<br>P2-3<br>/ADIN4 | I/O port 2<br>/A/D analog voltage<br>input              | 4-bit CMOS I/O ports.<br>Input and output can be programmed<br>in 1-bit units.<br>Pins P2-0 to P3-3 are also used for<br>the built-in 8-bit, 8-channel AD<br>converter analog input.<br>The built-in AD converter uses a<br>successive comparison system.<br>When using a 4.5 MHz oscillator, the<br>conversion clock can be selected from                                                                                               | VDD                                      |

| 51~54   | P3-0<br>/ADIN5<br>2<br>P3-3<br>/ADIN8 | I/O port 3<br>/A/D analog voltage<br>input              | among 900 kHz, 100 kHz, and 50 kHz. When using a 75 kHz oscillator, the conversion clock is set to 75 kHz. The conversion times are respectively 23, 192, 382, and 294 $\mu$ s. The necessary pins can be programmed to A/D analog input in 1-bit units. Voltage up to the V <sub>DD</sub> can be input as the AD converter analog input voltage. Settings for the AD converter and its associated control can be performed by software. | Input<br>instruction                     |

|         |                                       |                                                         | 4-bit CMOS I/O ports.<br>Input and output can be programmed<br>in 1-bit units.<br>Pins P4-1 to P4-3 also input/output<br>the two serial interface circuits (SIO1,<br>SIO2).<br>On the clock edge of the SCK1 pin,                                                                                                                                                                                                                        |                                          |

| 57      | P4-0                                  | I/O port 4                                              | SIO1 can input 4-bit or 8-bit serial data to pin SI1 or input/output data to                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 58      | P4-1<br>/SI1<br>/SI2                  | Serial data input 1<br>/Serial data input 2             | pin SO1. For the serial operation clock<br>(SCK1), an internal (SCK = 37.5 kHz)<br>or external clock can be selected. This<br>design facilitates LSI control and<br>communication between controllers.                                                                                                                                                                                                                                   | Input instruction<br>(P4-0)              |

| 59      | P4-2<br>/SO1<br>/SO2                  | Serial data<br>input/output 1<br>/Serial data input 2   | Enabling the SIO1 interrupt jumps the<br>program to address 4 when SIO1<br>execution is complete.<br>On the falling edge of the SCK2 pin,<br>SIO2 can input 26-bit serial data to                                                                                                                                                                                                                                                        | V <sub>DD</sub>                          |

| 60      | P4-3<br>/SCK1<br>/SCK2                | Serial clock<br>input/output 1<br>/Serial clock input 2 | the SI2 pin.<br>SIO2 incorporates a data detector.<br>Enabling the SIO2 interrupt triggers<br>the interrupt on the falling edge of the<br>SCK2 pin and jumps the program to<br>address 6.<br>The SIO1 and SIO2 inputs all<br>incorporate Schmitt circuits.<br>SIO1 and SIO2 and their associated<br>controls can be operated and set by<br>software.                                                                                     | Input instruction + SIOon<br>(P4-1~P4-3) |

| Pin No.              | Symbol                                                                      | Pin Name                                                                                                                                                                                       | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Remarks                                                                                                              |

|----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 61<br>62<br>63<br>64 | P5-0/BUZR<br>P5-1<br>/SI3<br>P5-2<br>/SO3<br>/SO4<br>P5-3<br>/SCK3<br>/SCK4 | I/O port 5<br>/buzzer output<br>/Serial data input 3<br>/Serial data<br>input/output 3<br>/Serial data<br>input/output 4<br>/Serial clock<br>input/output 3<br>/Serial clock<br>input/output 4 | 4-bit CMOS I/O ports.<br>Input and output can be programmed<br>in 1-bit unit.<br>Pin 5-0 is also used to output a buzzer<br>signal. Pins P5-1 to P5-3 are also<br>used to input/output the two serial<br>interface circuits (SIO3, SIO4).<br>The buzzer output can be selected<br>from eight frequency settings (0.625<br>to 3 kHz), which can be output in four<br>modes: Continuous, Single-Shot, 10<br>Hz-Intermittent, and 10-Hz Intermittent<br>at 1-Hz Intervals.<br>SIO3 is a serial interface supporting<br>three lines, while the SIO4 serial<br>interface supports two lines.<br>On the clock edge of the SCK3/SCK4<br>pin, SIO3/SIO4 can input 4- or 8-bit<br>serial data to pin SI3 or output data to<br>the SO3/SO4 pin. For the serial<br>operating clock (SCK3/SCK4), an<br>internal (450/225/150/75 kHz) clock or<br>external clock can be selected.<br>The clock data output is N-channel<br>open drain. This design facilitates LSI<br>control and communication between<br>controllers.<br>Enabling the SIO3 or SIO4 interrupts<br>triggers the interrupt and jumps the<br>program to address 3 when interface<br>SIO3 or SIO4 completes execution.<br>This is effective for high-speed serial<br>communications.<br>The SIO3 and SIO4 inputs all<br>incorporate Schmitt circuits.<br>SIO3, SIO4, and their associated<br>controls can be used and set by<br>software. | $V_{DD}$ Input instruction<br>(P5-0)<br>$V_{DD}$ $V_{DD}$ $V_{DD}$ $V_{DD}$ Input instruction + SIOon<br>(P5-1~P5-3) |

| 65                   | MUTE                                                                        | Muting output port                                                                                                                                                                             | 1-bit output port.<br>Normally used as a muting control<br>signal output. This pin can set the<br>internal MUTE bit to 1 according to<br>changes in the I/O port 8 input and<br>HOLD input. The MUTE bit output<br>logic can be changed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| 66                   | TEST                                                                        | Test mode control<br>input                                                                                                                                                                     | Input pin for controlling Test mode.<br>When the pins are at High level, the<br>device is in Test mode; at Low level,<br>in normal operation.<br>Normally, set the pins to Low level or<br>NC (pull-down resistors are<br>incorporated).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| Pin No.  | Symbol                    | Pin Name                                          | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Remarks |

|----------|---------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 67       | HOLD                      | Hold mode control<br>input                        | Input pin for requesting and releasing<br>Hold mode.<br>Normally used to input radio mode<br>selection or battery detection signals.<br>Hold mode includes Clock Stop mode<br>(crystal oscillator stopped) and Wait<br>mode (CPU stopped), which can be<br>set by the CKSTP and WAIT<br>instructions respectively.<br>Clock Stop mode can be entered by<br>software in one of two ways: on<br>command or when Low level is<br>detected on the HOLD pin. Clock<br>Stop mode can be released when<br>High level is detected on the HOLD<br>pin or when the input changes.<br>Executing the CKSTP instruction<br>stops the clock generator and CPU,<br>entering memory backup mode. In this<br>state the device is set to low current<br>dissipation (10 $\mu$ A max).<br>Wait mode is executed, regardless of<br>the HOLD pin input state, and the<br>device is set to low current<br>dissipation. To set wait mode, specify<br>by software either crystal oscillator<br>only operating or CPU suspended.<br>Wait mode is released when the<br>HOLD pin input changes. |         |

| 68<br>69 | INTR1<br>INTR2<br>/PCTRin | External interrupt<br>input<br>/pulse count input | External interrupt input pins.<br>Enabling the interrupt function and<br>inputting a pulse (of at least 1.11 to<br>$3.33 \ \mu s$ when the 4.5 MHz clock is in<br>use, or at least 13.3 to 40 $\ \mu s$ when the<br>75 kHz clock used) to these input pins<br>generates an interrupt (INTR1/2) and<br>jumps the program to address 1/2.<br>The input logic and the clock edge<br>(rising/falling) can be individually<br>selected for each interrupt input.<br>The internal 8-bit timer clock can be<br>selected as input to the pins. At the<br>pulse count or when the count<br>reaches a specified value, an interrupt<br>can be generated (to address 5).<br>These pins are also used to input an<br>8-bit pulse counter. This counter can<br>be selected from either rising and<br>falling edge input, or an up-counter<br>and a down-counter.<br>These pins are Schmitt inputs and can<br>also be used as input ports. The pins<br>can also be utilized as ports for<br>inputting remote control signals or<br>tape counts.                                    |         |

| Pin No.  | Symbol                                           | Pin Name                             | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Remarks          |

|----------|--------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 70<br>71 | IF <sub>IN1</sub> /IN1<br>IF <sub>IN2</sub> /IN2 | IF signal inputs<br>/input port      | IF signal input pins for the IF counter<br>to count the IF signals of the FM and<br>AM bands and detect the automatic<br>stop position.<br>The input frequency is in the range<br>0.3 to 20 MHz. A built-in input amp<br>and capacitive coupling support<br>low-amplitude operation.<br>The IF counter is a 20-bit counter with<br>selectable gate times of 1, 4, 16, and<br>64 ms. 20 bits of data can be easily<br>stored in memory. In Manual mode,<br>the gates can be switched on and off<br>by instruction.<br>These input pins can also be<br>programmed as an input port (IN<br>port). In this case, they become<br>CMOS inputs and the clocks of those<br>inputs can be counted using the IF<br>counter.<br>Note: Pins set as IF input go Low in<br>PLL Off mode. | RFIN<br>VDD      |

| 73       | FMIN                                             | FM local oscillation<br>signal input | Programmable counter input pins for<br>the FM/AM band.<br>Their input mode can be switched by<br>software from either $1/2 + pulse$<br>swallow (VHF/FM) mode for FM input,<br>or pulse swallow (HF) or direct<br>division (LF) mode for AM input.<br>The local oscillation output<br>(voltage-controlled oscillator or V <sub>CO</sub><br>output) is normally input at the<br>following frequencies: 50 to 230 MHz<br>in VHF mode, 50 to 140 MHz in FM1                                                                                                                                                                                                                                                                                                                    | RFIN<br>VDD<br>T |

| 74       | AMIN                                             | AM local oscillation<br>signal input | mode, 10 to 60 MHz in FM2 mode, 1<br>to 30 MHz in HF mode, and 0.5 to 20<br>MHz in LF mode.<br>A built-in input amp and capacitive<br>coupling support low-amplitude<br>operation.<br>Note: In PLL Off mode or when the<br>pins are not set for input, the<br>input goes to high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RFIN<br>VDD<br>T |

| 75       | VPLL                                             | PLL constant voltage<br>output       | Constant voltage output for the PLL.<br>The PLL constant voltage is used as<br>the power supply for the PLL and IF<br>counter. In PLL On mode, the<br>constant voltage power supply is 3.55<br>V (typ.). In PLL Off mode, the V <sub>DD</sub> is<br>output. Connecting a capacitor (0.1<br>$\mu$ F, 10 $\mu$ F typ.) stabilizes the power<br>supply.                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

| Pin No.  | Symbol            | Pin Name                                   | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Remarks |

|----------|-------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 77<br>78 | DO1<br>DO2/OUT    | Phase comparator<br>output<br>/output port | PLL phase comparator output pins.<br>In tri-state output, when the<br>programmable counter divider output<br>is higher than the reference<br>frequency, the pins output High level;<br>when the output is lower than the<br>reference frequency, the pins output<br>Low level. When the outputs match,<br>the pins go to high impedance.<br>Because DO1 and DO2 are output in<br>parallel, optimal filter constants can be<br>designed for both the AM and FM<br>bands.<br>The DO2 pin can be programmed to<br>high impedance or set as an output<br>port (OUT). Therefore, lockup time<br>can be improved using the DO1 and<br>DO2 pins or the pins can be<br>effectively used as output ports.<br>Lock-up time can also be improved by<br>using DO1 and DO2 together by<br>setting the pins to High-Speed Lock<br>mode when using a 4.5 MHz<br>oscillator. When the phase difference<br>equals or exceeds ±1.11 µs, DO1 and<br>DO2 output the phase difference is<br>less than ±1.11 µs, the DO2 output<br>goes to high impedance and only DO1<br>outputs the phase difference pulse. |         |

| 79       | TEST2             | Test mode control<br>input 2               | Input pin for controlling Test mode.<br>When the pins are at High level, the<br>device is in Test mode; at Low level,<br>in normal operation.<br>Normally, set the pins to Low level or<br>NC (pull-down resistors are<br>incorporated).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 80~83    | P6-0<br>~<br>P6-3 | I/O port 6                                 | 4-bit CMOS I/O ports.<br>Input and output can be programmed<br>in 1-bit units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 84~87    | P7-0              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| 88~91    | P8-0<br>≀<br>P8-3 | I/O port 8                                 | 4-bit CMOS I/O port.<br>Input and output can be programmed<br>in 1-bit units.<br>As the pins can be pulled up or pulled<br>down by software they can be used as<br>key input pins. When set to an I/O port<br>input, that input can be varied to<br>release Clock Stop or Wait modes or<br>to set the MUTE bit of the MUTE pin<br>to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Pin No.                    | Symbol                               | Pin Name                           | Function and Operation                                                                                                                                                                                                                                                                                                                                                                        | Remarks                     |

|----------------------------|--------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 92                         | VCPU                                 | CPU constant<br>voltage output     | Constant voltage output pin for the CPU or oscillators.<br>In normal mode, a constant voltage power supply of 2.95 V (typ.) is output; in Clock Stop mode, V <sub>DD</sub> is output. Connecting a capacitor (0.1 $\mu$ F, 10 $\mu$ F typ.) stabilizes the power supply.                                                                                                                      |                             |

| 94                         | X <sub>OUT2</sub>                    | 75 kHz crystal                     | Crystal oscillator pins.<br>Connect a 4.5 MHz crystal (Ci = Co = $30 \text{ pF}$ typ.) to X <sub>IN1</sub> and X <sub>OUT1</sub> and a 75 kHz crystal (Ci = Co = $30 \text{ pF}$ typ.) to X <sub>IN2</sub> and X <sub>OUT2</sub> .<br>Two different types of crystal resonators (4.5 MHz and 75 kHz) can be connected, or simply connect one (either 4.5 MHz or 75 kHz). Note that            | Xout2 ROUT2<br>RfXT2<br>VDD |

| 95                         | X <sub>IN2</sub>                     | oscillator pins                    | if a 75 kHz crystal only is connected,<br>X <sub>IN1</sub> must be fixed to GND level. If a<br>4.5 MHz crystal only is connected, it is<br>not necessary to fix the 75 kHz crystal<br>oscillator pins. If both 4.5 MHz and 75<br>kHz crystal oscillators are connected,<br>after a reset the CPU operates on the<br>4.5 MHz crystal oscillator clock. The<br>clock can be readily switched by |                             |

| 97                         | X <sub>OUT1</sub>                    | 4.5 MHz crystal                    |                                                                                                                                                                                                                                                                                                                                                                                               |                             |

| 98                         | XIN1                                 | oscillator pins                    |                                                                                                                                                                                                                                                                                                                                                                                               |                             |

| 100                        | $V_{EE}$                             | LCD driver bias voltage output pin | This is the bias voltage output pin for the LCD driver.                                                                                                                                                                                                                                                                                                                                       | _                           |

| 39<br>56<br>76<br>96       | VDD1<br>VDD2<br>VDD3<br>VDD4         |                                    | Pins used for supplying power.<br>In PLL On mode, the pins supply $V_{DD}$<br>= 4.0 to 5.5 V; in PLL Off mode, the<br>pins supply $V_{DD}$ = 3.5 to 5.5 V.<br>In backup state (on execution of the<br>CKSTP instruction), current<br>dissipation becomes low (10 µA max),<br>reducing the power supply voltage to                                                                             | VDD                         |

| 41<br>55<br>72<br>93<br>99 | GND1<br>GND2<br>GND3<br>GND4<br>GND5 | Power supply pins                  | <ul> <li>2.0 V.</li> <li>If 3.5 V or more is applied to these pins when the voltage is 0 V, a system reset is applied to the device and the program starts from address 0 (power-on reset).</li> <li>Note: To operate the power-on reset, allow 10 to 100 ms while the device power supply voltage rises.</li> </ul>                                                                          | GND                         |

#### Absolute Maximum Ratings (Ta = 25°C)

| Characteristics                      | Symbol               | Rating                   | Unit |

|--------------------------------------|----------------------|--------------------------|------|

| Power supply voltage                 | V <sub>DD</sub>      | -0.3~6.0                 | V    |

| V <sub>PP</sub> Power supply voltage | V <sub>PP</sub>      | -0.3~13.0                | V    |

| Input voltage 1                      | V <sub>IN1</sub> (*) | -0.3~VCPU + 0.3          | V    |

| Input voltage 2                      | V <sub>IN2</sub> (*) | -0.3~VPLL + 0.3          | V    |

| Input voltage 3                      | V <sub>IN3</sub> (*) | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Power dissipation                    | PD                   | 400                      | mW   |

| Operating temperature                | T <sub>opr</sub>     | -40~85                   | °C   |

| Storage temperature                  | T <sub>stg</sub>     | -65~150                  | °C   |

\*: V<sub>IN1</sub>: Includes X<sub>IN1</sub>, X<sub>OUT1</sub>, X<sub>IN2</sub>, and X<sub>OUT2</sub> pins V<sub>IN2</sub>: Includes AMin, FMin, IFin1, IFin2 (when IF input set) pins V<sub>IN3</sub>: Input pins, apart from V<sub>IN1</sub> and V<sub>IN2</sub>

#### Electrical Characteristics (unless otherwise specified, $Ta = -40 - 85^{\circ}C$ , $V_{DD} = 3.5 - 5.5 V$ )

| Characteristics                               | Symbol           | Test<br>Circuit | Test Condition                                                                                                          | Min  | Тур. | Max  | Unit |

|-----------------------------------------------|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Operating power supply voltage range          | V <sub>DD1</sub> | —               | When CPU operating                                                                                                      | 3.5  | ~    | 5.5  | V    |

| Operating power supply voltage range          | V <sub>DD2</sub> |                 | When PLL operating                                                                                                      | 4.0  | ~    | 5.5  | v    |

| Memory hold voltage range                     | VHD              | —               | Crystal oscillation stopped<br>(CKSTP instruction executed)                                                             | 2.0  | ~    | 5.5  | V    |

|                                               | I <sub>DD1</sub> | _               | When PLL operating (VHF<br>mode) and at FMin = 230 MHz<br>input, Ta = 25°C                                              |      | 3    | 5    |      |

|                                               | I <sub>DD2</sub> | _               | When CPU only operating<br>(4.5-MHz clock operating,<br>75-kHz oscillation stopped, PLL<br>off, display lit), Ta = 25°C |      | 1.0  | 1.5  | mA   |

|                                               | I <sub>DD3</sub> | _               | When CPU only operating<br>(75-kHz clock operating,<br>4.5-MHz oscillation stopped,<br>PLL off, display lit), Ta = 25°C |      | 0.3  | 0.5  |      |

| Operating power supply current                | I <sub>DD4</sub> | —               | In Hard Wait mode (4.5-MHz<br>crystal only operating),<br>Ta = 25°C                                                     | _    | 200  | _    |      |

|                                               | I <sub>DD5</sub> | _               | In Hard Wait mode (75-kHz<br>crystal only operating),<br>Ta = 25°C                                                      | _    | 70   | _    |      |

|                                               | I <sub>DD6</sub> | _               | When soft wait executed (PLL<br>off, CPU operating<br>intermittently on 4.5-MHz clock,<br>display lit), Ta = 25°C       |      | 350  | _    | μΑ   |

|                                               | I <sub>DD7</sub> | _               | When soft wait executed (PLL<br>off, CPU operating<br>intermittently on 75-kHz clock,<br>display lit), Ta = 25°C        |      | 250  | _    |      |

| Memory hold current                           | IHD              |                 | Crystal oscillator stopped<br>(CKSTP instruction executed)                                                              |      | 0.1  | 10   | μA   |

| Crystal oscillator frequency                  | fXT1             |                 | Crystal oscillator 1<br>(X <sub>IN1</sub> , X <sub>OUT1</sub> )                                                         |      | 4.5  | _    | MHz  |

|                                               | fXT2             | _               | Crystal oscillator 2<br>(X <sub>IN2</sub> , X <sub>OUT2</sub> )                                                         | _    | 75   | _    | kHz  |

| Crystal oscillation startup time              | tst              | _               | Crystal oscillator fXT2 = 75 kHz $(X_{IN2}, X_{OUT2})$                                                                  | _    | _    | 1.0  | s    |

| Constant voltage power supply voltage for CPU | VCPU             | _               | GND reference (VCPU)                                                                                                    | 2.65 | 2.95 | 3.25 | V    |

| Constant voltage power supply voltage for PLL | VPLL             | _               | GND reference (VPLL), $V_{DD} = 4.0$ to 5.5 V                                                                           | 3.15 | 3.55 | 3.95 | V    |

| Low voltage detection voltage                 | VSTOP            |                 | (VCPU), STOP F/F bit detected                                                                                           | 2.15 | 2.40 | 2.65 | V    |

#### Programmable Counter and IF Counter Operating Frequency Ranges

| Characteristics | Symbol | Test<br>Circuit | Test Condition                                                 | Min | Тур. | Max | Unit |

|-----------------|--------|-----------------|----------------------------------------------------------------|-----|------|-----|------|

| FMin (VHF mode) | fVHF   | _               | $V_{IN} = 0.2 \ V_{p\text{-}p}, \ V_{DD} = 4.0\text{-}5.5 \ V$ | 50  | ~    | 230 |      |

| FMin (FM mode)  | fFM1   |                 | $V_{IN} = 0.1 \ V_{p\text{-}p}, \ V_{DD} = 4.0{\sim}5.5 \ V$   | 50  | ~    | 140 |      |

|                 | fFM2   | _               | $V_{IN} = 0.1 \ V_{p\text{-}p}, \ V_{DD} = 4.0{\sim}5.5 \ V$   | 10  | ~    | 60  | MHz  |

| AMin (HF mode)  | fHF    |                 | $V_{IN} = 0.1 \ V_{p\text{-}p}, \ V_{DD} = 4.0{\sim}5.5 \ V$   | 1.0 | ~    | 30  |      |

| AMin (LF mode)  | fLF    | —               | $V_{IN} = 0.1 \ V_{p\text{-}p}, \ V_{DD} = 4.0{\sim}5.5 \ V$   | 0.5 | ~    | 20  |      |

| IFIN1, IFIN2    | fIF    |                 | $V_{IN} = 0.1 \ V_{p\text{-}p}, \ V_{DD} = 4.0{\sim}5.5 \ V$   | 0.3 | ~    | 20  |      |

#### Programmable Counter and IF Counter Input Oscillation Ranges

| Characteristics | Symbol | Test<br>Circuit | Test Condition                   | Min | Тур. | Max | Unit             |

|-----------------|--------|-----------------|----------------------------------|-----|------|-----|------------------|

| FMin (VHF mode) | VVHF   | _               | fVHF, $V_{DD} = 4.0$ ~5.5 V      | 0.2 | ~    | 1.0 |                  |

| FMin (FM mode)  | VFM    | _               | $fFM1/fFM2, V_{DD} = 4.0~5.5 V$  | 0.1 | ~    | 1.0 |                  |

| AMin (HF mode)  | VHF    | _               | fHF, $V_{DD} = 4.0$ ~5.5 V       | 0.1 | ~    | 1.0 | V <sub>p-p</sub> |

| AMin (LF mode)  | VLF    | _               | fLF, $V_{DD} = 4.0$ ~5.5 V       | 0.1 | ~    | 1.0 |                  |

| IFIN1, IFIN2    | VIF    | _               | fIF, V <sub>DD</sub> = 4.0~5.5 V | 0.1 | ~    | 1.0 |                  |

#### LCD Common Outputs/Segment Outputs (COM~COM4, S1~S22)

| Characteristics        |                           | Symbol | Test<br>Circuit | Test Condition           | Min  | Тур. | Max  | Unit |

|------------------------|---------------------------|--------|-----------------|--------------------------|------|------|------|------|

|                        | GND level                 | VBS1   | _               | $V_{DD} = 5 V$ , no load | _    | 0.00 | 0.15 |      |

|                        | 1/3 V <sub>DD</sub> level | VBS2   |                 | $V_{DD} = 5 V$ , no load | 1.52 | 1.67 | 1.82 | 1    |

| Bias output<br>voltage | 1/2 V <sub>DD</sub> level | VBS3   | _               | $V_{DD} = 5 V$ , no load | 2.35 | 2.50 | 2.65 | V    |

| . enage                | 2/3 V <sub>DD</sub> level | VBS4   | _               | $V_{DD} = 5 V$ , no load | 3.18 | 3.33 | 3.48 |      |

|                        | V <sub>DD</sub> level     | VBS5   |                 | $V_{DD} = 5 V$ , no load | 4.85 | 5.00 | _    |      |

#### Output Ports and I/O Ports (OT1~OT30, P1-0~P10-3)

| Characteristics               |            | Symbol          | Test<br>Circuit | Test Condition                                                             | Min                   | Тур.  | Max                 | Unit |

|-------------------------------|------------|-----------------|-----------------|----------------------------------------------------------------------------|-----------------------|-------|---------------------|------|

| Output<br>current             | High level | IOH1            | _               | $V_{DD}=5~V,~V_{OH}=V_{DD}-0.5~V$                                          | -1.00                 | -2.50 | _                   |      |

|                               | Low level  | IOL1            | _               | $V_{DD} = 5 \text{ V}, V_{OL} = 0.5 \text{ V},$<br>except for P5-1 to P5-3 | 1.00                  | 2.50  |                     | mA   |

|                               |            | IOL2            | _               | V <sub>DD</sub> = 5 V, V <sub>OL</sub> = 0.5V,<br>P5-1~P5-3                | 4.00                  | 10.00 |                     |      |

| Input leakage current         |            | ILI             | _               | V <sub>IH</sub> = VDD, V <sub>IL</sub> = 0V<br>(P1-0~P10-3)                |                       |       | ±1.0                | μA   |

| Input voltage                 | High level | V <sub>IH</sub> | _               | (P1-0~P10-3)                                                               | V <sub>DD</sub> × 0.8 | 1     | V <sub>DD</sub>     | V    |

|                               | Low level  | VIL             | _               | (P1-0~P10-3)                                                               | 0                     | 1     | $V_{DD} \times 0.2$ | v    |

| Input pulled-up/down resistor |            | RIN1            |                 | When P8-0 to P8-3 pulled up/down                                           | 15                    | 60    | 250                 | kΩ   |

#### MUTE, DO1, DO2 Output

| Characteristics            |            | Symbol | Test<br>Circuit | Test Condition                                              | Min   | Тур.  | Max  | Unit |

|----------------------------|------------|--------|-----------------|-------------------------------------------------------------|-------|-------|------|------|

| Output<br>current          | High level | IOH1   | _               | $V_{DD}=5~V,~V_{OH}=V_{DD}-0.5~V$                           | -1.25 | -2.50 | _    | mA   |

|                            | Low level  | IOL1   | _               | $V_{DD}=5~V,~V_{OL}=0.5~V$                                  | 1.25  | 2.50  | _    | ША   |

| Output off leakage current |            | ITL    | _               | V <sub>DD</sub> = 5 V, VTLH = 5 V,<br>VTLL = 0 V (DO1, DO2) |       |       | ±100 | nA   |

#### HOLD, INTR1/2, IN1/2 Input Ports, RESET Input

| C                     | Characteristics | Symbol          | Test<br>Circuit | Test Condition                | Min                   | Тур. | Max                 | Unit |

|-----------------------|-----------------|-----------------|-----------------|-------------------------------|-----------------------|------|---------------------|------|

| Input leakage current |                 | ILI             | _               | $V_{IH}=V_{DD},\ V_{IL}=0\ V$ | _                     | _    | ±1.0                | μΑ   |

| Output<br>current     | High level      | V <sub>IH</sub> | _               | _                             | V <sub>DD</sub> × 0.8 | ~    | V <sub>DD</sub>     | V    |

|                       | Low level       | V <sub>IL</sub> | _               | _                             | 0                     | 2    | $V_{DD} \times 0.2$ | v    |

#### AD Converter (ADIN1~ADIN8, DCREF)

| Characteristics                 | Symbol | Test<br>Circuit | Test Condition                                            | Min | Тур. | Max             | Unit |

|---------------------------------|--------|-----------------|-----------------------------------------------------------|-----|------|-----------------|------|

| Analog input voltage range      | VAD    | —               | ADin1~ADin8                                               | 0   | ~    | V <sub>DD</sub> | V    |

| Resolution                      | VRES   | —               | _                                                         | _   | 8    | _               | bit  |

| Linear error                    | _      | —               | —                                                         | _   | ±0.5 | ±1.0            | LSB  |

| Conversion total error          | _      | —               | $V_{DD} = 5 V, DCREF = 5 V$                               | _   | ±3.0 | ±8.0            | LOD  |

| Analog input leakage            | ILI    | _               | $V_{DD} = 5V, V_{IH} = 5V, V_{IL} = 0 V$<br>(ADin1~ADin8) | _   | _    | ±1.0            | μΑ   |

| Reference voltage input current | IREF   | _               | V <sub>DD</sub> = 5V, DCREF = 5 V<br>(DCREF)              |     | 0.5  | 1.0             | mA   |

#### **Crystal Oscillators**

| Characteristics                     | Symbol | Test<br>Circuit | Test Condition                         | Min  | Тур. | Max  | Unit   |  |

|-------------------------------------|--------|-----------------|----------------------------------------|------|------|------|--------|--|

| XIN1 amp feedback resistance        | RfXT1  | _               | (X <sub>IN1</sub> -X <sub>OUT1</sub> ) | 0.35 | 1.0  | 3.00 | MΩ     |  |

| XIN2 amp feedback resistance        | RfXT2  | _               | (X <sub>IN2</sub> -X <sub>OUT2</sub> ) | 3.5  | 10   | 30.0 | 1012.2 |  |

| X <sub>OUT1</sub> output resistance | ROUT1  | _               | (X <sub>OUT1</sub> )                   | 1.2  | 3.0  | 10.0 | kO     |  |

| X <sub>OUT2</sub> output resistance | ROUT2  | —               | (X <sub>OUT2</sub> )                   | 1.5  | 4.0  | 15.0 | kΩ     |  |

#### Others

| Characteristics               | Symbol | Test<br>Circuit | Test Condition                             | Min  | Тур. | Max  | Unit |

|-------------------------------|--------|-----------------|--------------------------------------------|------|------|------|------|

| Input pulled-down resistance  | RIN2   |                 | (TEST)                                     | 15.0 | 60   | 250  |      |

| Input amp feedback resistance | RfIN   | _               | VPLL = 3.5 V<br>(FMin, AMin, IFin1, IFin2) | 350  | 800  | 3500 | kΩ   |

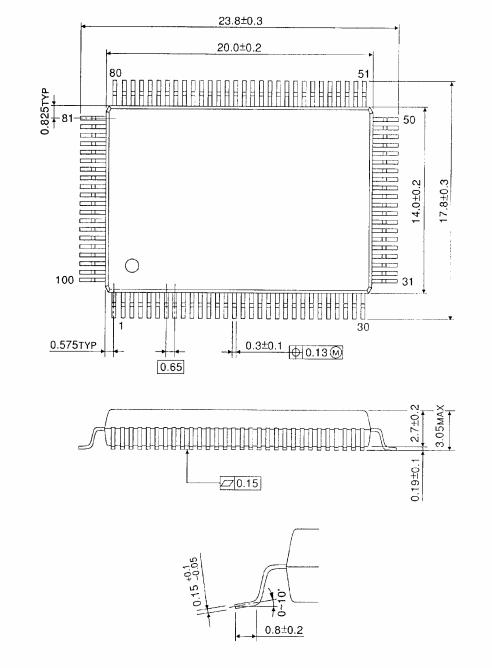

#### **Package Dimensions**

Unit : mm

Weight: 1.6 g (typ.) Note: Lead type PD-Pff

#### **RESTRICTIONS ON PRODUCT USE**

Handbook" etc. 021023\_A

• The information contained herein is subject to change without notice. 021023\_D

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

• The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_C

• The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E