# **RQK2001HQDQA**

## Silicon N Channel MOS FET **Power Switching**

REJ03G1731-0100 Rev.1.00 Sep 01, 2008

### **Features**

• High drain to source voltage and Low gate drive

$V_{DSS}$ : 200 V and  $V_{GSS}$ :  $\pm 30$  V

- Low drive current

- High speed switching

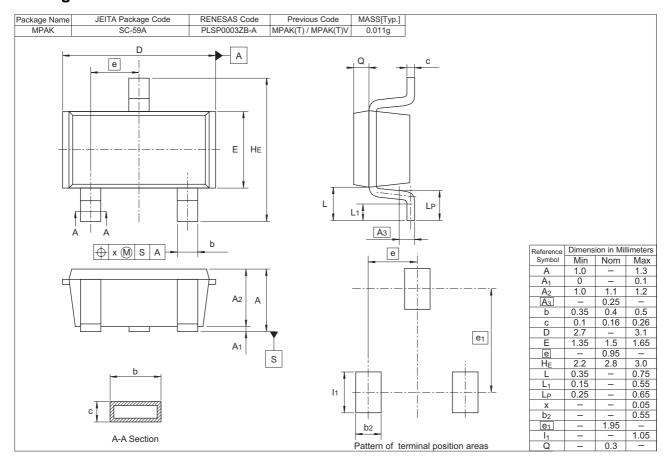

- Small traditional package (MPAK)

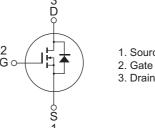

### **Outline**

RENESAS Package code: PLSP0003ZB-A (Package name: MPAK)

1. Source

3. Drain

Note: Marking is "HQ".

### **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                                     | Symbol                      | Ratings     | Unit   |

|------------------------------------------|-----------------------------|-------------|--------|

| Drain to source voltage                  | V <sub>DSS</sub>            | 200         | V      |

| Gate to source voltage                   | V <sub>GSS</sub>            | ±30         | V      |

| Drain current                            | I <sub>D</sub>              | 0.4         | А      |

| Drain peak current                       | I <sub>D(pulse)</sub> Note1 | 1.6         | А      |

| Body - drain diode reverse drain current | I <sub>DR</sub>             | 0.4         | А      |

| Channel dissipation                      | Pch Note2                   | 0.8         | W      |

| Thermal resistance                       | Rth(ch-a) Note2             | 156         | °C / W |

| Channel temperature                      | Tch                         | 150         | °C     |

| Storage temperature                      | Tstg                        | -55 to +150 | °C     |

Notes: 1. PW  $\leq$  10  $\mu$ s, Duty cycle  $\leq$  1%

2. When using the glass epoxy board (FR-4  $40 \times 40 \times 1$  mm)

## **Electrical Characteristics**

$(Ta = 25^{\circ}C)$

| Item                                | Symbol               | Min | Тур | Max  | Unit | Test conditions                                              |

|-------------------------------------|----------------------|-----|-----|------|------|--------------------------------------------------------------|

| Drain to source breakdown voltage   | V <sub>(BR)DSS</sub> | 200 | _   | _    | V    | $I_D = 10 \text{ mA}, V_{GS} = 0$                            |

| Gate to source leak current         | I <sub>GSS</sub>     |     | _   | +0.1 | μΑ   | $V_{GS} = +30 \text{ V}, V_{DS} = 0$                         |

| Gate to source leak current         | I <sub>GSS</sub>     | _   | _   | -0.1 | μΑ   | $V_{GS} = -30 \text{ V}, V_{DS} = 0$                         |

| Zero gate voltage drain current     | I <sub>DSS</sub>     |     | _   | 1    | μΑ   | $V_{DS} = 200 \text{ V}, V_{GS} = 0$                         |

| Gate to source cutoff voltage       | $V_{GS(off)}$        | 3   | _   | 4.5  | V    | $V_{DS} = 10 \text{ V}, I_{D} = 1 \text{ mA}$                |

| Drain to source on state resistance | R <sub>DS(on)</sub>  | 1   | 5.0 | 6.7  | Ω    | $I_D = 0.15 \text{ A}, V_{GS} = 10 \text{ V}^{\text{Note3}}$ |

| Forward transfer admittance         | y <sub>fs</sub>      | 0.2 | 0.3 | _    | S    | $I_D = 0.15 \text{ A}, V_{DS} = 10 \text{ V}^{\text{Note3}}$ |

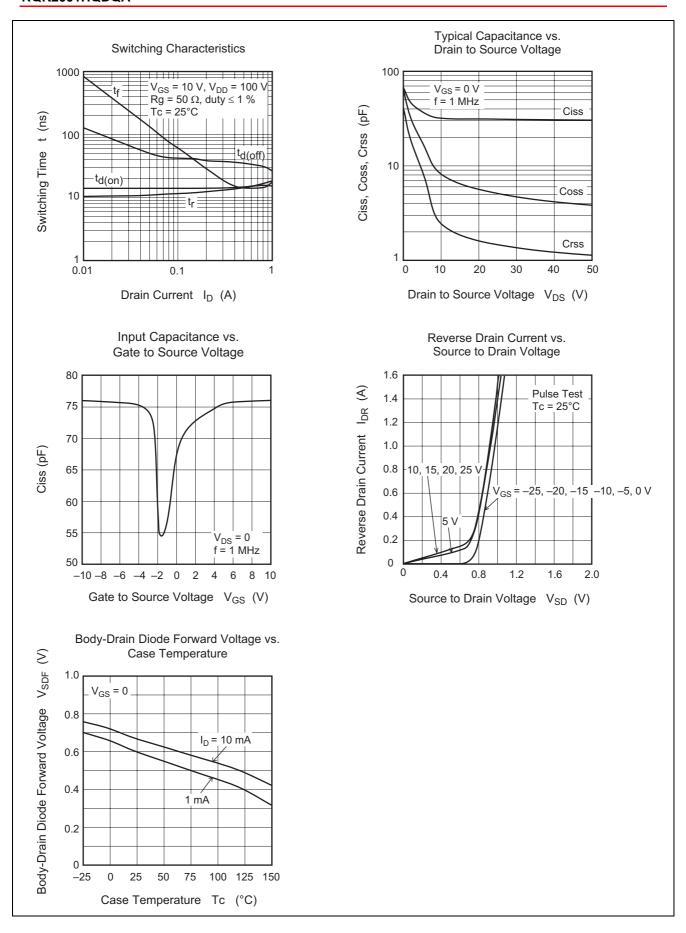

| Input capacitance                   | Ciss                 | 1   | 30  | _    | pF   | V <sub>DS</sub> = 25 V                                       |

| Output capacitance                  | Coss                 | 1   | 5   | _    | pF   | $V_{GS} = 0$                                                 |

| Reverse transfer capacitance        | Crss                 | _   | 2   | _    | pF   | f = 1 MHz                                                    |

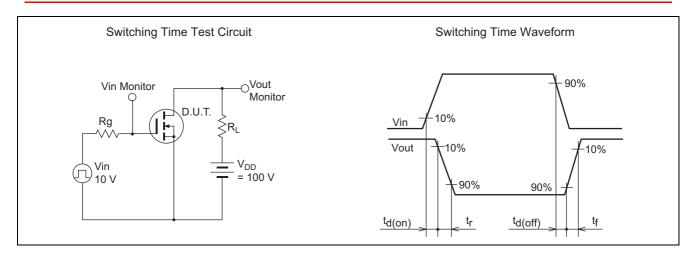

| Turn - on delay time                | t <sub>d(on)</sub>   | _   | 13  | _    | ns   | I <sub>D</sub> = 0.15 A                                      |

| Rise time                           | t <sub>r</sub>       | _   | 12  | _    | ns   | V <sub>GS</sub> = 10 V                                       |

| Turn - off delay time               | t <sub>d(off)</sub>  | _   | 42  | _    | ns   | $R_L = 667 \Omega$                                           |

| Fall time                           | t <sub>f</sub>       | _   | 38  | _    | ns   | $Rg = 50 \Omega$                                             |

| Total gate charge                   | Qg                   | _   | 1.8 | _    | nC   | V <sub>DD</sub> = 100 V                                      |

| Gate to Source charge               | Qgs                  | _   | 0.4 | _    | nC   | V <sub>GS</sub> = 10 V                                       |

| Gate to drain charge                | Qgd                  | _   | 0.9 | _    | nC   | $I_D = 0.4 A$                                                |

| Body - drain diode forward voltage  | $V_{DF}$             | _   | 0.8 | 1.2  | V    | $I_F = 0.4 \text{ A}, V_{GS} = 0^{\text{Note3}}$             |

Notes: 3. Pulse test

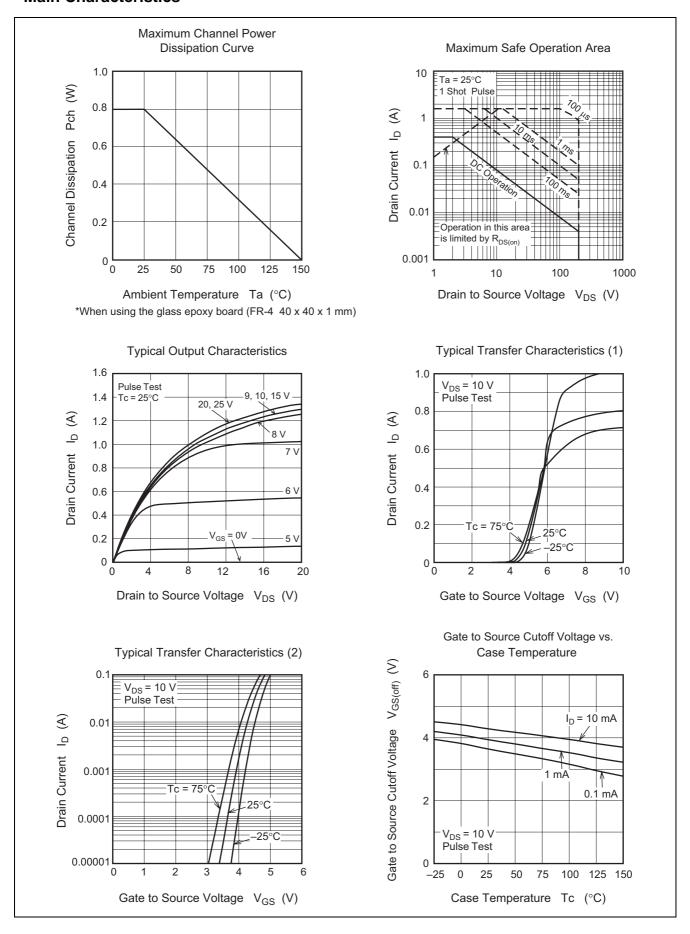

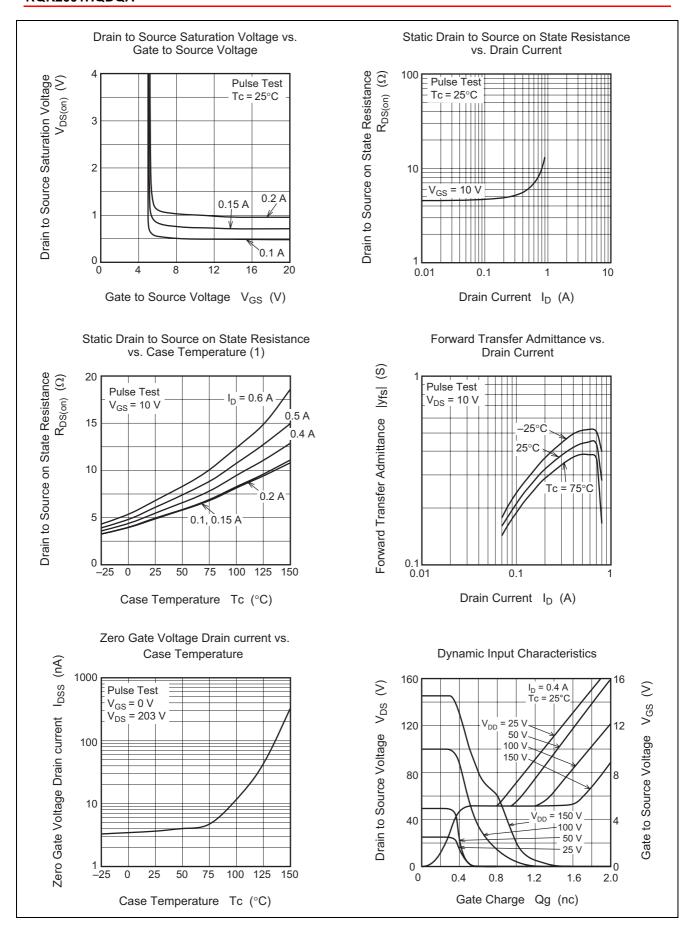

### **Main Characteristics**

### **Package Dimensions**

## **Ordering Information**

| Part No.         | Quantity  | Shipping Container               |

|------------------|-----------|----------------------------------|

| RQK2001HQDQATL-E | 3000 pcs. | φ178 mm reel, 8 mm Emboss taping |

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the such procedure in the procedure of the development of the

### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510