## GENERAL PURPOSE PLASTIC SILICON RECTIFIER Reverse Voltage - 50 to 1000 V Forward Current - 1.5 A

## **Features**

- · High current capability

- Low leakage current

- Low cost

## **Mechanical Data**

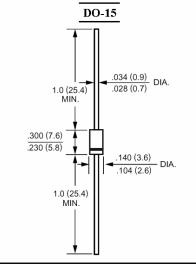

• Case: Molded plastic, DO-15

• Terminals: Plated axial leads, solderable per MIL-STD-202, method 208 guaranteed · Polarity: Color band denotes cathode end

• Mounting position: Any

Dimensions in inches and (millimeters)

## **Absolute Maximum Ratings and Characteristics**

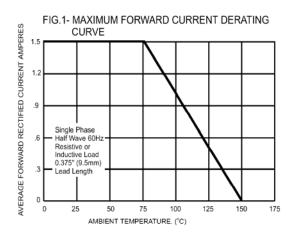

Ratings at 25 °C ambient temperature unless otherwise specified. Single phase, half wave, 60 Hz, resistive or inductive load. For capacitive load, derate current by 20%.

| Parameter                                                                                          | Symbols           | 1N<br>5391  | 1N<br>5392 | 1N<br>5393 | 1N<br>5394 | 1N<br>5395 | 1N<br>5396 | 1N<br>5397 | 1N<br>5398 | 1N<br>5399 | Units |

|----------------------------------------------------------------------------------------------------|-------------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|-------|

| Maximum Recurrent Peak Reverse Voltage                                                             | $V_{RRM}$         | 50          | 100        | 200        | 300        | 400        | 500        | 600        | 800        | 1000       | V     |

| Maximum RMS Voltage                                                                                | V <sub>RMS</sub>  | 35          | 70         | 140        | 210        | 280        | 350        | 420        | 560        | 700        | V     |

| Maximum DC Blocking Voltage                                                                        | $V_{DC}$          | 50          | 100        | 200        | 300        | 400        | 500        | 600        | 800        | 1000       | V     |

| Maximum Average Forward Rectified Current 0.375"(9.5 mm) Lead Length at $T_A = 75$ °C              | I <sub>(AV)</sub> | 1.5         |            |            |            |            |            |            |            |            | Α     |

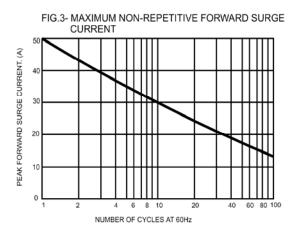

| Peak Forward Surge Current, 8.3 ms Single Half-sine-wave Superimposed on rated load (JEDEC method) | I <sub>FSM</sub>  | 50          |            |            |            |            |            |            |            |            | А     |

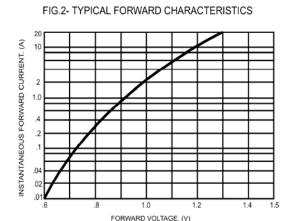

| Maximum Forward Voltage at 1.5 A DC                                                                | V <sub>F</sub>    | 1.4         |            |            |            |            |            |            |            |            | V     |

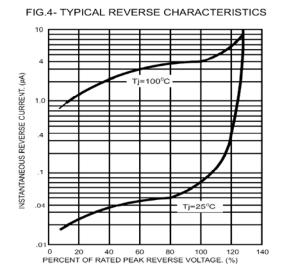

| Maximum Reverse Current $T_A = 25$ °C at Rated DC Blocking Voltage $T_A = 100$ °C                  | I <sub>R</sub>    | 5<br>500    |            |            |            |            |            |            |            |            | μΑ    |

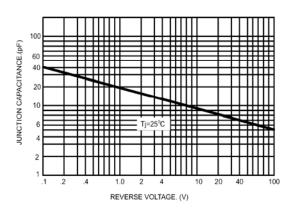

| Typical Junction Capacitance 1)                                                                    | CJ                | 20          |            |            |            |            |            |            |            |            | pF    |

| Typical Thermal Resistance 2)                                                                      | $R_{\theta JA}$   | 50          |            |            |            |            |            |            |            |            | °C/W  |

| Operating Junction Temperature Range                                                               | TJ                | -55 to +150 |            |            |            |            |            |            |            |            | °C    |

| Storage Temperature Range                                                                          | T <sub>stg</sub>  | -55 to +150 |            |            |            |            |            |            |            |            | °C    |

<sup>1)</sup> Measured at 1 MHz and applied reverse voltage of 4 VDC.

<sup>&</sup>lt;sup>2)</sup> Thermal resistance junction to ambient 0.375" (9.5 mm) lead length P.C.B mounted.

FIG.5- TYPICAL JUNCTION CAPACITANCE

Dated: 25/04/2006 H