### **Typical Applications**

The HMC641LC4 is ideal for:

- Telecom Infrastructure

- Microwave Radio & VSAT

- Military & Space Hybrids

- Test Instrumentation

- SATCOM & Sensors

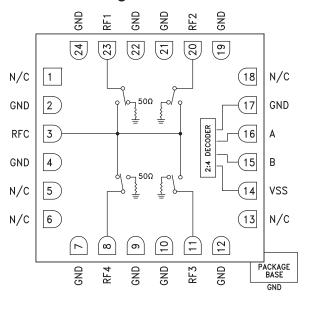

#### **Functional Diagram**

#### **Features**

Broadband Performance: DC - 20 GHz

High Isolation: 42 dB @ 12 GHz

Low Insertion Loss: 2.1 dB @ 12 GHz

Integrated 2:4 TTL Decoder

24 Lead 4x4mm SMT Package: 16mm<sup>2</sup>

#### **General Description**

The HMC641LC4 is a broadband non-reflective GaAs PHEMT SP4T switch in a compact 4x4 mm ceramic package. Covering DC to 20 GHz, this switch offers high isolation, low insertion loss and on-chip termination of isolated ports. This switch also includes an on board binary decoder circuit which reduces the number of required logic control lines from four to two. The HMC641LC4 is controlled with 0/ -5V logic, exhibits fast switching speed and consumes much less DC current than pin diode based solutions. The HMC641LC4 is also available in die form as the HMC641.

# Electrical Specifications, $T_A = +25^{\circ}$ C, With 0/-5V Control, Vss = -5V, 50 Ohm System

| Parameter                                                                                 |             | Frequency                        | Min.     | Тур.       | Max.       | Units      |

|-------------------------------------------------------------------------------------------|-------------|----------------------------------|----------|------------|------------|------------|

| Insertion Loss                                                                            |             | DC - 12 GHz<br>DC - 20 GHz       |          | 1.6<br>2.3 | 2.8<br>3.5 | dB<br>dB   |

| Isolation (RFC to RF1 - RF4)                                                              |             | DC - 12 GHz<br>DC - 20 GHz       | 30<br>30 | 42<br>40   |            | dB<br>dB   |

| Return Loss                                                                               | "On State"  | DC - 12 GHz<br>DC - 20 GHz       |          | 18<br>17   |            | dB<br>dB   |

| Return Loss                                                                               | "Off State" | DC - 20 GHz                      |          | 13         |            | dB         |

| Input Power for 1 dB Compression                                                          |             | 0.05 - 0.25 GHz<br>0.25- 20 GHz  | 10<br>20 | 15<br>23   |            | dBm<br>dBm |

| Input Third Order Intercept<br>(Two-Tone Input Power= +14 dBm Each Tone)                  |             | 0.05 - 0.25 GHz<br>0.25 - 20 GHz |          | 30<br>39   |            | dBm<br>dBm |

| Switching Characteristics<br>tRISE, tFALL (10/90% RF)<br>tON, tOFF (50% CTL to 10/90% RF) |             | DC - 20 GHz                      |          | 15<br>88   |            | ns<br>ns   |

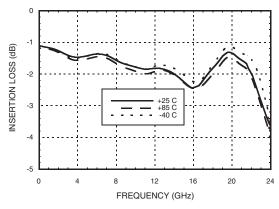

### Insertion Loss vs. Temperature

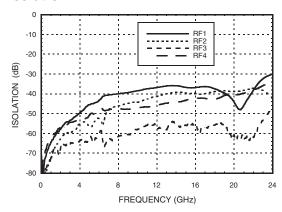

#### Isolation

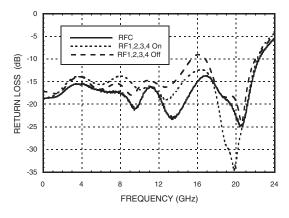

#### **Return Loss**

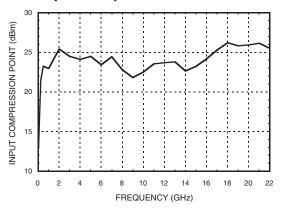

#### 1 dB Input Compression Point

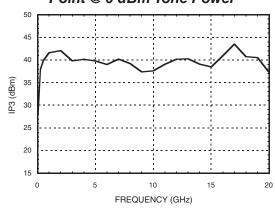

# Input Third Order Intercept Point @ 0 dBm Tone Power

### **Absolute Maximum Ratings**

| Bias Voltage (Vss)                                                   | -7V              |  |

|----------------------------------------------------------------------|------------------|--|

| Control Voltage Range (A & B)                                        | Vss -0.5V to +1V |  |

| Maximum Input Power                                                  | +24 dBm          |  |

| Channel Temperature                                                  | 150 °C           |  |

| Thermal Resistance<br>Channel to die bottom (Insertion Loss Path)    | 199 °C/W         |  |

| Thermal Resistance Channel to die bottom (Terminated Path)  219 °C/W |                  |  |

| Storage Temperature                                                  | -65 to +150 °C   |  |

| Operating Temperature                                                | -40 to +85 °C    |  |

| ESD Sensitivity (HBM) Class 1A                                       |                  |  |

#### **Truth Table**

| Control Input |      | Signal Path State |  |

|---------------|------|-------------------|--|

| Α             | В    | RFC to:           |  |

| High          | High | RF1               |  |

| Low           | High | RF2               |  |

| High          | Low  | RF3               |  |

| Low           | Low  | RF4               |  |

### Bias Voltage & Current

| Vss Range= -5.0 Vdc ±10% |     |                   |  |  |

|--------------------------|-----|-------------------|--|--|

| Vss Iss (Typ) (Vdc) (mA) |     | Iss (Max)<br>(mA) |  |  |

| -5                       | 1.7 | 5.0               |  |  |

### TTL/CMOS Control Voltages

| State | Bias Condition             |  |

|-------|----------------------------|--|

| Low   | -2.5V to 0V @ 30 μA Typ.   |  |

| High  | -5V to -3.8V @ 1.7 μA Typ. |  |

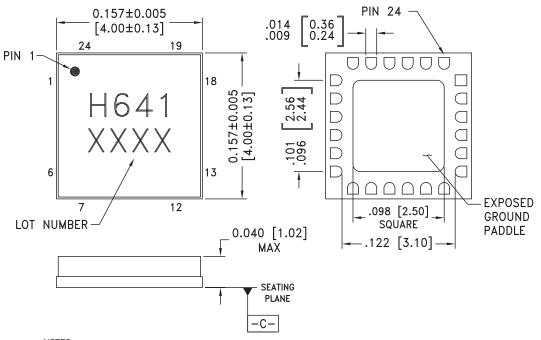

### **Outline Drawing**

#### BOTTOM VIEW

#### NOTES:

- 1. PACKAGE BODY MATERIAL: ALUMINA

- 2. LEAD AND GROUND PADDLE PLATING: 30-80 MICROINCHES GOLD OVER 50 MICROINCHES MINIMUM NICKEL.

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C-

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. CLASSIFIED AS MOISTURE SENSITIVITY LEVEL (MSL) 1.

# **Pin Descriptions**

| Pin Number                                                 | Function                   | Description                                                                                                                                | Interface Schematic |  |

|------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| 1, 5, 6, 13, 18                                            | N/C                        | These pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally. |                     |  |

| 2, 4, 7, 9, 10, 12,<br>17, 19, 21, 22, 24<br>Ground Paddle | GND                        | These pins and the exposed ground paddle must be connected to RF/DC ground.                                                                | =<br>GND            |  |

| 3, 8, 11, 20, 23                                           | RFC, RF1, RF2,<br>RF3, RF4 | These pads are DC coupled and matched to 50 Ohms. Blocking capacitors are required if RF line potential is not equal to 0V.                |                     |  |

| 14                                                         | Vss                        | Supply Voltage -5 Vdc ± 10%.                                                                                                               |                     |  |

| 15                                                         | CTLB                       | See Truth Table and Control Voltage Table.                                                                                                 | CTLA OTLB           |  |

| 16                                                         | CTLA                       | See Truth Table and Control Voltage Table.                                                                                                 | CTLB —              |  |

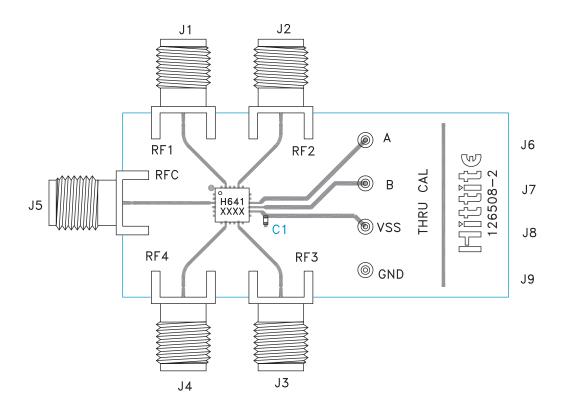

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 126511 [1]

| Item    | Description                  |

|---------|------------------------------|

| J1 - J5 | PCB Mount SMA Connector      |

| C1      | 1000 pF Capacitor, 0402 Pkg. |

| U1      | HMC641LC4 Switch             |

| PCB [2] | 126508 Evaluation PCB        |

<sup>[1]</sup> Reference this number when ordering complete evaluation PCB

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation board should be mounted to an appropriate heat sink. The evaluation circuit board shown is available from Hittite upon request.

<sup>[2]</sup> Circuit Board Material: Rogers 4350 or Arlon FR4