# **SPT7851**

# 10-Bit, 20 MSPS, 79mW Analog-to-Digital Converter

#### **Features**

- 10-Bit, 20 MSPS Analog-to-Digital converter

- Monolithic CMOS

- · Internal track-and-hold

- Low input capacitance: 1.4 pF

- Low power dissipation: 79mW

- 2.8 to 3.6V power supply range

- TTL-compatible outputs

- -40°C to +85°C operation

#### **Applications**

- CCD imaging cameras and sensors

- · Medical imaging

- RF communications

- · Document and film scanners

- Electro-optics

- Transient signal analysis

- Handheld equipment

#### **Description**

The SPT7851 10-bit, 20 MSPS analog-to-digital converter has a pipelined converter architecture built in a CMOS process. It delivers high performance with a typical power dissipation of only 79mW. With low distortion and high dynamic range, this device offers the performance needed for imaging, multimedia, telecommunications and instrumentation applications.

The SPT7851 is available in a 44-lead Thin Quad Flat Pack (TQFP) package in the industrial temperature range (-40°C to +85°C).

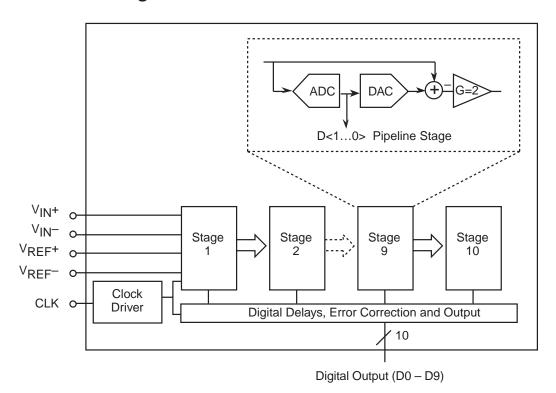

## **Functional Block Diagram**

# **Electrical Specifications**

$(T_A = T_{MIN} - T_{MAX}, V_{DD1} = V_{DD2} = V_{DD3} = 3.3V, V_{REF-} = 1.0V, V_{REF+} = 2.0V, Common Mode Voltage = 1.65V, f_{CLK} = 20 \, MSPS, Bias1 = 90 \mu A, Bias2 = 9.5 \mu A, Differential Input, Duty Cycle = 50%; unless otherwise noted)$

| Parameter                                       | Conditions                           | Test Level | Min  | Тур     | Max  | Units  |

|-------------------------------------------------|--------------------------------------|------------|------|---------|------|--------|

| DC Accuracy                                     |                                      |            |      |         |      |        |

| Resolution                                      |                                      |            |      | 10      |      | Bits   |

| Differential Linearity                          |                                      | V          |      | ±0.6    |      | LSB    |

| Integral Linearity                              |                                      | V          |      | ±0.75   |      | LSB    |

| No Missing Codes                                |                                      | VI         | G    | uarante | ed   |        |

| Analog Input                                    |                                      |            |      |         |      |        |

| Input Voltage Range (differential)              |                                      | IV         | ±0.6 | ±1.0    | ±1.7 | V      |

| Common Mode Input Voltage                       |                                      | IV         | 1.2  | 1.65    | 1.9  | V      |

| Input Capacitance                               |                                      | V          |      | 1.4     |      | pF     |

| Input Bandwidth (large signal)                  |                                      | V          |      | 120     |      | MHz    |

| Offset (mid-scale)                              | $V_{IN+} = V_{IN-} = V_{CM}$         | V          |      | ±1.0    |      | %FSR   |

| Gain Error                                      |                                      | V          |      | 0.3     |      | %FSR   |

| Reference Voltages                              |                                      |            |      |         |      |        |

| Reference Input Voltage Range                   | V <sub>REF+</sub> – V <sub>REF</sub> | IV         | 0.6  | 1.0     | 1.7  | V      |

| Negative Reference Voltage (V <sub>REF</sub> _) |                                      | IV         | 0.9  | 1.0     | 1.3  | V      |

| Positive Reference Voltage (V <sub>REF+</sub> ) |                                      | IV         | 1.9  | 2.0     | 2.9  | V      |

| Common Mode Output Voltage (V <sub>CM</sub> )   | $I_O = -1\mu A$                      | VI         | 1.3  | 1.65    | 1.8  | V      |

| V <sub>REF+</sub> Current                       |                                      | V          |      | 35      |      | μΑ     |

| V <sub>REF</sub> _ Current                      |                                      | V          |      | -25     |      | μΑ     |

| Switching Performance                           |                                      |            |      |         |      |        |

| Maximum Conversion Rate                         |                                      | VI         | 20   |         |      | MHz    |

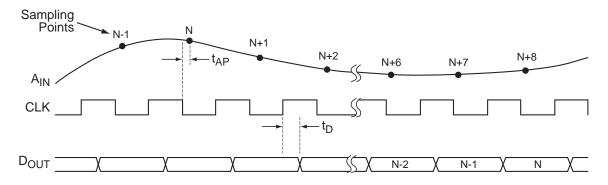

| Pipeline Delay (see Figure 1)                   |                                      | IV         |      | 7.5     |      | CLK    |

| Aperture Delay Time (T <sub>AP</sub> )          |                                      | V          |      | 5       |      | ns     |

| Aperture Jitter Time                            |                                      | V          |      | 10      |      | ps-rms |

| Dynamic Performance                             |                                      |            |      |         |      |        |

| Signal-To-Noise Ratio                           | $f_{IN} = 5MHz$                      | VI         | 57   | 58      |      | dB     |

|                                                 | $f_{IN} = 10MHz$                     | V          |      | 58      |      | dB     |

| Effective Number of Bits                        | $f_{IN} = 5MHz$                      | VI         | 9.0  | 9.3     |      | Bits   |

|                                                 | $f_{IN} = 10MHz$                     | V          |      | 9.0     |      | Bits   |

| Total Harmonic Distortion                       | $f_{IN} = 5MHz$                      | VI         |      | -68     | -61  | dB     |

|                                                 | $f_{IN} = 10MHz$                     | V          |      | -60     |      | dB     |

| Signal-To-Noise and Distortion                  | $f_{IN} = 5MHz$                      | VI         | 56   | 58      |      | dB     |

|                                                 | $f_{IN} = 10MHz$                     | V          |      | 56      |      | dB     |

| Spurious Free Dynamic Range                     | $f_{IN} = 5MHz$                      | VI         | 62   | 70      |      | dB     |

|                                                 | $f_{IN} = 10MHz$                     | V          |      | 61      |      | dB     |

| Differential Phase                              |                                      | V          |      | 0.2     |      | deg    |

| Differential Gain                               |                                      | V          |      | 0.5     |      | %      |

#### **Electrical Specifications**

$(T_A = T_{MIN} - T_{MAX}, V_{DD1} = V_{DD2} = V_{DD3} = 3.3V, V_{REF-} = 1.0V, V_{REF+} = 2.0V, Common Mode Voltage = 1.65V, <math>f_{CLK} = 20$  MSPS, Bias1 =  $90\mu$ A, Bias2 =  $9.5\mu$ A, Differential Input, Duty Cycle = 50%; unless otherwise noted)

| Parameter                                                                | Conditions            | Test Level | Min                    | Тур                    | Max                    | Units |

|--------------------------------------------------------------------------|-----------------------|------------|------------------------|------------------------|------------------------|-------|

| Digital Inputs                                                           |                       |            |                        |                        |                        |       |

| Logic 1 Voltage                                                          |                       | VI         | 80%<br>V <sub>DD</sub> |                        |                        |       |

| Logic 0 Voltage                                                          |                       | VI         |                        |                        | 20%<br>V <sub>DD</sub> |       |

| Maximum Input Current Low                                                | V <sub>IN</sub> = GND | VI         |                        |                        | ±1                     | μΑ    |

| Maximum Input Current High                                               | $V_{IN} = V_{DD}$     | VI         |                        |                        | ±1                     | μΑ    |

| Input Capacitance                                                        |                       | V          |                        | 1.8                    |                        | pF    |

| Digital Outputs                                                          |                       |            |                        |                        |                        |       |

| Logic 1 Voltage                                                          | I <sub>O</sub> = -2mA | VI         | 85%<br>V <sub>DD</sub> | 90%<br>V <sub>DD</sub> |                        | V     |

| Logic 0 Voltage                                                          | I <sub>O</sub> = +2mA | VI         |                        | 0.1                    | 0.4                    | V     |

| CLK to Output Delay Time (t <sub>D</sub> )                               |                       | IV         | 4                      | 8                      | 12                     | ns    |

| Power Supply Requirements                                                |                       |            |                        |                        |                        |       |

| Supply Voltage (V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DD3</sub> ) |                       | IV         | 2.8                    | 3.3                    | 3.6                    | V     |

| Supply Current (I <sub>DD</sub> )                                        |                       | VI         |                        | 24                     | 30                     | mA    |

| Power Dissipation                                                        |                       | VI         |                        | 79                     | 100                    | mW    |

| Power Supply Rejection Ratio                                             |                       | V          |                        | 67                     |                        | dB    |

#### **TEST LEVEL CODES**

All electrical characteristics are subject to the following conditions:

All parameters having min/max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection.

#### LEVEL TEST PROCEDURE

- IV Parameter is guaranteed (but not tested) by design or characterization data.

- V Parameter is a typical value for information purposes only.

- VI 100% production tested at  $T_A = +25$ °C. Parameter is guaranteed over specified temperature range.

## Absolute Maximum Ratings (beyond which the device may be damaged)

| Parameter                                   | Min  | Max                  | Units |

|---------------------------------------------|------|----------------------|-------|

| Supply Voltages                             |      |                      |       |

| $V_{DD1}, V_{DD2}, V_{DD3}$                 | -0.5 | +6                   | V     |

| Input Voltages                              |      |                      |       |

| Analog and Digital Input                    | -0.5 | V <sub>DD</sub> +0.5 | V     |

| V <sub>REF+</sub> , V <sub>REF-</sub> , CLK | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Operating Temperature Range                 | -40  | +85                  | °C    |

| Storage Temperature Range                   | -65  | +125                 | °C    |

#### Note:

Operation at any Absolute Maximum Rating is not implied.

See Electrical Specifications for proper nominal applied conditions in typical applications.

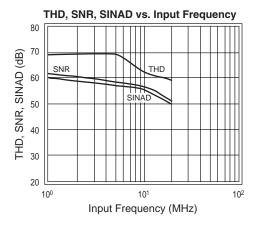

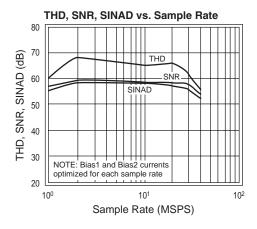

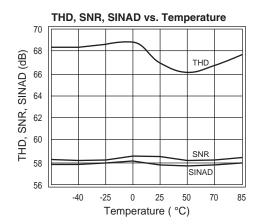

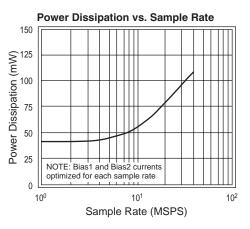

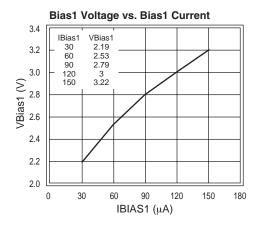

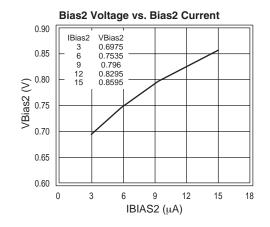

#### **Typical Performance Characteristics**

$(T_A = T_{MIN} - T_{MAX}, V_{DD1} = V_{DD2} = V_{DD3} = 3.3V, V_{REF-} = 1.0V, V_{REF+} = 2.0V, Common Mode Voltage = 1.65, <math>f_{CLK} = 20$  MSPS, Bias1 =  $90\mu$ A, Bias2 =  $9.5\mu$ A, Differential Input, Duty Cycle = 50%; unless otherwise noted)

Figure 1: Timing Diagram

# **General Description**

The SPT7851 is an ultra-low power, 10-bit, 20 MSPS ADC. It has a pipelined architecture and incorporates digital error correction of all 10 bits. This error correction ensures good linearity performance for input frequencies up to Nyquist. The inputs are fully differential, making the device insensitive to system-level noise. This device can also be used in a single-ended mode. (See analog input section.) With the power dissipation roughly proportional to the sampling rate, this device is ideal for very low power applications in the range of 1 to 20 MSPS.

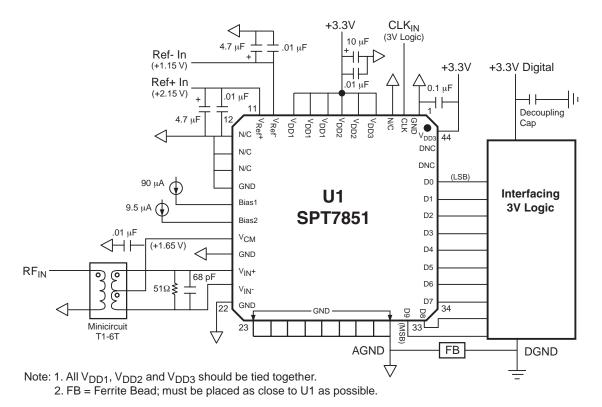

## **Typical Interface Circuit**

The SPT7851 requires few external components to achieve the stated operation and performance. Figure 2 shows the typical interface requirements when using the SPT7851 in normal circuit operation. The following sections provide a description of the functions and outline critical performance criteria to consider for achieving the optimal device performance.

Figure 2: Typical Interface Circuit

REV. 1B October 2003 5

#### **Analog Input**

The input of the SPT7851 can be configured in various ways depending on if a single-ended or differential, AC- or DC-coupled input is desired.

The AC coupled input is most conveniently implemented using a transformer with a center tapped secondary winding. The center tap is connected to the  $V_{CM}$  pin as shown in Figure 2. To obtain low distortion, it is important that the selected transformer does not exhibit core saturation at the full-scale voltage. Proper termination of the input is important for input signal purity. A small capacitor across the inputs attenuates kickback noise from the internal sample and hold.

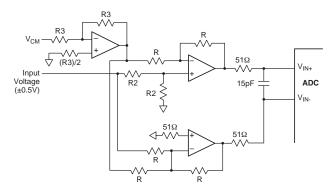

Figure 3 illustrates a solution (based on operational amplifiers) that can be used if a a DC-coupled single-ended input is desired. The selection criteria of the buffer op-amps is as follows:

- Open loop gain > 75dB

- Gain bandwidth product > 50MHz

- Total Harmonic Distortion ≤ -75dB

- Signal-to-Noise Ratio > 75dB

Figure 3: DC-coupled single-ended to differential conversion (power supplies/bypassing not shown)

## **Power Supplies and Grounding**

The SPT7851 is operated from a single power supply in the range of 2.8 to 3.6 volts. Nominal operation is suggested to be 3.3 volts. All power supply pins should be bypassed as close to the package as possible. The analog and digital grounds should be connected together with a ferrite bead as shown in the typical interface circuit and as close to the ADC as possible.

#### References

The SPT7851 has a differential analog input. The voltages applied to the VREF+ and VREF- pins determine the input voltage range and are equal to  $\pm$ (VREF+ – VREF-). This voltage range will be symmetrical about the common mode voltage. Externally generated reference voltages must be connected to these pins. (See figure 2, Typical Interface Circuit.) For best performance, these voltages should be symmetrical about the midpoint of the supply voltage. Common Mode Voltage

#### **Reference Circuit**

The SPT7851 has an on-board common mode voltage reference circuit (VCM). It is typically one-half of the supply voltage and can drive loads of up to 20  $\mu$ A. This circuit is commonly used to drive the center tap of the RF transformer in fully differential applications. For single-ended applications, this output can be used to provide the level shifting required for the single-to-differential converter conversion circuit.

#### **Bias Current Circuits**

The bias currents suggested (Bias 1 and Bias 2 in figure 2) optimize device performance for the stated sample rate of 20 MSPS. To achieve the best dynamic performance when operating the device at sample rates other than 20 MSPS, the bias current levels should be adjusted. Table I shows the settings for Bias 1 and Bias 2 for selected sample rates. The "Bias Voltage vs Bias Current" graphs on page 4 show the relationship between the bias current and the bias voltage. Please refer to the application note for more information.

Table I - Sample Rate Settings

| Sample Rate (MHz) | Bias1 (μA) | Bias2 (μA) |

|-------------------|------------|------------|

| 1                 | 30         | 3.0        |

| 5                 | 50         | 6.0        |

| 10                | 70         | 7.5        |

| 20                | 90         | 9.5        |

#### Clock

The SPT7851 accepts a low voltage CMOS logic level at the CLK input. The duty cycle of the clock should be kept as close to 50% as possible. Because consecutive stages in the ADC are clocked in opposite phase to each other, a non-50% duty cycle reduces the settling time available for every other stage and thus could potentially cause a degradation of dynamic performance.

For optimal performance at high input frequencies, the clock should have low jitter and fast edges. The rise/fall times should be kept shorter than 2ns. Overshoot and undershoot should be avoided. Clock jitter causes the noise floor to rise proportional to the input frequency. Because jitter can be caused by crosstalk on the PC board, it is recommended that the clock trace be kept as short as possible and standard transmission line practices be followed.

## **Digital Outputs**

The digital output data appears in an offset binary code at 3.3V CMOS logic levels. A negative full scale input results

in an all zeros output code (000...0). A positive full scale input results in an all 1's code (111...1). The output data is available 7.5 clock cycles after the data is sampled. The input signal is sampled on the high to low transition of the input clock. Output data should be latched on the low to high clock transition as shown in figure 1, the Timing Diagram. The output data is invalid for the first 20 clock cycles after the device is powered up.

#### **Evaluation Board**

The EB7851 Evaluation Board is available to aid designers in demonstrating the full performance capability of the SPT7851. The board includes an on-board clock driver, adjustable voltage references, adjustable bias current circuits, single-to-differential input buffers with adjustable levels, a single-to-differential transformer (1:1), digital output buffers and 3.3/5 V adjustable logic outputs. An application note (AN7851) is also available which describes the operation of the evaluation board and provides an example of the recommended power and ground layout and signal routing. Contact the factory for price and availability.

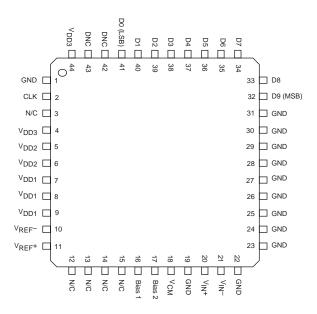

## **Pin Configuration**

#### **Pin Assignments**

| Pin Name                                 | Description                            |  |

|------------------------------------------|----------------------------------------|--|

| V <sub>IN+</sub> , V <sub>IN-</sub>      | Analog Inputs                          |  |

| V <sub>REF+</sub> ,<br>V <sub>REF-</sub> | External Reference Inputs              |  |

| CLK                                      | Input Clock                            |  |

| V <sub>CM</sub>                          | Common Mode Output Voltage (1.65V typ) |  |

| Bias1                                    | Bias Current (90μA typ)                |  |

| Bias2                                    | Bias Current (9.5μA typ)               |  |

| D0 – D9                                  | Digital Outputs (D0 = LSB)             |  |

| GND                                      | Analog Ground                          |  |

| $V_{DD1}$                                | Analog Power Supply                    |  |

| $V_{DD2}$                                | Digital Power Supply                   |  |

| V <sub>DD3</sub>                         | Digital Output Power Supply            |  |

| N/C                                      | No connect                             |  |

| DNC                                      | Do not connect pins; leave floating    |  |

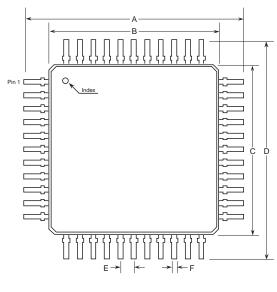

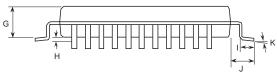

# **Package Dimensions**

#### TQFP-44

| Cymbal | Inc       | hes   | Millin    | neters |

|--------|-----------|-------|-----------|--------|

| Symbol | Min       | Max   | Min       | Max    |

| А      | 0.472 Typ |       | 12.00 Typ |        |

| В      | 0.394 Typ |       | 10.00 Typ |        |

| С      | 0.394 Typ |       | 10.00 Typ |        |

| D      | 0.472 Typ |       | 12.00 Typ |        |

| E      | 0.031 Typ |       | 0.80 Typ  |        |

| F      | 0.012     | 0.018 | 0.300     | 0.45   |

| G      | 0.053     | 0.057 | 1.35      | 1.45   |

| Н      | 0.002     | 0.006 | 0.05      | 0.15   |

| I      | 0.018     | 0.030 | 0.450     | 0.750  |

| J      | 0.039 Typ |       | 1.00 Typ  |        |

| K      | 0-7°      |       | 0-7°      |        |

# **Ordering Information**

| Model   | Part Number | Package     | Container | Pack Qty |

|---------|-------------|-------------|-----------|----------|

| SPT7851 | SPT7851SIT  | 44-pin TQFP | Tray      | -        |

Temperature range for all parts: -40°C to +85°C.

For additional information regarding our products, please visit CADEKA at: cadeka.com

CADEKA Headquarters Loveland, Colorado

T: 970.663.5452

T: 877.663.5452 (toll free)

CADEKA, the CADEKA logo design, COMLINEAR and the COMLINEAR logo design are trademarks or registered trademarks of CADEKA Microcircuits LLC. All other brand and product names may be trademarks of their respective companies.

CADEKA reserves the right to make changes to any products and services herein at any time without notice. CADEKA does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by CADEKA; nor does the purchase, lease, or use of a product or service from CADEKA convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of CADEKA or of third parties.

Copyright ©2007-2008 by CADEKA Microcircuits LLC. All rights reserved.