To all our customers

## Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI 16-BIT SINGLE-CHIP MICROCOMPUTER 7700 FAMILY / 7700 SERIES

or su

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of JAPAN and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

## Preface

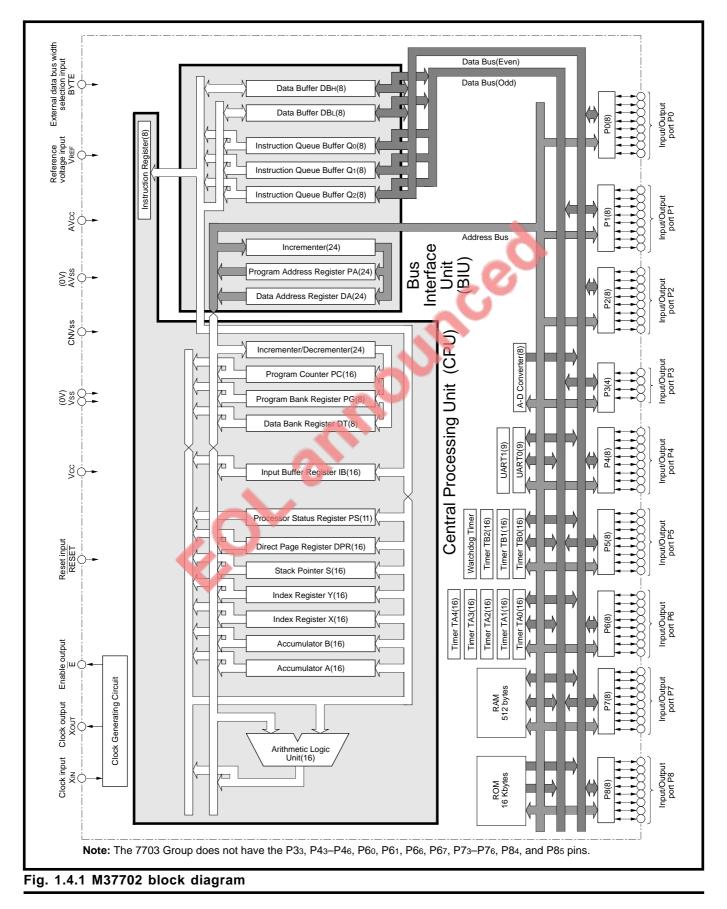

This manual describes the hardware of the Mitsubishi CMOS 16-bit microcomputers 7702 Group and 7703 Group. After reading this manual, the user will be able to understand the functions, so that they can utilize their capabilities fully.

For details concerning the software, refer to the 7700 Family Software Manual.

## **BEFORE USING THIS MANUAL**

### 1. Constitution

This user's manual consists of the following chapters. Refer to the chapters relevant to used products and the processor mode.

### •Chapter 1. DESCRIPTION to Chapter 17. APPLICATION

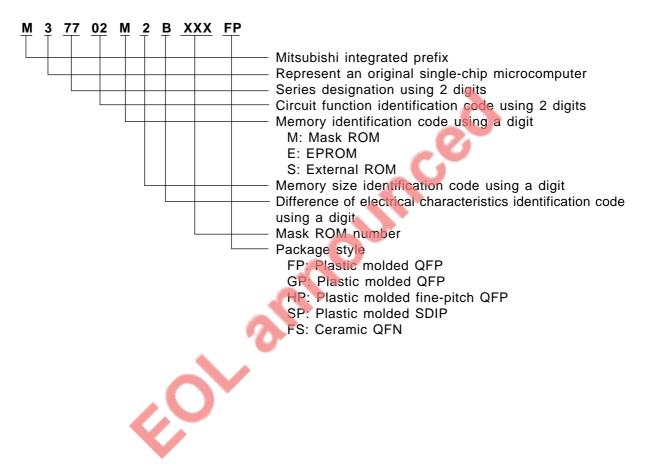

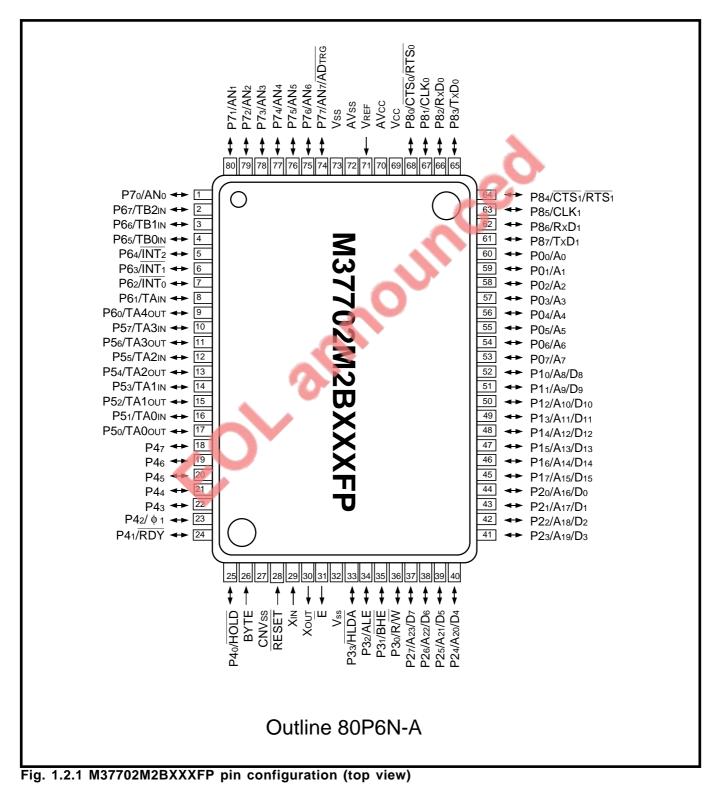

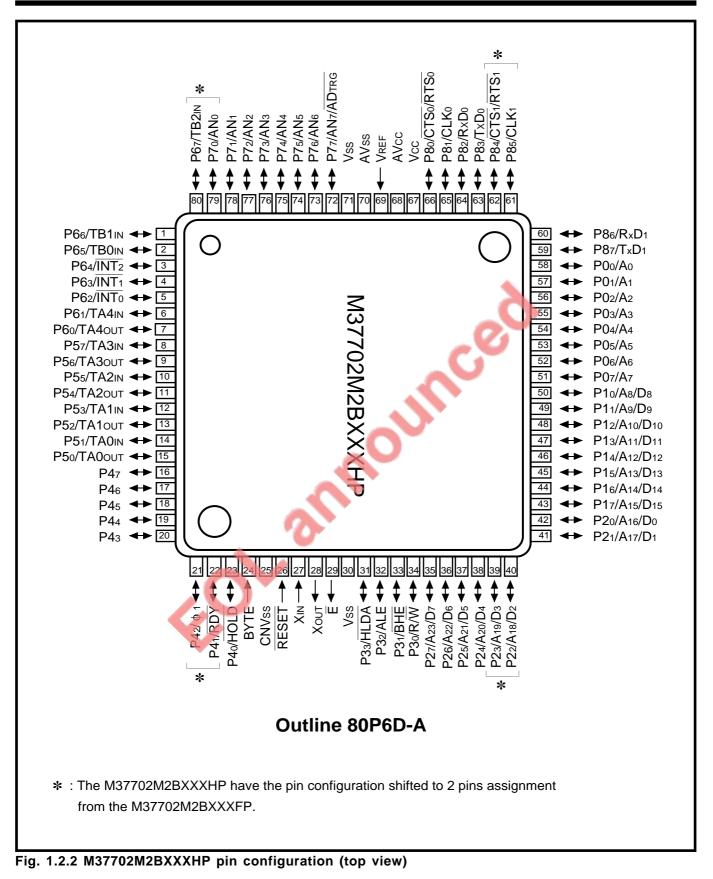

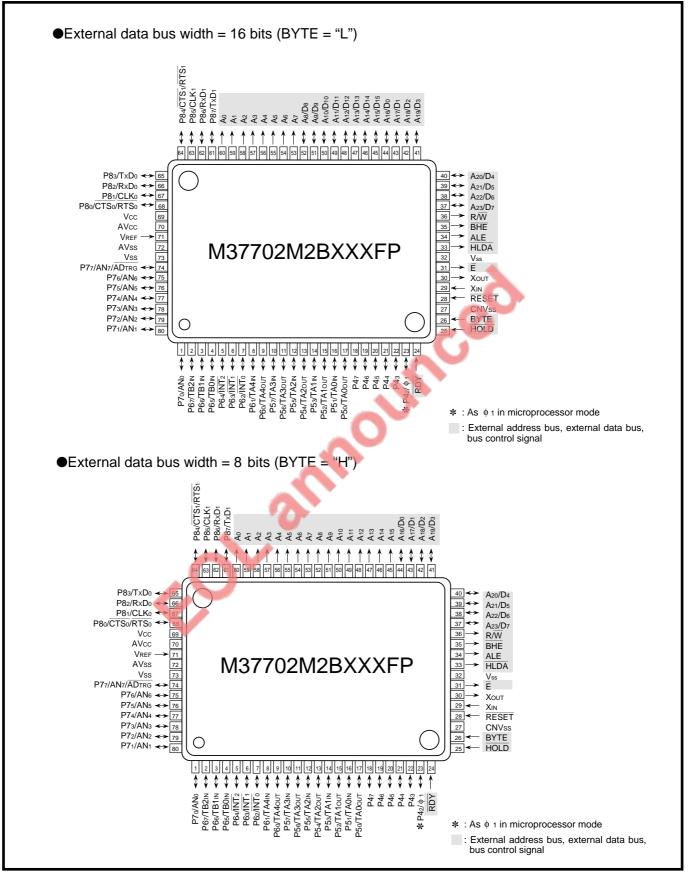

Functions which are common to all products and all processor modes are explained, using the M37702M2BXXXFP as an example.

When there are functional differences between the low voltage version, PROM version and the 7703 Group, the referential section is indicated. Refer to that section about differences and to "**Chapter. 1** to **Chapter. 17**" about the common functions.

### **•**Chapter 18. LOW VOLTAGE VERSION

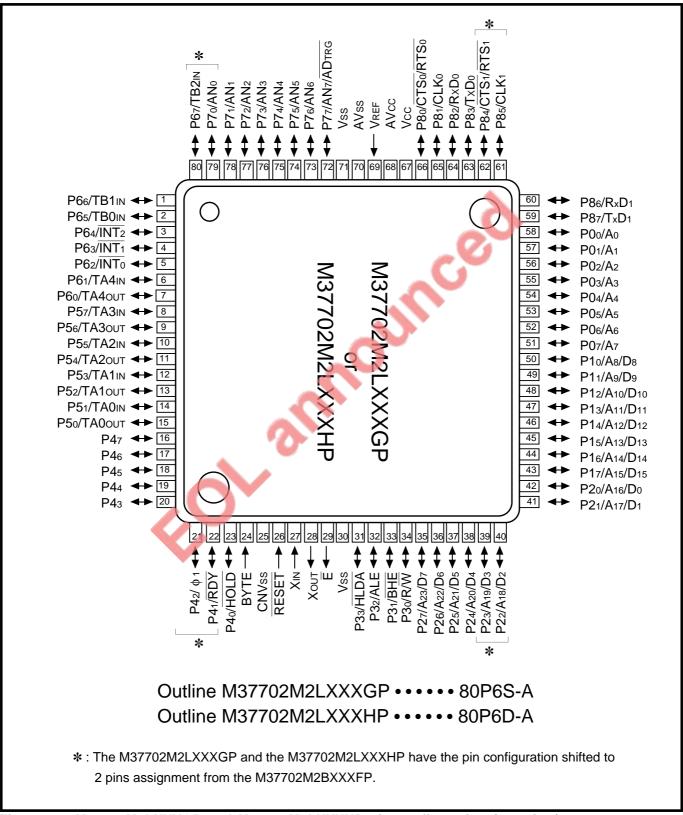

Refer to this chapter when using the products of which difference of electrical characteristics identification code (see on page 1–2) is "L," the M37702M2LXXXGP for example. This chapter mainly explains the differences from the M37702M2BXXXFP, using the M37702M2LXXXGP as an example.

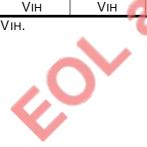

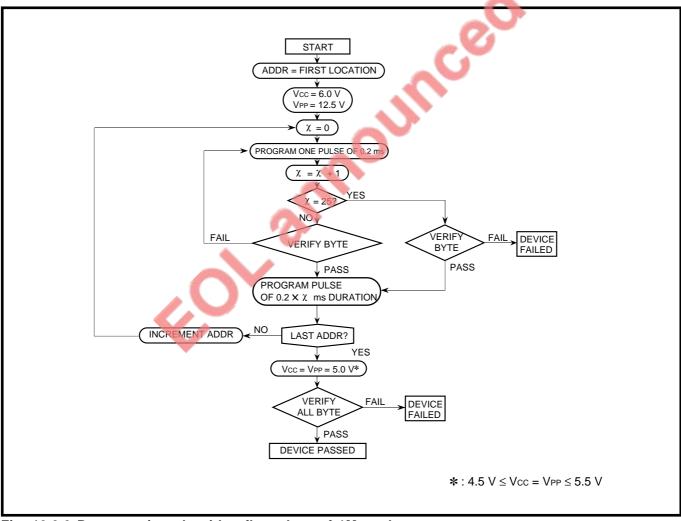

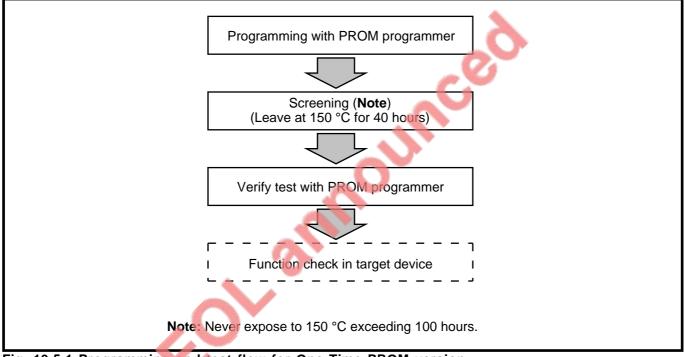

#### **•**Chapter 19. PROM VERSION

Refer to this chapter when using the products of which memory identification code (see on page 1– 2) is "E," the M37702<u>E</u>2BXXXFP for example. This chapter mainly explains the differences from the M37702M2BXXXFP, using the M37702E2BXXXFP as an example.

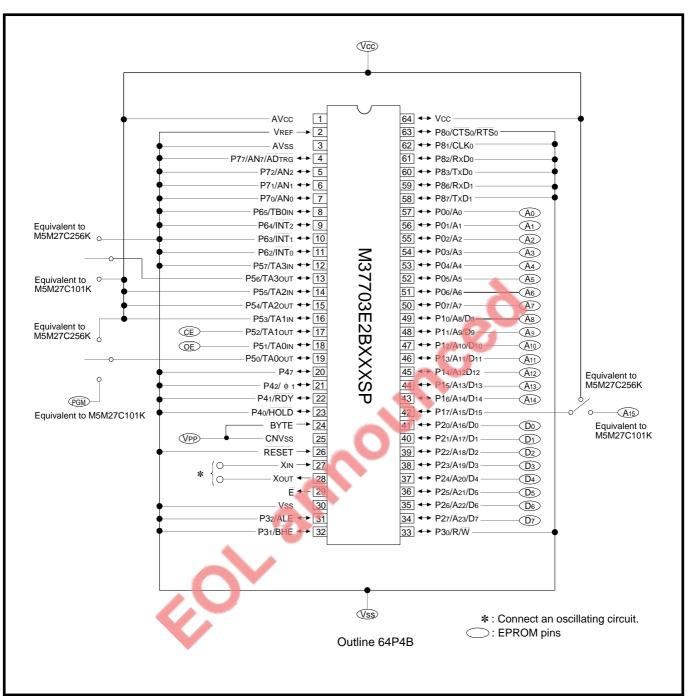

### •Chapter 20. 7703 GROUP

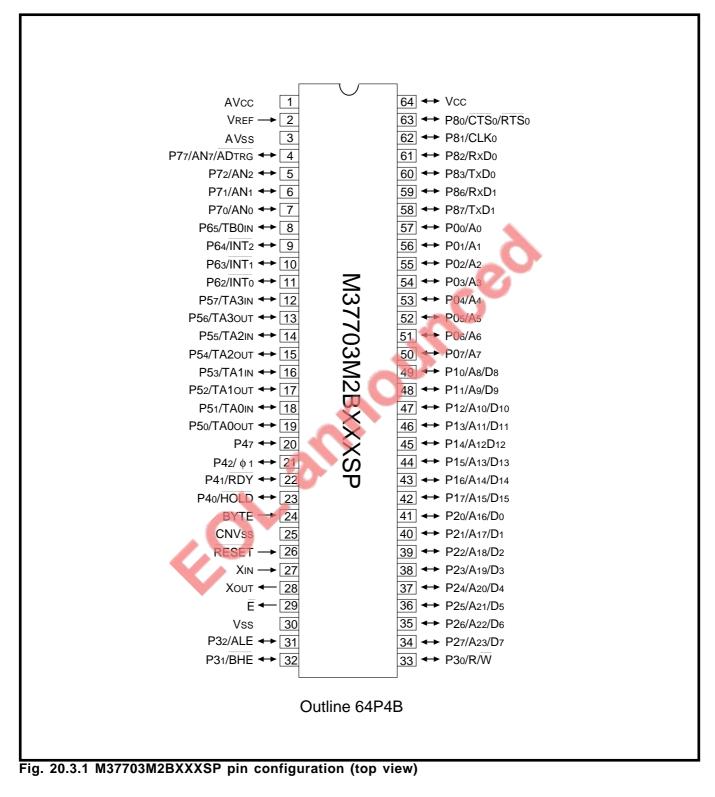

Refer to this chapter when using the 7703 Group. This chapter mainly explains the differences from the 7702 Group, using the M37703M2BXXXSP as an example.

### Appendix

Useful information for 7702 and 7703 Groups usage is shown.

### 2. Remark

#### ●25 MHz version and 16 MHz version

The 25 MHz version products are distinguished from the 16 MHz version products in part of Chapters as the case may be. Refer to it as follows:

•Products of which difference of electrical characteristics identification code is "B," M37702M2BXXXFP as an example......Column of "25 MHz version"

•Products of which difference of electrical characteristics identification code is "A," M37702M2AXXFP as an example......Column of "16 MHz version"

#### Product expansion

See the latest data book and data sheets. Additionally, ask the contact addresses on the last page.

#### •Electrical characteristics

See also the latest data book or data sheet.

#### Development support tools

See the latest data book and data sheet.

#### Software

See "7700 Family Software Manual."

### •Mask ROM Confirmation Form, PROM Confirmation Form, Mark Specification Form

Copy the form in the latest data book and use it. Or, ask the contact addresses on the last page.

### 3. Register structure

The view of the register structure is described below:

| /                       | *        | :1                                  |                                            |           |      |

|-------------------------|----------|-------------------------------------|--------------------------------------------|-----------|------|

| b7 b6 b5 b4 b3 b2 b1 b0 | XXX re   | egister (Address XX <sub>16</sub> ) | *2                                         |           | *3   |

|                         | Bit      | Bit name                            | Functions                                  | At reset  | (rw) |

|                         | 0        | select bit                          | 0 :<br>1 :                                 | 0         | RW   |

|                         | - 1      | select bit                          | 0 :<br>1 :<br>The value is "0" at reading. | Undefined | WO   |

|                         | - 2      | flag                                | 0:<br>1:                                   | 0         | RO   |

|                         | . 3      | Fix this bit to "0."                |                                            | 0         | RW   |

|                         | - 4      | This bit is ignored in mode.        |                                            | 0         | RW   |

|                         | - 7 to 5 | Nothing is assigned.                |                                            | Undefined | —    |

|                         |          |                                     |                                            |           |      |

\*1

Blank : Set to "0" or "1" to meet the purpose

- : Set to "0" at writing. : Set to "1" at writing. 0

- 1

- Х : This bit is not used in the specific mode or state. It may be either "0" or "1."

- \*4

: Nothing is assigned.

### \*2

- 0 : "0" immediately after a reset.

- : "1" immediately after a reset. 1

Undefined :Undefined immediately after a reset.

### \*3

- RW : It is possible to read the bit state at reading. The written value becomes valid data.

- RO : It is possible to read the bit state at reading. The written value becomes invalid. Accordingly, the written value may be either "0" or "1."

- : The written value becomes valid data. It is not possible to read the bit state. WO The value is undefined at reading. However, the bit with the commentaries of " The value is "0" at reading" in the functions column or the notes is always "0" at reading.(See to \*4 above.)

: It is no possible to read the bit state. The value is undefined at reading. However, the bit with the commentaries of "The value is "0" at reading" in the functions column or the notes is always "0" at reading.(See to \*4 above.) The written value becomes invalid. Accordingly, the written value may be "0" or "1."

# **Table of Contents**

| CHAPTER 1. DESCRIPTION                                                     |                                 |

|----------------------------------------------------------------------------|---------------------------------|

| <ul> <li>1.1 Performance overview</li> <li>1.2 Pin configuration</li></ul> | <b>1-4</b><br><b>1-6</b><br>1-9 |

| CHAPTER 2. CENTRAL PROCESSING UNIT (CPU)                                   |                                 |

| 2.1 Central processing unit                                                |                                 |

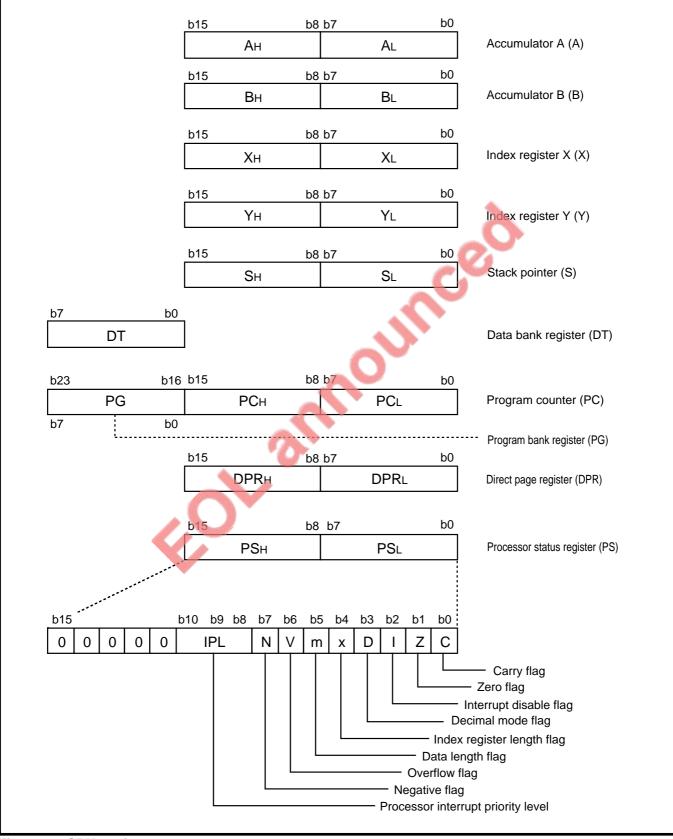

| 2.1.1 Accumulator (Acc)                                                    |                                 |

| 2.1.2 Index register X (X)                                                 |                                 |

| 2.1.3 Index register Y (Y)                                                 |                                 |

| 2.1.4 Stack pointer (S)                                                    |                                 |

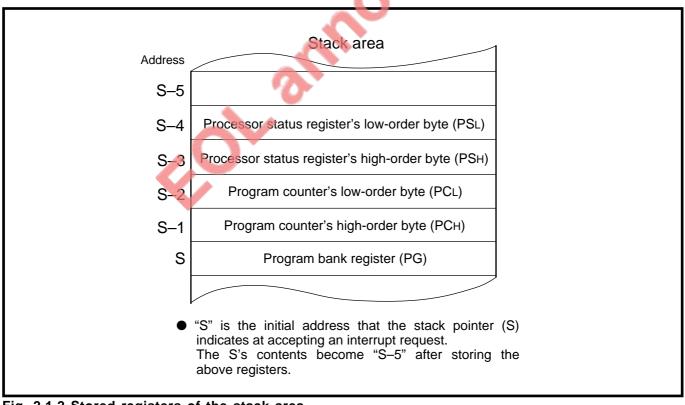

| 2.1.5 Program counter (PC)                                                 | 2-5                             |

| 2.1.6 Program bank register (PG)                                           | 2-5                             |

| 2.1.7 Data bank register (DT)                                              | 2-6                             |

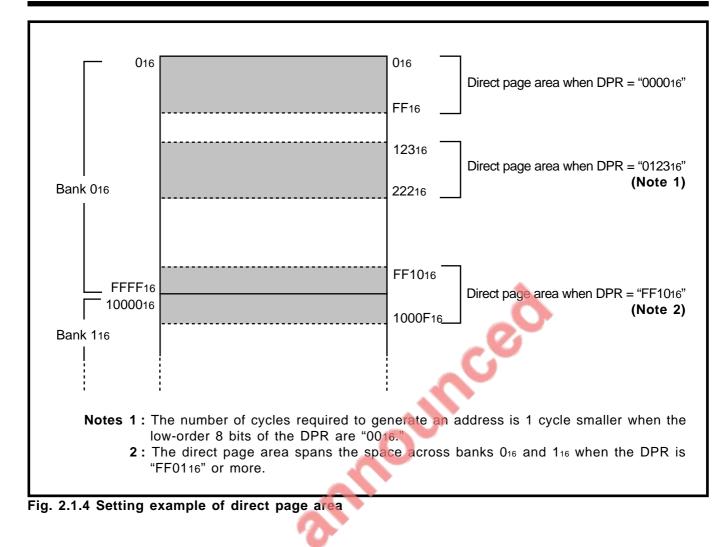

| 2.1.8 Direct page register (DPR)                                           |                                 |

| 2.1.9 Processor status register (PS)                                       |                                 |

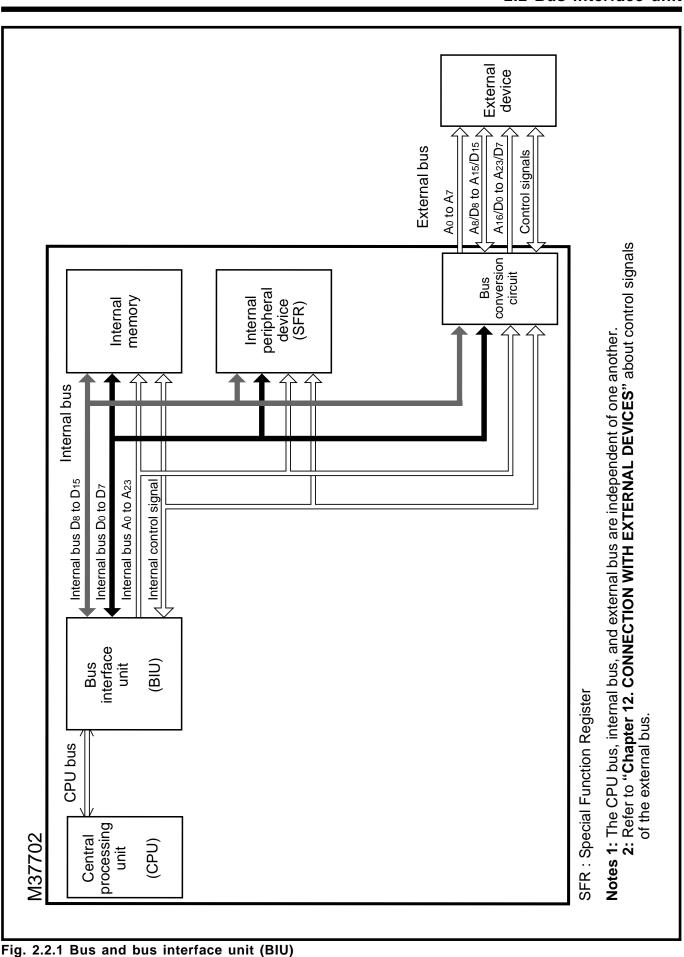

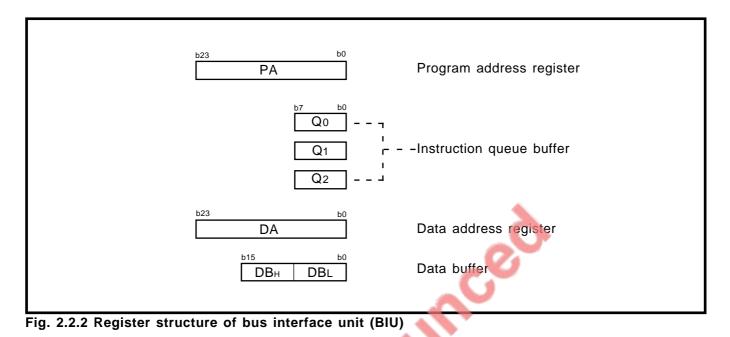

| 2.2 Bus interface unit                                                     |                                 |

| 2.2.1 Overview                                                             |                                 |

| 2.2.2 Functions of bus interface unit (BIU)                                |                                 |

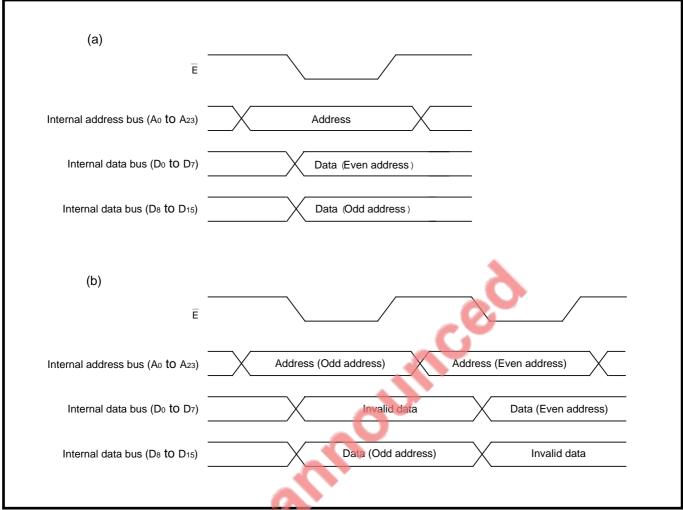

| 2.2.3 Operation of bus interface unit (BIU)                                |                                 |

| 2.3 Access space                                                           |                                 |

| 2.3.1 Banks                                                                |                                 |

| 2.3.2 Direct page                                                          |                                 |

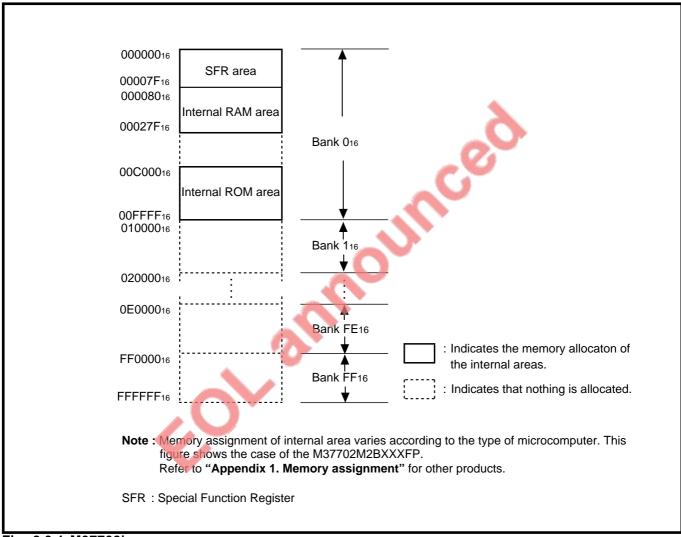

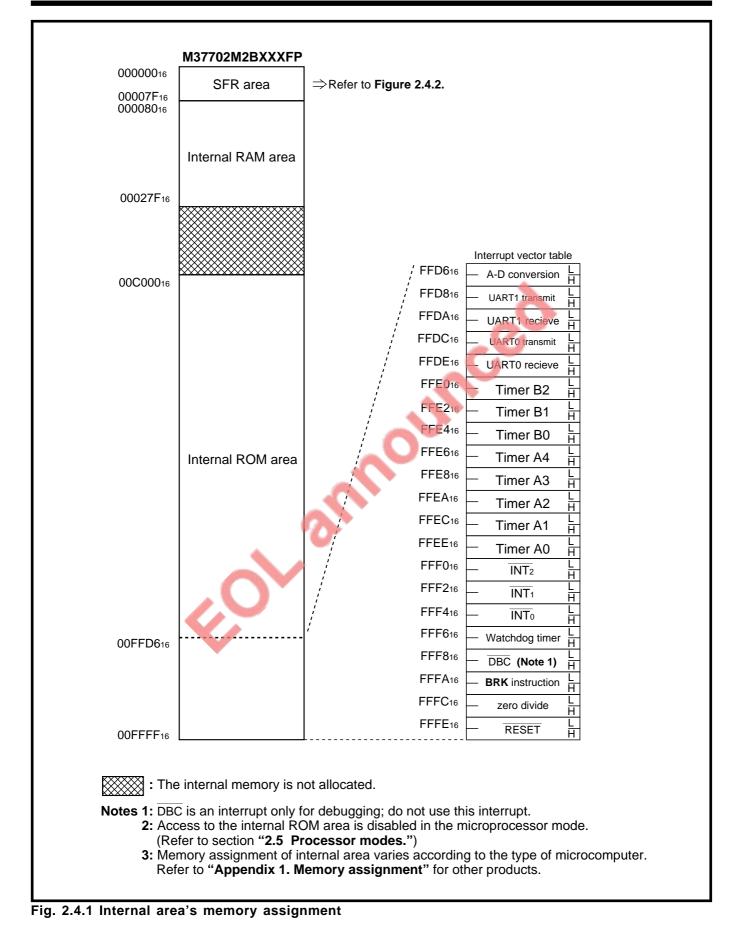

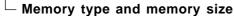

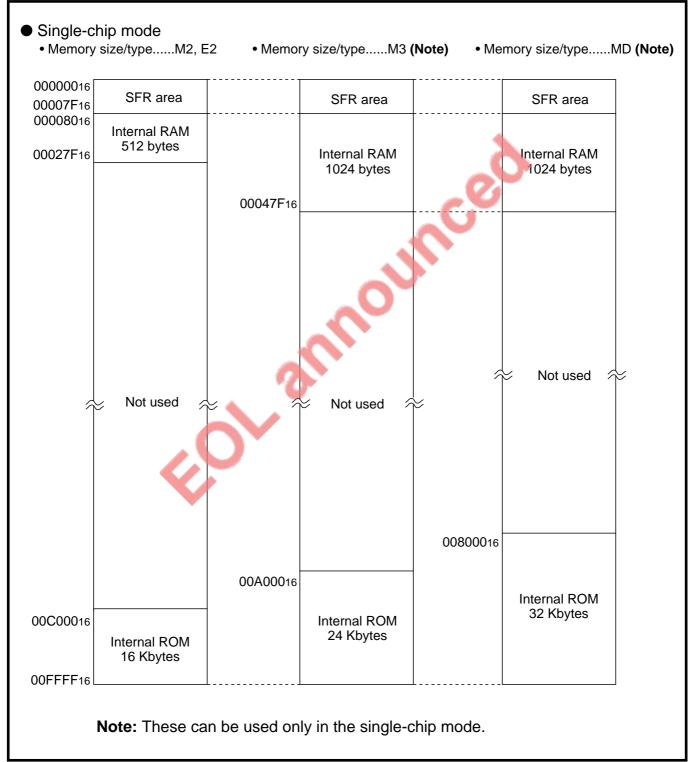

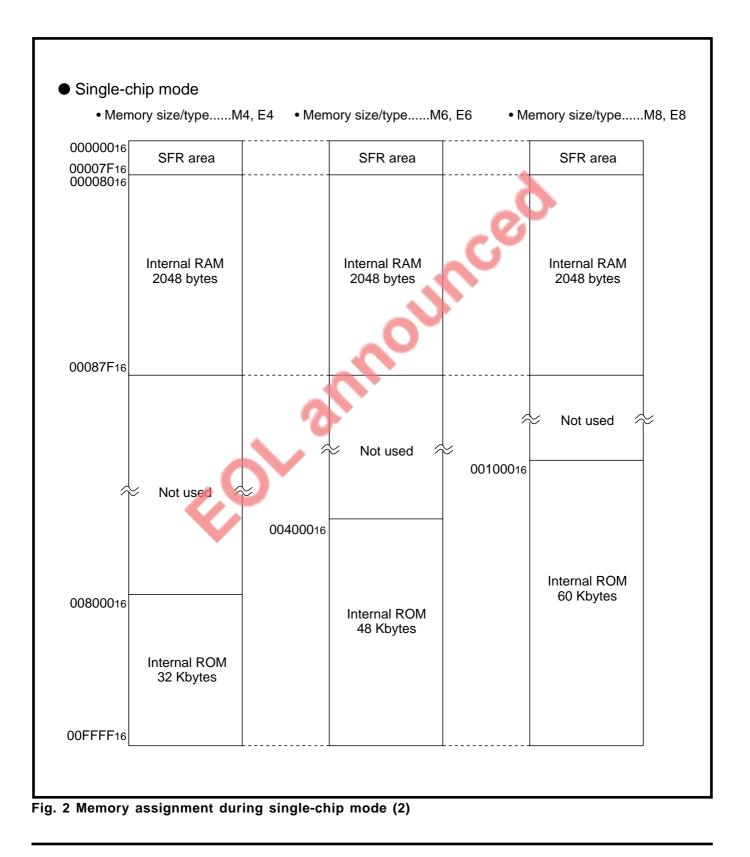

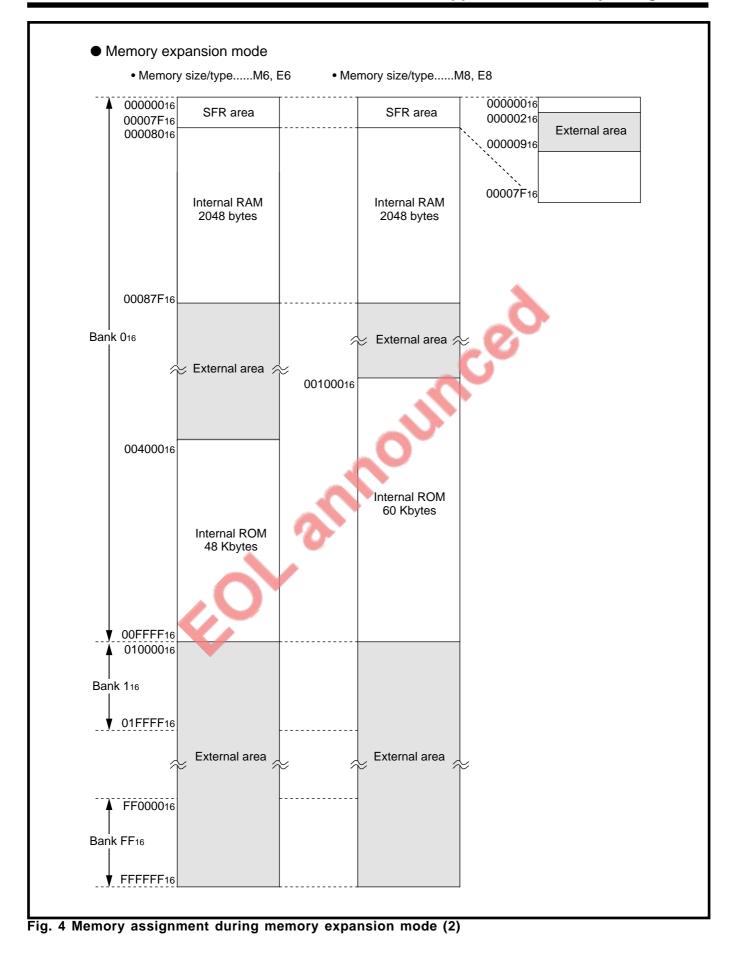

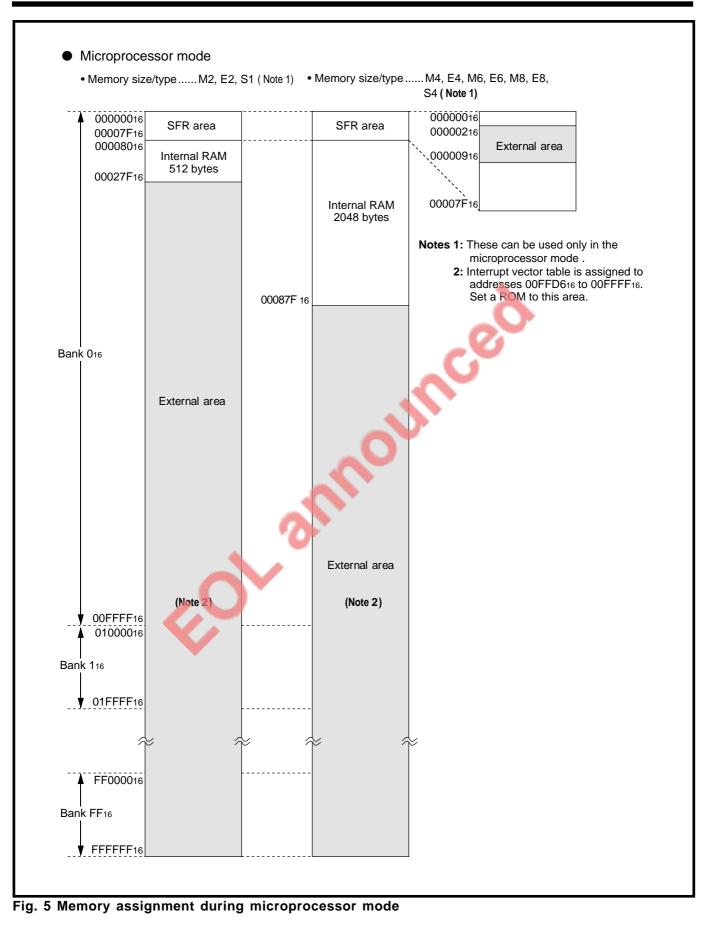

| 2.4 Memory assignment                                                      |                                 |

| 2.4.1 Memory assignment in internal area                                   |                                 |

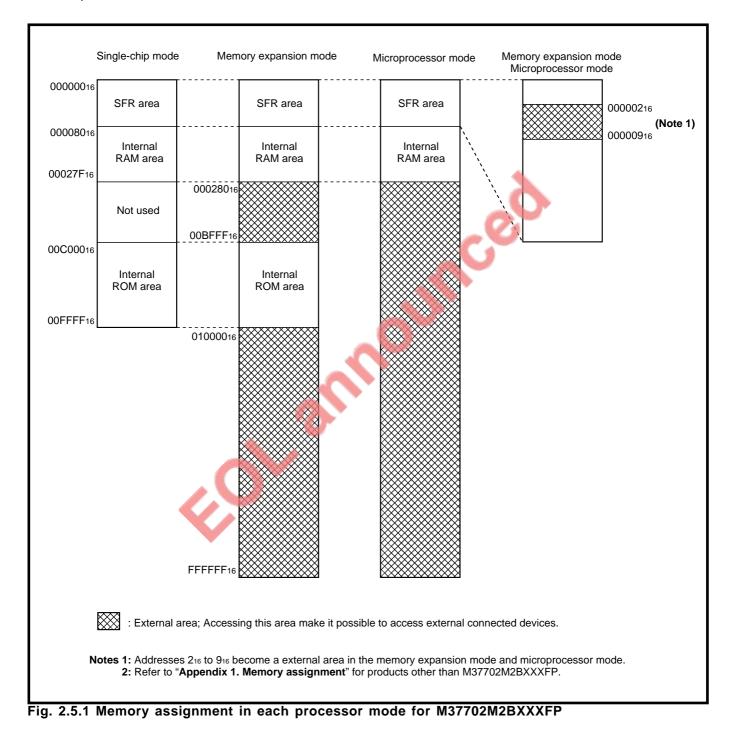

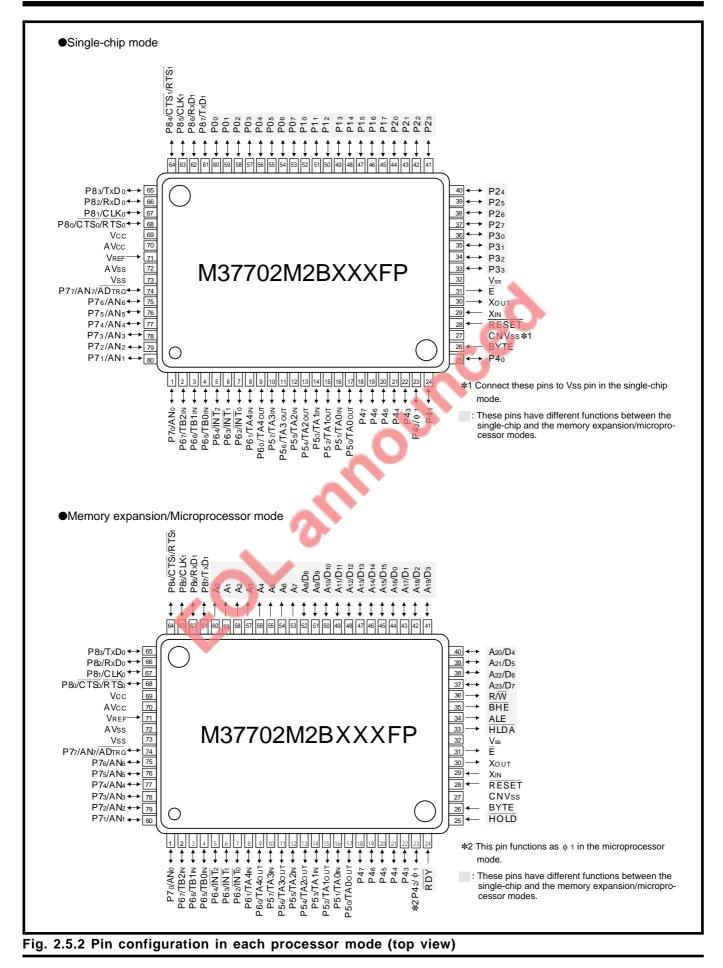

| 2.5 Processor modes                                                        |                                 |

| 2.5.1 Single-chip mode                                                     |                                 |

| 2.5.2 Memory expansion and microprocessor modes                            |                                 |

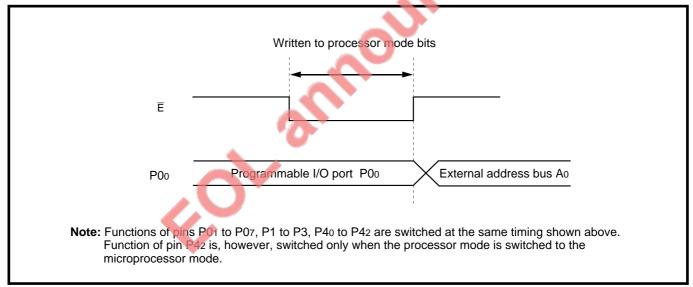

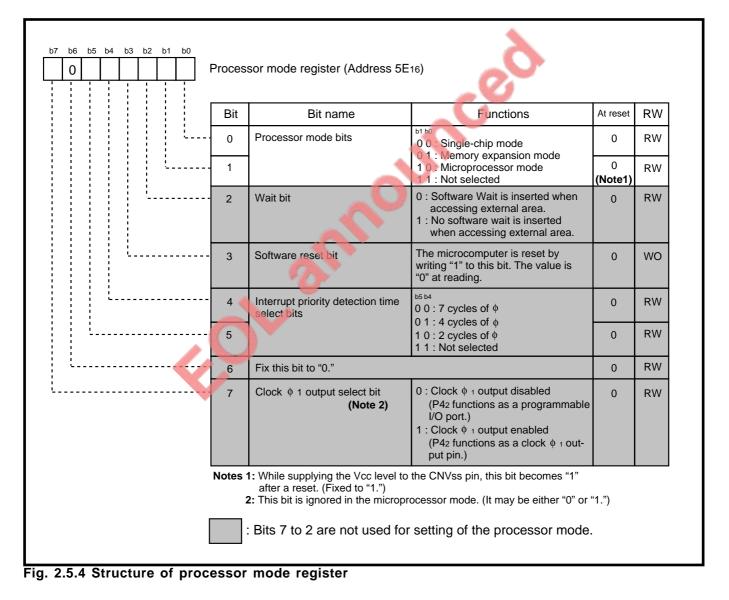

| 2.5.3 Setting processor modes                                              |                                 |

| [Precautions when selecting processor mode]                                |                                 |

| CHAPTER 3. INPUT/OUTPUT PINS                                               |                                 |

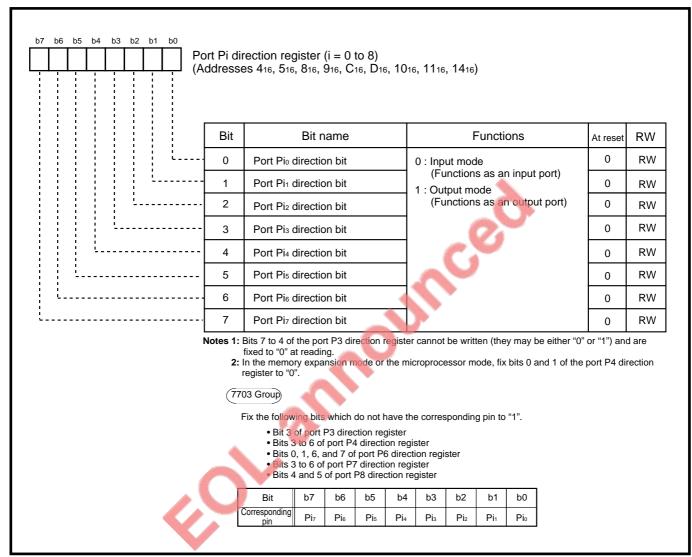

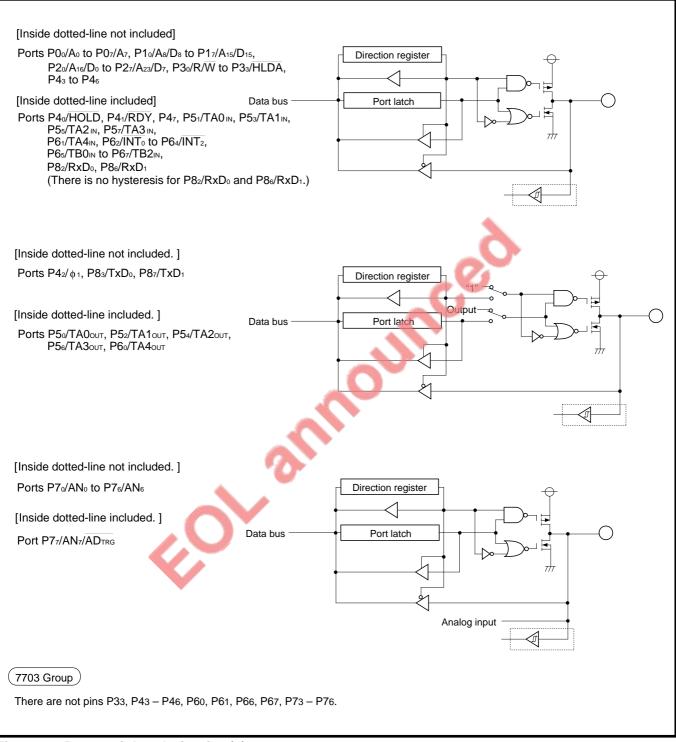

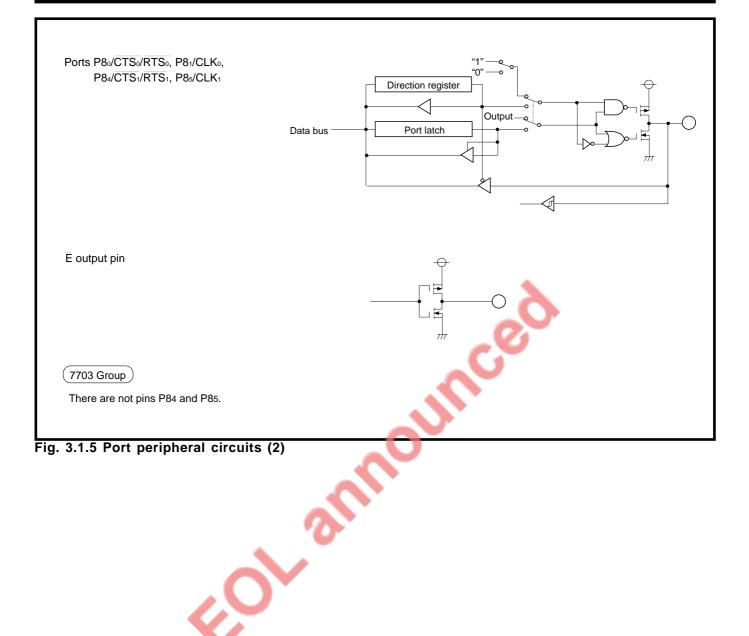

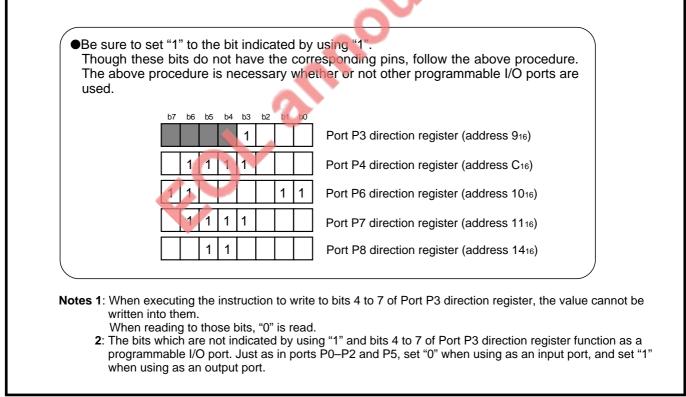

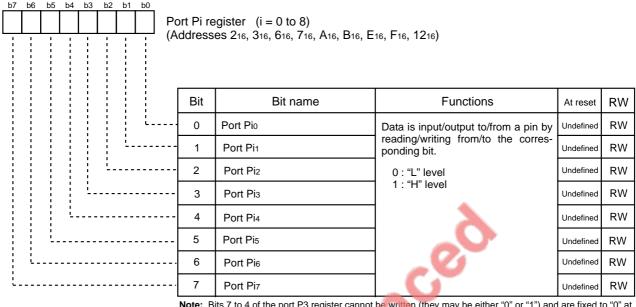

| 3.1 Programmable I/O ports                                                 |                                 |

| 3.1.1 Direction register                                                   |                                 |

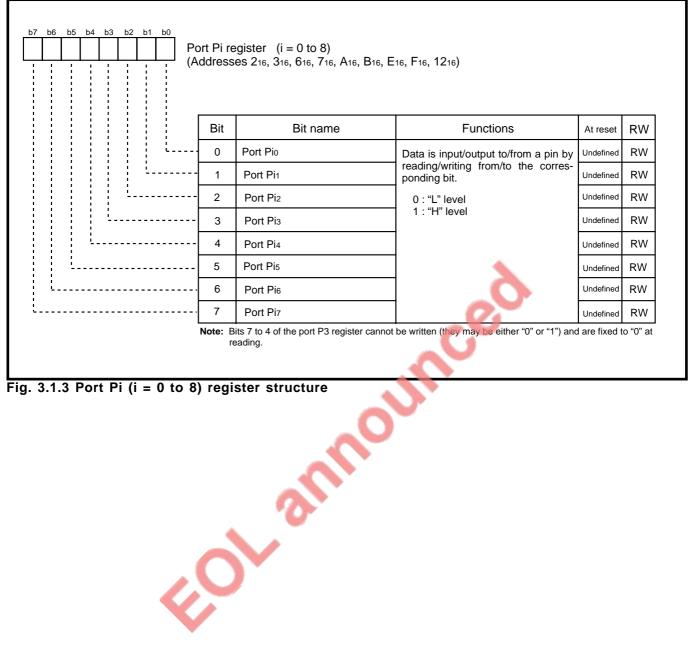

| 3.1.2 Port register                                                        |                                 |

| 3.2 I/O pins of internal peripheral devices                                |                                 |

|                                                                            |                                 |

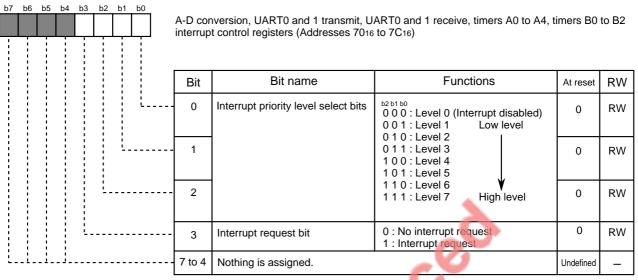

| CHAPTER 4. INTERRUPTS                                                      |                                 |

| CHAFTER 4. INTERRUFTS                                                      |                                 |

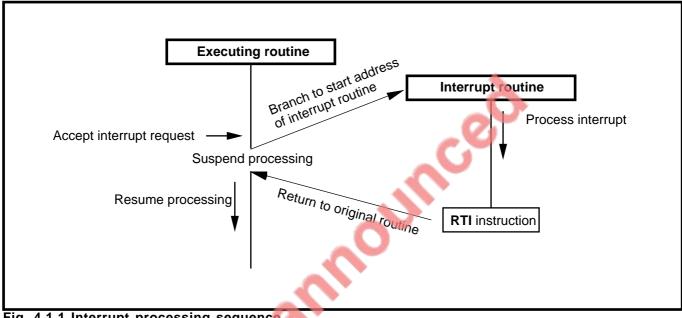

| 4.1 Overview                                                               | 4-2                             |

| 4.2 Interrupt sources                                                      |                                 |

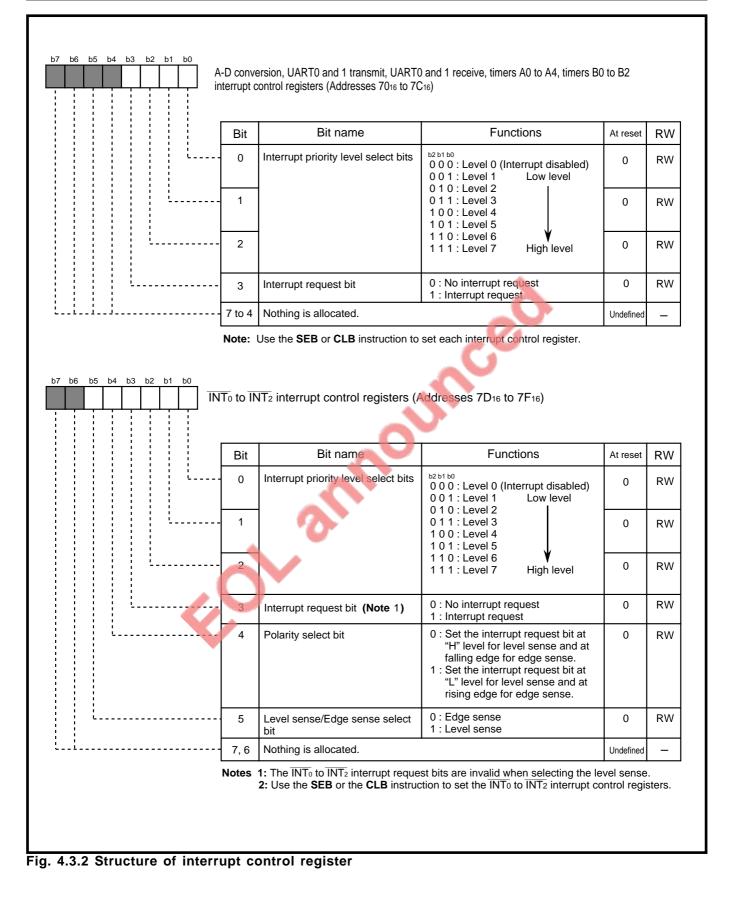

| 4.3 Interrupt control                                                                   | 4-6  |

|-----------------------------------------------------------------------------------------|------|

| 4.3.1 Interrupt disable flag (I)                                                        | 4-8  |

| 4.3.2 Interrupt request bit                                                             |      |

| 4.3.3 Interrupt priority level select bits and processor interrupt priority level (IPL) | 4-8  |

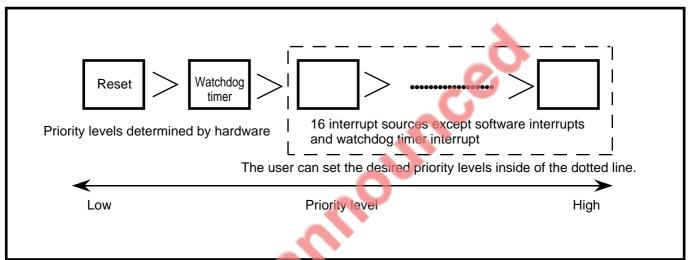

| 4.4 Interrupt priority level                                                            | 4-10 |

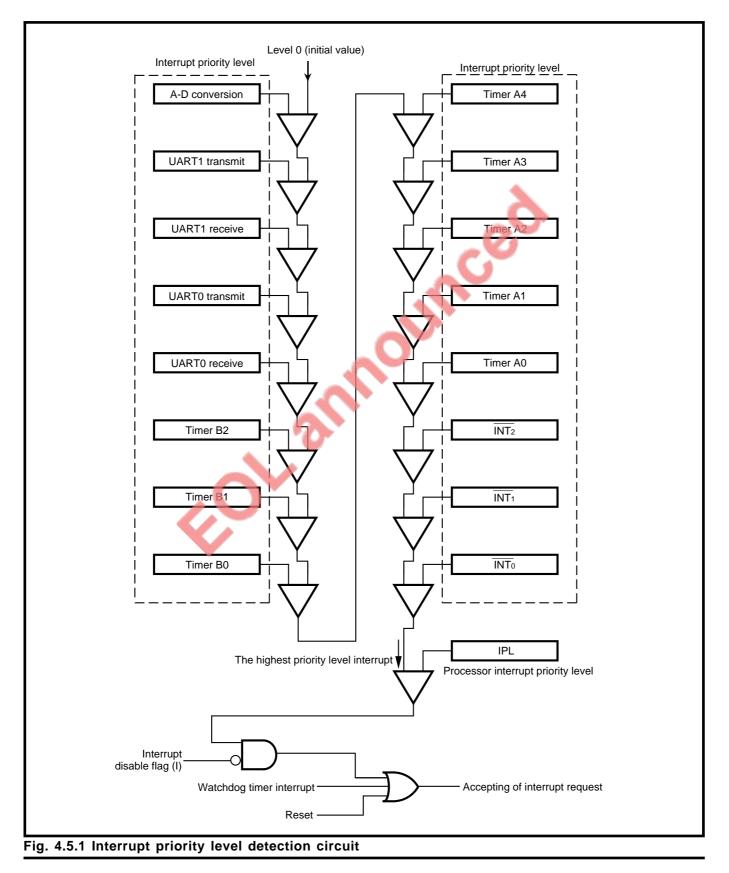

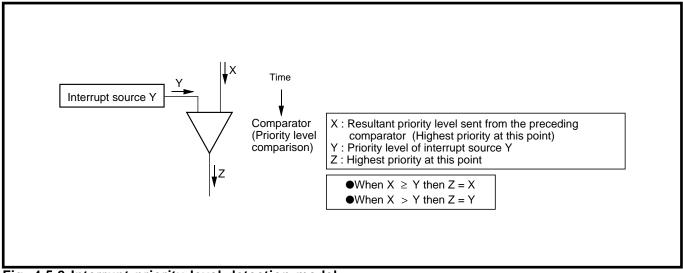

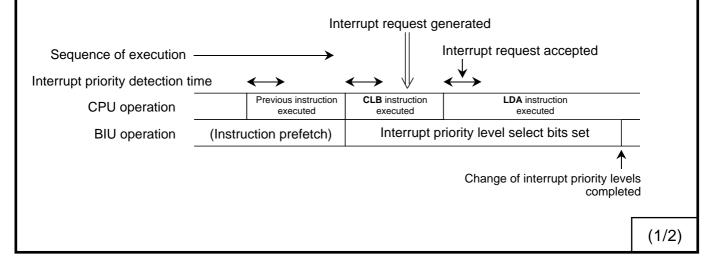

| 4.5 Interrupt priority level detection circuit                                          |      |

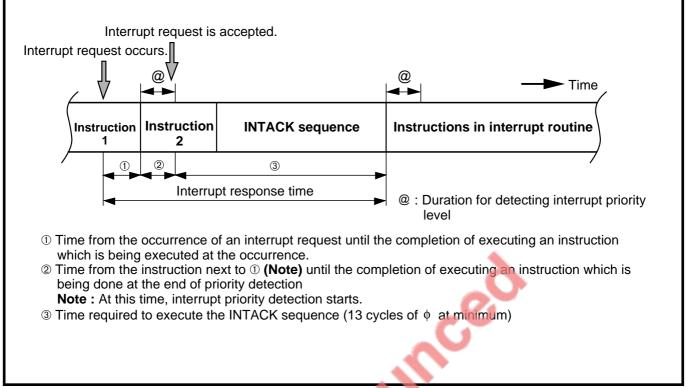

| 4.6 Interrupt priority level detection time                                             |      |

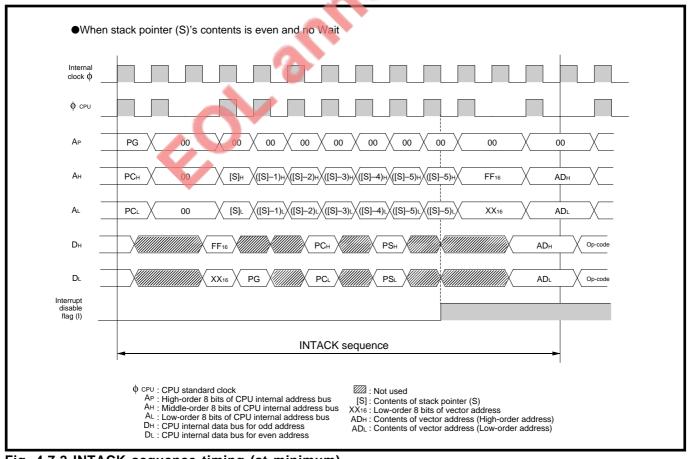

| 4.7 Sequence from acceptance of interrupt request to execution of interrupt routine     | 4-14 |

| 4.7.1 Change in IPL at acceptance of interrupt request                                  |      |

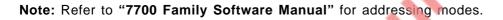

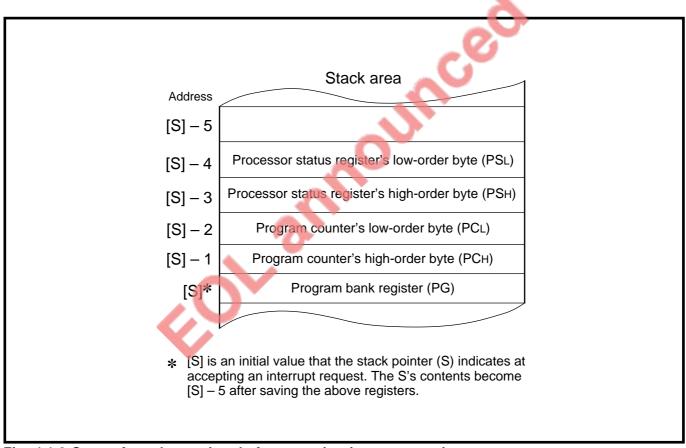

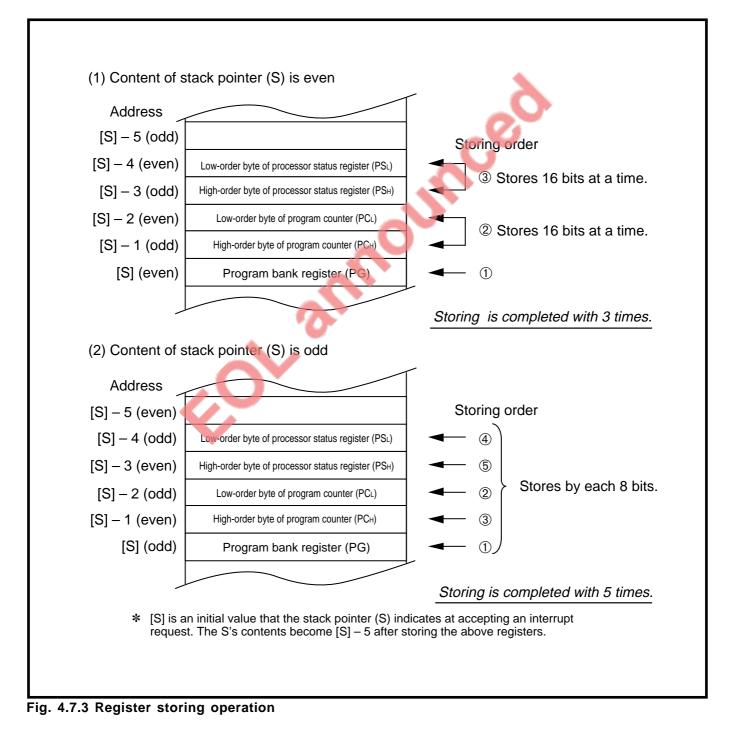

| 4.7.2 Storing registers                                                                 | 4-17 |

| 4.8 Return from interrupt routine                                                       | 4-18 |

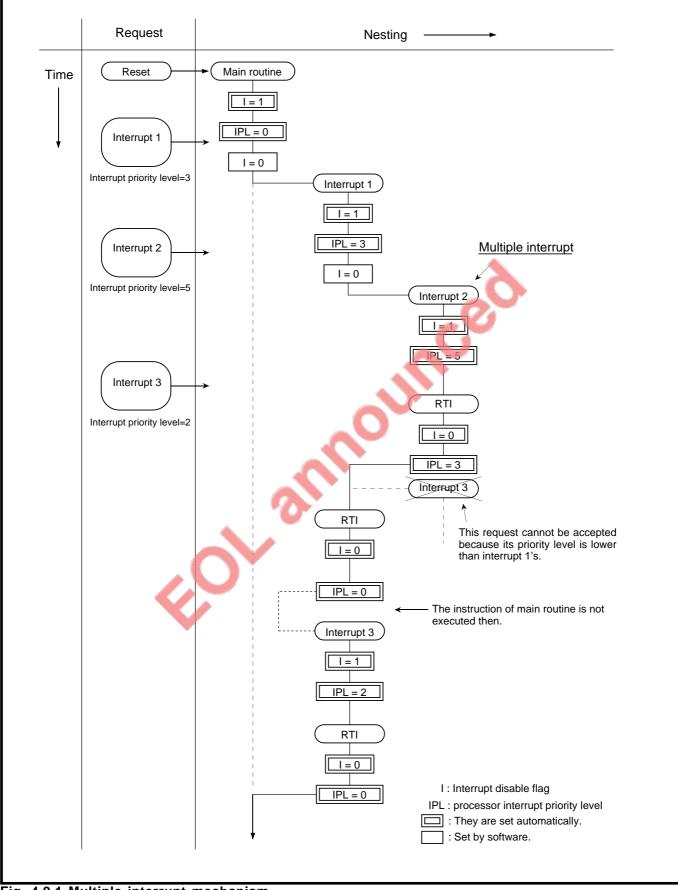

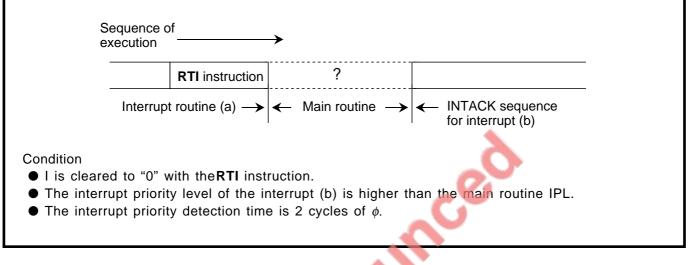

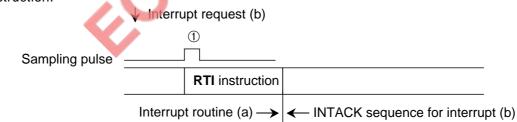

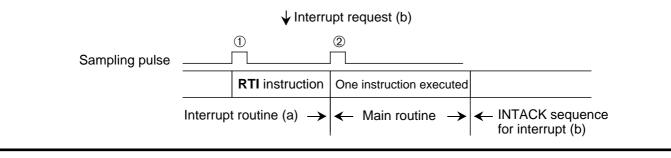

| 4.9 Multiple interrupts                                                                 | 4-18 |

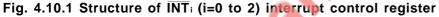

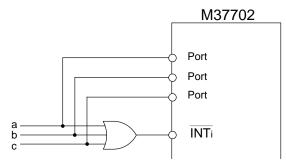

| 4.10 External interrupts (INT; interrupt)                                               |      |

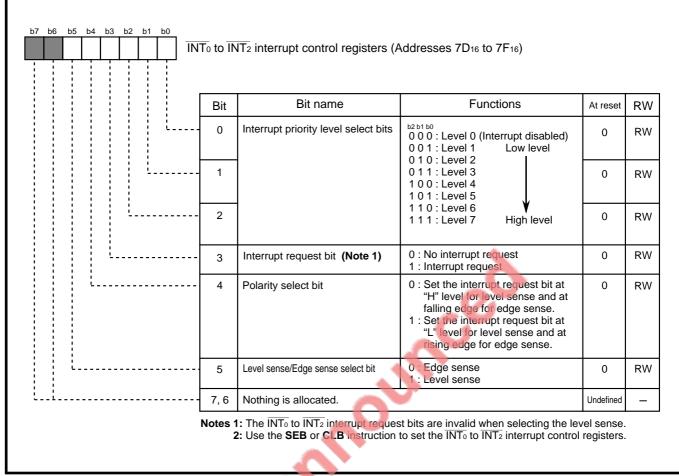

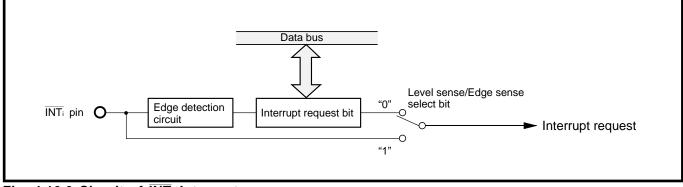

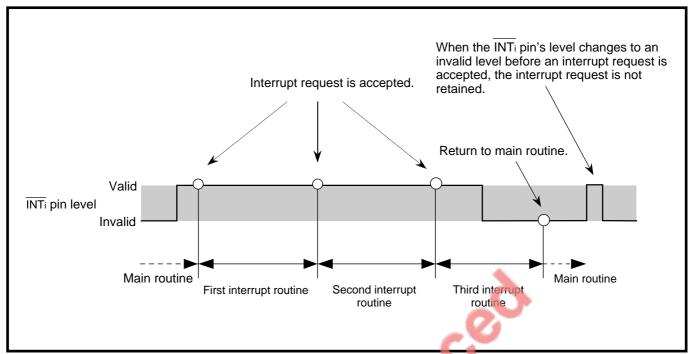

| 4.10.1 Function of INT interrupt request bit                                            | 4-23 |

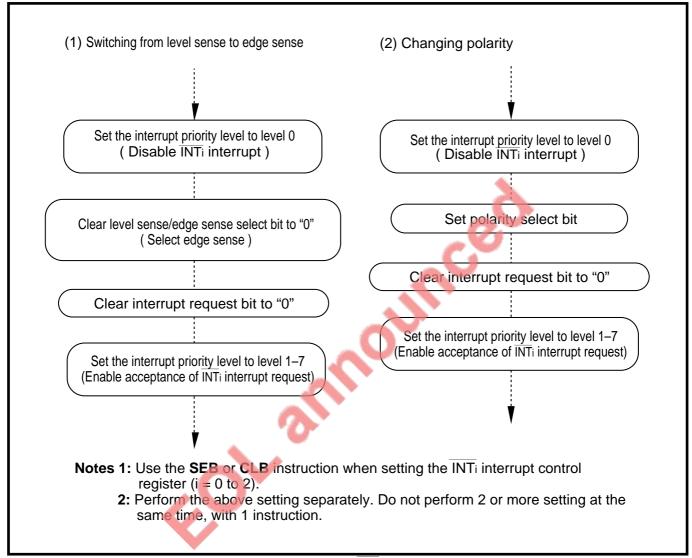

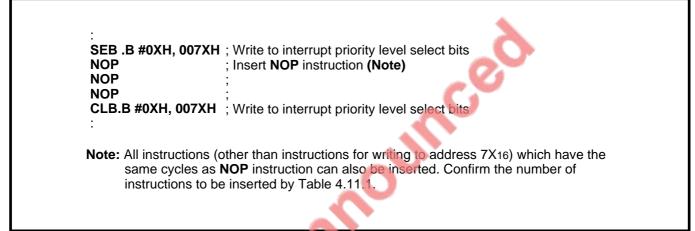

| 4.10.2 Switch of occurrence factor of INT interrupt request                             | 4-25 |

| 4.11 Precautions when using interrupts                                                  |      |

|                                                                                         |      |

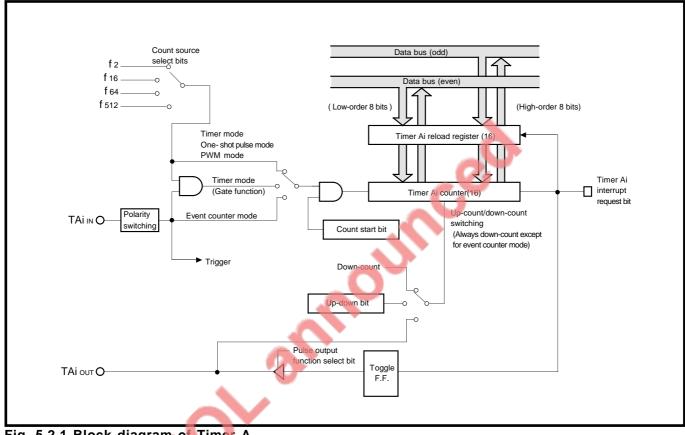

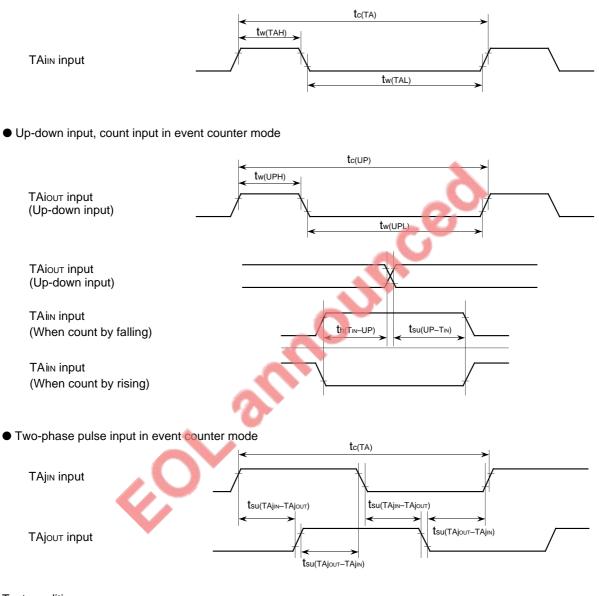

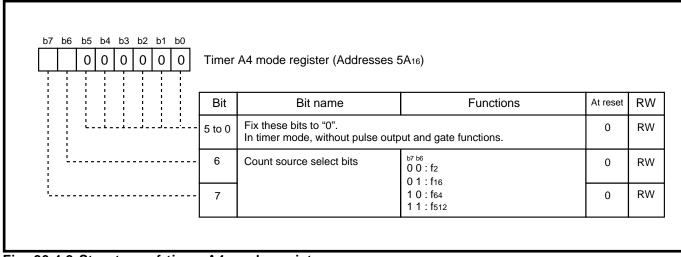

## CHAPTER 5. TIMER A

| 5.1 Overview                                          | 5-2  |

|-------------------------------------------------------|------|

| 5.2 Block description                                 | 5-3  |

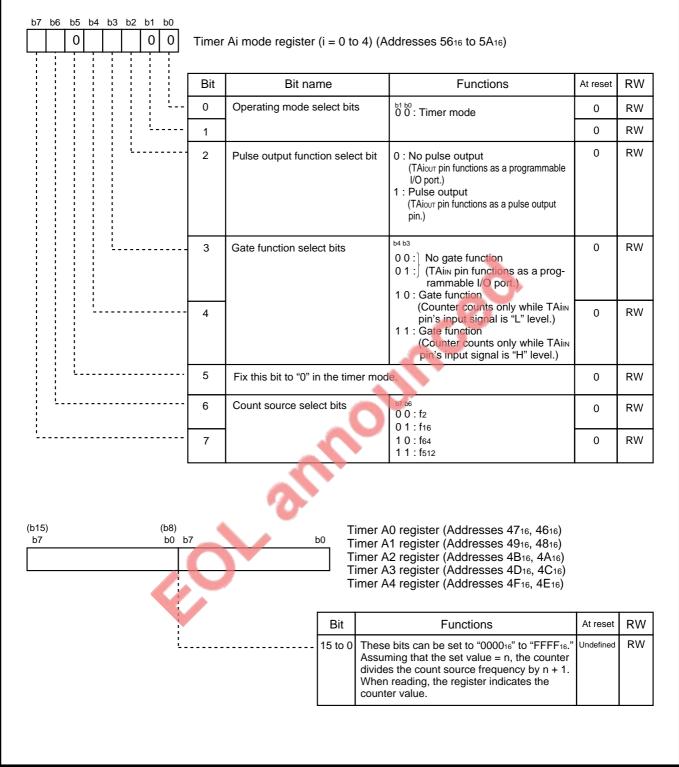

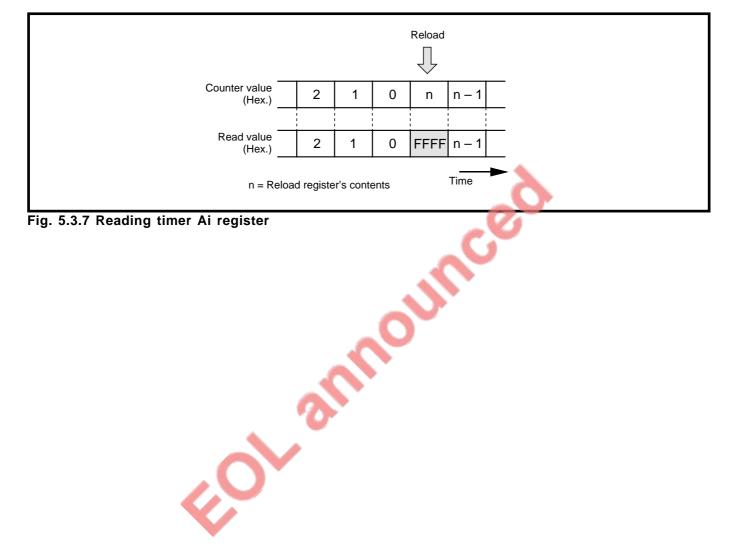

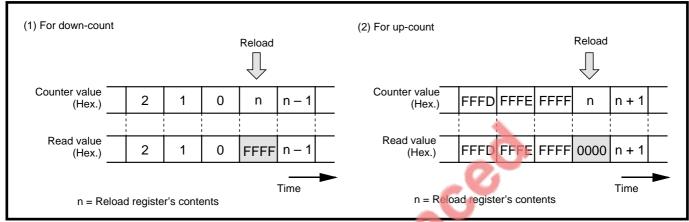

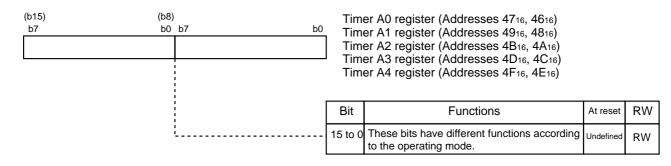

| 5.2.1 Counter and reload register (timer Ai register) |      |

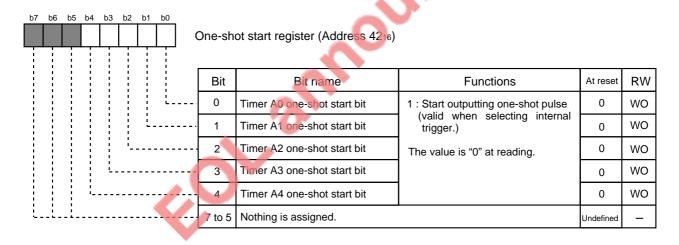

| 5.2.2 Count start register                            |      |

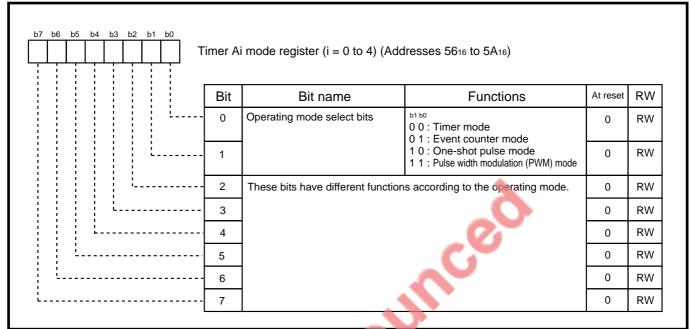

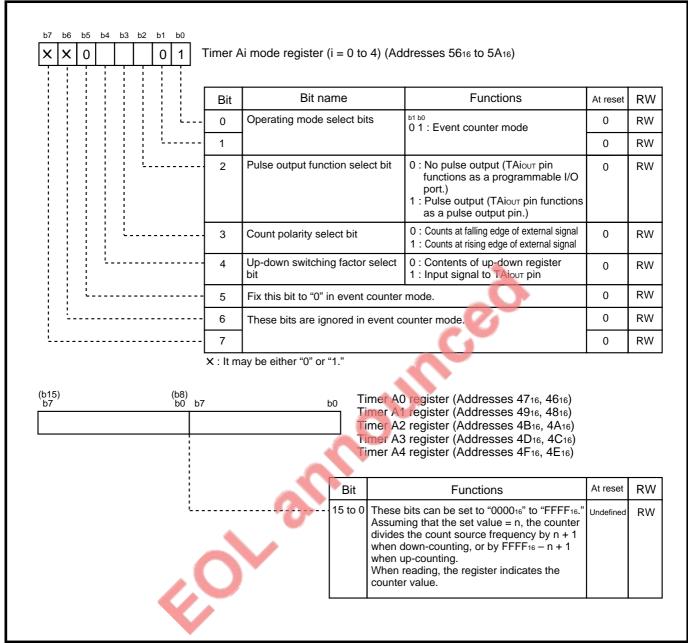

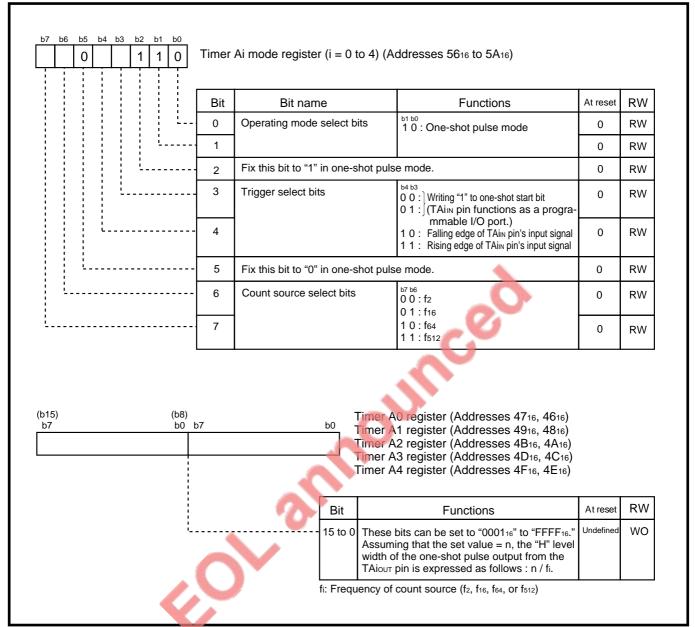

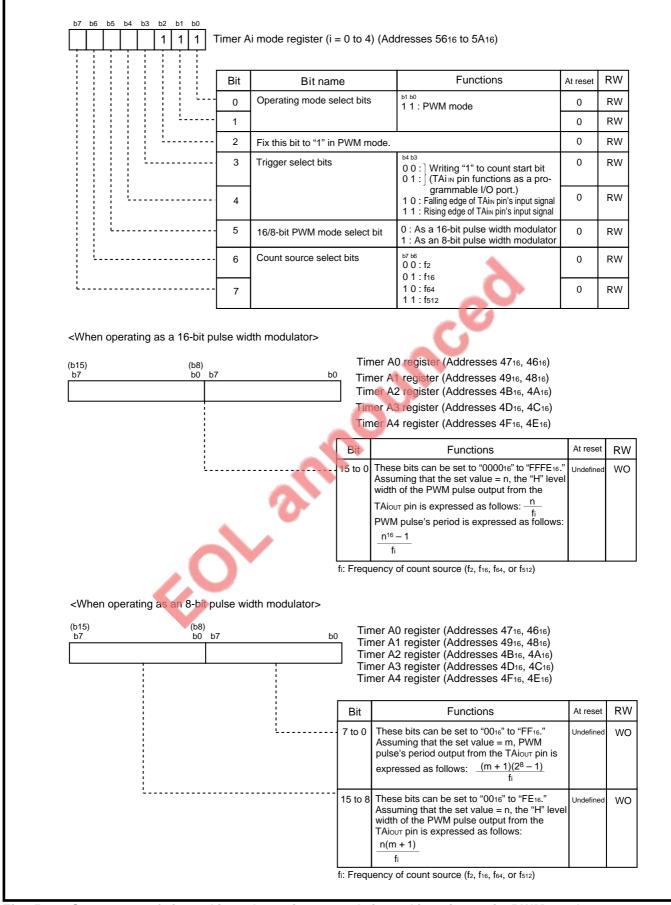

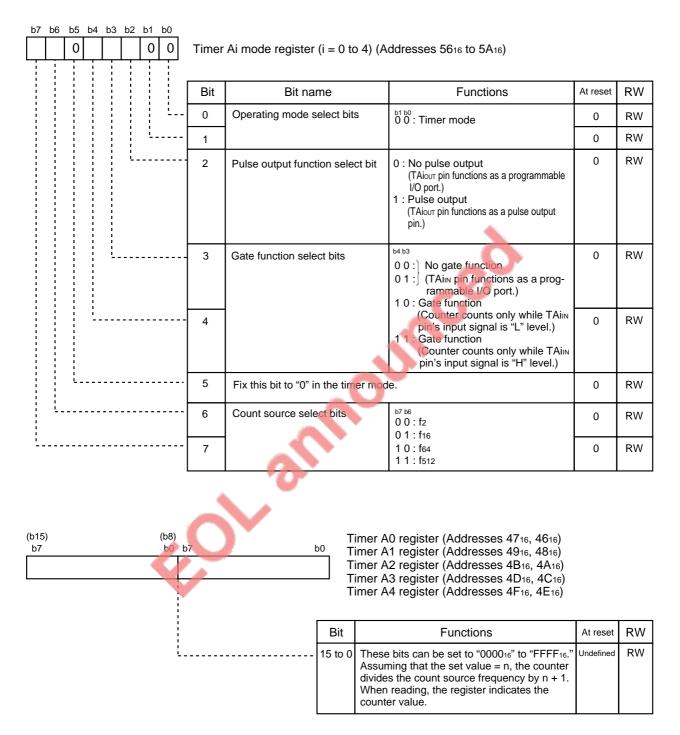

| 5.2.3 Timer Ai mode register                          |      |

| 5.2.4 Timer Ai interrupt control register             |      |

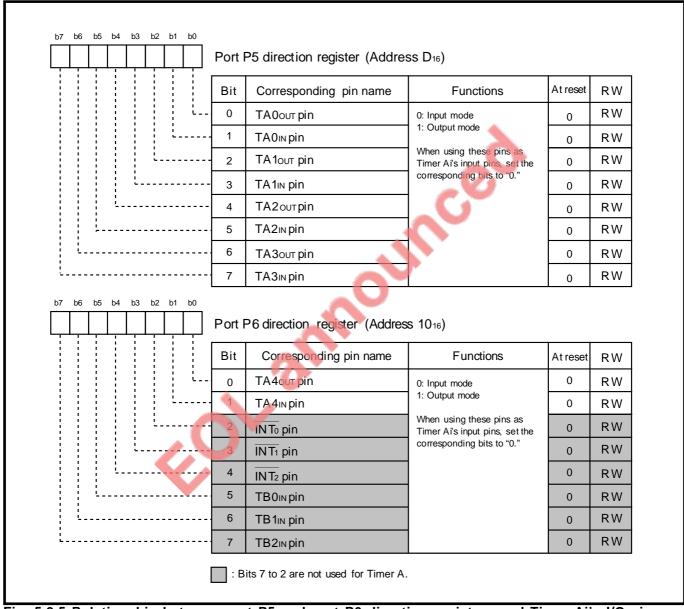

| 5.2.5 Port P5 and port P6 direction registers         |      |

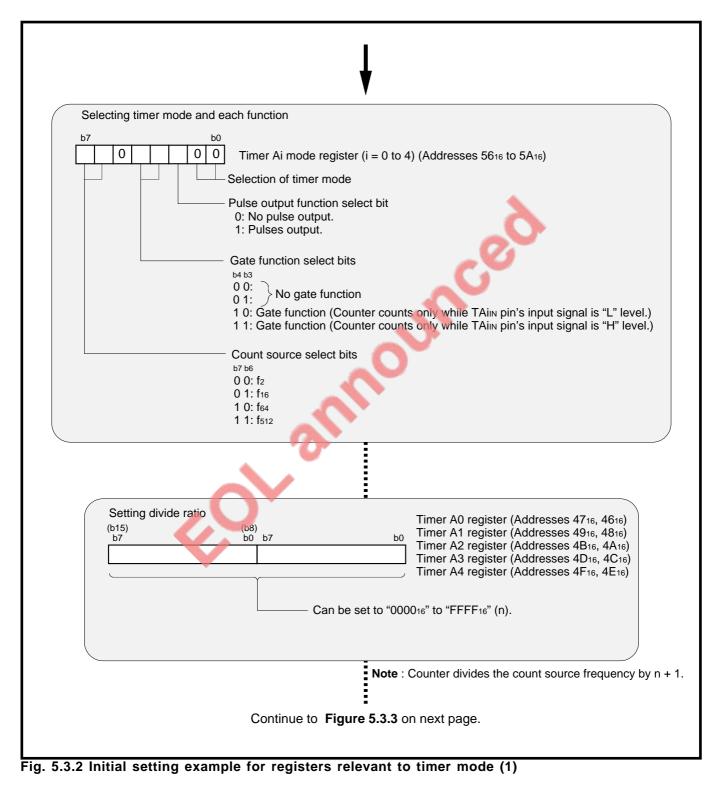

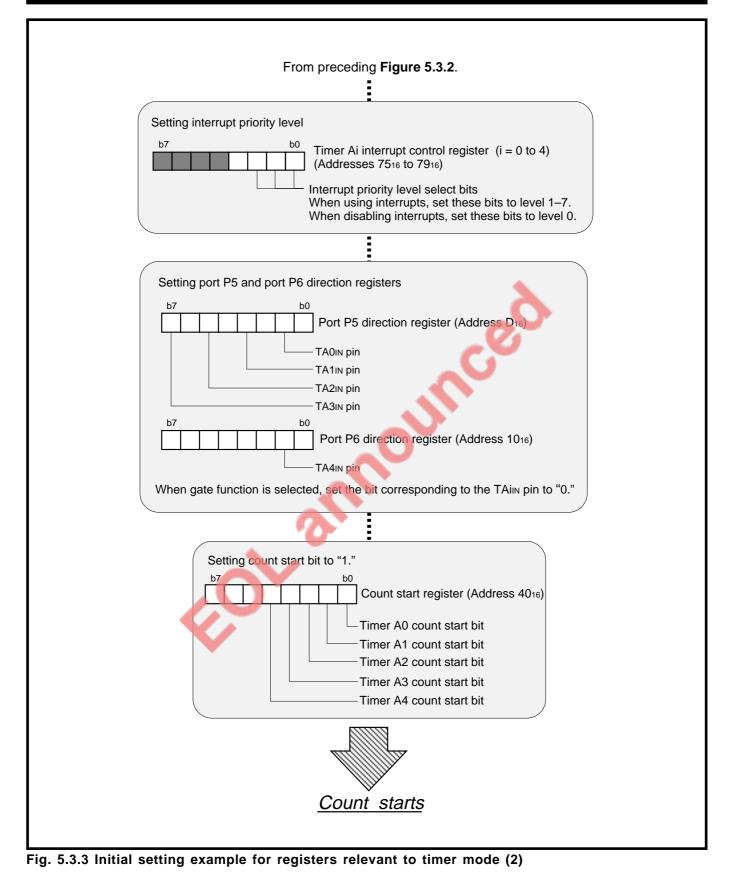

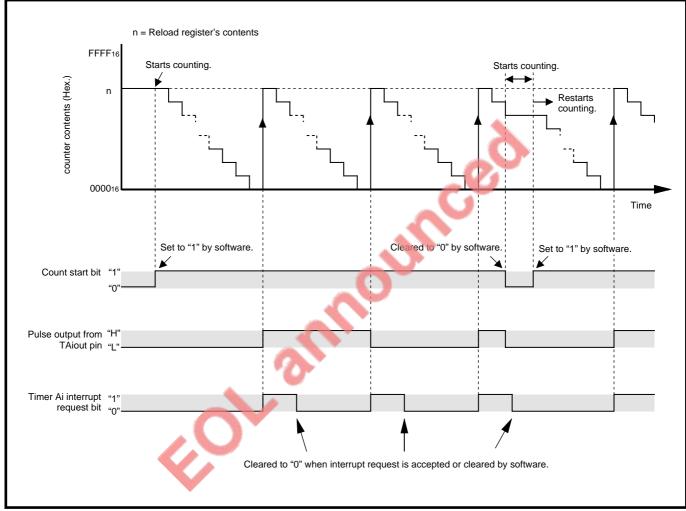

| 5.3 Timer mode                                        | 5-9  |

| 5.3.1 Setting for timer mode                          |      |

| 5.3.2 Count source                                    |      |

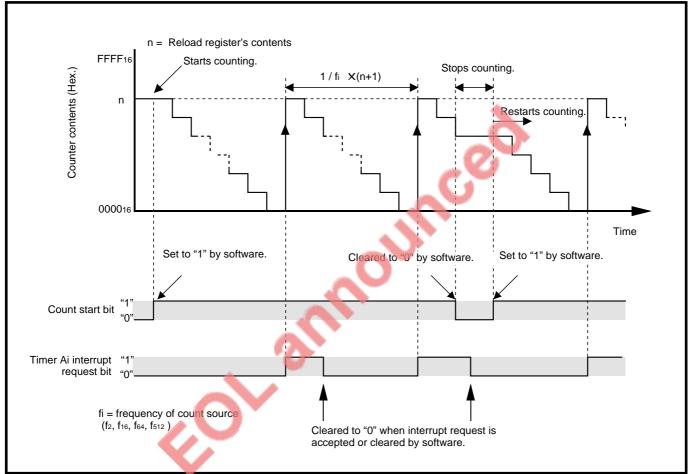

| 5.3.3 Operation in timer mode                         |      |

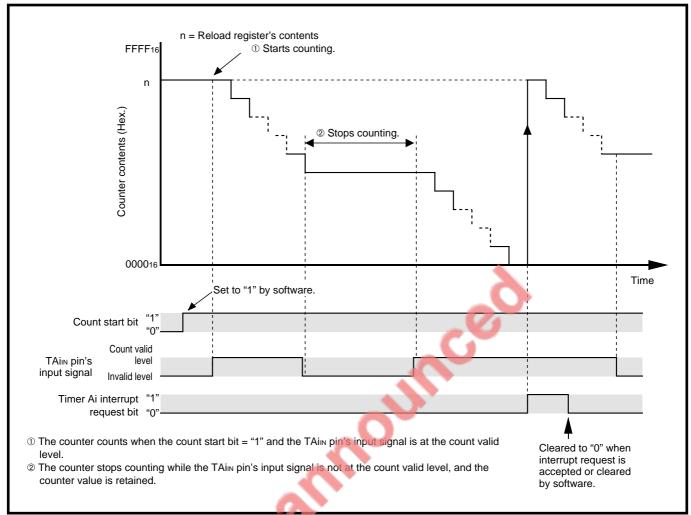

| 5.3.4 Select function                                 | 5-15 |

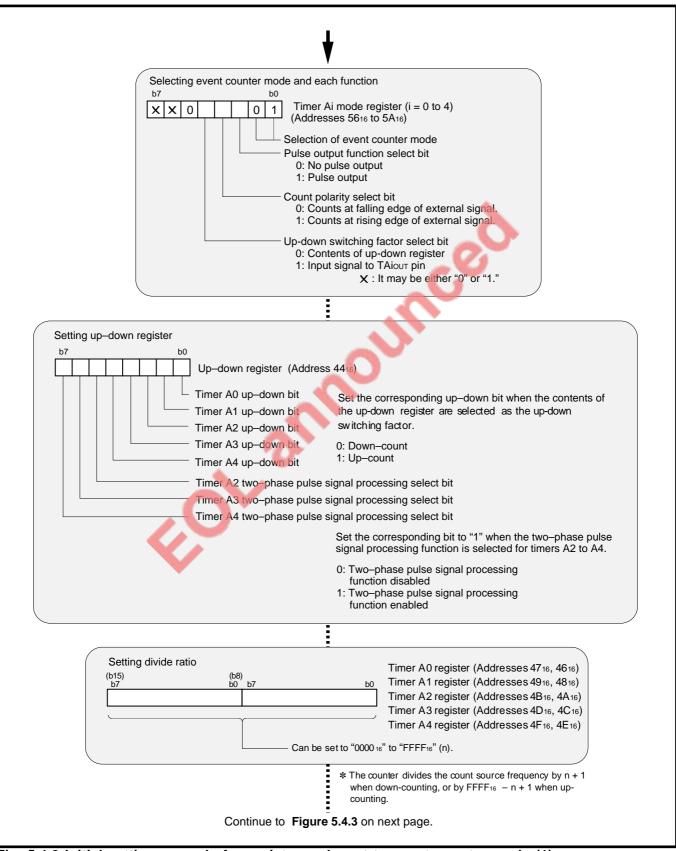

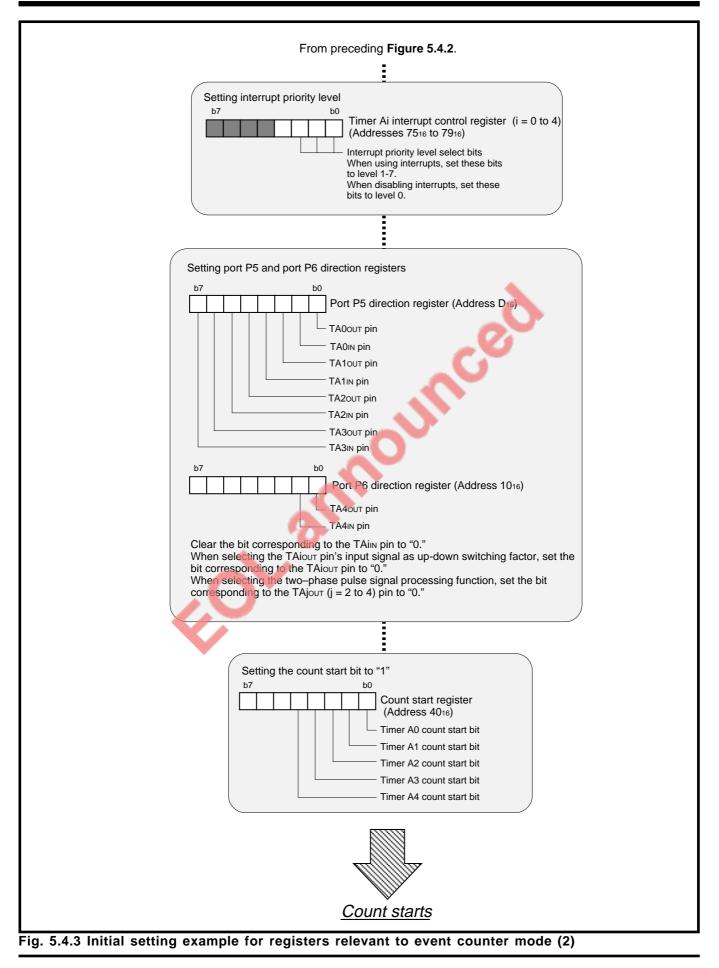

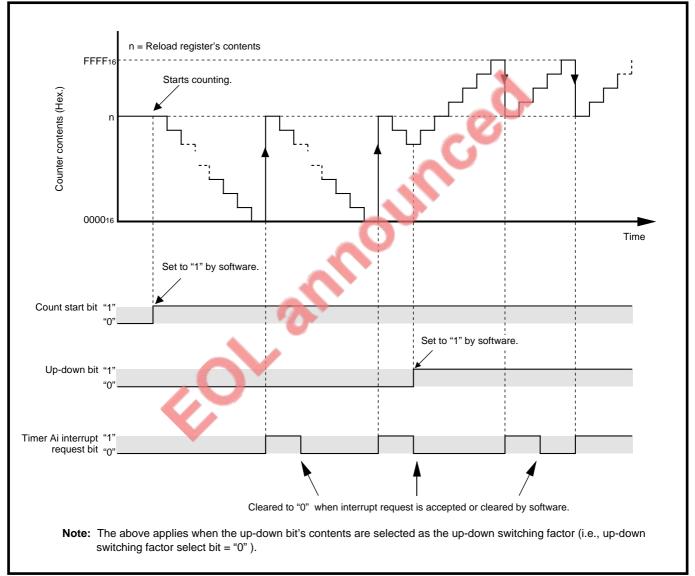

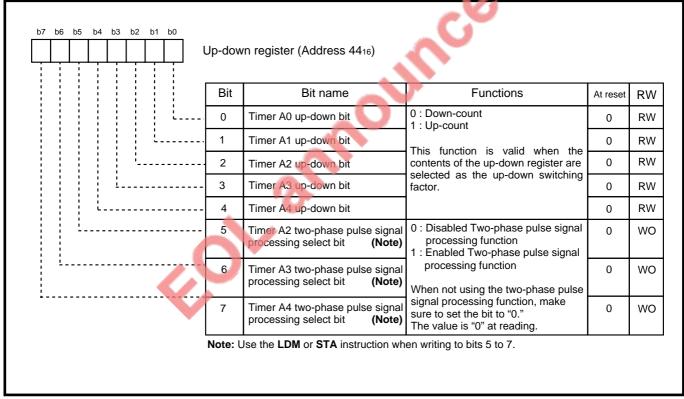

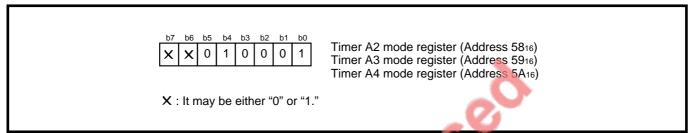

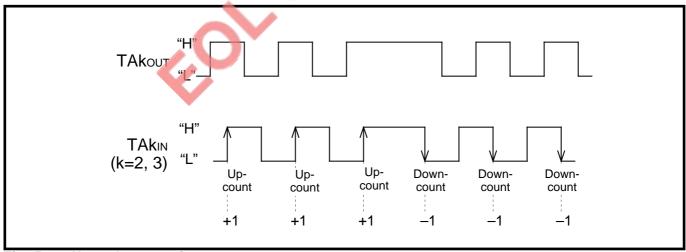

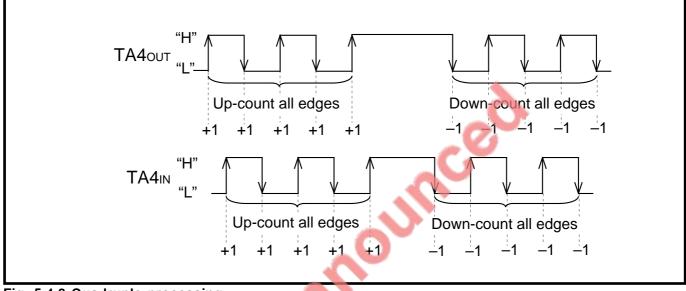

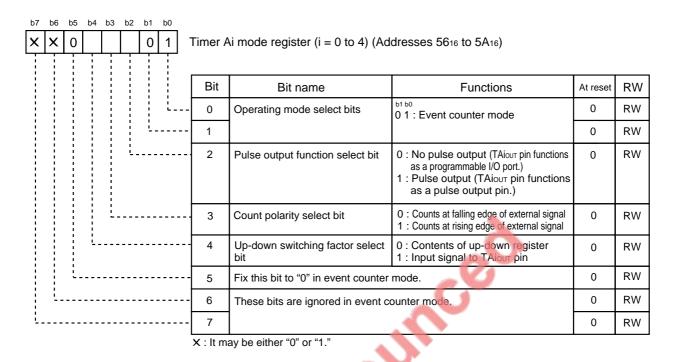

| 5.4 Event counter mode                                | 5-19 |

| 5.4.1 Setting for event counter mode                  |      |

| 5.4.2 Operation in event counter mode                 | 5-24 |

| 5.4.3 Select functions                                | 5-26 |

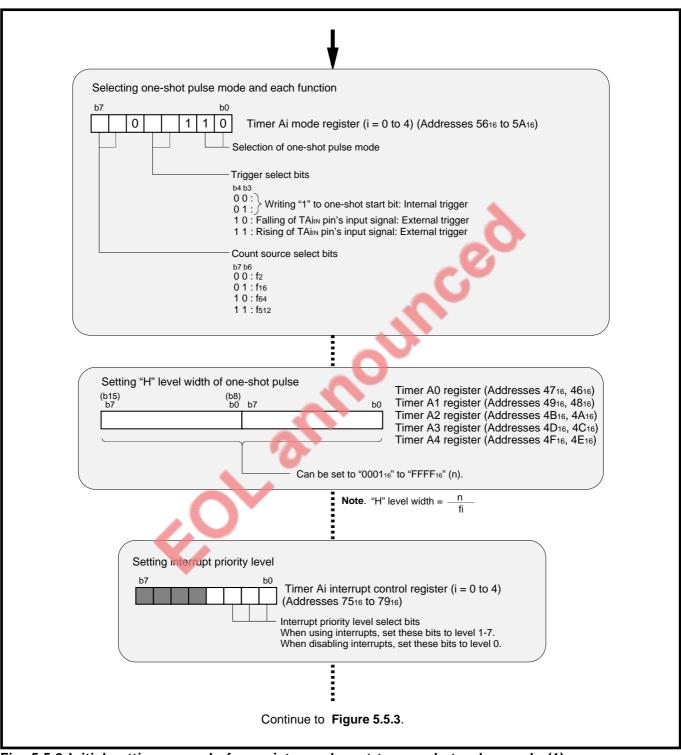

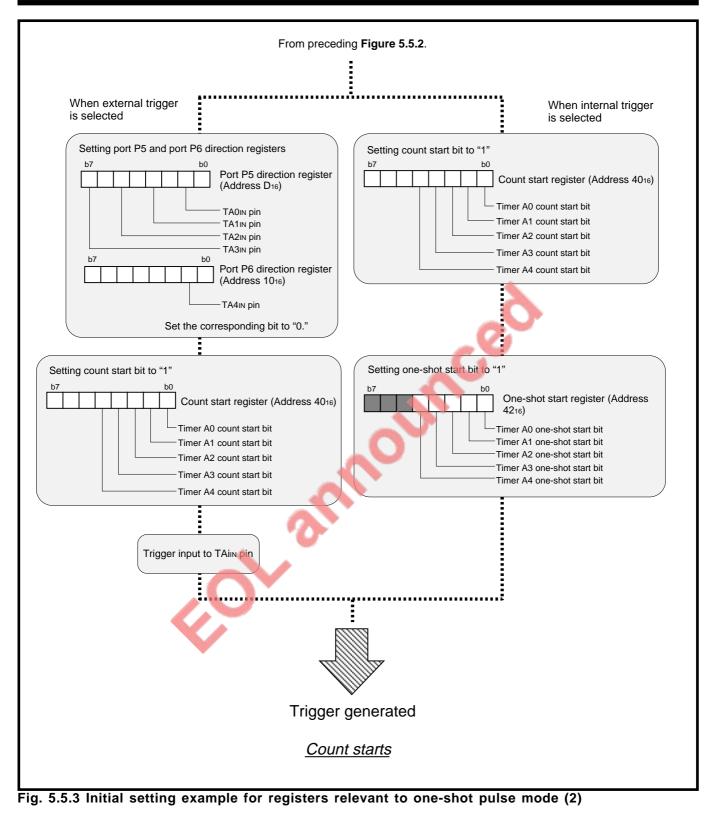

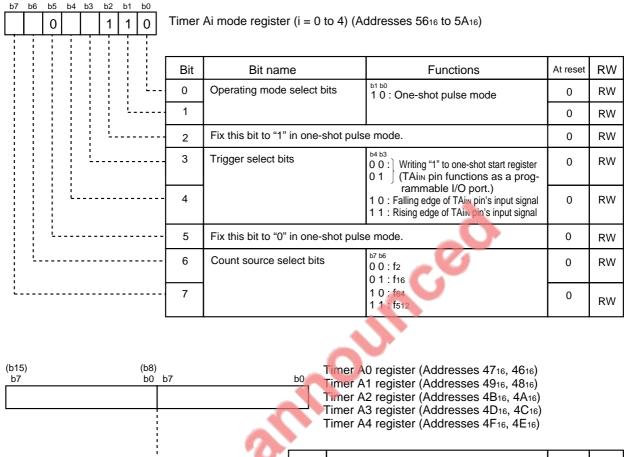

| 5.5 One-shot pulse mode                               |      |

| 5.5.1 Setting for one-shot pulse mode                 | 5-32 |

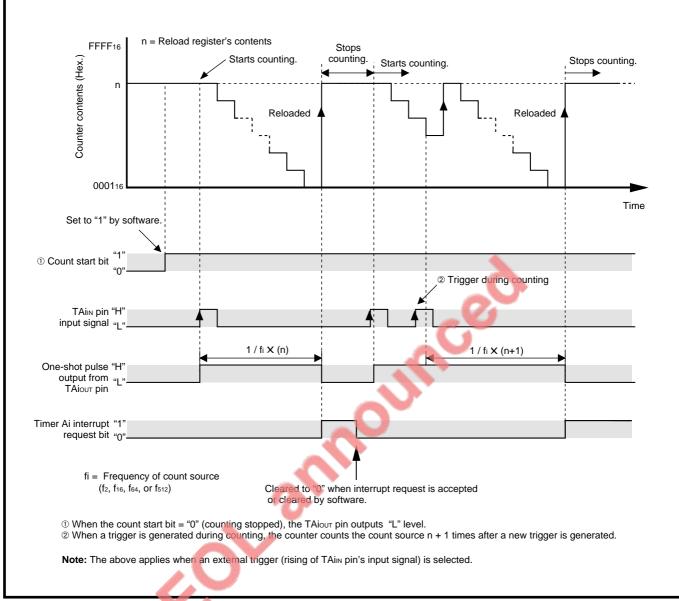

| 5.5.2 Count source                                    |      |

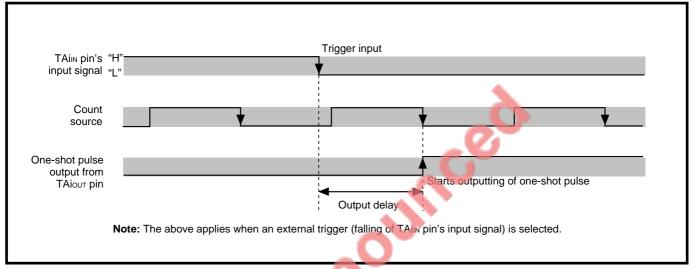

| 5.5.3 Trigger                                         |      |

| 5.5.4 Operation in one-shot pulse mode                |      |

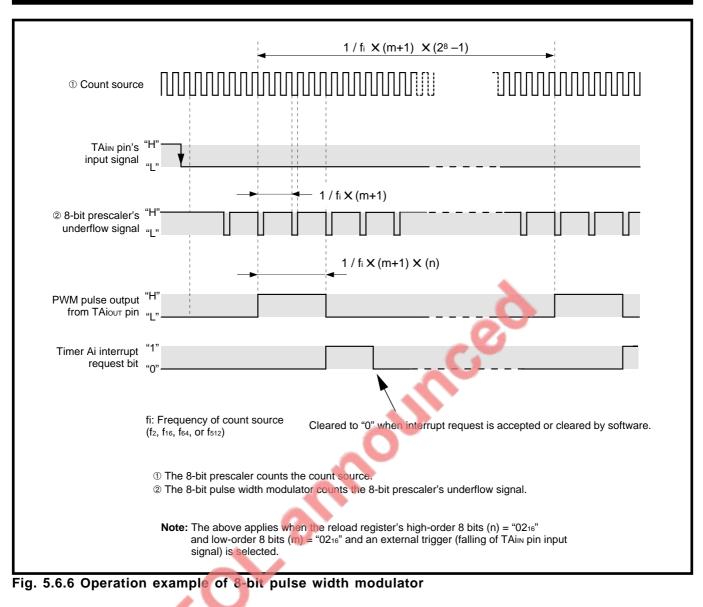

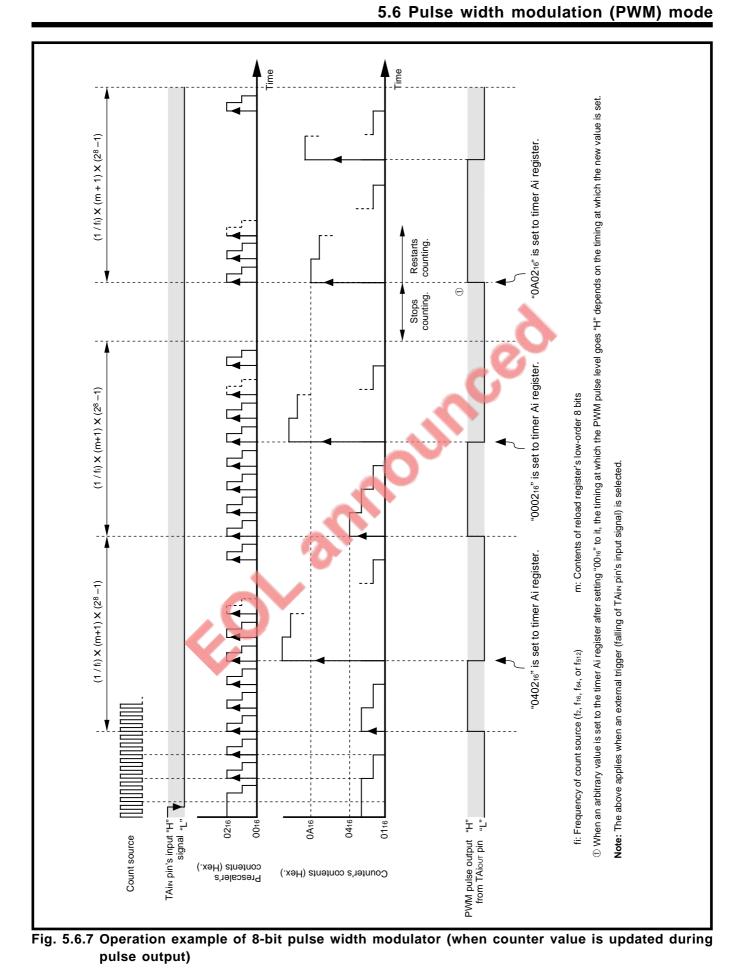

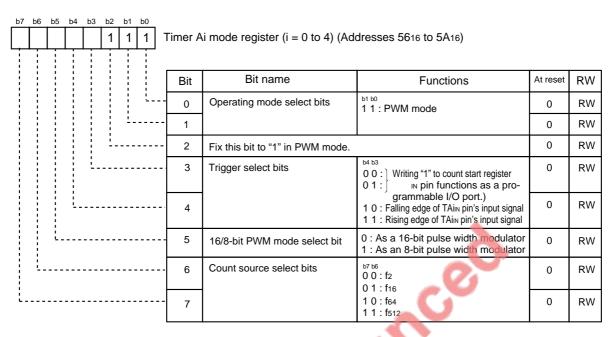

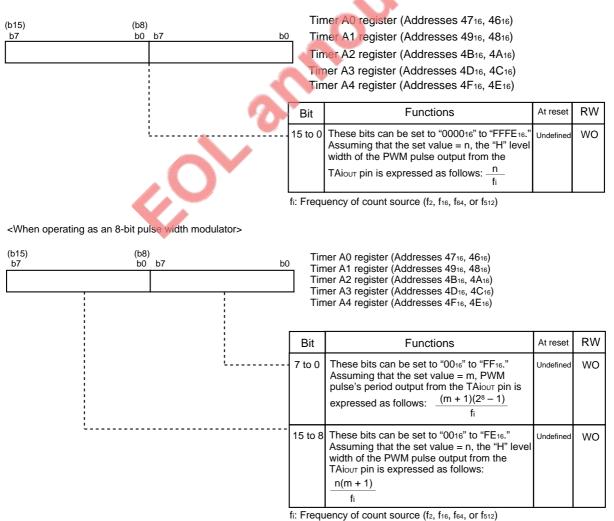

| 5.6 Pulse width modulation (PWM) mode                 |      |

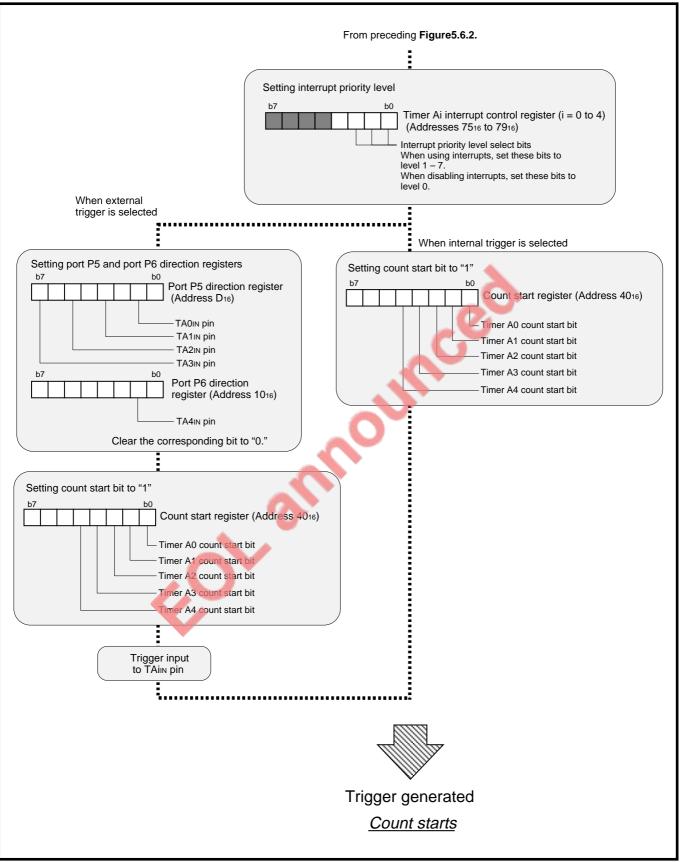

| 5.6.1 Setting for PWM mode                            |      |

| 5.6.2 Count source                                    |      |

| 5.6.3 Trigger                                         |      |

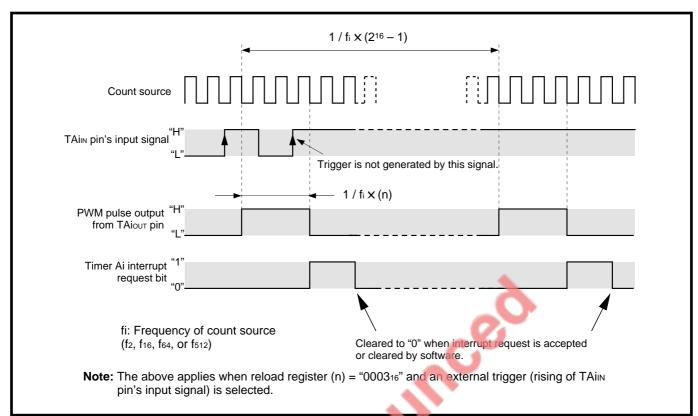

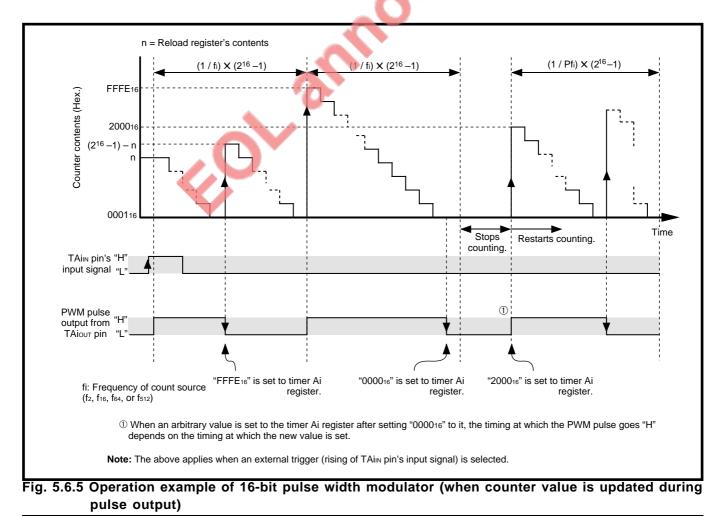

| 5.6.4 Operation in PWM mode                           | 5-44 |

|                                                       |      |

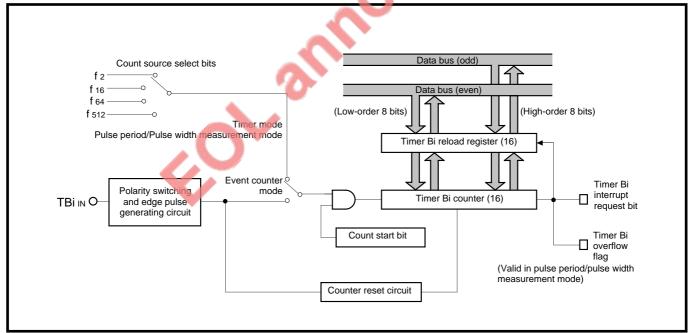

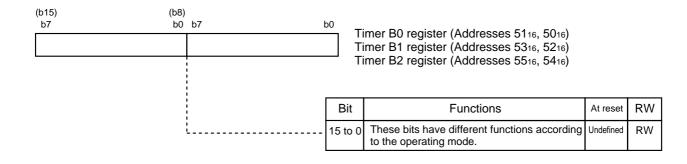

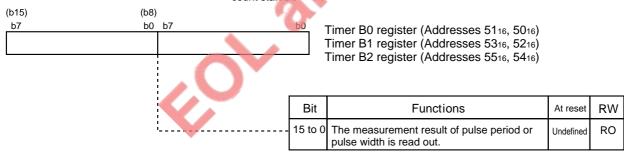

### CHAPTER 6. TIMER B

| 6-2 |

|-----|

|     |

|     |

|     |

|     |

| 6-6 |

|     |

## **Table of Contents**

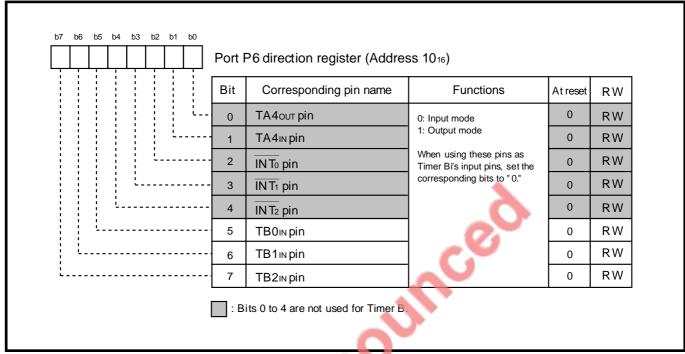

| 6.2.5 Port P6 direction register                             | 6-7  |

|--------------------------------------------------------------|------|

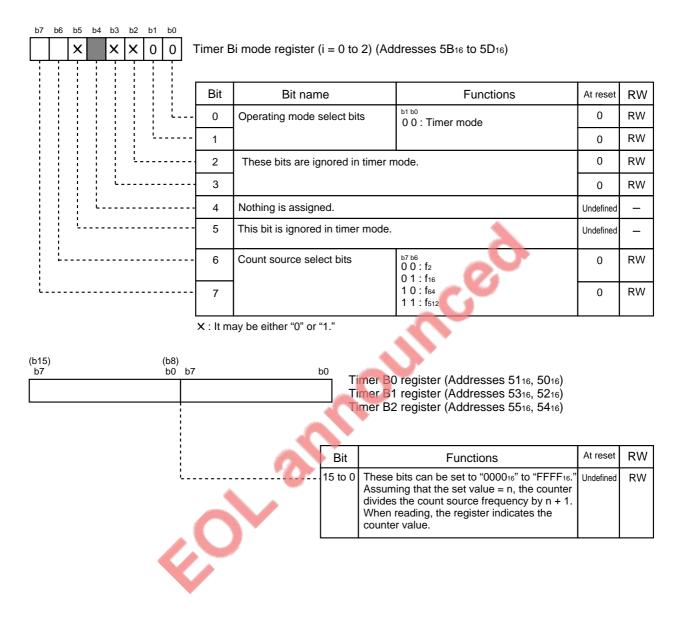

| 6.3 Timer mode                                               |      |

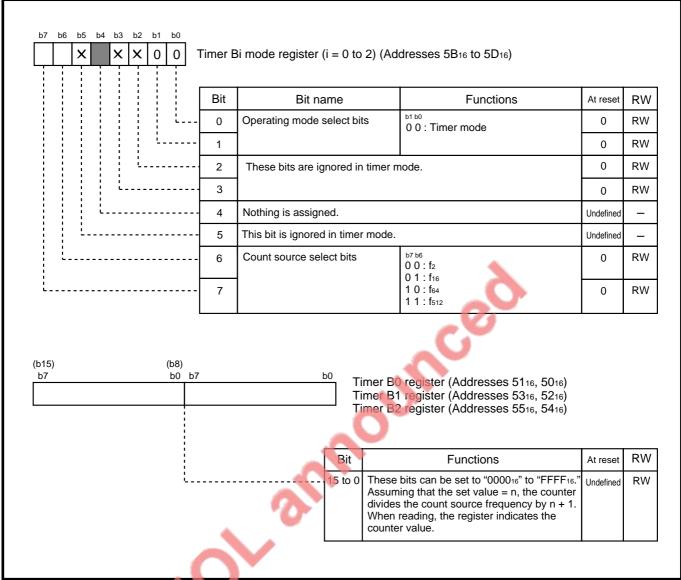

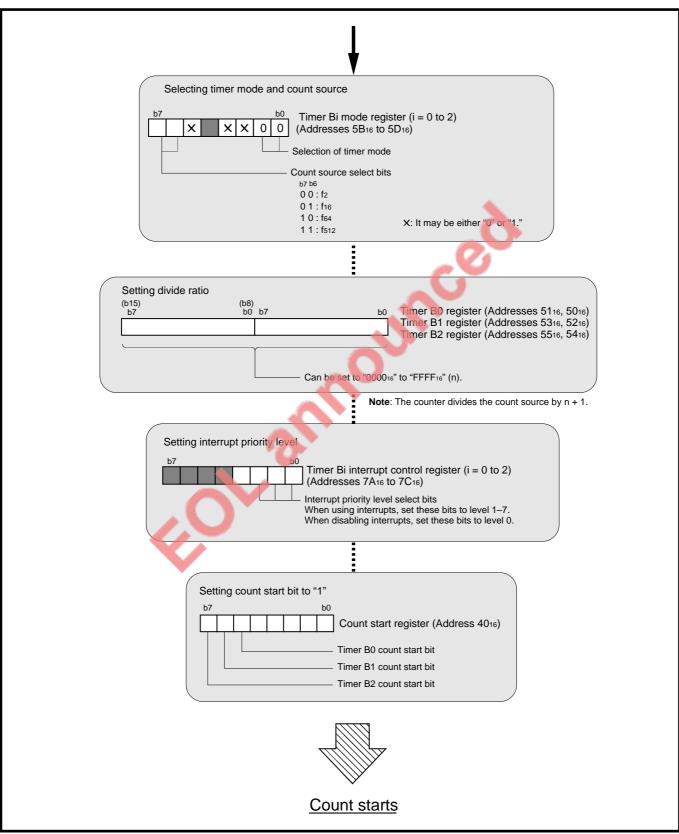

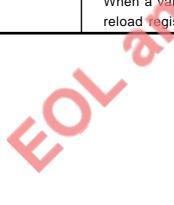

| 6.3.1 Setting for timer mode                                 | 6-10 |

| 6.3.2 Count source                                           | 6-11 |

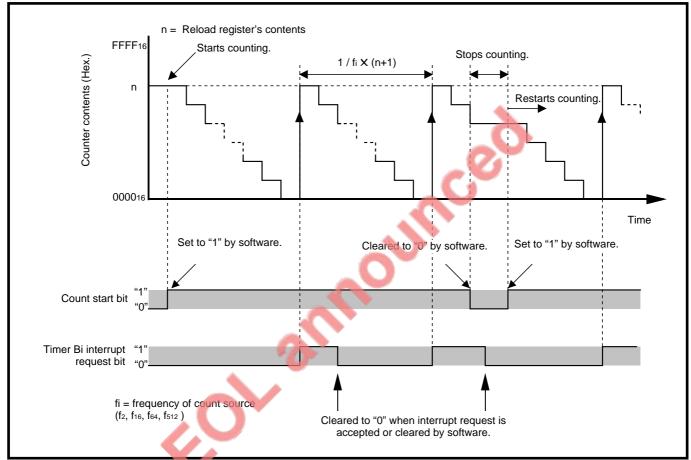

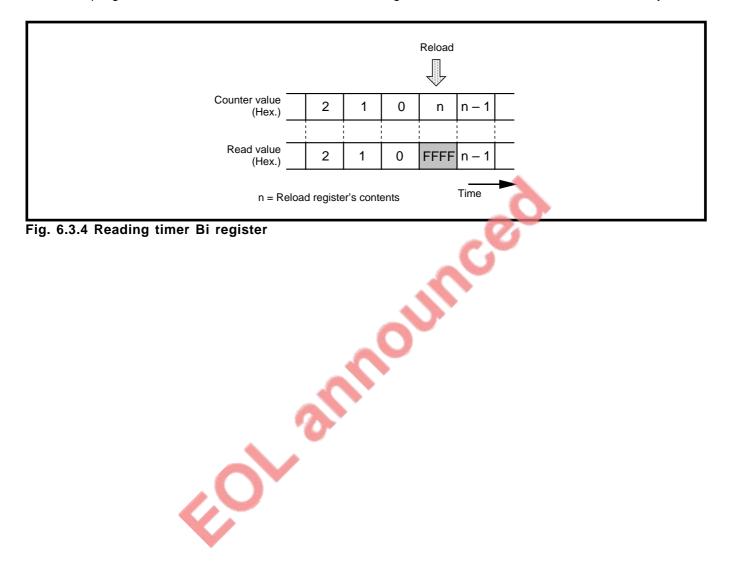

| 6.3.3 Operation in timer mode                                | 6-12 |

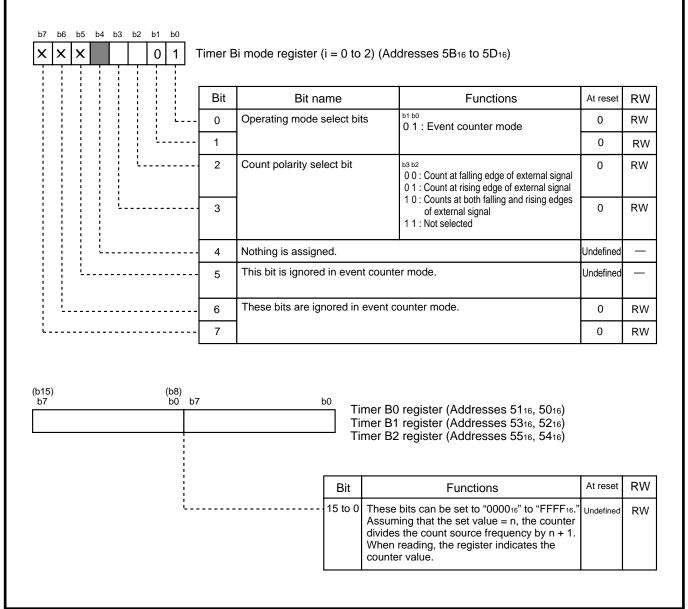

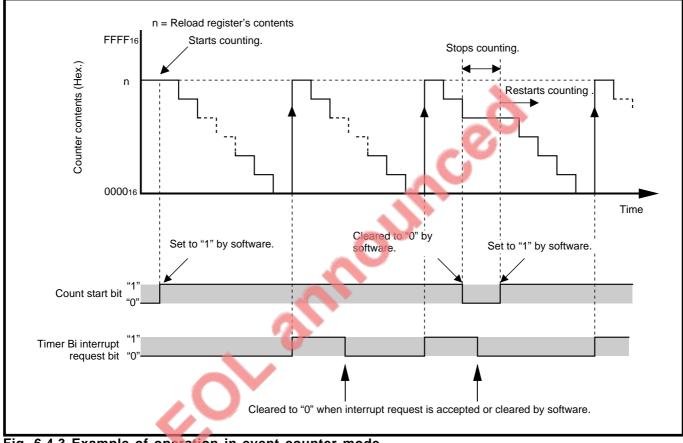

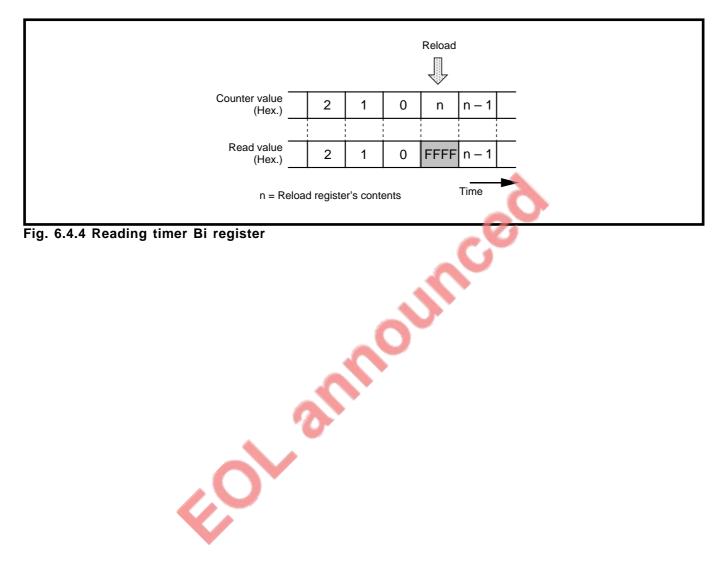

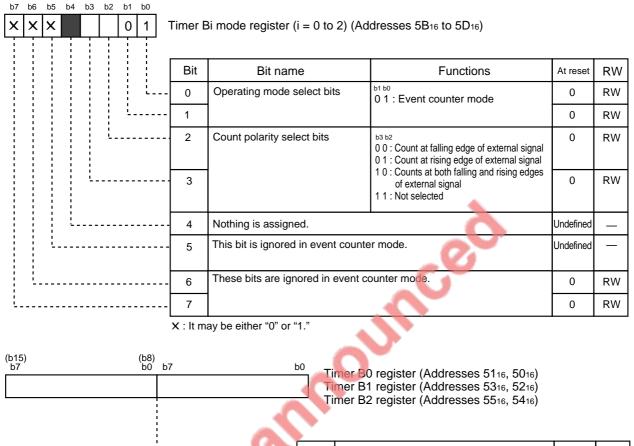

| 6.4 Event counter mode                                       | 6-14 |

| 6.4.1 Setting for event counter mode                         | 6-16 |

| 6.4.2 Operation in event counter mode                        | 6-17 |

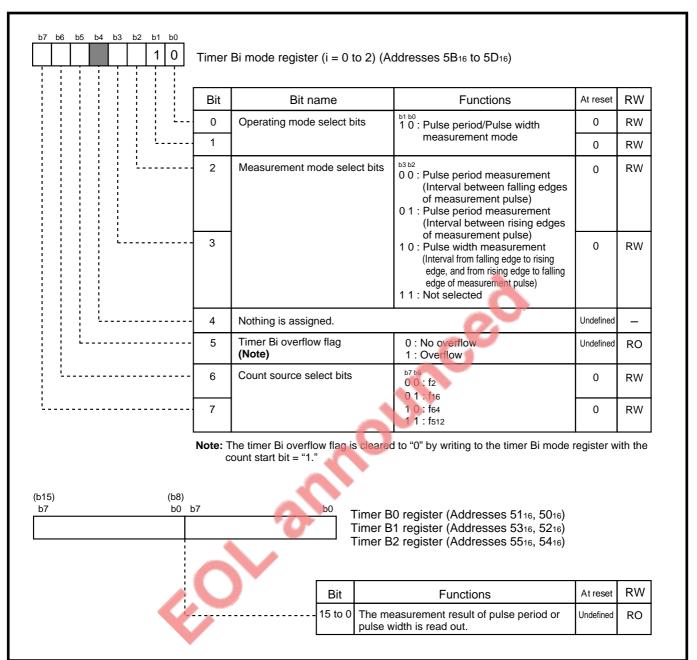

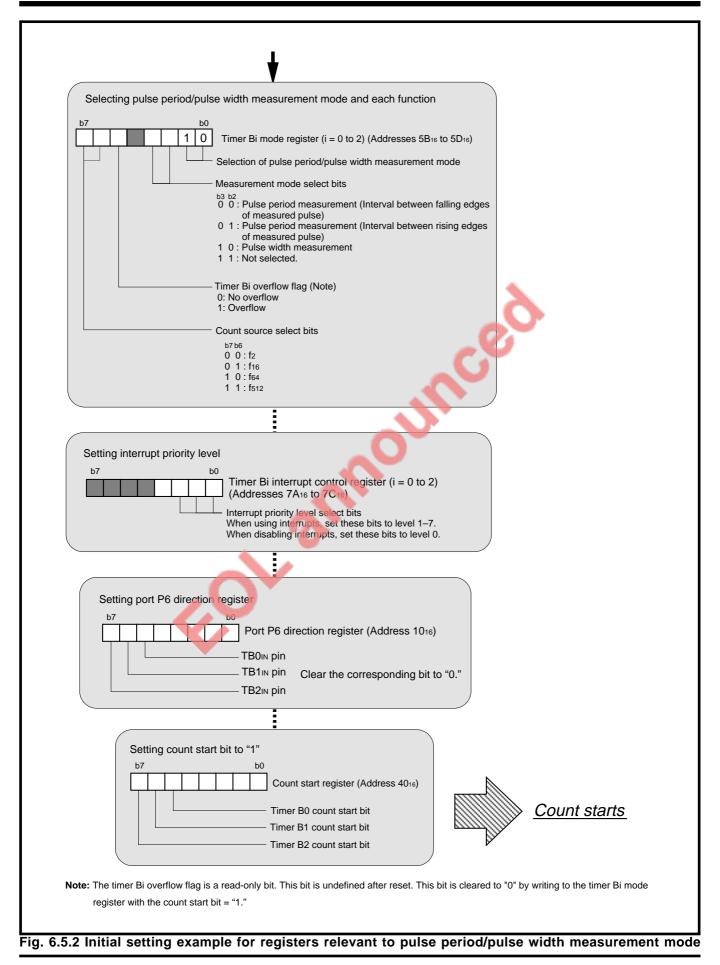

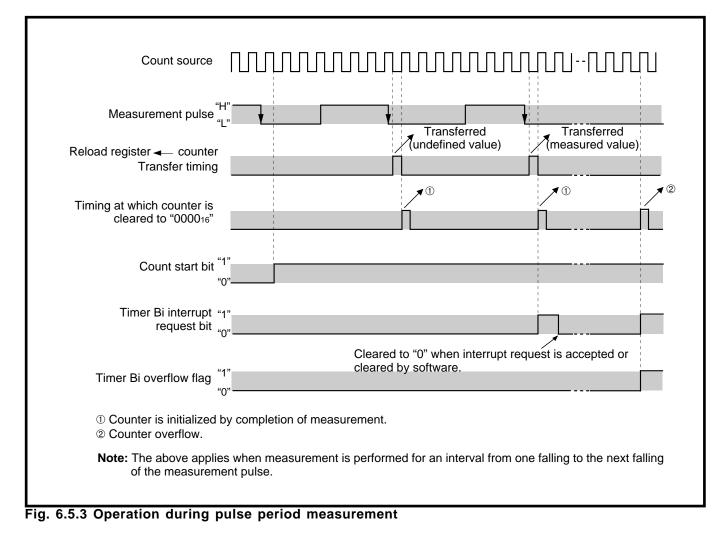

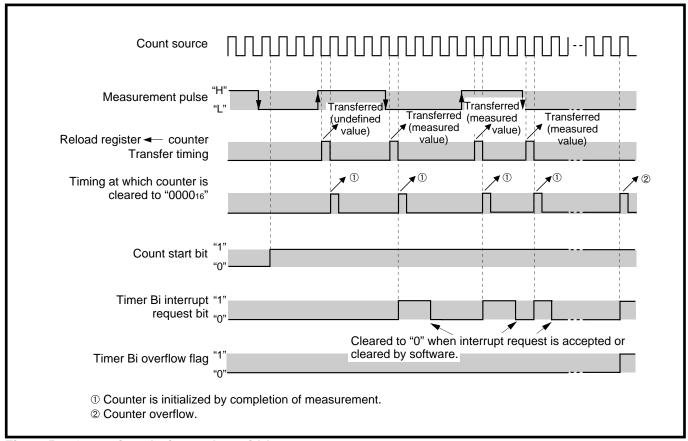

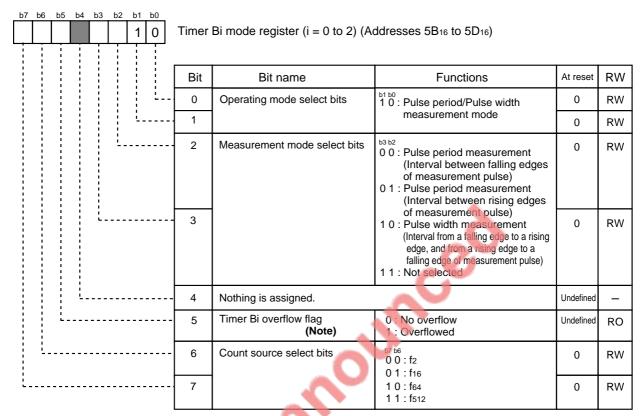

| 6.5 Pulse period/pulse width measurement mode                | 6-19 |

| 6.5.1 Setting for pulse period/pulse width measurement mode  | 6-21 |

| 6.5.2 Count source                                           | 6-23 |

| 6.5.3 Operation in pulse period/pulse width measurement mode | 6-24 |

### CHAPTER 7. SERIAL I/O

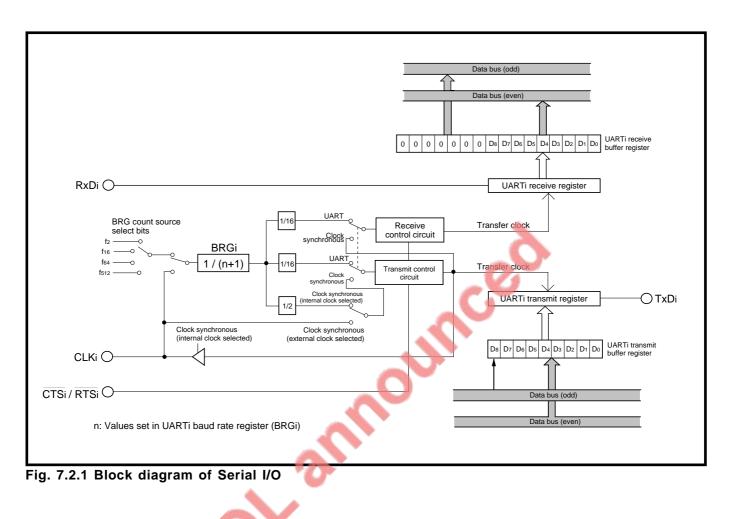

| 7.1 Overview                                                                         | 7-2    |

|--------------------------------------------------------------------------------------|--------|

| 7.2 Block description                                                                | 7-3    |

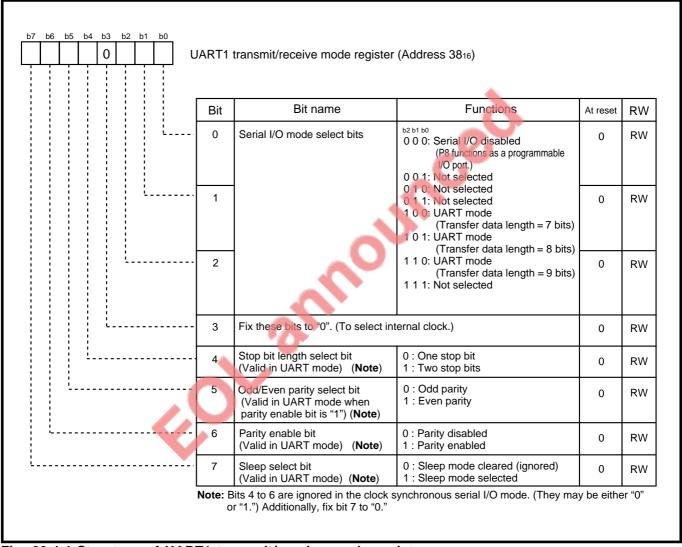

| 7.2.1 UARTi transmit/receive mode register                                           | 7-4    |

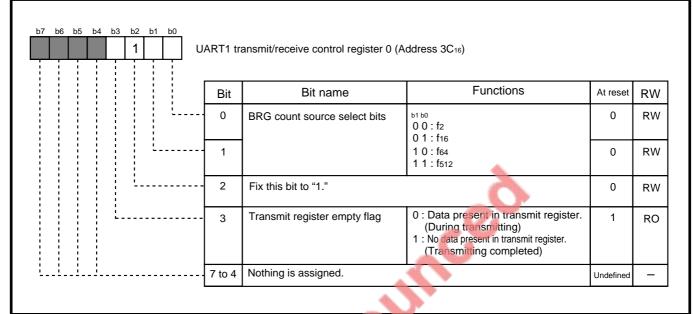

| 7.2.2 UARTi transmit/receive control register 0                                      |        |

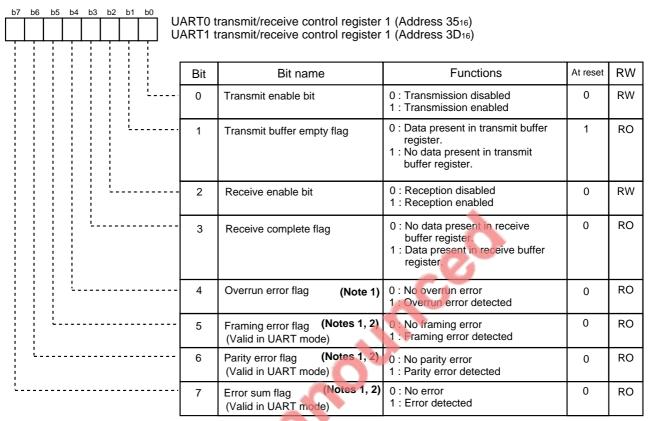

| 7.2.3 UARTi transmit/receive control register 1                                      | 7-7    |

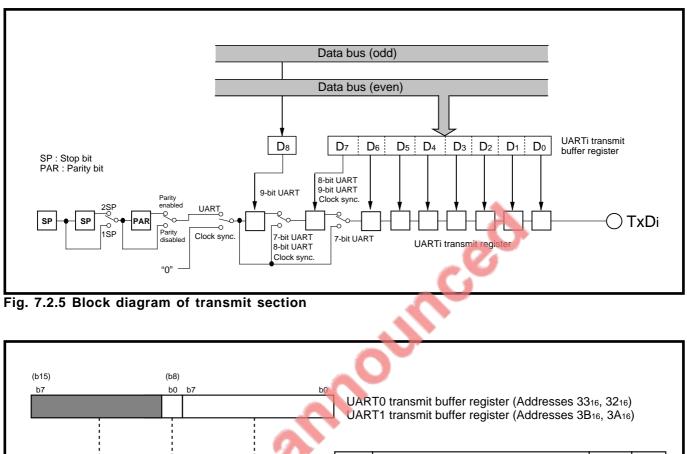

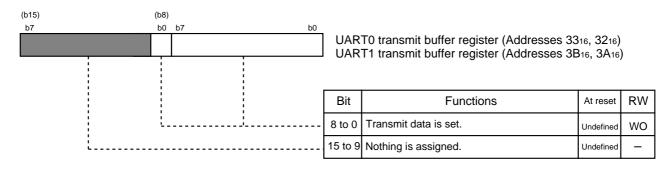

| 7.2.4 UARTi transmit register and UARTi transmit buffer register                     | 7-9    |

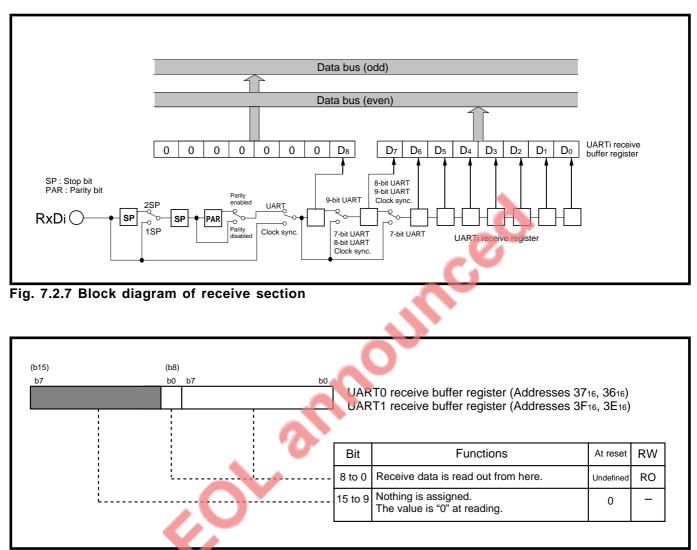

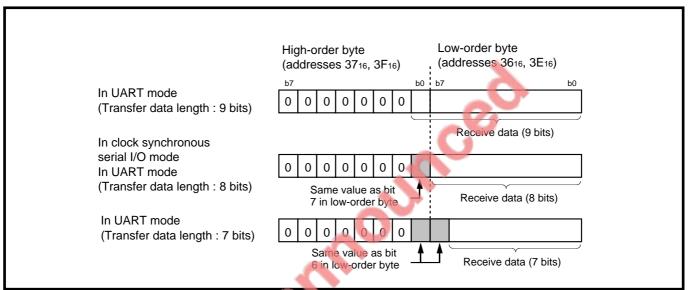

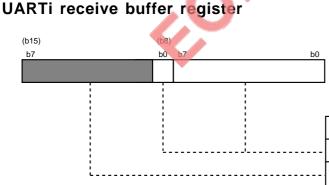

| 7.2.5 UARTi receive register and UARTi receive buffer register                       | .7-11  |

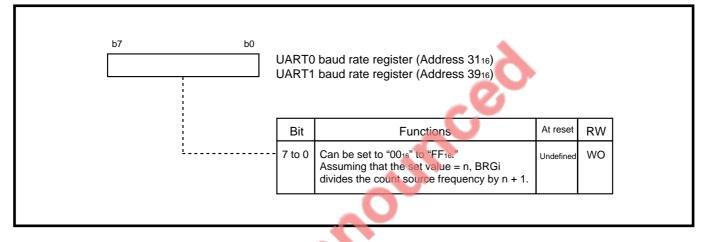

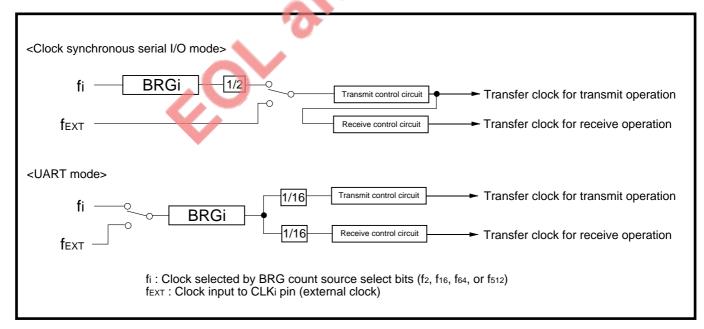

| 7.2.6 UARTi baud rate register (BRGi)                                                | . 7-13 |

| 7.2.7 UARTi transmit interrupt control and UARTi receive interrupt control registers | 7-14   |

| 7.2.8 Port P8 direction register                                                     |        |

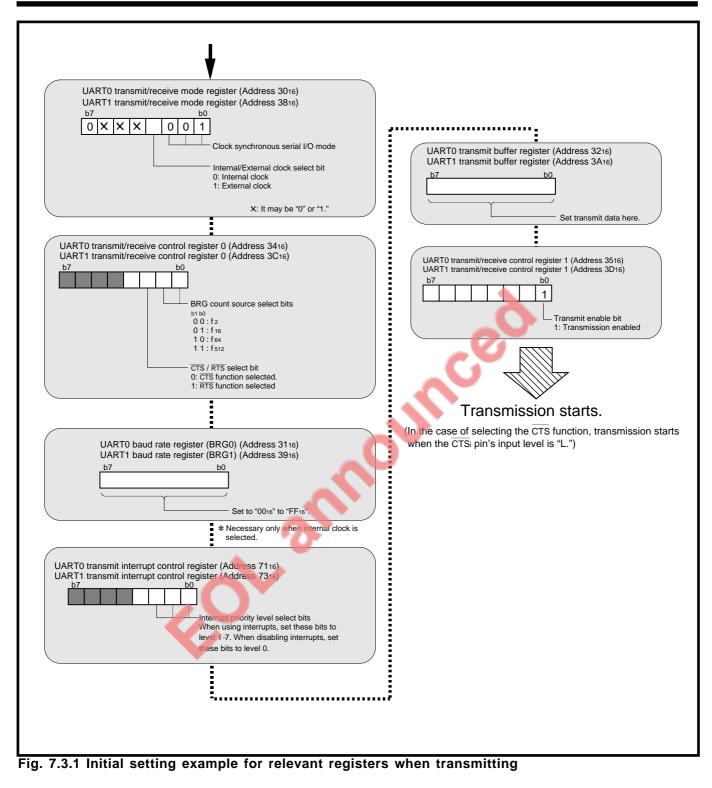

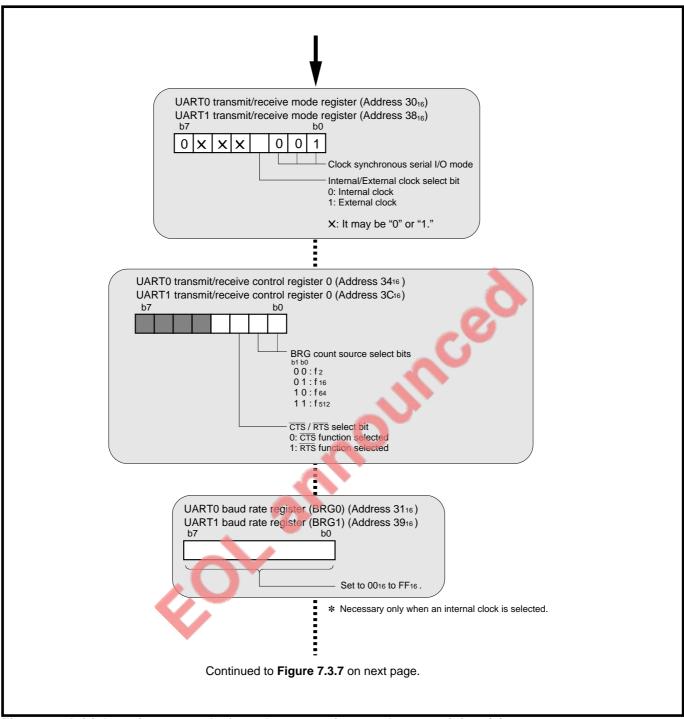

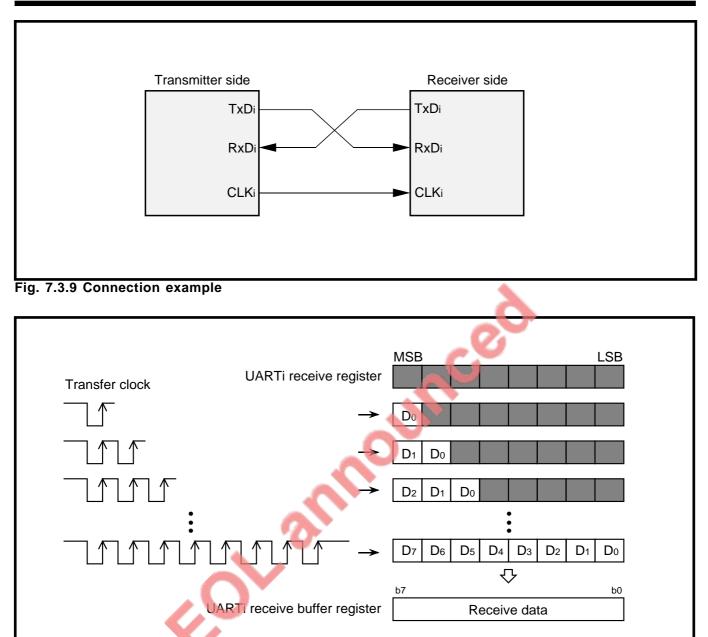

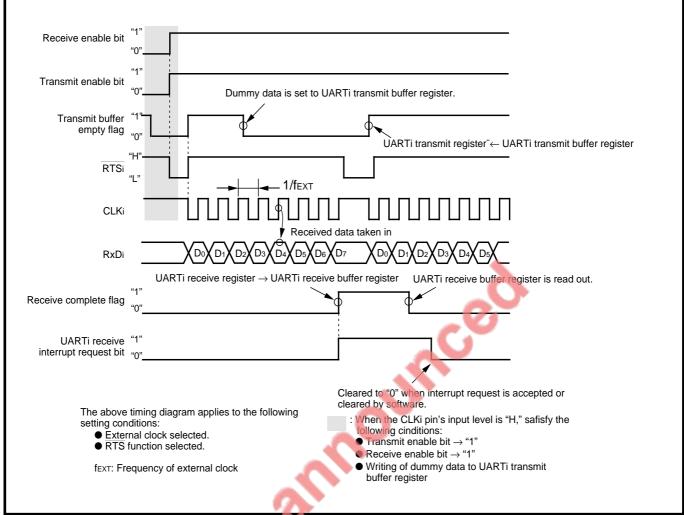

| 7.3 Clock synchronous serial I/O mode                                                | . 7-17 |

| 7.3.1 Transfer clock (synchronizing clock)                                           | . 7-18 |

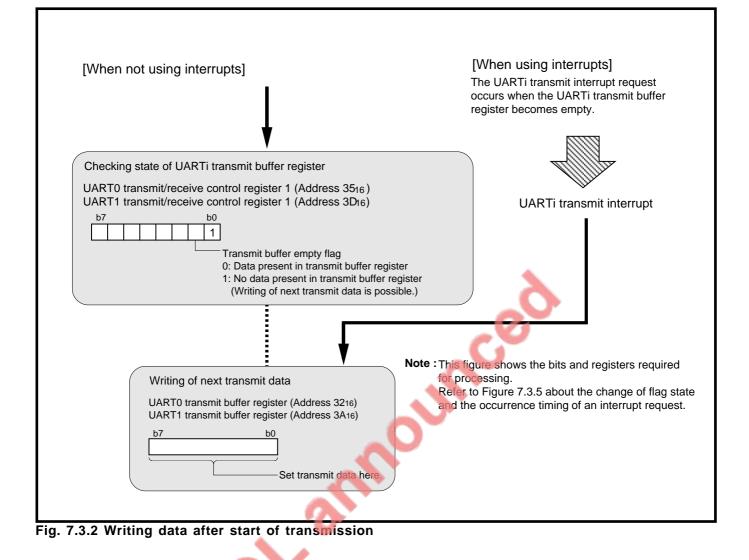

| 7.3.2 Method of transmission                                                         |        |

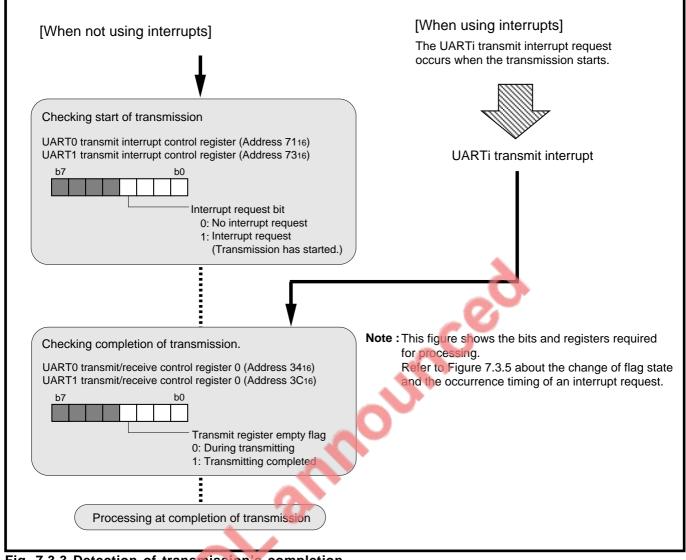

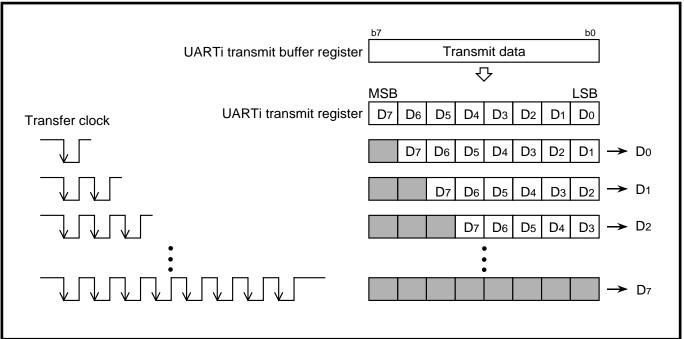

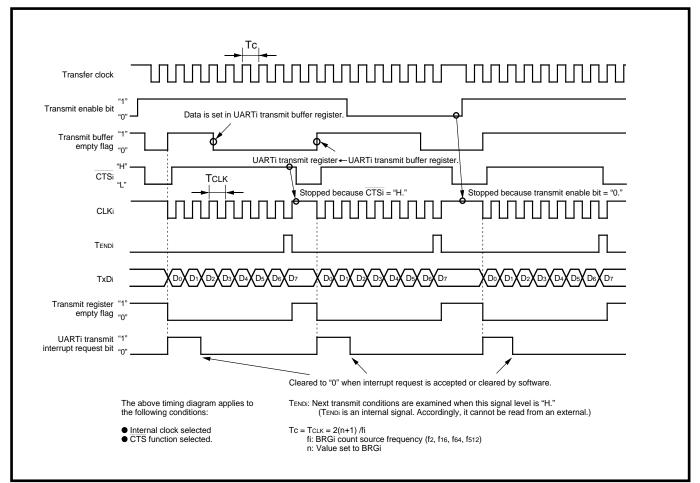

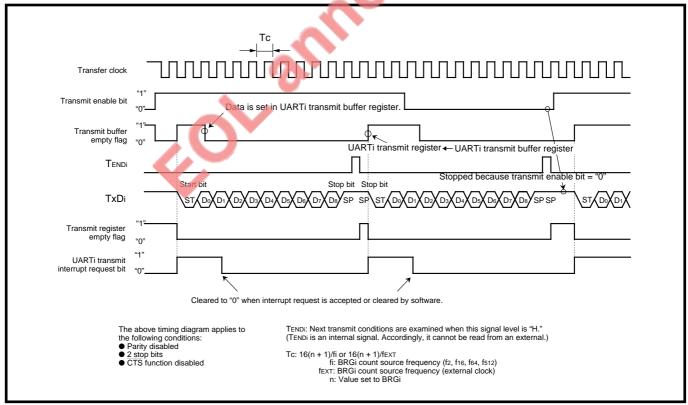

| 7.3.3 Transmit operation                                                             |        |

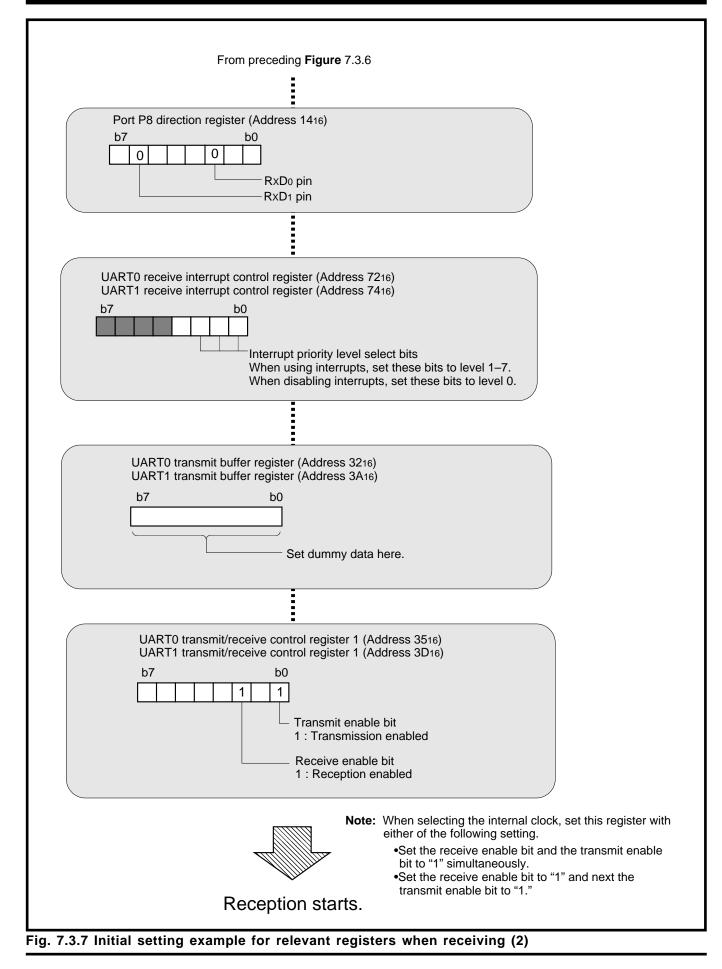

| 7.3.4 Method of reception                                                            | 7-25   |

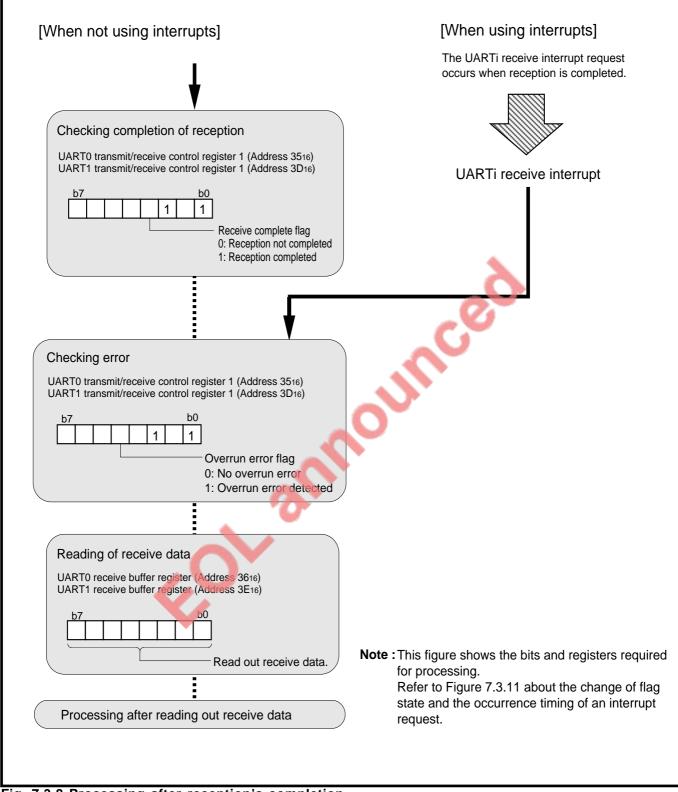

| 7.3.5 Receive operation                                                              |        |

| 7.3.6 Process on detecting overrun error                                             |        |

| [Precautions when operating in clock synchronous serial I/O mode]                    |        |

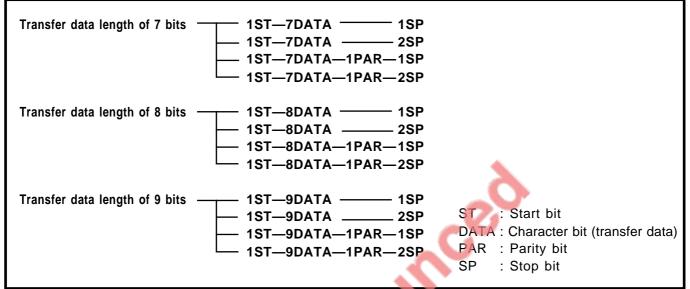

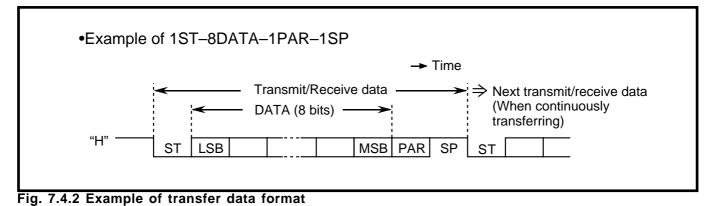

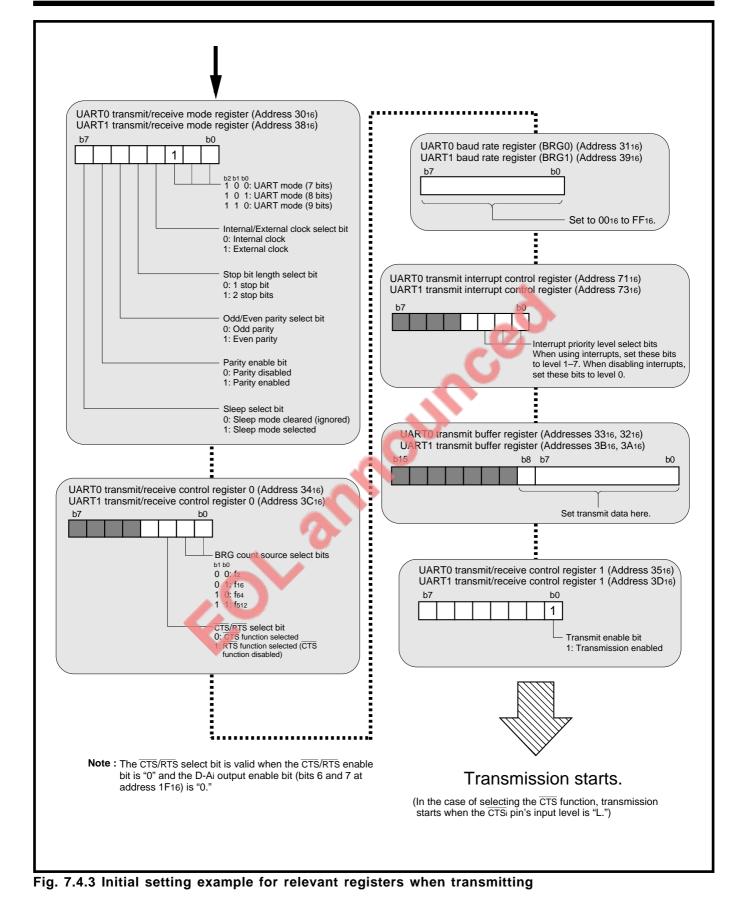

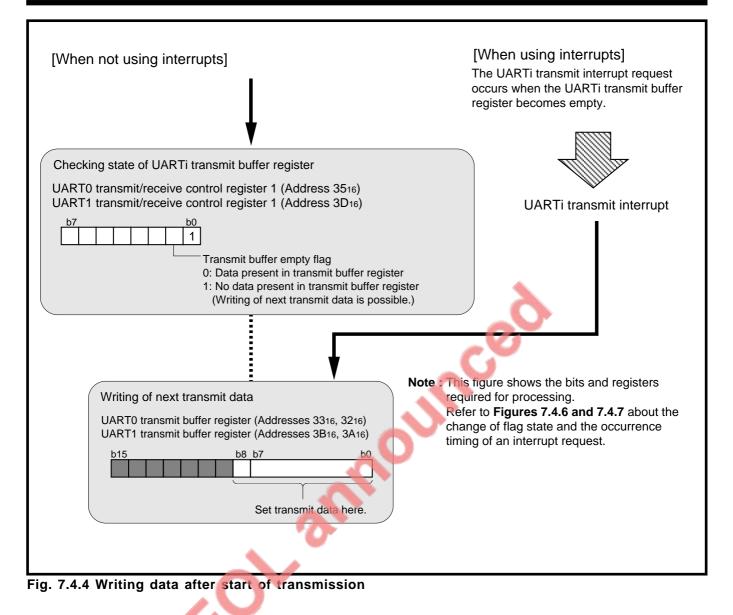

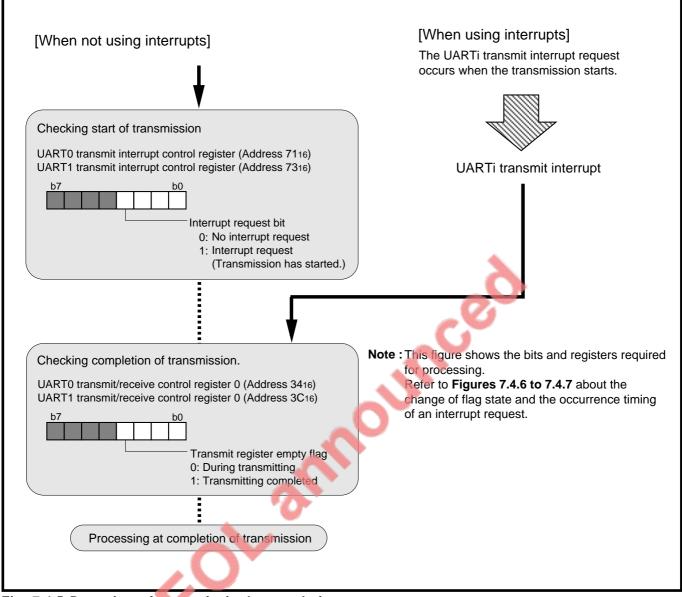

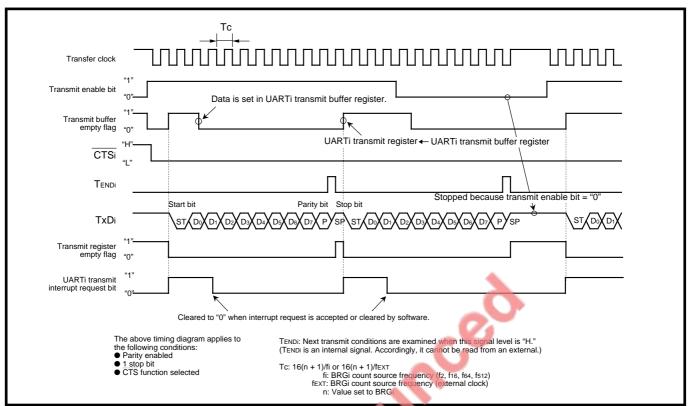

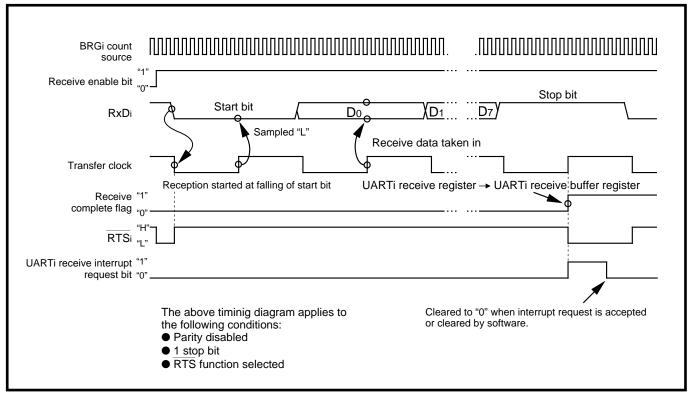

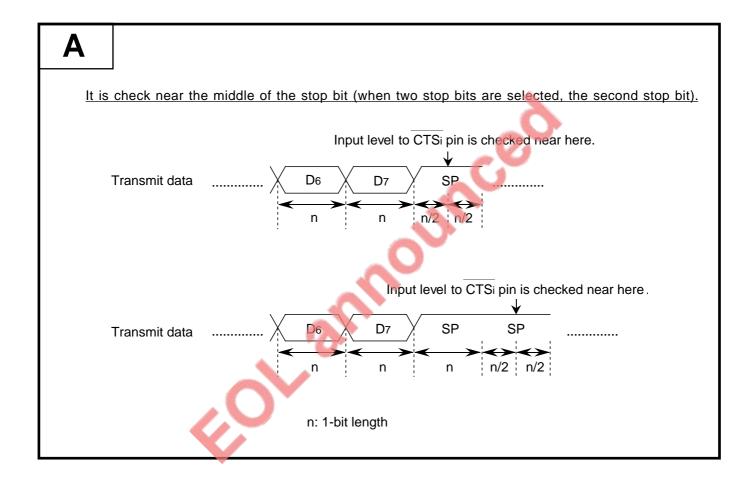

| 7.4 Clock asynchronous serial I/O (UART) mode                                        |        |

| 7.4.1 Transfer rate (frequency of transfer clock)                                    |        |

| 7.4.2 Transfer data format                                                           |        |

| 7.4.3 Method of transmission                                                         |        |

| 7.4.4 Transmit operation                                                             |        |

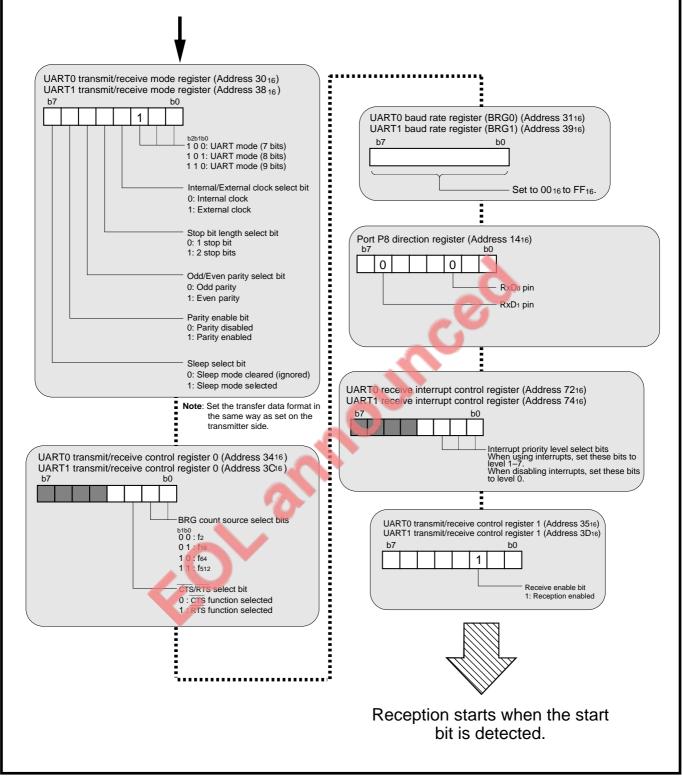

| 7.4.5 Method of reception                                                            |        |

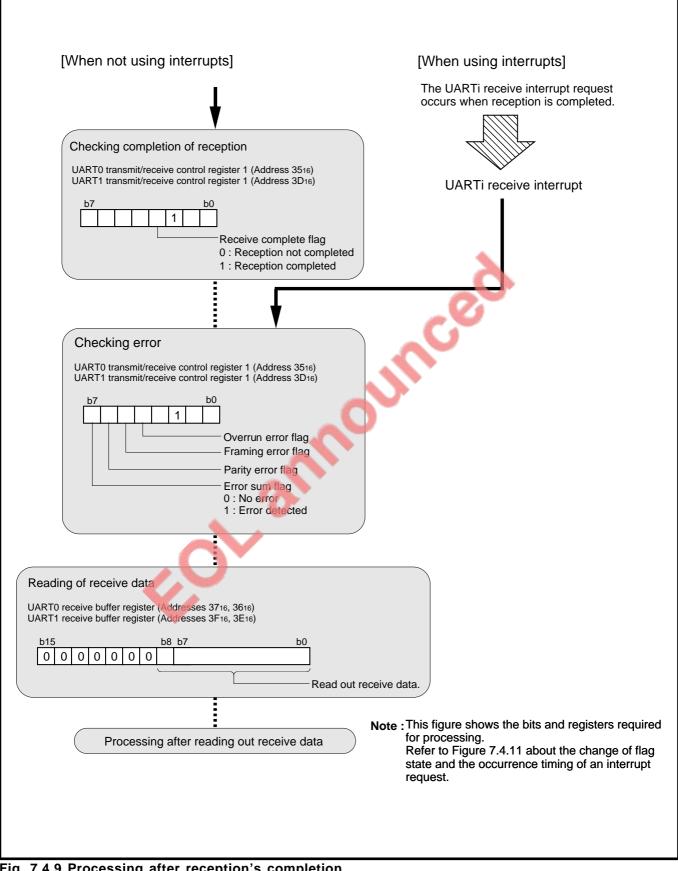

| 7.4.6 Receive operation                                                              |        |

| 7.4.7 Process on detecting error                                                     |        |

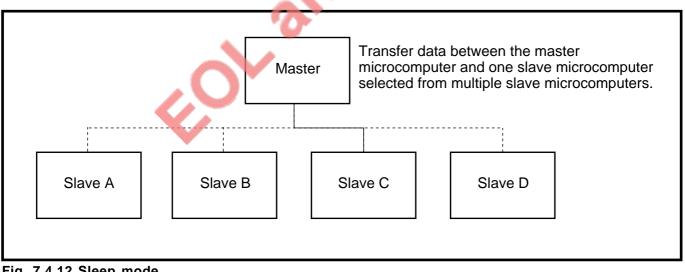

| 7.4.8 Sleep mode                                                                     |        |

| [Precautions when operating in clock asynchronous serial I/O mode]                   | .7-53  |

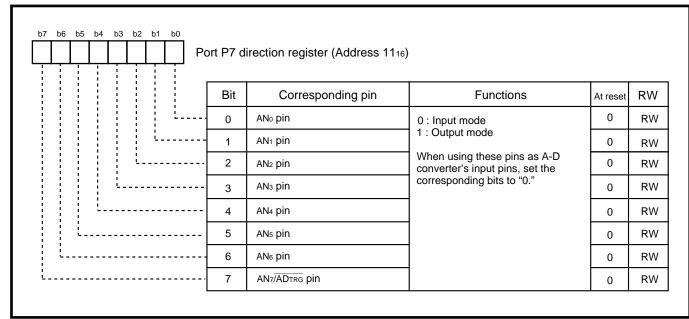

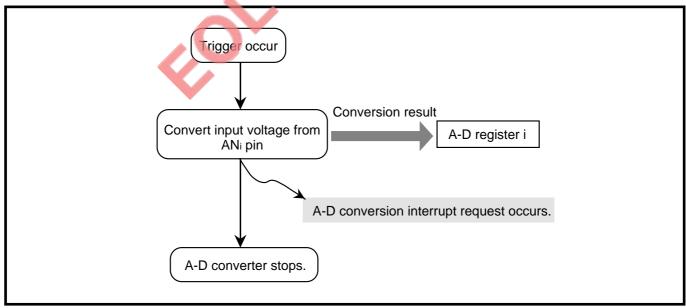

## CHAPTER 8. A-D CONVERTER

| 8.1 Overview                                    | 8-2 |

|-------------------------------------------------|-----|

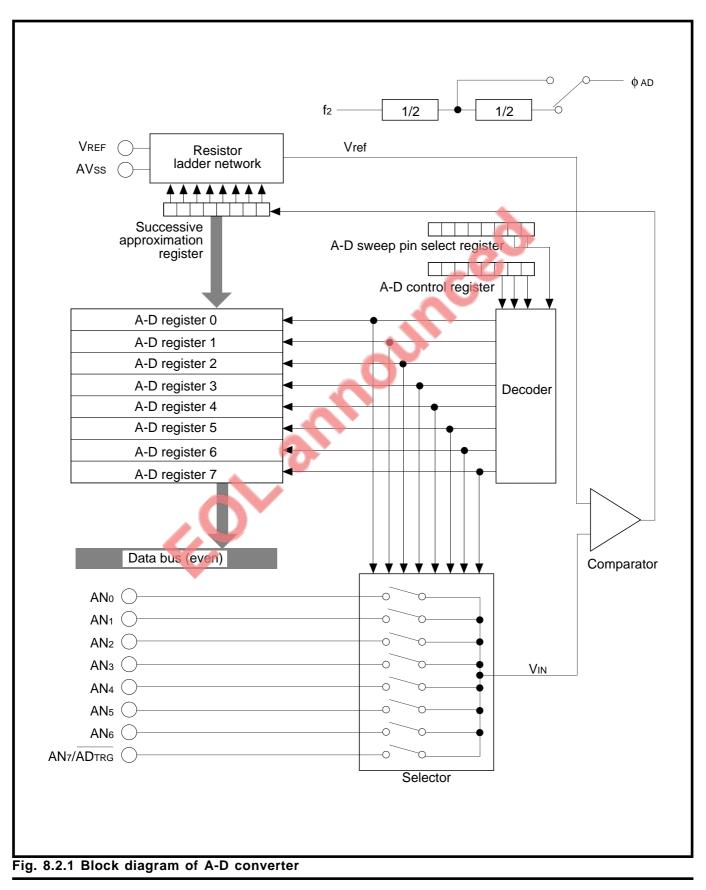

| 8.2 Block description                           | 8-3 |

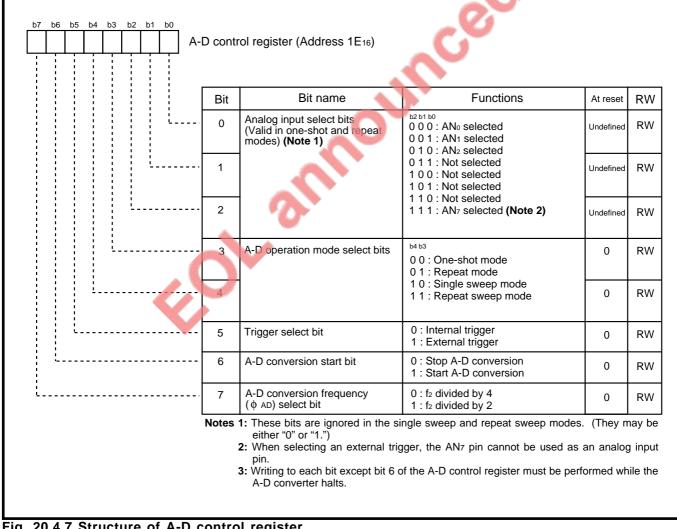

| 8.2.1 A-D control register                      |     |

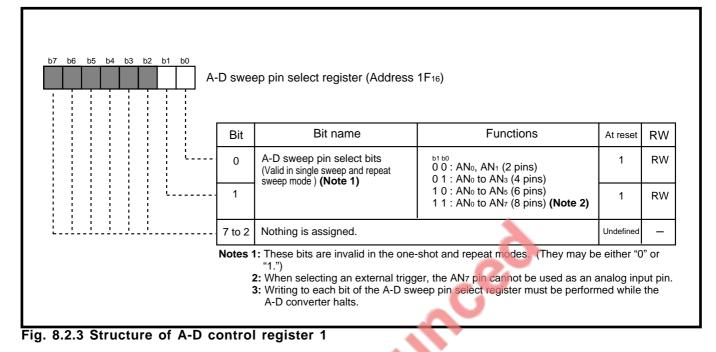

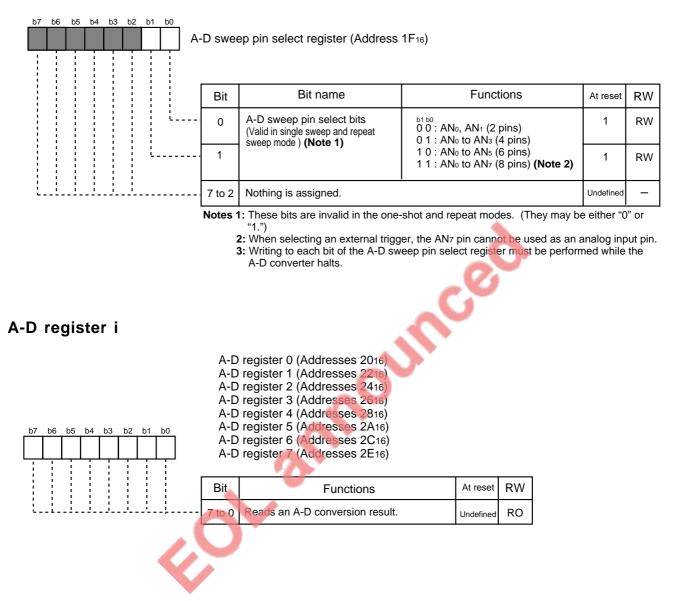

| 8.2.2 A-D sweep pin select register             |     |

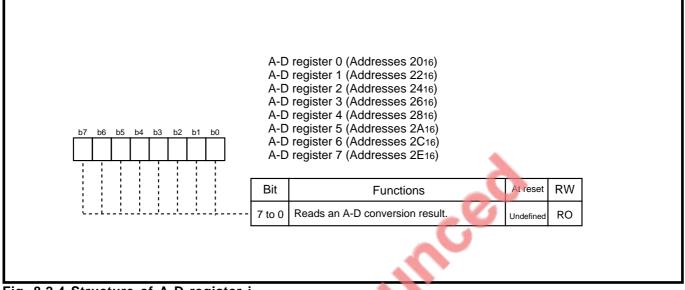

| 8.2.3 A-D register i (i = 0 to 7)               |     |

| 8.2.4 A-D conversion interrupt control register |     |

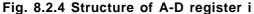

| 8.2.5 Port P7 direction register                |     |

| 5                                               |     |

## **Table of Contents**

| ••• • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-10                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

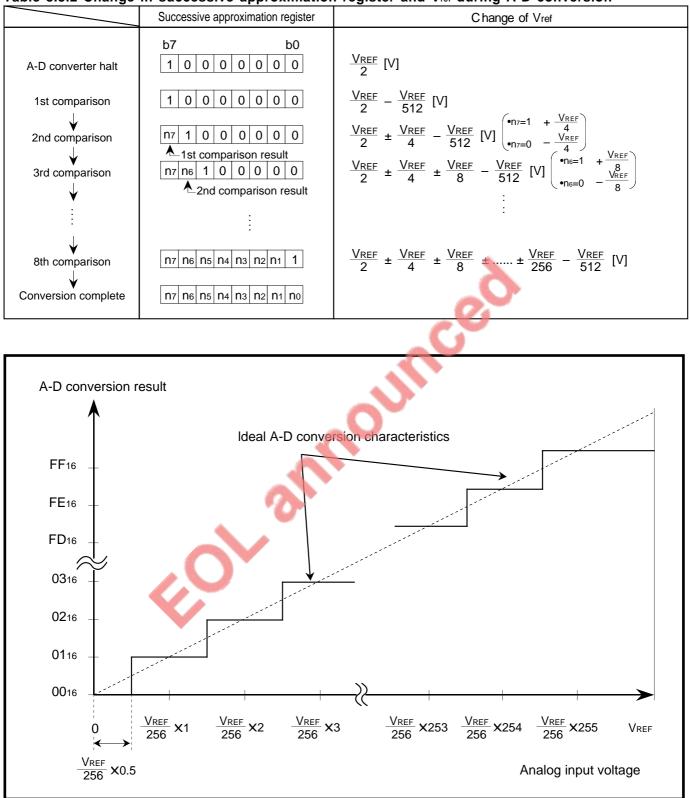

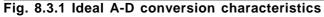

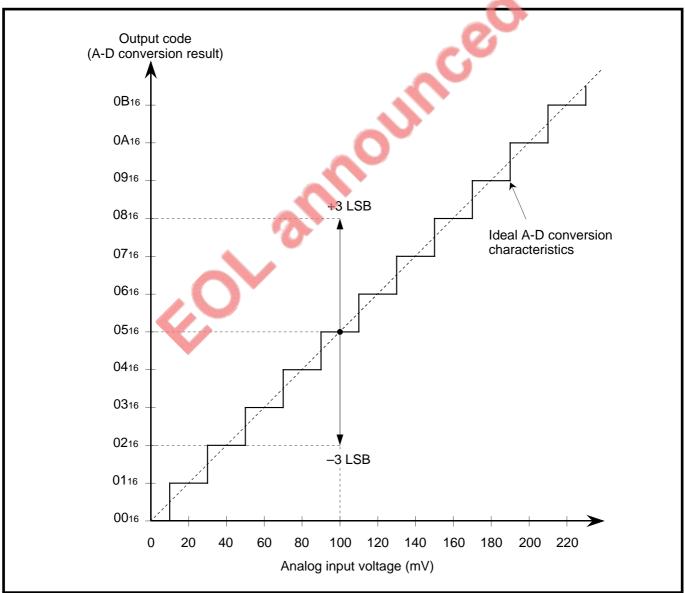

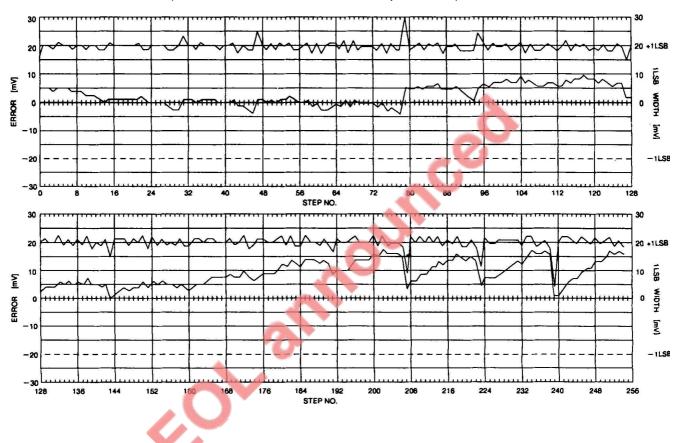

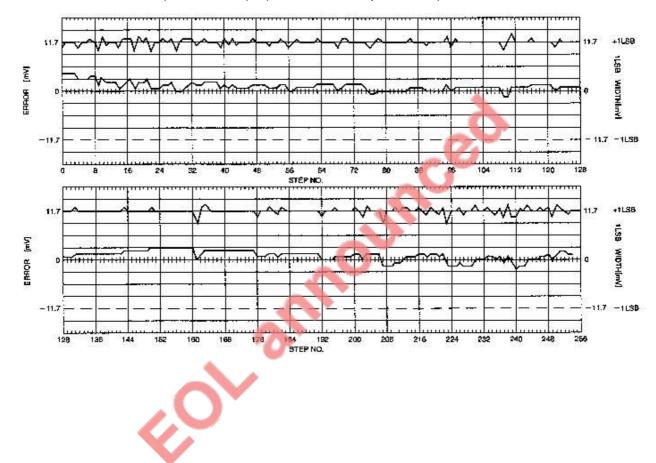

| 8.4 Absolute accuracy and differential non-linearity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                          |

| 8.4.1 Absolute accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-12                                                                                                                     |

| 8.4.2 Differential non-linearity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-13                                                                                                                     |

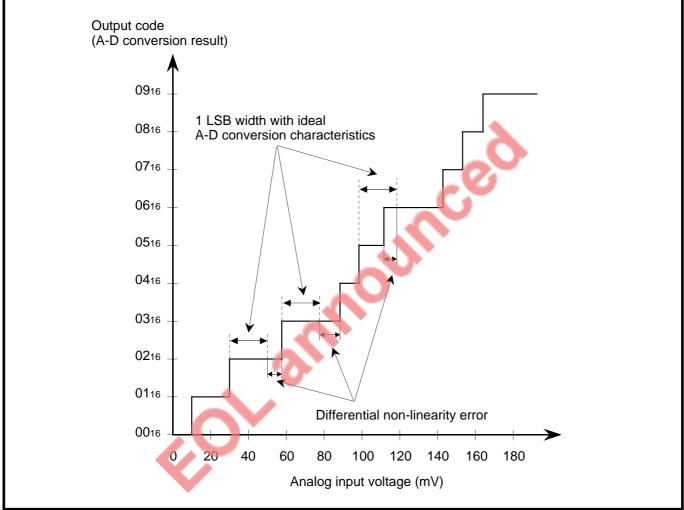

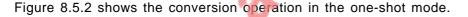

| 8.5 One-shot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                          |

| 8.5.1 Settings for one-shot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

| 8.5.2 One-shot mode operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

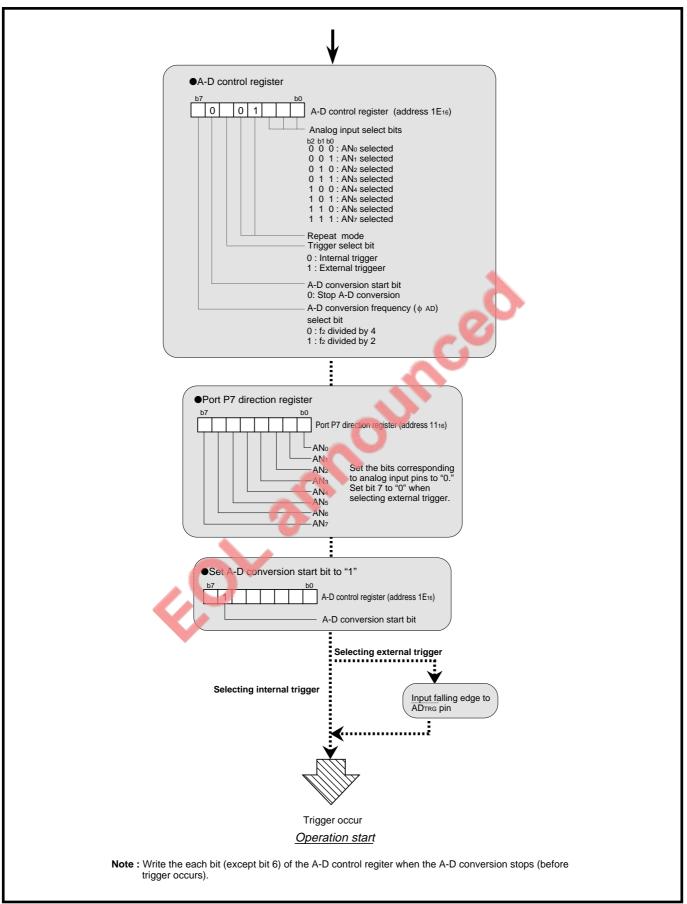

| 8.6 Repeat mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |

| 8.6.1 Settings for repeat mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                          |

| 8.6.2 Repeat mode operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                          |

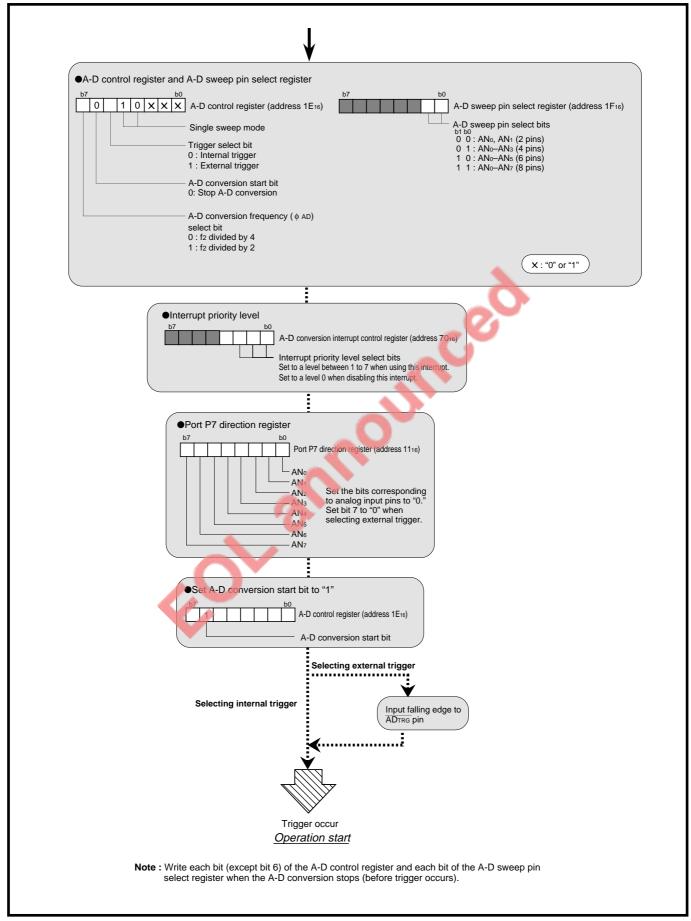

| 8.7 Single sweep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 8.7.1 Settings for single sweep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |

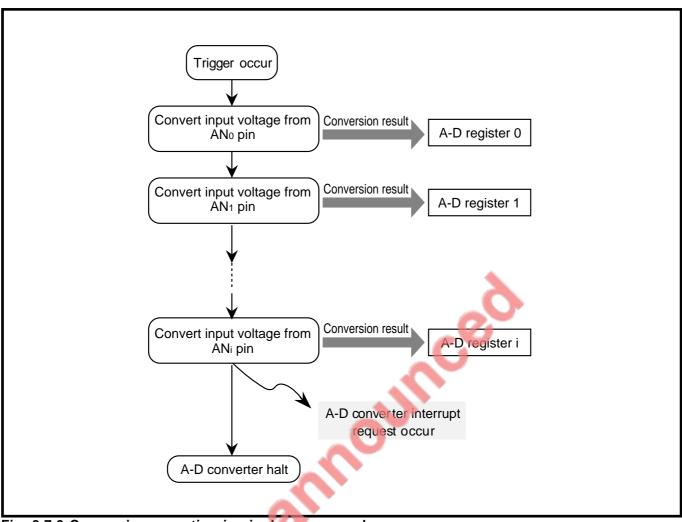

| 8.7.2 Single sweep mode operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

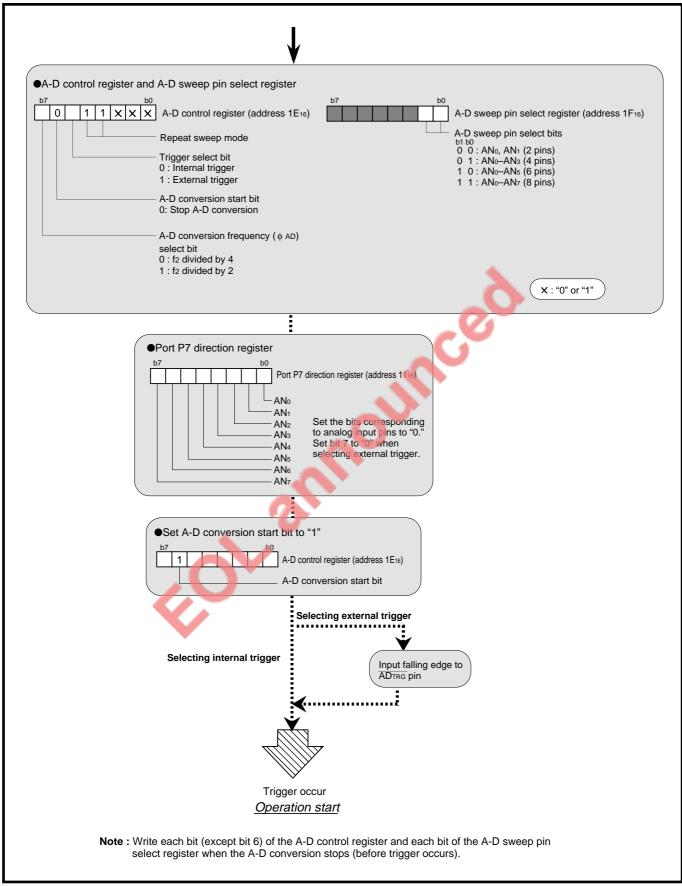

| 8.8 Repeat sweep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 8.8.1 Settings for repeat sweep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |

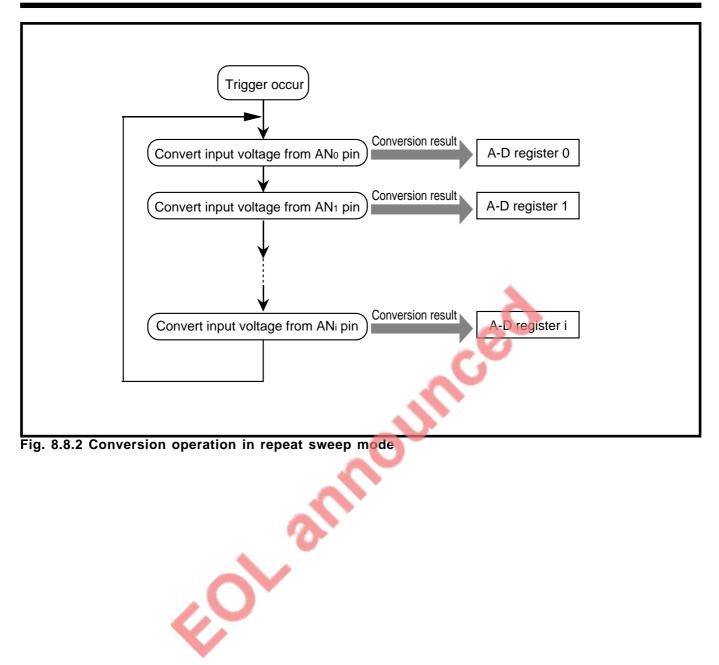

| 8.8.2 Repeat sweep mode operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| 8.9 Precautions when using A-D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-28                                                                                                                     |

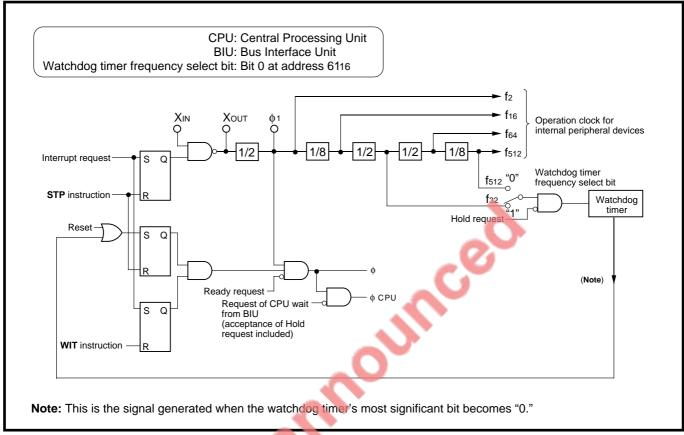

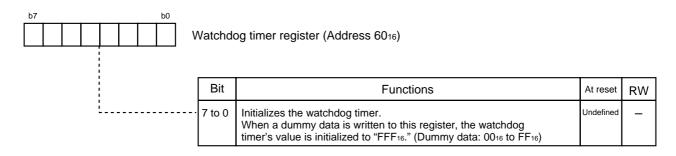

| CHAPTER 9. WATCHDOG TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |

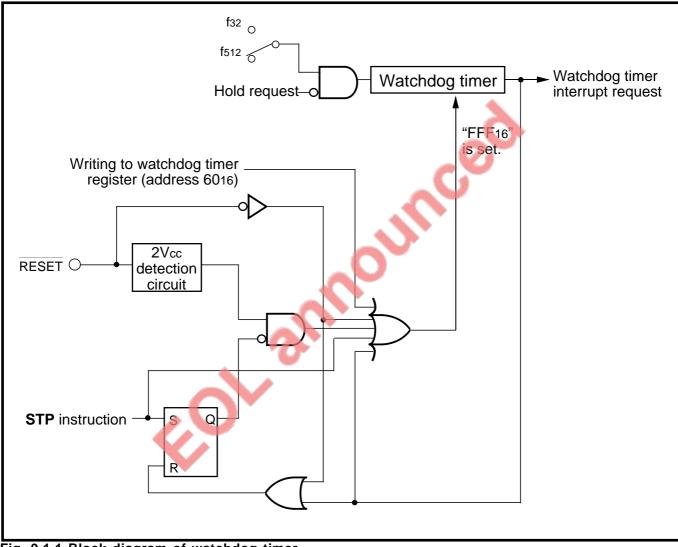

| 9.1 Block description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 9.1.1 Watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |

| 9.1.2 Watchdog timer frequency select register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                          |

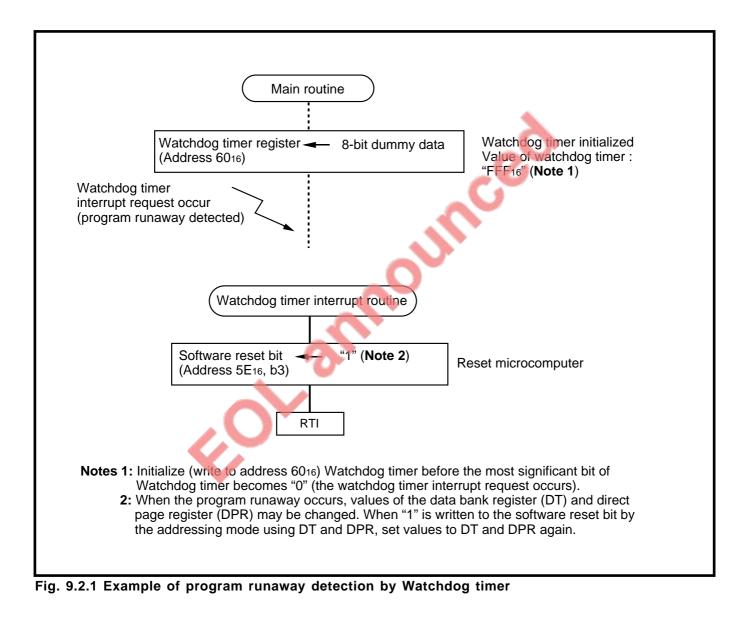

| 9.2 Operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

| 9.2.1 Basic operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 9.2.2 Operation in Stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |

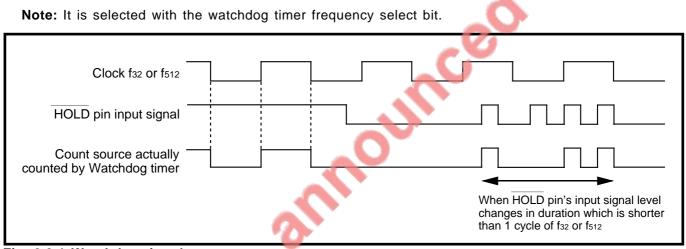

| 9.2.3 Operation in Hold state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| 9.3 Precautions when using watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

| CHAPTER 10. STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |

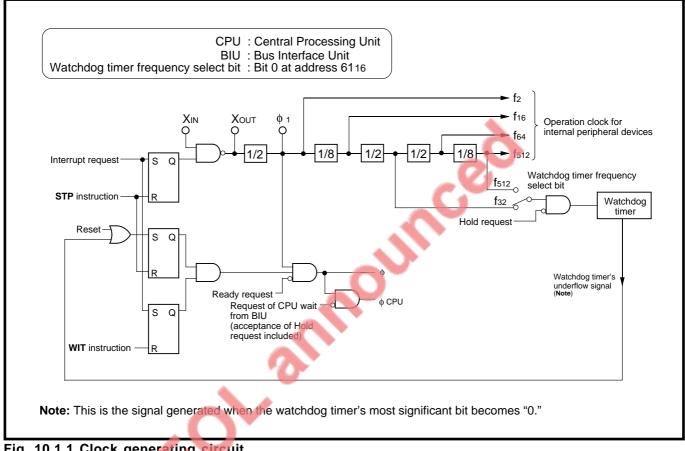

| 10.1 Clock generating circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| 10.2 Operation description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                          |

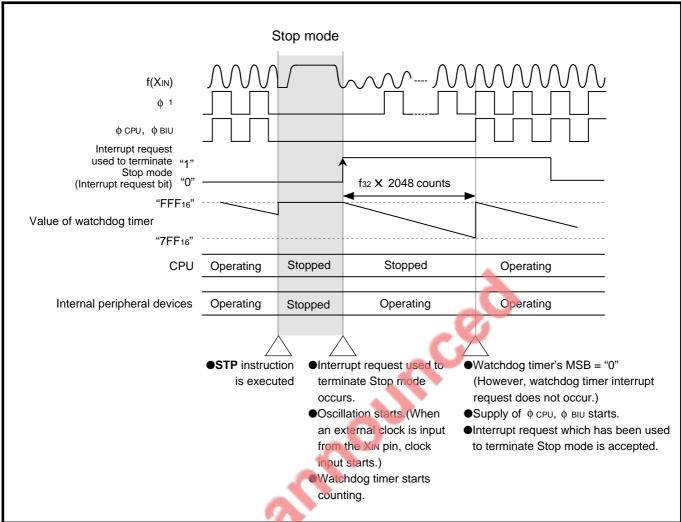

| 10.2.1 Termination by interrupt request occurrence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |

| 10.2.2 Termination by hardware reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |

| 10.2.2 Termination by hardware reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |

| 10.3 Precautions for Stop mode<br>CHAPTER 11. WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10-5<br><b>10-6</b>                                                                                                      |

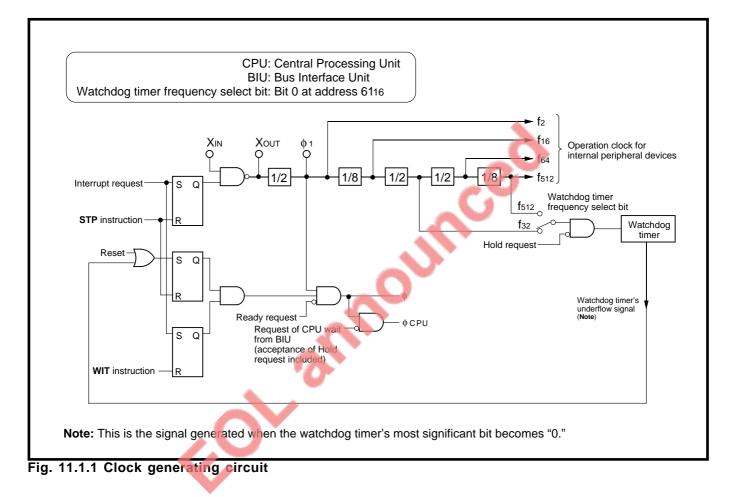

| 10.3 Precautions for Stop mode<br>CHAPTER 11. WAIT MODE<br>11.1 Clock generating circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                          |

| 10.3 Precautions for Stop mode<br>CHAPTER 11. WAIT MODE<br>11.1 Clock generating circuit<br>11.2 Operation description                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode                                                                                                                                                                                                                                                                                |                                                                                                                          |

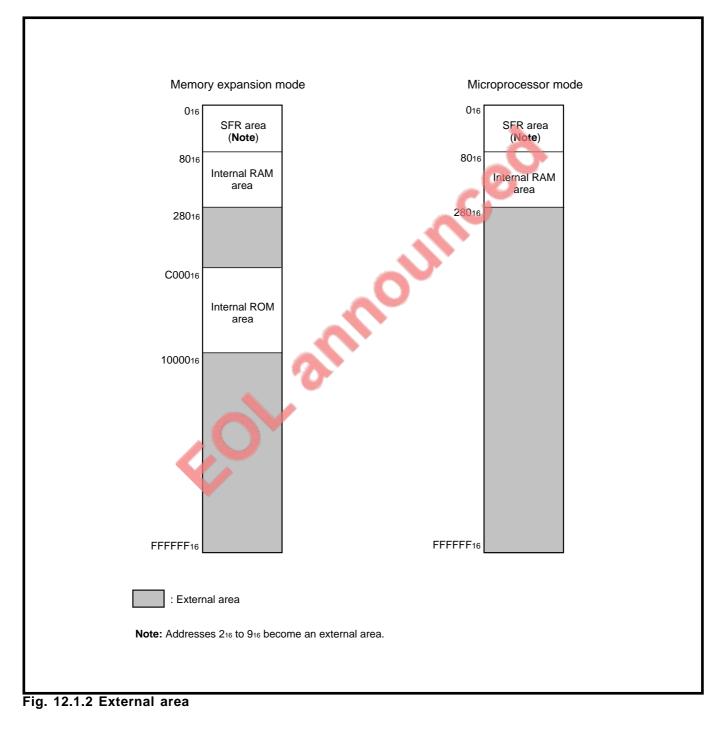

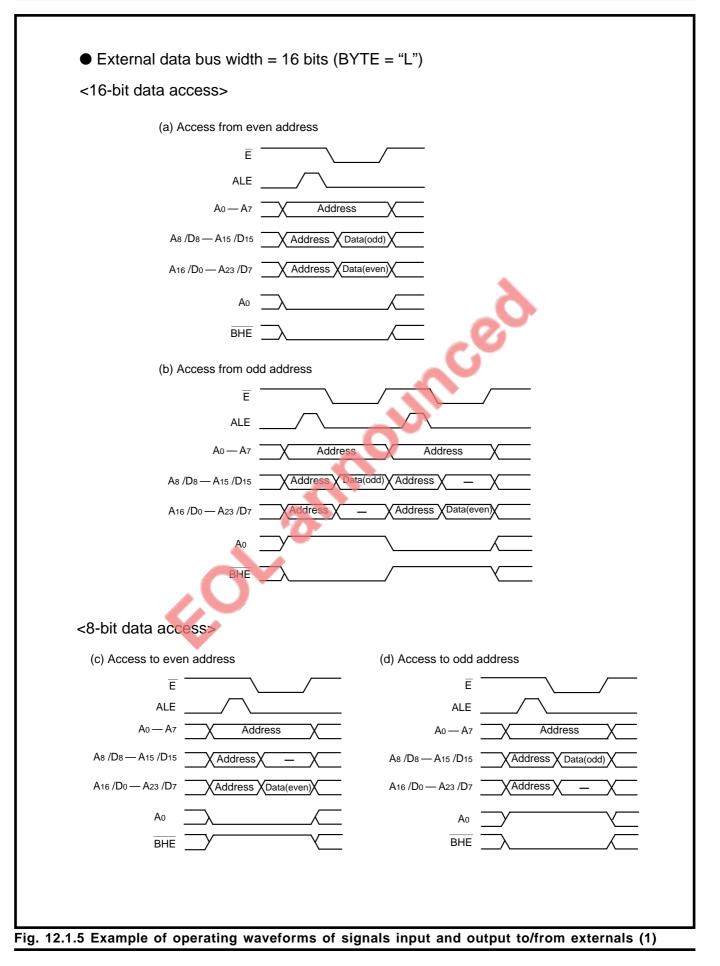

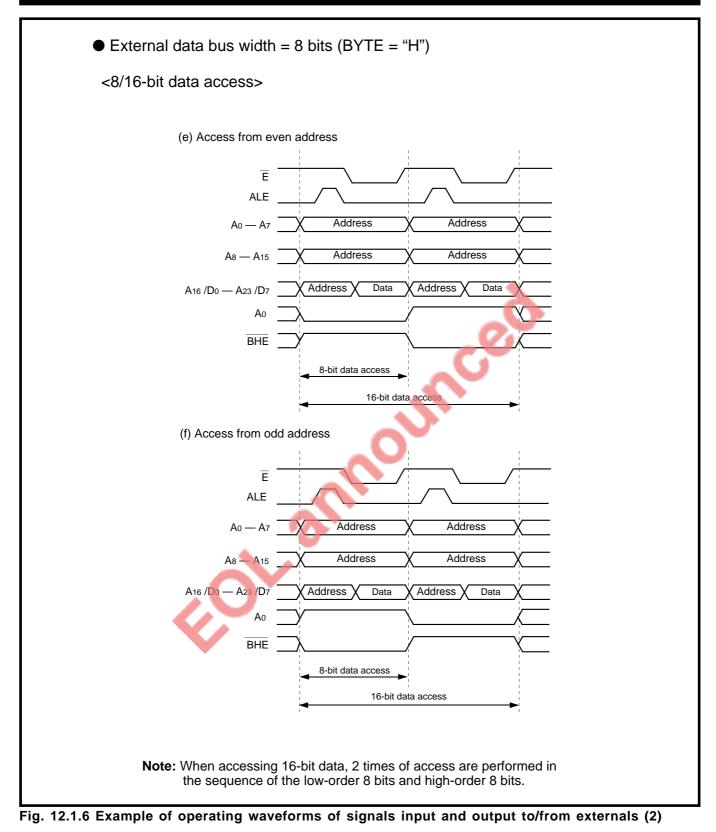

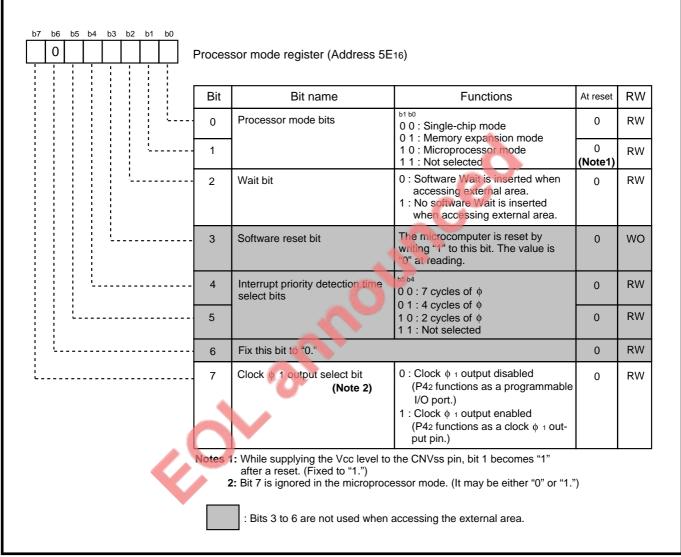

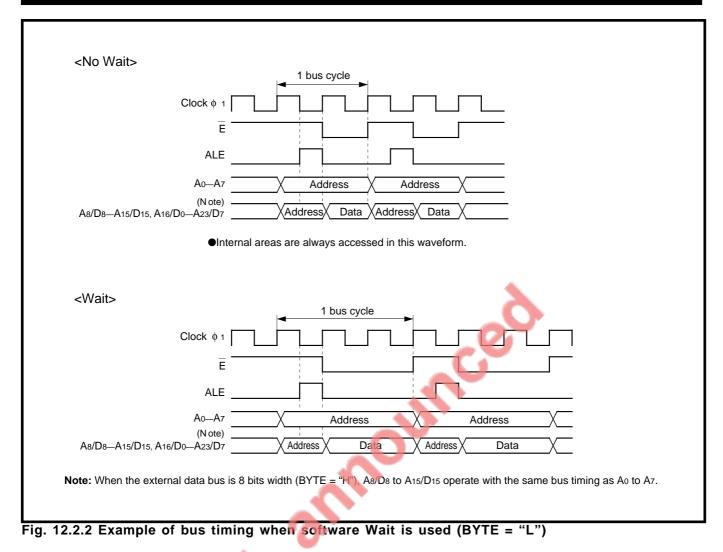

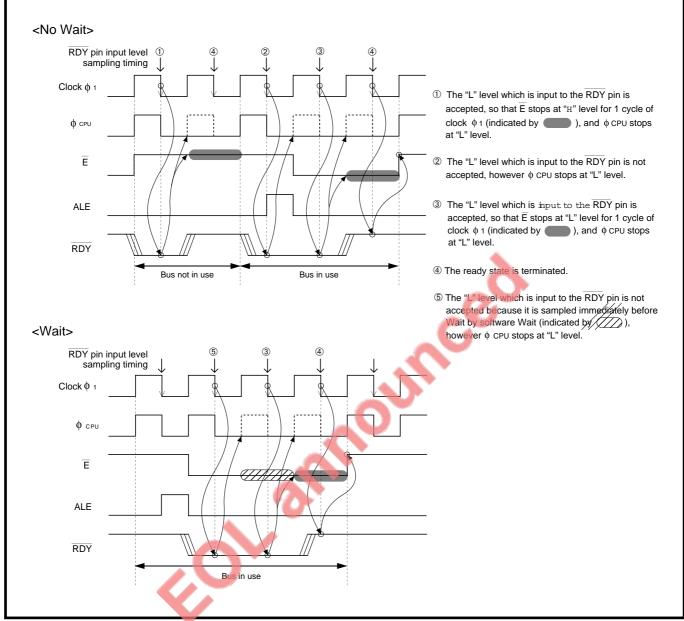

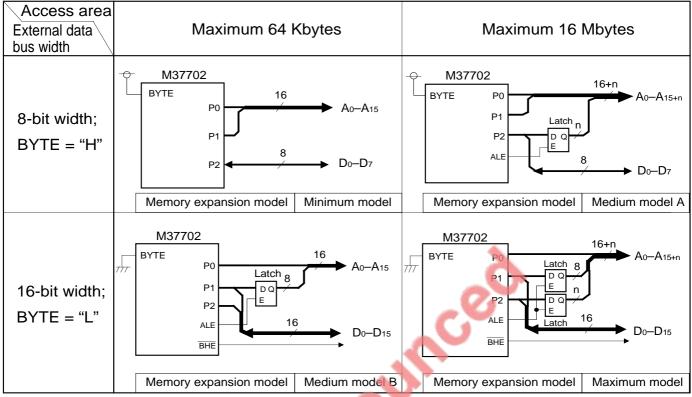

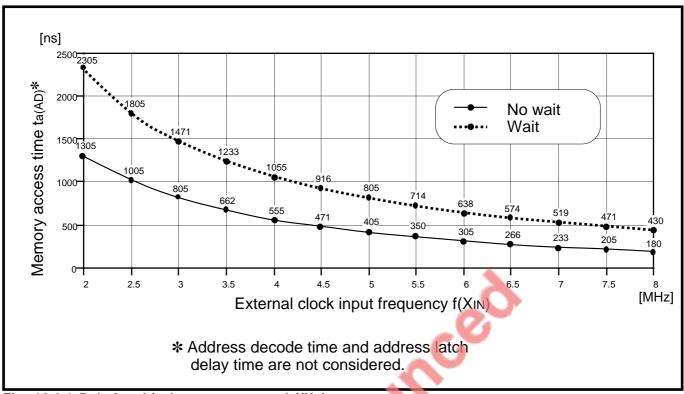

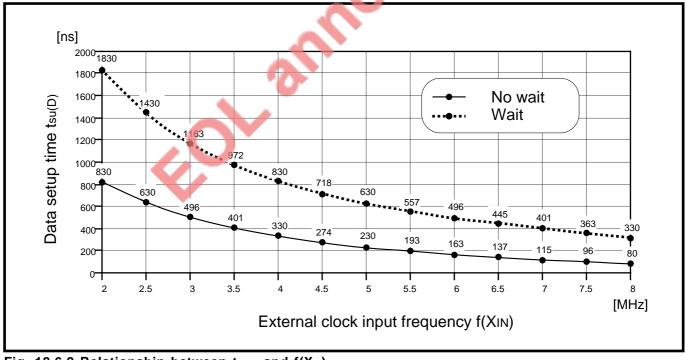

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES                                                                                                                                                                                                                           |                                                                                                                          |

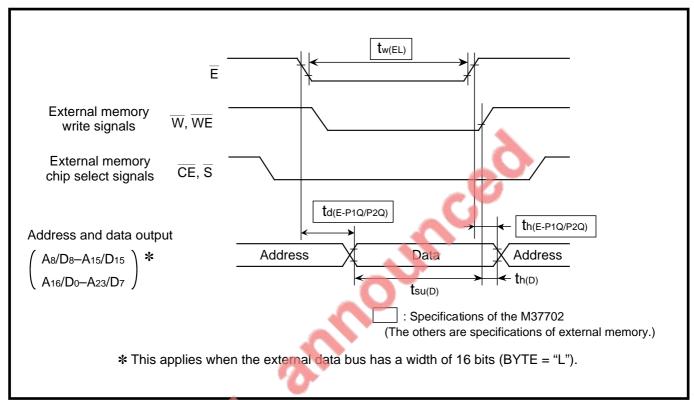

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES         12.1 Signals required for accessing external devices                                                                                                                                                              |                                                                                                                          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES         12.1 Signals required for accessing external devices         12.1.1 Descriptions of signals                                                                                                                       |                                                                                                                          |

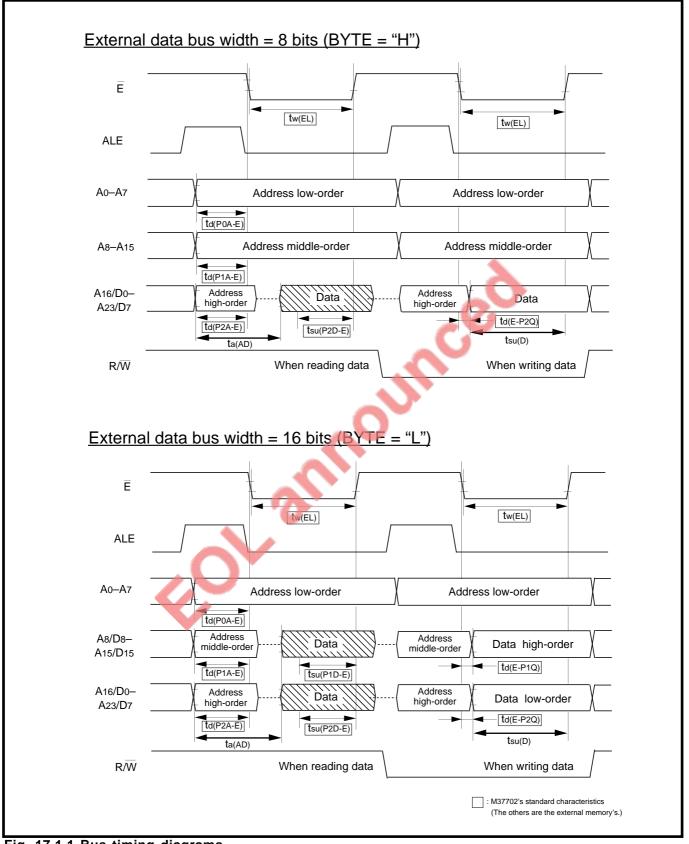

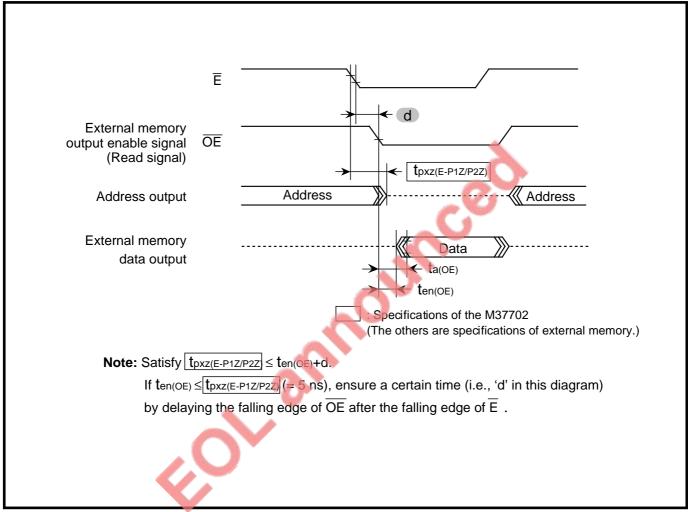

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES         12.1 Signals required for accessing external devices         12.1.1 Descriptions of signals         12.1.2 Operation of bus interface unit (BIU)                                                                  |                                                                                                                          |

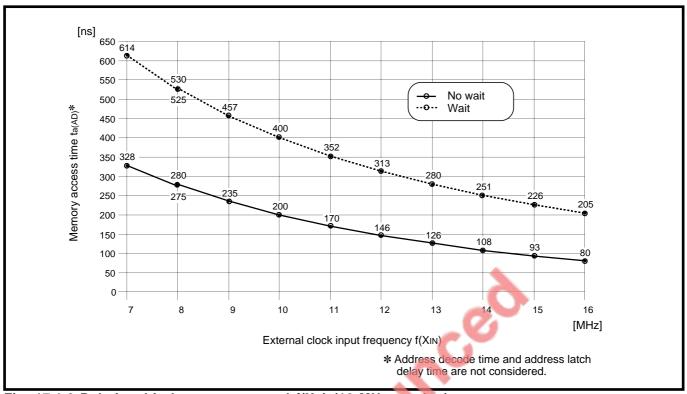

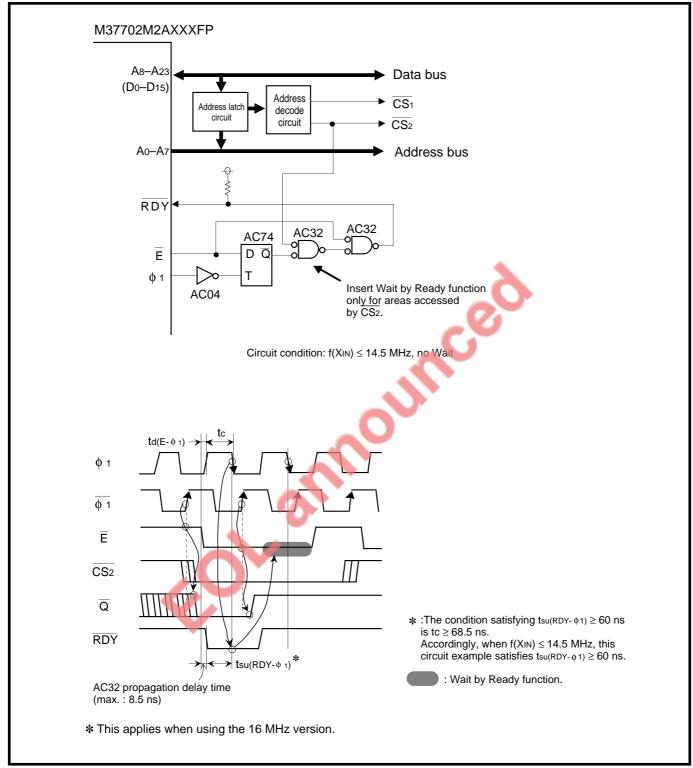

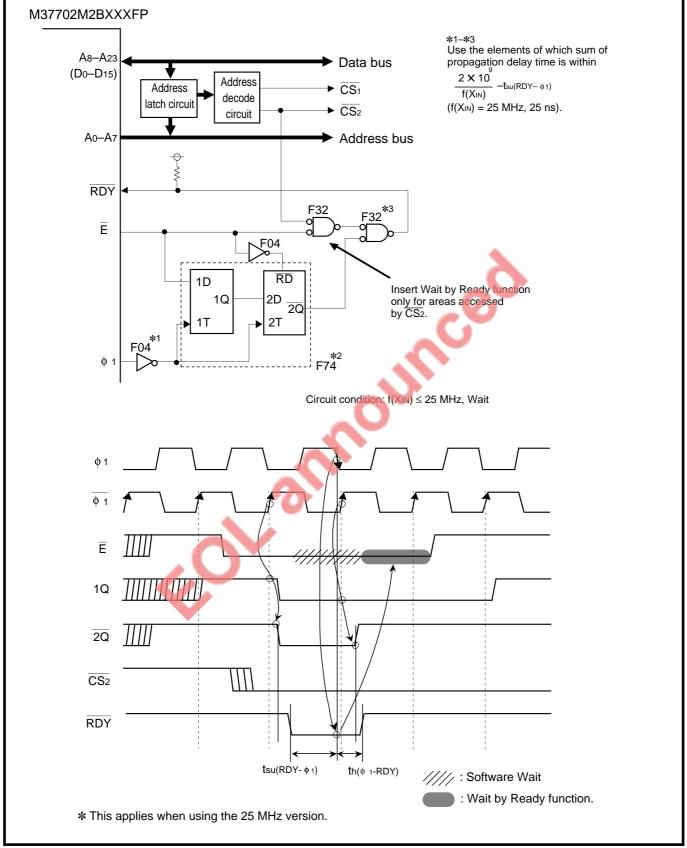

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES         12.1 Signals required for accessing external devices         12.1.1 Descriptions of signals         12.1.2 Operation of bus interface unit (BIU)         12.3 Ready function         12.3.1 Operation description | 10-5<br>10-6<br>11-2<br>11-3<br>11-4<br>11-4<br>11-4<br>11-5<br>11-5<br>12-2<br>12-8<br>12-11<br>12-13<br>12-14          |

| 10.3 Precautions for Stop mode         CHAPTER 11. WAIT MODE         11.1 Clock generating circuit         11.2 Operation description         11.2.1 Termination by interrupt request occurrence         11.2.2 Termination by hardware reset         11.3 Precautions for Wait mode         CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES         12.1 Signals required for accessing external devices         12.1.1 Descriptions of signals         12.1.2 Operation of bus interface unit (BIU)         12.2 Software Wait         12.3 Ready function           | 10-5<br>10-6<br>11-2<br>11-3<br>11-4<br>11-4<br>11-4<br>11-5<br>11-5<br>12-2<br>12-8<br>12-11<br>12-13<br>12-14<br>12-16 |

| CHAPTER 13. RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

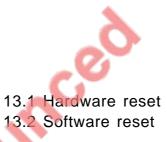

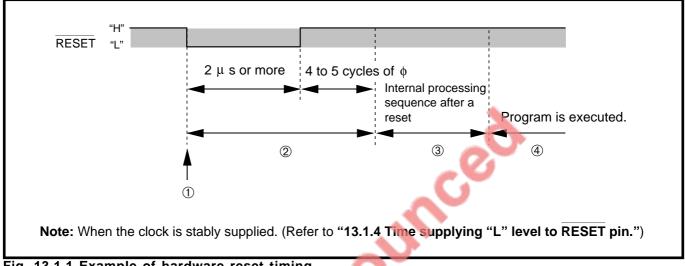

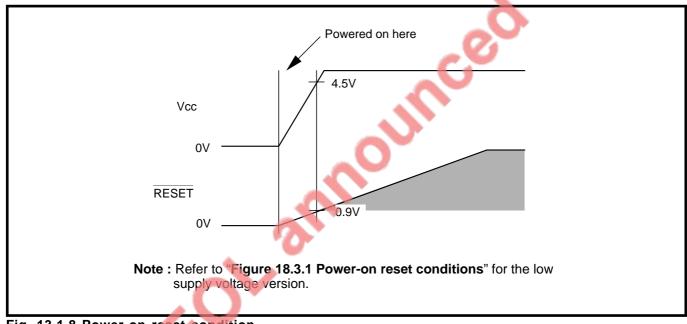

| 13.1 Hardware reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13-2                                                                                                                                                                                                                          |

| 13.1.1 Pin state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                               |

| 13.1.2 State of CPU, SFR area, and internal RAM area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                               |

| 13.1.3 Internal processing sequence after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                               |

| 13.1.4 Time supplying "L" level to RESET pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                               |

| 13.2 Software reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                               |

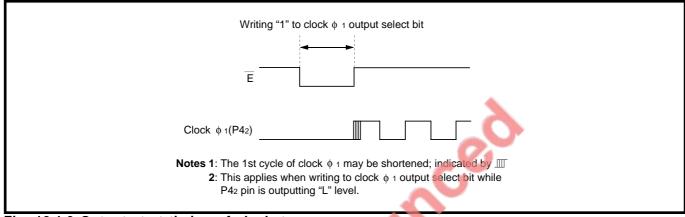

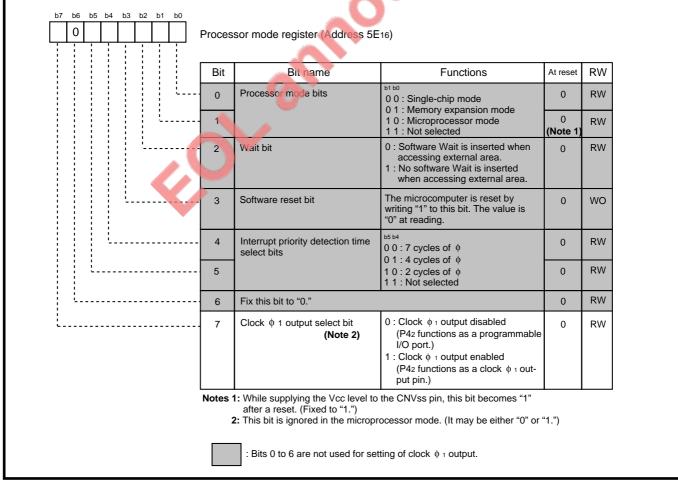

| CHAPTER 14. CLOCK GENERATING CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                               |

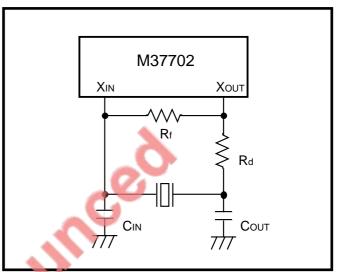

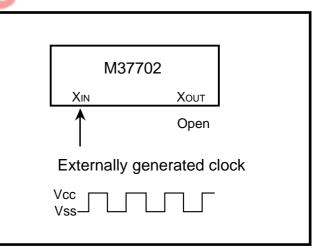

| 14.1 Oscillation circuit example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                               |

| 14.1.1 Connection example using resonator/oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                               |

| 14.1.2 Input example of externally generated clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |

| 14.2 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                               |

| 14.2.1 Clock generated in clock generating circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14-4                                                                                                                                                                                                                          |

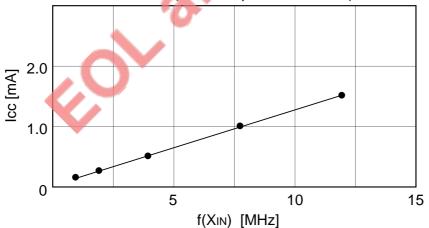

| CHAPTER 15. ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |

| 15.1 Absolute maximum ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |

| 15.2 Recommended operating conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |

| 15.3 Electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                               |

| 15.4 A-D converter characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |