Data Sheet

February 18, 2009

FN6851.0

## 3A Integrated Digital DC-DC Converter

#### **Description**

The ZL2105 is an innovative power conversion and management IC that combines an integrated synchronous step-down DC-DC converter with key power management functions in a small package, resulting in a flexible and integrated solution. Zilker Labs Digital-DC<sup>TM</sup> technology enables unparalleled power management integration while delivering industry-leading performance in a tiny footprint.

The ZL2105 can provide an output voltage from 0.6 V to 5.5 V from an input voltage between 4.5 V and 14 V. Internal 4.5 A low  $R_{\rm DS(ON)}$  synchronous power MOSFETs enable the ZL2105 to deliver continuous loads up to 3 A with high efficiency, and an internal Schottky bootstrap diode further reduces discrete component count. The ZL2105 also supports phase spreading for reduced system capacitance.

Power management features such as digital softstart delay and ramp, sequencing, tracking, and margining can be configured by simple pinstrapping or through an on-chip serial port. The ZL2105 uses standard PMBus<sup>TM</sup> protocol for communicating with other devices to provide intelligent system power management.

#### **Features**

#### **Power Conversion**

- High efficiency

- 3 A continuous output current

- Integrated MOSFET switches

- 4.5 V to 14 V input range

- 0.54 V to 5.5 V output range (with margin)

- ±1% output voltage accuracy

- 200 kHz to 2 MHz switching frequency

- Supports phase spreading

- Small footprint (6 x 6 mm QFN package)

#### Power Management

- Digital soft start/stop

- Precision delay and ramp-up

- Power good/enable

- Voltage tracking, sequencing, and margining

- Output voltage/current monitoring

- Thermal monitor w/ shutdown

- Non-volatile memory

- I<sup>2</sup>C/SMBus<sup>TM</sup> communication bus

- PMBus compatible

#### **Applications**

- Telecom and storage equipment

- Digital set-top box

- Industrial supplies

- 12 V distributed power systems

- Point of load converters

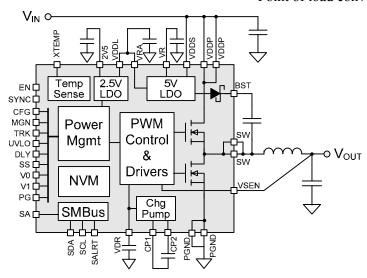

Figure 1. Block Diagram

# **Table of Contents**

| 1. Electrical Characteristics                              |    |

|------------------------------------------------------------|----|

| 2. Pin Descriptions                                        |    |

| 3. Typical Application Circuit                             | 8  |

| 4. ZL2105 Overview                                         |    |

| 4.1 Digital-DC Architecture                                |    |

| 4.2 Power Conversion Overview                              | 11 |

| 4.3 Power Management Overview                              | 12 |

| 4.4 Multi-mode Pins                                        | 12 |

| 5. Power Conversion Functional Description                 | 13 |

| 5.1 Internal Bias Regulators and Input Supply Connections  |    |

| 5.2 High-side Driver Boost Circuit                         | 13 |

| 5.3 Low-side Driver Supply Options                         |    |

| 5.4 Dual Input Supply Configuration                        | 14 |

| 5.5 Output voltage Selection                               | 15 |

| 5.6 Start-up Procedure                                     | 15 |

| 5.7 Soft Start Delay and Ramp Times                        | 16 |

| 5.8 Switching Frequency and PLL                            | 17 |

| 5.9 Component Selection                                    | 19 |

| 5.10 Current Sensing and Current Limit Threshold Selection | 22 |

| 5.11 Loop Compensation                                     | 22 |

| 5.12 Non-linear Response (NLR) Settings                    | 23 |

| 5.13 Efficiency Optimized Drive Dead-time Control          |    |

| 6. Power Management Functional Description                 | 24 |

| 6.1 Input Undervoltage Lockout                             |    |

| 6.2 Power Good (PG) and Output Overvoltage Protection      |    |

| 6.3 Output Overvoltage Protection                          | 25 |

| 6.4 Output Pre-Bias Protection                             |    |

| 6.5 Output Overcurrent Protection                          |    |

| 6.6 Thermal Overload Protection                            | 26 |

| 6.7 Voltage Tracking                                       | 27 |

| 6.8 Voltage Margining                                      |    |

| 6.9 I <sup>2</sup> C/SMBus Communications                  |    |

| 6.10 I <sup>2</sup> C/SMBus Device Address Selection       |    |

| 6.11 Phase Spreading                                       | 29 |

| 6.12 Output Sequencing                                     |    |

| 6.13 Monitoring via I <sup>2</sup> C/SMBus                 |    |

| 6.14 Temperature Monitoring using the XTEMP Pin            | 31 |

| 6.15 Non-Volatile Memory and Device Security Features      |    |

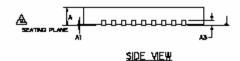

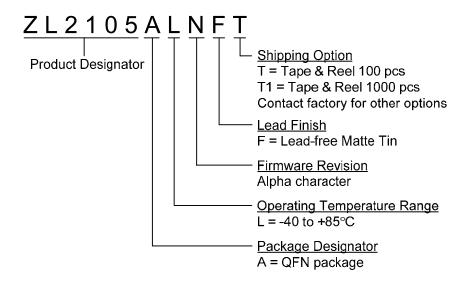

| 7. Package Dimensions                                      | 33 |

| 8. Ordering Information                                    |    |

| 9. Related Documentation                                   | 34 |

| 10 Pavision History                                        | 25 |

# 1. Electrical Characteristics

#### **Table 1. Absolute Maximum Ratings**

Voltage measured with respect to SGND. Operating beyond these limits may cause permanent damage to the device. Functional operation beyond the Recommended Operating Conditions is not implied.

| Parameter                         | Pin                                                                                           | Comments        | Value       | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------|-----------------|-------------|------|

| DC Supply Voltage                 | VDDP, VDDS, VDR                                                                               |                 | -0.3 to 17  | V    |

| Logic Supply Voltage              | VDDL                                                                                          | Optional        | -0.3 to 6.5 | V    |

| High Side Supply Voltage          | BST                                                                                           |                 | -0.3 to 30  | V    |

| High Side Boost Voltage           | BST - SW                                                                                      |                 | -0.3 to 8   | V    |

| Switch Node Current               | SW                                                                                            | Sink or Source  | 4.5         | A    |

| Internal Drive References         | VR, VRA                                                                                       |                 | -0.3 to 6.5 | V    |

| Internal 2.5 V Reference          | V25                                                                                           |                 | -0.3 to 3   | V    |

| Logic I/O Voltage                 | EN, MGN, PG, SDA, SCL, SA,<br>SALRT, SS, DLY, SYNC,<br>VTRK, UVLO, V(0,1), ILIM,<br>VSEN, CFG |                 | -0.3 to 6.5 | V    |

| Ground Differential               | DGND - SGND<br>PGND - SGND                                                                    |                 | ±0.3        | V    |

| MOSFET Drive Reference<br>Current | VR                                                                                            |                 | 30          | mA   |

| Analog Reference Current          | VRA                                                                                           |                 | 150         | mA   |

| 2.5 V Reference Current           | V25                                                                                           |                 | 60          | mA   |

| Junction Temperature              | _                                                                                             |                 | -55 to 150  | °C   |

| Storage Temperature               | _                                                                                             |                 | -55 to 150  | °C   |

| Lead Temperature                  | All                                                                                           | Soldering, 10 s | 300         | °C   |

**Table 2. Recommended Operating Conditions and Thermal Information**

| Parameter                                          | Symbol               | Min  | Тур | Max | Unit |

|----------------------------------------------------|----------------------|------|-----|-----|------|

| Input Supply Voltage Range, VDDP, VDDS             | VDDS tied to VR, VRA | 4.5  | _   | 5.5 | V    |

| (See Figure 8)                                     | VR, VRA floating     | 5    | _   | 14  | V    |

| Logic Supply Voltage Range, VDDL                   | VDDL (optional)      | 3.0  | _   | 5.5 | V    |

| Internal Driver Supply, VDR                        | VDR                  | 10   | _   | 14  | V    |

| Output Voltage Range <sup>1</sup>                  | $V_{OUT}$            | 0.54 | _   | 5.5 | V    |

| Operating Junction Temperature Range               | $T_{J}$              | -40  | _   | 125 | °C   |

| Junction to Ambient Thermal Impedance <sup>2</sup> | $\Theta_{ m JA}$     | _    | 35  | _   | °C/W |

| Junction to Case Thermal Impedance <sup>3</sup>    | $\Theta_{ m JC}$     | _    | 5   | _   | °C/W |

#### Notes:

- 1. Includes margin

- 2.  $\Theta_{JA}$  is measured in free air with the device mounted on a multi-layer FR4 test board and the exposed metal pad soldered to a low impedance ground plane using multiple vias.

- 3. For  $\Theta_{JC}$ , the "case" temperature is measured at the center of the exposed metal pad. See Figure 4 for thermal derating.

**Table 3. Electrical Specifications**

$V_{DDP} = V_{DDS} = 12 \text{ V}, T_A = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  unless otherwise noted. Typical values are at  $T_A = 25 ^{\circ}\text{C}$ .

| Parameter                                    | Conditions                                                              | Min   | Тур     | Max      | Unit     |

|----------------------------------------------|-------------------------------------------------------------------------|-------|---------|----------|----------|

| Input and Supply Characteristics             |                                                                         |       |         |          |          |

| I <sub>DDS</sub> supply current              | $f_{SW} = 200 \text{ kHz}, \text{ no load}$                             | -     | 2       | 3        | mA       |

| IDDS Supply current                          | $f_{SW} = 1$ MHz, no load                                               | _     | 5       | 6        | mA       |

| I <sub>DDL</sub> supply current              | $f_{SW} = 200 \text{ kHz}$ , no load $f_{SW} = 1 \text{ MHz}$ , no load | _     | 8<br>10 | 16<br>20 | mA<br>mA |

| I <sub>DDS</sub> shutdown current            | EN = 0 V, VDDL tied to VRA, No I <sup>2</sup> C/SMBus activity          | _     | 0.7     | 1        | mA       |

| I <sub>DDL</sub> shutdown current            | EN = 0  V,  VDDL = 5  V,<br>No I <sup>2</sup> C/SMBus activity          | _     | 225     | 500      | μΑ       |

| VR reference output voltage                  | $V_{DD} > 5.5 \text{ V}, I_{VR} < 5 \text{ mA}$                         | 4.5   | 5.2     | 5.5      | V        |

| VRA reference output voltage                 | $V_{DD} > 5.5 \text{ V}, I_{VRA} < 35 \text{ mA}$                       | 4.5   | 5.2     | 5.5      | V        |

| V25 reference output voltage                 | $I_{V25} < 50 \text{ mA}$                                               | 2.25  | 2.5     | 2.75     | V        |

| Output Characteristics                       |                                                                         |       |         |          |          |

| Output Current                               |                                                                         | _     | _       | 3        | A        |

| Output voltage adjustment range <sup>1</sup> | $V_{IN} > V_{OUT}$                                                      | 0.6   | -       | 5.0      | V        |

| Output walks a such sint was lating          | Set using resistors                                                     | _     | 10      | _        | mV       |

| Output voltage setpoint resolution           | Set using I <sup>2</sup> C/SMBus                                        | _     | ±0.025  | _        | % FS     |

| VSEN output voltage accuracy                 | Includes line, load, temp                                               | -1    | _       | 1        | %        |

| VSEN input bias current                      | VSEN = 5.5 V                                                            | _     | 100     | 200      | μA       |

|                                              | Set using DLY pin or resistor                                           | 7     | _       | 200      | ms       |

| Soft start delay duration range <sup>2</sup> | Set using I <sup>2</sup> C/SMBus                                        | 0.007 | _       | 500      | S        |

| Soft start delay duration accuracy           |                                                                         | _     | 6       | _        | ms       |

| C-C-t-t-t-t-t-t-t-t-t-t-t-t-t-t-t-t-t-t      | Set using SS pin                                                        | 10    | _       | 100      | ms       |

| Soft start ramp duration range               | Set using resistor or via I <sup>2</sup> C                              | 0     | _       | 200      | ms       |

| Soft start ramp duration accuracy            |                                                                         | _     | 100     | _        | μs       |

| Logic Input/Output Characteristics           |                                                                         | •     | •       |          |          |

| Logic input bias current                     | During configuration restore                                            | -1    | _       | 1        | mA       |

| (EN,PG,SCL,SDA,SALRT)                        | Operating                                                               | -10   | _       | 10       | μA       |

| MGN pin current                              |                                                                         | -1    | _       | 1        | mA       |

| Logic input low, V <sub>IL</sub>             |                                                                         | _     | _       | 0.8      | V        |

| Logic input OPEN (N/C)                       | Multi-mode logic pins                                                   | _     | 1.4     | 1        | V        |

| Logic input high, V <sub>IH</sub>            |                                                                         | 2.0   | _       | -        | V        |

| Logic output low, V <sub>OL</sub>            | $I_{OL} \le 4 \text{ mA}$                                               | _     | _       | 0.4      | V        |

| Logic output high, V <sub>OH</sub>           | $I_{OH} \ge -2 \text{ mA}$                                              | 2.25  | _       | _        | V        |

| Tracking                                     | •                                                                       |       | ı       |          |          |

| VTRK input bias current                      | VTRK = 5.5 V                                                            | _     | 110     | 200      | μA       |

| VTRK tracking accuracy                       | 100% Tracking, V <sub>OUT</sub> - VTRK                                  | - 100 | _       | + 100    | mV       |

#### Notes:

- 1. Does not include margin

- 2. The device requires approximately 6 ms following an enable signal and prior to output ramp. The minimum settable delay is 7 ms.

## Table 3 is continued on the following page

**Table 3. Electrical Characteristics (continued)**

$V_{DDP} = V_{DDS} = 12 \text{ V}$ ,  $T_A = -40^{\circ}\text{C}$  to 85°C unless otherwise noted. Typical values are at  $T_A = 25^{\circ}\text{C}$ .

| Parameter                                       | Conditions                                              | Min  | Тур  | Max  | Unit                         |

|-------------------------------------------------|---------------------------------------------------------|------|------|------|------------------------------|

| Oscillator and Switching Characteristics        |                                                         |      |      |      |                              |

| Switch node current, I <sub>SW</sub>            | Sourcing or Sinking                                     | _    | 3    | 4.0  | A                            |

| Switching frequency range                       |                                                         | 200  | _    | 2000 | kHz                          |

| Switching frequency set-point accuracy          | Predefined settings                                     | -5   | _    | 5    | %                            |

| Minimum SYNC pulse width                        |                                                         | 150  | _    | _    | ns                           |

| Input clock frequency drift tolerance           | External clock source                                   | -13  | _    | 13   | %                            |

| Maximum duty cycle                              |                                                         | 90   | _    | _    | %                            |

| R <sub>DS(ON)</sub> of High Side N-channel FETs | $I_{SW} = 1 \text{ A}, V_{GS} = 4.7 \text{ V}$          | _    | 125  | 180  | mΩ                           |

| D Class City National FFTs                      | I <sub>SW</sub> =1A, V <sub>GS</sub> =8.5V, Charge Pump | _    | 123  | 140  | mΩ                           |

| R <sub>DS(ON)</sub> of Low Side N-channel FETs  | I <sub>SW</sub> =1A, V <sub>GS</sub> =12V               | _    | 114  | 130  | mΩ                           |

| Fault Protection Characteristics                |                                                         |      |      |      |                              |

| UVLO threshold range                            |                                                         | 3.79 | _    | 13.2 | V                            |

| UVLO setpoint accuracy                          |                                                         | -2   | _    | 2    | %                            |

| UVLO hysteresis                                 | Factory default                                         | _    | 3    | _    | %                            |

| O V LO Hysteresis                               | Configurable via I <sup>2</sup> C/SMBus                 | 0    | _    | 100  | %                            |

| UVLO delay                                      |                                                         | _    | _    | 2.5  | μs                           |

| Power good low threshold                        | Factory default                                         | _    | 90   | _    | % V <sub>OUT</sub>           |

| Power good high threshold                       | Factory default                                         | _    | 115  | _    | % V <sub>OUT</sub>           |

| Power good hysteresis                           | Factory default                                         | _    | 5    | _    | %                            |

| Power good delay                                | Using pin-strap or resistor <sup>1</sup>                | 0    | _    | 200  | ms                           |

| rowei good delay                                | Configurable via I <sup>2</sup> C/SMBus                 | 0    | _    | 500  | S                            |

| VCEN dom.oldo.co. through old                   | Factory default                                         | _    | 85   | _    | % V <sub>OUT</sub>           |

| VSEN undervoltage threshold                     | Configurable via I <sup>2</sup> C/SMBus                 | 0    | _    | 110  | % V <sub>OUT</sub>           |

| VCEN assemble as threshold                      | Factory default                                         | _    | 115  | _    | % V <sub>OUT</sub>           |

| VSEN overvoltage threshold                      | Configurable via I <sup>2</sup> C/SMBus                 | 0    | _    | 115  | % V <sub>OUT</sub>           |

| VSEN undervoltage hysteresis                    |                                                         | _    | 5    | _    | % V <sub>O</sub>             |

| VSEN undervoltage/ overvoltage fault            | Factory default                                         | _    | 16   | _    | μs                           |

| response time                                   | Configurable via I <sup>2</sup> C/SMBus                 | 5    | _    | 60   | μs                           |

| Peak current limit threshold                    |                                                         | 0.2  | _    | 4.5  | A                            |

| Current limit setpoint accuracy                 | Using ILIM pin or via I <sup>2</sup> C/SMBus            | _    | ±100 | _    | mA                           |

| Commant limit about Jacob Jolean                | Factory default                                         | _    | 5    | _    | ${\rm t_{SW}}^2$             |

| Current limit shutdown delay                    | Configurable via I <sup>2</sup> C/SMBus                 | 1    | _    | 32   | t <sub>sw</sub> <sup>2</sup> |

| Thermal protection threshold (junction          | Factory default                                         | _    | 125  | _    | °C                           |

| temperature)                                    | Configurable via I <sup>2</sup> C/SMBus                 | -40  | _    | 125  | °C                           |

| Thermal protection hysteresis                   |                                                         | _    | 15   | _    | °C                           |

#### Notes:

- 1. Factory default Power Good delay is set to the same value as the soft start ramp time.

- 2.  $t_{SW} = 1/f_{SW}$ , where  $f_{SW}$  is the switching frequency.

# 2. Pin Descriptions

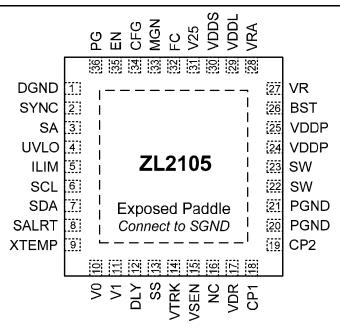

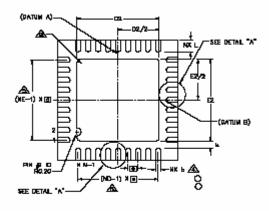

Figure 2. ZL2105 Pin Configurations (top view)

**Table 4. Pin Descriptions**

| Pin    | Label   | Type <sup>1</sup> | Description                                                                                                                                                                                         |

|--------|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DGND    | PWR               | Digital ground. Common return for digital signals. Connect to low impedance ground plane.                                                                                                           |

| 2      | SYNC    | I/O, M            | Clock synchronization input. Used to set switching frequency of internal clock or for synchronization to external frequency reference. Programmable open drain output. Factory default is push-pull |

| 3      | SA      | I,M               | Serial address pin used to assign unique SMBus address to each IC.                                                                                                                                  |

| 4      | UVLO    | I,M               | Sets the input undervoltage lockout threshold that disables the device.                                                                                                                             |

| 5      | ILIM    | I,M               | Sets the current limit threshold level.                                                                                                                                                             |

| 6      | SCL     | I/O               | Serial clock signal for system communications.                                                                                                                                                      |

| 7      | SDA     | I/O               | Serial data signal for system communications.                                                                                                                                                       |

| 8      | SALRT   | О                 | SMBus alert signal.                                                                                                                                                                                 |

| 9      | XTEMP   | I                 | External temperature sensor input.                                                                                                                                                                  |

| 10,11  | V0, V1  | I,M               | Output voltage select pins. Used to set the output voltage.                                                                                                                                         |

| 12     | DLY     | I,M               | Soft start delay select pin. Sets the delay from when EN is asserted until the output voltage starts to ramp.                                                                                       |

| 13     | SS      | I,M               | Digital soft-start/stop. Sets the ramp period for the output to reach the desired regulation point (after soft-start delay period, if applicable).                                                  |

| 14     | VTRK    | I                 | Track input. Allows the output to track another voltage.                                                                                                                                            |

| 15     | VSEN    | I                 | Output voltage positive feedback sensing node.                                                                                                                                                      |

| 16     | NC      | -                 | No internal connection.                                                                                                                                                                             |

| 17     | VDR     | PWR               | Supply pin for internal drivers.                                                                                                                                                                    |

| 18, 19 | CP1,CP2 | I/O               | Level-shift charge pump for 5 V operation. Connect external capacitor.                                                                                                                              |

#### Notes:

1. I = Input, O = Output, PWR = Power or Ground. M = Multi-mode pins.

**Table 4. Pin Descriptions (continued)**

| Pin   | Label | Type <sup>1</sup> | Description                                                                                                                                                                |

|-------|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20,21 | PGND  | PWR               | Power ground. Common return for internal switching MOSFETs.                                                                                                                |

| 22,23 | SW    | I/O               | Switching node (level-shift common).                                                                                                                                       |

| 24,25 | VDDP  | PWR               | Bias power for internal switching MOSFETs (return is PGND).                                                                                                                |

| 26    | BST   | PWR               | Bootstrap V <sub>DD</sub> for level-shift driver (referenced to SW).                                                                                                       |

| 27    | VR    | PWR               | Regulated bias from internal 5V low-dropout regulator (return is PGND). Decouple with a 4.7 $\mu$ F capacitor to PGND. Connect 91 $\Omega$ resistor between VR and VRA.    |

| 28    | VRA   | PWR               | Regulated 5 V bias for internal analog circuitry (return is SGND). Decouple with a 4.7 $\mu$ F capacitor to SGND. Connect 91 $\Omega$ resistor between VR and VRA.         |

| 29    | VDDL  | PWR               | Internal logic supply. Connect to VRA or apply a 3.0-5.5 V external supply. Return is SGND.                                                                                |

| 30    | VDDS  | PWR               | IC supply voltage (return is SGND).                                                                                                                                        |

| 31    | V25   | PWR               | Regulated bias from internal 2.5 V low-dropout regulator. Decouple with a $10\mu F$ capacitor.                                                                             |

| 32    | FC    | I                 | Frequency compensation select pin. Used to set loop compensation.                                                                                                          |

| 33    | MGN   | I                 | Signal that enables margining of output voltage.                                                                                                                           |

| 34    | CFG   | I                 | Configuration pin. Sets switching phase delay and sequencing order.                                                                                                        |

| 35    | EN    | I                 | Enable input. Active high signal enables the device.                                                                                                                       |

| 36    | PG    | О                 | Power good output. This pin transitions high 100 ms after output voltage stabilizes within regulation band. Programmable open drain output. Factory default is open drain. |

| ePad  | SGND  | PWR               | Exposed thermal pad. Common return for analog signals; internal connection to SGND. Connect to low impedance ground plane.                                                 |

#### Notes:

<sup>1.</sup> I = Input, O = Output, PWR = Power or Ground. M = Multi-mode pins. Please refer to Section 4.4 "Multi-mode Pins," on page 12.

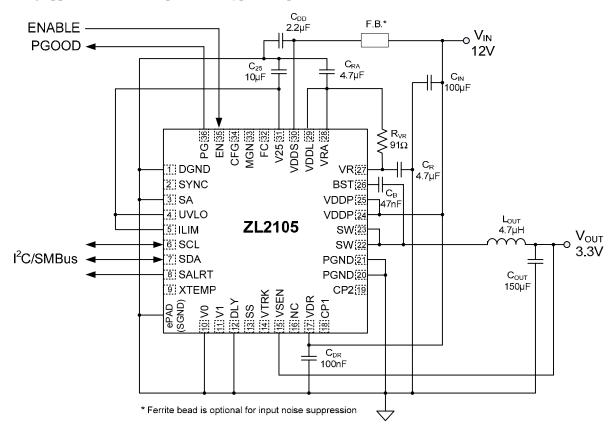

# 3. Typical Application Circuit

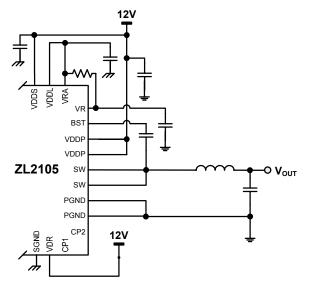

The following application circuit represents a typical implementation of the ZL2105.

Figure 3. 12 V to 3.3 V / 3 A Application Circuit (10.8 V UVLO, 10 ms SS delay, 50 ms SS ramp, 12 V used for low-side FET driver)

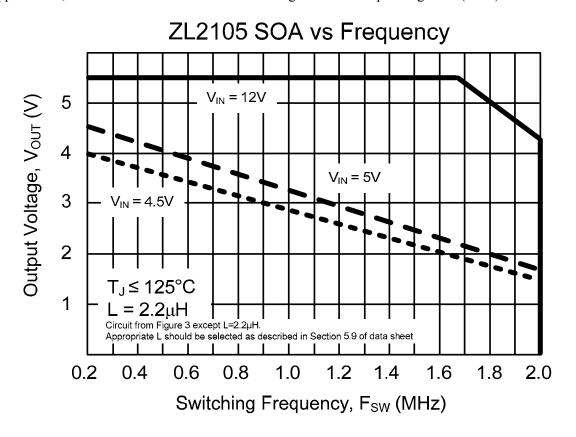

For all applications, the ZL2105 must be derated according to the Safe Operating Area (SOA) curves.

Figure 4. ZL2105 SOA Curves

#### 4. ZL2105 Overview

#### 4.1 Digital-DC Architecture

The ZL2105 is an innovative mixed-signal power conversion and power management IC based on Zilker Labs patented Digital-DC technology that provides an integrated, high performance step-down converter for point of load applications. The ZL2105 integrates all necessary PWM control circuitry as well as synchronous 4.5 A N-channel MOSFETs in order to provide an extremely small solution for providing load currents up to 3 A. Its unique PWM loop utilizes an ideal mix of analog and digital blocks to enable precise control of the entire power conversion process with no software required, resulting in a very flexible device that is also very easy to use. An extensive set of power management functions are fully integrated and can be configured using simple pin connections. The user configuration can be saved in an internal non-volatile memory (NVM). Additionally, all functions can be configured and monitored via the SMBus hardware interface using standard PMBus commands, allowing ultimate flexibility.

Once enabled, the ZL2105 is immediately ready to regulate power and perform power management tasks with no programming required. Advanced configuration options and real-time configuration changes are available via the I<sup>2</sup>C/SMBus interface if desired and continuous monitoring of multiple operating parameters is possible with minimal interaction from a host controller. Integrated sub-regulation circuitry enables single supply operation from any supply between 4.5 V and 14 V with no secondary bias supplies needed. The ZL2105

can also be configured to operate from a 3.3 V or 5 V standby supply when the main power rail is not present, allowing the user to configure and/or read diagnostic information from the device when the main power has been interrupted or is disabled.

The ZL2105 can be configured by simply connecting its pins according to the tables provided in the following sections. Additionally, a comprehensive set of tools and application notes are available to help simplify the design process. An evaluation board is also available to help the user become familiar with the device. This board can be evaluated as a standalone platform using pin configuration settings. A Windows<sup>TM</sup>-based GUI is also provided to enable full configuration and monitoring capability via the I<sup>2</sup>C/SMBus interface using an available computer and the included USB cable.

Application notes and reference designs are available to assist the user in designing to specific application demands. Please register for My ZL on <a href="https://www.zilkerlabs.com">www.zilkerlabs.com</a> to access the most up-to-date documentation or call your local Zilker Labs sales office to order an evaluation kit.

#### 4.2 Power Conversion Overview

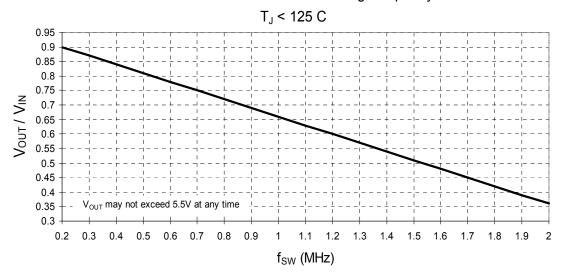

Figure 5. ZL2105 Block Diagram

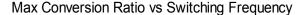

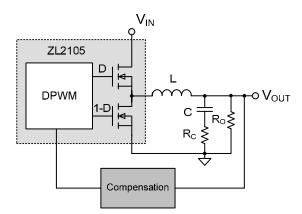

The ZL2105 operates as a voltage-mode, synchronous buck converter with a selectable constant frequency PWM control scheme. The ZL2105 incorporates dual low  $R_{DS(ON)}$  synchronous MOSFETs to help minimize the required circuit footprint.

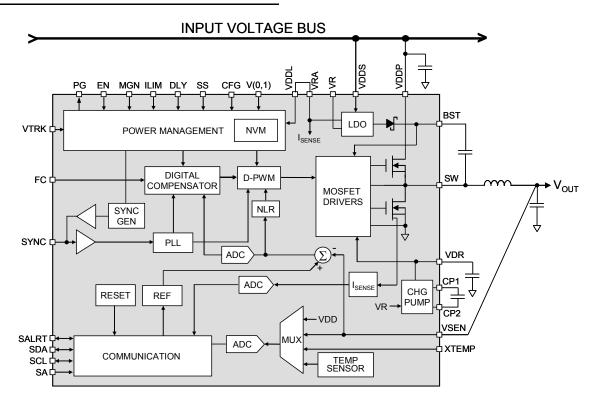

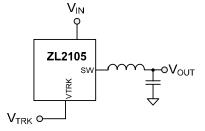

Figure 6. Synchronous Buck Converter

Figure 6 illustrates the basic synchronous buck converter topology showing the primary power train components. This converter is also called a step-down converter, as the output voltage must always be lower than the input voltage. The ZL2105 integrates two MOSFETs; QH is the top control MOSFET and QL is the bottom synchronous MOSFET. The amount of time that QH is on as a fraction of the total switching period

is known as the duty cycle D, which is described by the following equation:

$$D = \frac{V_{OUT}}{V_{IN}}$$

During time D, QH is on and  $V_{\text{IN}} - V_{\text{OUT}}$  is applied across the inductor.

As shown in Figure 5, the output voltage is directly applied to the VSEN pin. The VSEN signal is then compared to an internal programmable reference voltage that is set to the desired output voltage level. The error signal derived from this comparison is converted to a digital value with a fast analog to digital (A/D) converter. The digital signal is also applied to an adjustable digital compensation filter, and the compensated signal is used to derive the appropriate PWM duty cycle for driving the internal MOSFETs. The ZL2105 also incorporates a non-linear response (NLR) loop to improve the response time and reduce the output deviation as a result of a load transient. The ZL2105 monitors the power converter's operating conditions and continuously adjusts the turn-on and turn-off timing of the high-side and low-side MOSFETs to optimize the overall efficiency of the power supply.

#### 4.3 Power Management Overview

The ZL2105 incorporates a wide range of configurable power management features that are simple to implement with no external components. Additionally, the ZL2105 includes circuit protection features that continuously safeguard the device and load from damage due to unexpected system faults. The ZL2105 can continuously monitor input voltage, output voltage/current, internal temperature, and the temperature of an external thermal diode. A Power Good output signal is also included to enable power-on reset functionality for an external processor.

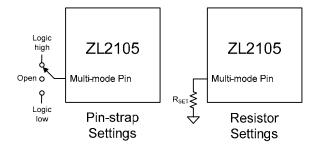

All power management functions can be configured using either pin configuration techniques (see Figure 7) or via the I<sup>2</sup>C/SMBus interface. Monitoring parameters can also be pre-configured to provide alerts for specific conditions. See Application Note AN13 for more details on SMBus monitoring.

#### 4.4 Multi-mode Pins

Most power management features can be configured using the multi-mode pins. The multi-mode pins can respond to four different connections as shown in Table 5. These pins are sampled when power is applied or by issuing a PMBus Restore command (See Application Note AN13).

Pin-strap Settings: Using this method, each pin can take on one of three possible states: LOW, OPEN, or HIGH. These pins can be connected to the VR or V25 pins for logic HIGH settings, as either pin provides a regulated voltage higher than 2 V. Using a single pin one of three settings can be selected, and using two pins the user can select one of nine settings.

Table 5. Multi-mode Pin Configuration

| Pin Tied To          | Value                 |

|----------------------|-----------------------|

| LOW<br>(Logic LOW)   | < 0.8 VDC             |

| OPEN<br>(N/C)        | No connection         |

| HIGH<br>(Logic HIGH) | > 2.0 VDC             |

| Resistor to SGND     | Set by resistor value |

Figure 7. Pin-strap and Resistor Setting Examples

Resistor Settings: This method allows a greater range of adjustability when connecting a finite value resistor (in a specified range) between the multi-mode pin and SGND. Standard 1% resistor values are used, and only every fourth E96 resistor value is used so the device can reliably recognize the value of resistance connected to the pin while eliminating the error associated with the resistor accuracy. A total of 25 unique selections are available using a single resistor.

*I*<sup>2</sup>*C/SMBus Method:* Almost any ZL2105 function can be configured via the I<sup>2</sup>C/SMBus interface using standard PMBus commands. Additionally, any value that has been configured using the pin-strap or resistor setting methods can also be re-configured and/or verified via the I<sup>2</sup>C/SMBus. See Application Note AN13 for more details.

The SMBus device address and VOUT\_MAX are the only parameters that must be set by external pins. All other device parameters can be set via the I<sup>2</sup>C/SMBus. The device address is set using the SA pin. VOUT\_MAX is determined as 10% greater than the voltage set by the V0 and V1 pins.

## 5. Power Conversion Functional Description

# 5.1 Internal Bias Regulators and Input Supply Connections

The ZL2105 employs three internal low dropout (LDO) regulators to supply bias voltages for internal circuitry as follows:

VR: The VR LDO provides a regulated 5 V bias supply for the MOSFET driver circuits. It is powered from the VDDS pin. A 4.7  $\mu$ F filter capacitor is required at the VR pin.

VRA: The VRA LDO provides a regulated 5 V bias supply for the current sense circuit and other analog circuitry. It is powered from the VDDS pin. A small filter capacitor is required at the VRA pin. For single supply operation, this pin should be connected to the VDDL pin so the VRA LDO can be used to power the digital core logic circuitry.

V25: The V25 LDO provides a regulated 2.5 V bias supply for the main controller circuitry. It is powered from the VDDL pin. A 10  $\mu$ F filter capacitor is required at the V25 pin.

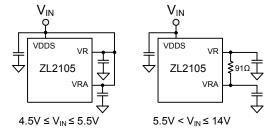

When the input supply (VDDS) is higher than 5.5 V, the VR and VRA pins should not be connected to any other pins. They should have a filter capacitor and a  $91\Omega$  resistor attached as shown in Figure 8. Due to the dropout voltage associated with the VR and VRA bias regulators, the VDDS pin must be connected to the VR and VRA pins for designs operating from a supply below 5.5 V. Figure 8 illustrates the required connections for both cases.

**Figure 8. Input Supply Connections**

Note: the internal bias regulators, VR and VRA, are not designed to be outputs for powering other circuitry. Do not attach external loads to either of these pins. The multi-mode pins may be connected to the V25 pin for logic HIGH settings.

#### 5.2 High-side Driver Boost Circuit

The gate drive voltage for the high-side MOSFET driver is generated by a floating bootstrap capacitor,  $C_B$  (see Figure 6). When the lower MOSFET (QL) is turned on, the SW node is pulled to ground and the capacitor is charged from the internal VR bias regulator through diode  $D_B$ . When QL turns off and the upper MOSFET (QH) turns on, the SW node is pulled up to  $V_{DDP}$  and the voltage on the bootstrap capacitor is boosted approximately 5V above  $V_{DDP}$  to provide the necessary voltage to power the high-side driver. An internal Schottky diode is used with  $C_B$  to help maximize the high-side drive supply voltage.

#### 5.3 Low-side Driver Supply Options

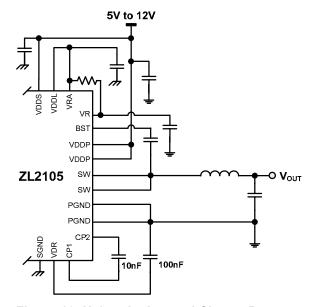

The ZL2105 provides multiple options for powering the internal low-side MOSFET drivers as follows:

12 V Supply: When operating from a 12 V input supply (or any supply 9 V or higher), efficiency can be optimized by operating the low-side MOSFET driver directly from the input supply. Connecting the input supply to the VDR pin (with no external capacitor connected between CP1 and CP2) applies the input supply directly to the low-side driver. This is the simplest method of powering the low-side driver and requires the fewest components. Figure 9 illustrates the required connections for implementing this configuration.

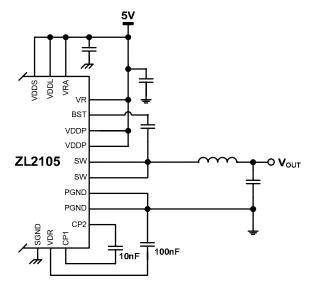

Figure 9. Using an External 12 V Supply to Power the Low-side Driver

Internal Charge Pump: A voltage doubler circuit can be used to optimize efficiency when operating from an input supply that is below 9 V or may occasionally drop below 9 V. The internal charge pump is enabled by connecting a 10 nF capacitor between the CP1 and CP2 pins and a 100 nF capacitor between VDR and PGND. The charge pump provides a low-side driver supply based on the equation below:

$$V_{CP} = (VR - 0.5V) \times 2$$

Figure 10. Using the Internal Charge Pump to Power the Low-side Driver

The required connections are shown in Figure 10.

Note: when the input supply is always lower than 5.5 V, the VDDS pin must be connected to the VR pin as shown in Figure 11. The resistor between VR and VRA is not required when VDDL and VDDS are tied directly to VR and VRA since this configuration overrides the internal LDOs.

Figure 11. Powering the Low-side Driver When VDDS ≤ 5.5 V

#### 5.4 Dual Input Supply Configuration

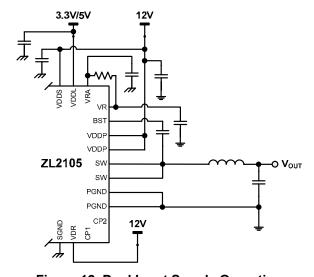

The ZL2105 allows the use of two unique input supplies to enable communication with the device when the primary power rail is not present. Typical applications of this scenario use a 12 V supply as the main power input and either a 3.3 V or 5 V standby supply to power the device during periods when the primary power supply is disabled or not operational. This configuration allows a host controller to communicate with the ZL2105 when the 12 V main supply is not available. Figure 12 shows the typical connections required for this configuration. This figure uses the 12 V supply for powering the low-side driver.

Figure 12. Dual Input Supply Operation

#### 5.5 Output voltage Selection

The output voltage may be set to any voltage between 0.6~V and 5.0~V provided that the input voltage is higher than the desired output voltage by an amount sufficient to prevent the device from exceeding its maximum duty cycle specification. Using the pin-strap method,  $V_{\rm OUT}$  can be set to any of nine standard voltages as shown in Table 6.

**Table 6. Pin-strap Output Voltage Settings**

|    |      | V0    |       |       |

|----|------|-------|-------|-------|

|    |      | LOW   | OPEN  | HIGH  |

|    | LOW  | 0.6 V | 0.8 V | 1.0 V |

| V1 | OPEN | 1.2 V | 1.5 V | 1.8 V |

|    | HIGH | 2.5 V | 3.3 V | 5.0 V |

The resistor setting method can be used to set the output voltage to levels not available in Table 6. Resistors R0 and R1 are selected to produce a specific voltage between 0.6 V and 5.0 V in 10 mV steps. Resistor R1 provides a coarse setting and resistor R0 provides a fine adjustment, thus eliminating the additional errors associated with using two 1% resistors (this typically adds 1.4% error).

To set  $V_{OUT}$  using resistors, follow the steps below to calculate an index value and then use Table 7 to select the resistor that corresponds to the calculated index value as follows:

1. Calculate Index1:

Index 1 =  $4 \times V_{OUT}$  ( $V_{OUT}$  in 10 mV steps)

- 2. Round the result down to the nearest whole number.

- 3. Select the value of R1 from Table 7 using the Index1 rounded value from step 2.

- 4. Calculate Index0:

$Index0 = 100 \times V_{OUT} - (25 \times Index1)$

5. Select the value of R0 from Table 7 using the Index0 value from step 4.

Table 7. Resistors for Setting Output Voltage

| Index | R0 or R1 |

|-------|----------|

| 0     | 10 kΩ    |

| 1     | 11 kΩ    |

| 2     | 12.1 kΩ  |

| 3     | 13.3 kΩ  |

| 4     | 14.7 kΩ  |

| 5     | 16.2 kΩ  |

| 6     | 17.8 kΩ  |

| 7     | 19.6 kΩ  |

| 8     | 21.5 kΩ  |

| 9     | 23.7 kΩ  |

| 10    | 26.1 kΩ  |

| 11    | 28.7 kΩ  |

| 12    | 31.6 kΩ  |

| put voitage |                         |  |  |

|-------------|-------------------------|--|--|

| Index       | R0 or R1                |  |  |

| 13          | $34.8~\mathrm{k}\Omega$ |  |  |

| 14          | $38.3~\mathrm{k}\Omega$ |  |  |

| 15          | 42.2 kΩ                 |  |  |

| 16          | 46.4 kΩ                 |  |  |

| 17          | 51.1 kΩ                 |  |  |

| 18          | 56.2 kΩ                 |  |  |

| 19          | $61.9~\mathrm{k}\Omega$ |  |  |

| 20          | 68.1 kΩ                 |  |  |

| 21          | 75 kΩ                   |  |  |

| 22          | 82.5 k $\Omega$         |  |  |

| 23          | 90.9 kΩ                 |  |  |

| 24          | 100 kΩ                  |  |  |

|             |                         |  |  |

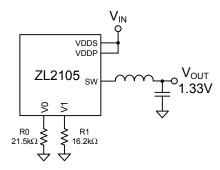

Example: For  $V_{OUT} = 1.33 \text{ V}$ ,

Index 1 = 4 x 1.33 V = 5.32; From Table 7, R1 = 16.2 k $\Omega$

Index0 =  $(100 \times 1.33 \text{ V}) - (25 \times 5) = 8$ ; From Table 7, R0 =  $21.5 \text{ k}\Omega$

Figure 13. Output Voltage Resistor Setting Example

The output voltage may also be set to any value between 0.6 V and 5.5 V using the I<sup>2</sup>C interface. See Application Note AN13 for details.

#### 5.6 Start-up Procedure

The ZL2105 follows a specific internal start-up procedure after power is applied to the VDD pins (VDDL, VDDP, and VDDS). Table 8 describes the start-up sequence.

If the device is to be synchronized to an external clock source, the clock frequency must be stable prior to asserting the EN pin. The device requires approximately 10-20 ms to check for specific values stored in its internal memory. If the user has stored values in memory, those values will be loaded. The device will then check the status of all multi-mode pins and load the values associated with the pin settings.

Once this process is completed, the device is ready to accept commands via the I<sup>2</sup>C/SMBus interface and the device is ready to be enabled. Once enabled, the device requires approximately 7 ms before its output voltage may be allowed to start its ramp-up process. If a soft-start delay period less than 7 ms has been configured (using PMBus commands), the device will default to a 7 ms delay period. If a delay period greater than 7 ms is configured, the device will wait for the configured delay period prior to starting to ramp its output.

After the delay period has expired, the output will begin to ramp towards its target voltage according to the pre-configured soft-start ramp time that has been set using the SS pin.

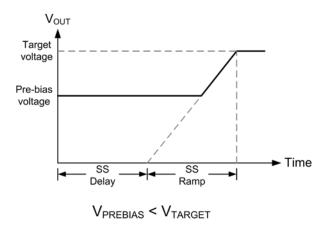

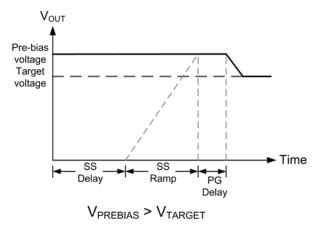

#### **Soft Start Delay and Ramp Times**

In some applications, it may be necessary to set a delay from when an enable signal is received until the output voltage starts to ramp to its target value. In addition, the designer may wish to precisely set the time required for  $V_{OUT}$  to ramp to its target value after the delay period has expired. These features may be used as part of an overall inrush current management strategy or to precisely control how fast a load IC is turned on. The ZL2105 gives the system designer several options for precisely and independently controlling both the delay and ramp time periods.

The soft-start delay period begins when the EN pin is asserted and ends when the delay time expires. The soft-start delay period is set using the DLY pin.

The soft-start ramp timer enables a precisely controlled ramp to the nominal  $V_{\text{OUT}}$  value that begins once the delay period has expired. The ramp-up is guaranteed monotonic and its slope may be precisely set using the SS pin.

The soft-start delay and ramp times can be set to one of three standard values according to Table 9 and Table 10 respectively.

**Table 9. Soft Start Delay Settings**

| DLY Pin Setting | Soft Start Delay Time |

|-----------------|-----------------------|

| LOW             | 10 ms                 |

| OPEN            | 50 ms                 |

| HIGH            | 100 ms                |

Table 8. ZL2105 Start-up Sequence

| Step# | Step Name                | Description                                                                                                                                                        | Time Duration                                                         |

|-------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1     | Power Applied            | Input voltage is applied to the ZL2105's VDD pins (VDDL, VDDP, VDDS)                                                                                               | Depends on input supply ramp time                                     |

| 2     | Internal Memory<br>Check | The device will check for values stored in its internal memory. This step is also performed after a Restore command.                                               | Approx 10-20 ms (device will ignore an enable signal or PMBus traffic |

| 3     | Multi-mode Pin<br>Check  | The device loads values configured by the multi-mode pins.                                                                                                         | during this period)                                                   |

| 4     | Device Ready             | The device is ready to accept an enable signal.                                                                                                                    | _                                                                     |

| 5     | Pre-ramp Delay           | The device requires approximately 6 ms following an enable signal and prior to ramping its output.  Additional pre-ramp delay may be configured using the DLY pin. | Approximately 6 ms                                                    |

5.7

**Table 10. Soft Start Ramp Settings**

| SS Pin Setting | Soft Start Ramp Time |

|----------------|----------------------|

| LOW            | 10 ms                |

| OPEN           | 50 ms                |

| HIGH           | 100 ms               |

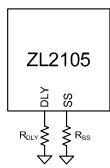

If the desired soft start delay and ramp times are not one of the values listed in Table 9 and Table 10, the times can be set to a custom value by connecting a resistor from the DLY or SS pin to SGND using the appropriate resistor values from Table 11. The value of this resistor is measured upon start-up or Restore and will not change if the resistor is varied after power has been applied to the ZL2105. See Figure 14 for typical connections using resistors.

Figure 14. DLY and SS Pin Resistor Connections

Table 11. DLY and SS Resistor Values

| and SS Resis                        |

|-------------------------------------|

| R <sub>DLY</sub> or R <sub>SS</sub> |

| 10 kΩ                               |

| 11 kΩ                               |

| 12.1 kΩ                             |

| 13.3 kΩ                             |

| 14.7 kΩ                             |

| 16.2 kΩ                             |

| 17.8 kΩ                             |

| 19.6 kΩ                             |

| 21.5 kΩ                             |

| 23.7 kΩ                             |

| 26.1 kΩ                             |

|                                     |

| <del>- ulucc</del> |                         |

|--------------------|-------------------------|

| DLY or             | $R_{DLY}$ or            |

| SS                 | R <sub>ss</sub>         |

| 110 ms             | 28.7 kΩ                 |

| 120 ms             | 31.6 kΩ                 |

| 130 ms             | $34.8~\mathrm{k}\Omega$ |

| 140 ms             | $38.3~\mathrm{k}\Omega$ |

| 150 ms             | 42.2 kΩ                 |

| 160 ms             | 46.4 kΩ                 |

| 170 ms             | 51.1 kΩ                 |

| 180 ms             | 56.2 kΩ                 |

| 190 ms             | 61.9 kΩ                 |

| 200 ms             | 68.1 kΩ                 |

| 200 ms             | 68.1 kΩ                 |

The soft start delay and ramp times can also be set to custom values via the I<sup>2</sup>C/SMBus interface. When the SS delay time is set to 0 ms, the device will begin its ramp-up after the internal circuitry has initialized (approx. 6 ms). When the soft-start ramp period is set to 0 ms, the output will ramp up as quickly as the output load capacitance will allow.

#### 5.8 Switching Frequency and PLL

The ZL2105 incorporates an internal phase-locked loop (PLL) to clock the internal circuitry. The PLL can be driven by an external clock source connected to the SYNC pin. When using the internal oscillator, the SYNC pin can be configured as a clock source for other Zilker Labs devices.

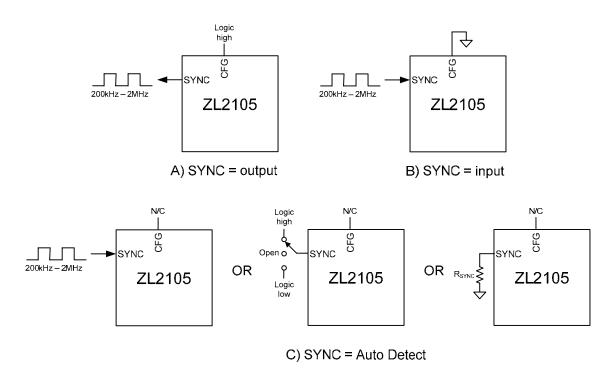

The CFG pin is used to select the operating mode of the SYNC pin, configure sequencing, and enable tracking. Table 12 describes the operating modes for the SYNC pin. Section 6.12 "Output Sequencing," on Page 30 describes sequencing and tracking. Figure 15 illustrates the typical connections for each SYNC configuration.

**Table 12. SYNC Pin Function Selection**

| CFG Pin                                                        | SYNC Pin Function              |  |

|----------------------------------------------------------------|--------------------------------|--|

| LOW                                                            | SYNC is configured as an input |  |

| OPEN                                                           | Auto detect mode               |  |

| HIGH SYNC is configured as an output f <sub>SW</sub> = 400 kHz |                                |  |

#### Configuration A: SYNC OUTPUT

When the SYNC pin is configured as an output (CFG pin is tied HIGH), the device will run from its internal oscillator and will drive the resulting internal oscillator signal (preset to 400 kHz) onto the SYNC pin so other devices can be synchronized to it. The SYNC pin will not be checked for an incoming clock signal while in this mode.

#### **Configuration B:** SYNC INPUT

When the SYNC pin is configured as an input (CFG pin is tied LOW), the device will automatically check for a clock signal on the SYNC pin each time the EN pin is asserted. The ZL2105's oscillator will then synchronize both frequency and phase with the rising edge of the external clock signal. The incoming clock signal must be in the range of 200 kHz to 2 MHz with a minimum duty cycle, and must be stable when the EN pin is asserted. See Table 3 for a complete list of performance requirements for the incoming clock signal.

Figure 15. SYNC Pin Configurations.

#### Configuration C: SYNC AUTO DETECT

When the SYNC pin is configured in auto detect mode (CFG pin is left OPEN), the device will automatically check for a clock signal on the SYNC pin after enable is asserted.

- If a valid clock signal is present, the ZL2105's oscillator will then synchronize both frequency and phase with the rising edge of the external clock signal. The incoming clock signal must be in the range of 200 kHz to 2 MHz with a minimum duty cycle, and must be stable when the EN pin is asserted. See Table 3 for a complete list of performance requirements for the incoming clock signal.

- If no incoming clock signal is present, the ZL2105 will configure the switching frequency according to the state of the SYNC pin as listed in Table 13. In this configuration, the SYNC pin is sampled only on start-up and will not modify its switching frequency if the SYNC pin is re-configured after start-up (unless the power is recycled).

**Table 13. Switching Frequency Selection**

| SYNC Pin | Frequency    |

|----------|--------------|

| LOW      | 200 kHz      |

| OPEN     | 400 kHz      |

| HIGH     | 1 MHz        |

| Resistor | See Table 14 |

If the user wishes to run the ZL2105 at a frequency not listed in Table 13, the switching frequency can be set using an external resistor,  $R_{SYNC}$ , connected between SYNC and SGND using Table 14.

Table 14. R<sub>SYNC</sub> Resistor Values

| Table 14. K <sub>SYNC</sub> Resist |                          |  |

|------------------------------------|--------------------------|--|

| F <sub>sw</sub>                    | R <sub>SYNC</sub>        |  |

| 200 kHz                            | 10 kΩ                    |  |

| 222 kHz                            | 11 kΩ                    |  |

| 242 kHz                            | 12.1 kΩ                  |  |

| 267 kHz                            | 13.3 k $\Omega$          |  |

| 296 kHz                            | 14.7 kΩ                  |  |

| 320 kHz                            | $16.2~\mathrm{k}\Omega$  |  |

| 364 kHz                            | 17.8 kΩ                  |  |

| 400 kHz                            | 19.6 kΩ                  |  |

| 421 kHz                            | $21.5  \mathrm{k}\Omega$ |  |

| 471 kHz                            | 23.7 k $\Omega$          |  |

| 533 kHz                            | 26.1 kΩ                  |  |

| $F_{sw}$ | R <sub>SYN</sub>        |

|----------|-------------------------|

| 571 kHz  | 28.7 kΩ                 |

| 615 kHz  | 31.6 kΩ                 |

| 667 kHz  | $34.8~\mathrm{k}\Omega$ |

| 727 kHz  | $38.3~\mathrm{k}\Omega$ |

| 889 kHz  | 46.4 kΩ                 |

| 1000 kHz | 51.1 kΩ                 |

| 1143 kHz | 56.2 kΩ                 |

| 1333 kHz | 68.1 kΩ                 |

| 1600 kHz | 82.5 kΩ                 |

| 2000 kHz | 100 kΩ                  |

The switching frequency can also be set to any value between 200 kHz and 2 MHz using the  $I^2C/SMBus$  interface. The available frequencies are bounded by  $f_{SW}$  = 8 MHz/N, where  $4\le N\le 40$ . See Application Note AN13 for details.

If multiple Zilker Labs devices are used together, connecting the SYNC pins together will force all devices to synchronize with each other. The CFG pin of one device must set its SYNC pin as an output and the remaining devices must have their SYNC pins set as an input.

Note: The switching frequency read back using the appropriate PMBus command will differ slightly from the selected value in Table 14. The difference is due to hardware quantization.

#### 5.9 Component Selection

The ZL2105 is a synchronous buck converter with integrated MOSFETs that uses an external inductor and capacitors to perform the power conversion process. The proper selection of the external components is critical for optimized performance. For more detailed guidelines regarding component selection, refer to Application Note AN11.

To select the appropriate external components for the desired performance goals, the power supply requirements listed in Table 15 must be known.

**Table 15. Power Supply Requirements**

| Parameter                                  | Range                    | Example<br>Value        |

|--------------------------------------------|--------------------------|-------------------------|

| Input voltage (V <sub>IN</sub> )           | 4.5–14.0 V               | 12 V                    |

| Output voltage (V <sub>OUT</sub> )         | 0.6–5.5 V                | 1.2 V                   |

| Output current (I <sub>OUT</sub> )         | 0 to 3 A                 | 2 A                     |

| Output voltage ripple (V <sub>orip</sub> ) | < 3% of V <sub>OUT</sub> | 1% of V <sub>OUT</sub>  |

| Output load step (I <sub>ostep</sub> )     | < Io                     | 50% of I <sub>o</sub>   |

| Output load step rate                      | _                        | 10 A/μS                 |

| Output deviation due to load step          | _                        | 50 mV                   |

| Maximum PCB temp.                          | 120°C                    | 85°C                    |

| Desired efficiency                         | _                        | 85%                     |

| Other considerations                       | _                        | Optimize for small size |

#### 5.9.1 Design Goal Trade-offs

The design of the buck power stage requires several compromises among size, efficiency, and cost. The inductor core loss increases with frequency, so there is a trade-off between a small output filter made possible by a higher switching frequency and getting better power supply efficiency. Size can be decreased by increasing the switching frequency at the expense of efficiency. Cost can be minimized by using throughhole inductors and capacitors; however these components are physically large.

To start the design, select a frequency based on Table 16. This frequency is a starting point and may be adjusted as the design progresses.

**Table 16. Circuit Design Considerations**

| Frequency<br>Range | Efficiency | Circuit Size |

|--------------------|------------|--------------|

| 200–400 kHz        | Highest    | Larger       |

| 400–800 kHz        | Moderate   | Smaller      |

| 800 kHz –<br>2 MHz | Lower      | Smallest     |

#### 5.9.2 Inductor Selection

The output inductor selection process must include several trade-offs. A high inductance value will result in a low ripple current ( $I_{opp}$ ), which will reduce output capacitance and produce a low output ripple voltage, but may also compromise output transient load performance. Therefore, a balance must be struck between output ripple and optimal load transient

performance. A good starting point is to select the output inductor ripple equal to the expected load transient step magnitude ( $I_{ostep}$ ):

$$I_{opp} = I_{ostep}$$

Now the output inductance can be calculated using the following equation, where  $V_{\text{INM}}$  is the maximum input voltage:

$$L_{OUT} = \frac{V_{OUT} \times \left(1 - \frac{V_{OUT}}{V_{INM}}\right)}{fsw \times I_{opp}}$$

The average inductor current is equal to the maximum output current. The peak inductor current  $(I_{Lpk})$  is calculated using the following equation where  $I_{OUT}$  is the maximum output current:

$$I_{Lpk} = I_{OUT} + \frac{I_{opp}}{2}$$

Select an inductor rated for the average DC current with a peak current rating above the peak current computed above.

In over-current or short-circuit conditions, the inductor may have currents greater than 2X the normal maximum rated output current. It is desirable to use an inductor that still provides some inductance to protect the load and the internal MOSFETs from damaging currents in this situation.

Once an inductor is selected, the DCR and core losses in the inductor are calculated. Use the DCR specified in the inductor manufacturer's datasheet:

$$P_{LDCR} = DCR \times I_{Lrms}^{2}$$

I<sub>Lrms</sub> is given by

$$I_{Lrms} = \sqrt{I_{OUT}^2 + \frac{(I_{opp})^2}{12}}$$

where I<sub>OUT</sub> is the maximum output current. Next, calculate the core loss of the selected inductor. Since this calculation is specific to each inductor and manufacturer, refer to the chosen inductor datasheet. Add the core loss and the ESR loss and compare the total loss to the maximum power dissipation recommendation in the inductor datasheet.

#### 5.9.3 Output Capacitor Selection

Several trade-offs must also be considered when selecting an output capacitor. Low ESR values are needed to have a small output deviation during transient load steps ( $V_{osag}$ ) and low output voltage ripple ( $V_{orip}$ ). However, capacitors with low ESR, such as semi-stable (X5R and X7R) dielectric ceramic capacitors, also have relatively low capacitance values. Many designs can use a combination of high capacitance devices and low ESR devices.

For high ripple currents, a low capacitance value can cause a significant amount of output voltage ripple. Likewise, in high transient load steps, a relatively large amount of capacitance is needed to minimize the output voltage deviation while the inductor current ramps up or down to the new steady state output current value.

As a starting point, apportion one-half of the output ripple voltage to the capacitor ESR and the other half to capacitance, as shown in the following equations:

$$C_{OUT} = \frac{I_{opp}}{8 \times f_{sw} \times \frac{V_{orip}}{2}}$$

$$ESR = \frac{V_{orip}}{2 \times I_{opp}}$$

Use these values to make an initial capacitor selection, using a single or capacitor several capacitors in parallel.

After a capacitor has been selected, the resulting output voltage ripple can be calculated using the following equation:

$$V_{orip} = I_{opp} \times ESR + \frac{I_{opp}}{8 \times f_{sw} \times C_{OUT}}$$

Because each part of this equation was made to be less than or equal to half of the allowed output ripple voltage, the  $V_{\text{orip}}$  should be less than the desired maximum output ripple.

For more information on the performance of the power supply in response to a transient load, refer to Application Note AN11.

#### 5.9.4 Input Capacitor

It is highly recommended that dedicated input capacitors be used in any point-of-load design, even when the supply is powered from a heavily filtered 5 or 12 V "bulk" supply from an off-line power supply. This is because of the high RMS ripple current that is drawn by the buck converter topology. This ripple ( $I_{\text{CINrms}}$ ) can be determined from the following equation:

$$I_{CINrms} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

Without capacitive filtering near the power supply circuit, this current would flow through the supply bus and return planes, coupling noise into other system circuitry. The input capacitors should be rated at 1.4X the ripple current calculated above to avoid overheating of the capacitors due to the high ripple current, which can cause premature failure. Ceramic capacitors with X7R or X5R dielectric with low ESR and 1.1X the maximum expected input voltage are recommended.

#### 5.9.5 Bootstrap Capacitor Selection

The high-side driver boost circuit utilizes an internal Schottky diode ( $D_B$ ) and an external bootstrap capacitor ( $C_B$ ) to supply sufficient gate drive for the high-side MOSFET driver.  $C_B$  should be a 47 nF ceramic type rated for at least 6.3V.

#### 5.9.6 C<sub>V25</sub> Selection

This capacitor is used to both stabilize and provide noise filtering for the 2.5 V internal power supply. It should be between 4.7 and 10  $\mu$ F, and should use a semi-stable X5R or X7R dielectric ceramic with a low (less than 10 m $\Omega$ ) ESR, and should have a rating of 4 V or more.

#### 5.9.7 C<sub>VR</sub> Selection

This capacitor is used to both stabilize and provide noise filtering for the 5 V reference supply  $(V_R)$ . It should be between 4.7 and 10  $\mu F$ , and be a semi-stable X5R or X7R dielectric ceramic capacitor with a low ESR less than 10 m $\Omega$ , and be rated 6.3 V or more. Because the current for the bootstrap supply is drawn from this capacitor,  $C_{VR}$  should be sized at least 10X the value of  $C_B$  so that a discharged  $C_B$  does not cause the voltage on it to droop excessively during a  $C_B$  recharge pulse.

#### 5.9.8 C<sub>VRA</sub> Selection

This capacitor is used to both stabilize and provide noise filtering for the analog 5 V reference supply  $(V_{RA})$ . It should be between 2.2 and 10  $\mu$ F, be a semistable X5R or X7R dielectric ceramic capacitor with a low ESR less than 10 m $\Omega$ , and be rated 6.3 V or more.

#### 5.9.9 R<sub>VR</sub> Selection

A 91 $\Omega$  resistor should be placed between VR and VRA to reduce noise and help the stability of the VR and VRA regulators over all operating conditions.

#### 5.9.10 Thermal Considerations

In typical applications, the ZL2105's high efficiency will limit the internal power dissipation inside the package. However, in applications that require a high ambient operating temperature the user must perform some thermal analysis to ensure that the ZL2105's maximum junction temperature is not violated.

The ZL2105 has a maximum junction temperature limit of 125°C, and the internal over temperature limiting circuitry will force the device to shut down if its junction temperature exceeds this threshold. In order to calculate the maximum junction temperature, the user must first calculate the power dissipated inside the IC (P<sub>O</sub>) as follows:

$$P_{Q} = (I_{LOAD}^{2})[(R_{DS(ON)QH})(DC) + (R_{DS(ON)QL})(1 - DC)]$$

The maximum operating junction temperature can then be calculated using the following equation:

$$T_{j\max} = T_{PCB} + P_Q \times \theta_{JC}$$

Where  $T_{PCB}$  is the expected maximum printed circuit board temperature, and  $\theta_{JC}$  is the junction-to-case thermal resistance for the ZL2105 package.

# 5.10 Current Sensing and Current Limit Threshold Selection

It is recommended that the user include a current limiting mechanism in their design to protect the power supply from damage and prevent excessive current from being drawn from the input supply in the event that the output is shorted to ground or an overload condition is imposed on the output. Current limiting is accomplished by sensing the current through the circuit during a portion of the duty cycle.

The ZL2105 incorporates MOSFET sensing across the internal low-side MOSFET. The user can select one of the three current limit thresholds using the ILIM pin according to Table 17.

**Table 17. Current Limit Selections**

| ILIM Pin | Current Limit Threshold |

|----------|-------------------------|

| LOW      | 3.0 A                   |

| OPEN     | 4.0 A                   |

| HIGH     | 4.5 A                   |

If the desired current limit threshold is not available in Table 17, the current limit threshold can be set in 200 mA increments using an external resistor,  $R_{\rm LIM}$ , connected between the ILIM pin and SGND using resistor values from Table 18.

The current limit threshold can also be set to a custom value via the I<sup>2</sup>C/SMBus interface. Please refer to Application Note AN13 for further details.

Table 18. Current Limit Threshold Settings

| I <sub>LIM</sub> | R <sub>LIM</sub> |

|------------------|------------------|

| 0.2 A            | 11 kΩ            |

| 0.4 A            | 12.1 kΩ          |

| 0.6 A            | 13.3 kΩ          |

| 0.8 A            | 14.7 kΩ          |

| 1.0 A            | 16.2 kΩ          |

| 1.2 A            | 17.8 kΩ          |

| 1.4 A            | 19.6 kΩ          |

| 1.6 A            | 21.5 kΩ          |

| 1.8 A            | 23.7 kΩ          |

| 2.0 A            | 26.1 kΩ          |

| 2.2 A            | 28.7 kΩ          |

| 2.4 A            | 31.6 kΩ          |

| noia octarigo    |                         |

|------------------|-------------------------|

| I <sub>LIM</sub> | $R_{LIM}$               |

| 2.6 A            | $34.8~\mathrm{k}\Omega$ |

| 2.8 A            | $38.3~\mathrm{k}\Omega$ |

| 3.0 A            | 42.2 k $\Omega$         |

| 3.2 A            | 46.4 kΩ                 |

| 3.4 A            | 51.1 kΩ                 |

| 3.6 A            | 56.2 kΩ                 |

| 3.8 A            | $61.9~\mathrm{k}\Omega$ |

| 4.0 A            | 68.1 kΩ                 |

| 4.2 A            | 75 kΩ                   |

| 4.4 A            | 82.5 k $\Omega$         |

| 4.6 A            | 90.9 k $\Omega$         |

| ·                |                         |

#### 5.11 Loop Compensation

The ZL2105 operates as a voltage-mode synchronous buck controller with a fixed frequency PWM scheme. Although the ZL2105 uses a digital control loop, it operates much like a traditional analog PWM controller. Figure 16 is a simplified block diagram of the ZL2105 control loop, which differs from an analog control loop only by the constants in the PWM and compensation blocks. As in the analog controller case, the compensation block compares the output voltage to the desired voltage reference and compensation zeroes are added to keep the loop stable. The resulting integrated error signal is used to drive the PWM logic, converting the error signal to a duty cycle to drive the internal MOSFETs.

Figure 16. Control Loop Block Diagram

**Table 19. Resistor Settings for Loop Compensation**

| NLR | f <sub>n</sub> Range            | f <sub>zesr</sub> Range            | R <sub>FC</sub> |

|-----|---------------------------------|------------------------------------|-----------------|

|     |                                 | $f_{zesr} > f_{sw}/10$             | 10 kΩ           |

|     | $f_{sw}/60 < f_n < f_{sw}/30$   | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 11 kΩ           |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 12.1 kΩ         |

|     |                                 | $f_{zesr} > f_{sw}/10$             | 13.3 kΩ         |

| Off | $f_{sw}/120 < f_n < f_{sw}/60$  | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 14.7 kΩ         |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 16.2 kΩ         |

|     |                                 | $f_{zesr} > f_{sw}/10$             | 17.8 kΩ         |

|     | $f_{sw}/240 < f_n < f_{sw}/120$ | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 19.6 kΩ         |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 21.5 kΩ         |

|     | $f_{sw}/60 < f_n < f_{sw}/30$   | $f_{zesr} > f_{sw}/10$             | 23.7 kΩ         |

|     |                                 | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 26.1 kΩ         |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 28.7 kΩ         |

|     |                                 | $f_{zesr} > f_{sw}/10$             | 31.6 kΩ         |

| On  | $f_{sw}/120 < f_n < f_{sw}/60$  | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 34.8 kΩ         |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 38.3 kΩ         |

|     |                                 | $f_{zesr} > f_{sw}/10$             | 42.2 kΩ         |

|     | $f_{sw}/240 < f_n < f_{sw}/120$ | $f_{sw}/10 > f_{zesr} > f_{sw}/30$ | 46.4 kΩ         |

|     |                                 | $f_{sw}/30 > f_{zesr} > f_{sw}/60$ | 51.1 kΩ         |

In the ZL2105, the compensation zeros are set by configuring the FC pin or via the  $I^2C/SMBus$  interface once the user has calculated the required settings. This method eliminates the inaccuracies due to the component tolerances associated with using external resistors and capacitors required with traditional analog controllers. Utilizing the loop compensation settings shown in Table 19 will yield a conservative crossover frequency at a fixed fraction of the switching frequency ( $f_S/20$ ) and 60° of phase margin.

**Step 1:** Using the following equation, calculate the resonant frequency of the LC filter,  $f_n$ .

$$f_n = \frac{1}{2\pi\sqrt{L \times C}}$$

**Step 2:** Calculate the ESR zero frequency ( $f_{ZESR}$ ).

$$f_{zesr} = \frac{1}{2\pi CRc}$$

**Step 3:** Based on Table 19, determine the appropriate resistor,  $R_{FC}$ .

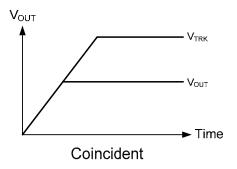

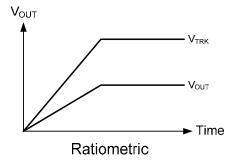

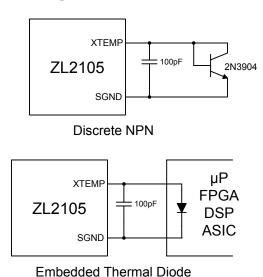

The FC pin can be pin-strapped as LOW, OPEN, or HIGH. These three positions are the same as the first three entries in Table 19.