# FireLink 1394 OHCI Link Controller

# 82C881

# Preliminary Data Book CONFIDENTIAL

Revision 1.0 912-2000-031 December 13, 1999

#### Copyright

Copyright © 1999 OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, manual, or otherwise, without the prior written permission of OPTi Inc., 1440 McCarthy Blvd. Milpitas, CA 95035.

#### Disclaimer

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### Trademarks

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

1440 McCarthy Blvd. Milpitas, CA 95035 Tel: (408) 486-8000 Fax: (408) 486-8001 WWW: http://www.opti.com

### TABLE OF CONTENTS

| 1.0 | FEATU    | FEATURES1                                         |    |  |  |  |  |

|-----|----------|---------------------------------------------------|----|--|--|--|--|

| 2.0 | OVERVIEW |                                                   |    |  |  |  |  |

| 3.0 | SIGNA    | L DEFINITIONS                                     | 3  |  |  |  |  |

| 3.1 | TERM     | MINOLOGY/NOMENCLATURE CONVENTIONS                 | 3  |  |  |  |  |

| 3.2 | Nuм      | ERICAL PIN CROSS-REFERENCE LIST                   | 5  |  |  |  |  |

| 3.3 | STR      | APPING OPTIONS                                    | 6  |  |  |  |  |

| 3   | 8.3.1    | Test Mode Selection (Pins 77, 78)                 | 6  |  |  |  |  |

| 3   | 8.3.2    | Serial EEPROM Presence Detect (Pin 5)             | 6  |  |  |  |  |

| 3.4 | SIGN     | IAL DESCRIPTIONS                                  | 7  |  |  |  |  |

| 3   | 8.4.1    | PCI Bus Interface Signals                         | 7  |  |  |  |  |

| 3   | 8.4.2    | PHY-Link Interface Signal Set                     | 9  |  |  |  |  |

| 3   | 8.4.3    | Miscellaneous Signals                             |    |  |  |  |  |

| 4.0 | FUNC     | TIONAL DESCRIPTION                                | 11 |  |  |  |  |

| 4.1 | Fund     | CTIONAL BLOCK DESCRIPTION                         | 11 |  |  |  |  |

| 4   | 1.1.1    | PCI Interface                                     |    |  |  |  |  |

| 4   | 1.2      | DMA Control Block                                 |    |  |  |  |  |

| 4   | 1.3      | Serial EEPROM Interface                           |    |  |  |  |  |

| 4   | 1.4      | Arbiter                                           | 14 |  |  |  |  |

| 4   | .1.5     | Register Block                                    |    |  |  |  |  |

| 4   | .1.6     | FIFO Block                                        |    |  |  |  |  |

| 4   | .1.7     | Link Block                                        |    |  |  |  |  |

| 4.2 | Seri     | AL EEPROM INTERFACE                               | 16 |  |  |  |  |

| 4   | .2.1     | Read Operations from the Serial EEPROM            |    |  |  |  |  |

| 4   | .2.2     | Write operations to the Serial EEPROM             |    |  |  |  |  |

| 4   | .2.3     | Related PCICFG Registers                          |    |  |  |  |  |

| 4   | .2.4     | Serial EEPROM MAP                                 |    |  |  |  |  |

| 5.0 | REGIS    | TER DESCRIPTIONS                                  | 19 |  |  |  |  |

| 5.1 | ОНС      | I AND BUS MANAGEMENT CONTROL AND STATUS REGISTERS | 19 |  |  |  |  |

| 5.2 | FIFC     | Configuration Registers                           | 19 |  |  |  |  |

| 5   | 5.2.1    | Tx FIFO-Related Registers                         | 20 |  |  |  |  |

| 5   | 5.2.2    | Rx FIFO-Related Registers                         | 21 |  |  |  |  |

| 5.3 | PCI      | CONFIGURATION REGISTERS                           | 23 |  |  |  |  |

# 82C881

| 5.   | 3.1   | PCI Configuration Space (PCICFG 00h to 3Fh)                    |

|------|-------|----------------------------------------------------------------|

| 5.4  | Pow   | PR MANAGEMENT REGISTERS                                        |

| 5.5  | Тімі  | NG INFORMATION                                                 |

| 6.0  | ELEC  | RICAL RATINGS                                                  |

| 7.0  | MECH  | ANICAL PACKAGE                                                 |

| 8.0  | TEST  | MODES                                                          |

| 9.0  | APPE  | NDIX A                                                         |

| 9.1  | ACR   | ONYMS AND DEFINITIONS                                          |

| 9.2  | Refi  | ERENCES                                                        |

| 10.0 | APPE  | NDIX B                                                         |

| 10.1 | FIFC  | D Programming                                                  |

| 1    | 0.1.1 | Programming Notes                                              |

| 1    | 0.1.2 | Important User Defined Values                                  |

| 1    | 0.1.3 | Current Default Configuration Values                           |

| 10.2 | Deb   | UG FEATURES                                                    |

| 1    | 0.2.1 | Reading/Writing Tx FIFO and Rx FIFO Bypassing DMA / Link Logic |

| 1    | 0.2.2 | Implementation                                                 |

| 1    | 0.2.3 | Direct Read of Internal Signals                                |

#### 1.0 Features

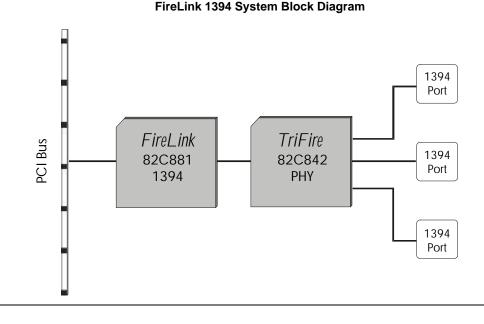

The OPTi 82C881 1394 OHCI Link Controller is a PCIbased host controller with the following features.

- Compliant with PCI Local Bus Specification 2.1

- Compliant with P1394a Draft 2.0 Standard for a Highperformance Serial Bus

- Interfaces to 33MHz, 32-bit PCI bus

- PnP (Plug and Play) compatible per PCI Local Bus Specification rev. 2.1

- Implements IEEE1212-based control and status registers that can be mapped to both I/O and memory space

- Incorporates independent DMA controllers for isochronous and asynchronous operations

- Supports four isochronous transmit and isochronous receive contexts

- Supports burst transactions on the PCI bus interface

- Offers direct access to the physical address space of the host

- Assigns priority for DMA per 1394 OHCI specification 1.00

- Supports four transmit and three receive configurable FIFOs

- Offers both packet per-buffer and buffer-fill modes of operation for the isochronous receive context

- Incorporates two wire industry-standard Serial EEPROM interface

- Functions as a 1394 cycle master

- Supports asynchronous and isochronous transfers at 100, 200 and 400 Mbps

- Implements a fully Bus Manager Capable node including an Isochronous Resource Manager

- Interfaces to PHYs that conform to the Link-PHY interface described in Chapter 5 of the P1394a Draft 2.0 specification

- Interfaces to 1394-1995 compliant PHYs

- Offers selective disabling of 1394a features (controllable by software) for interfacing to a partially P1394a compliant PHY

- Supports posting of physical write request packets

- Complies with the PCI Power Management specification rev. 1.1, supporting ACPI states D0 and D3<sub>hot</sub> and PME# generation

- Incorporates CLKRUN# support

- Implements comprehensive Debug Registers

- Implements physical upper bound register.

#### 2.0 Overview

This document describes the OPTi FireLink 1394 OHCI Link Controller (82C881). It details:

- Signal Definitions

- Strap Selectable Options

- Functionality

- Register Descriptions.

82C881

#### 3.0 Signal Definitions

#### 3.1 Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of active low and active high signals. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

The tables in this section use several common abbreviations. Table 3-1 lists the mnemonics and their meanings. Note that TTL/CMOS/Schmitt-trigger levels pertain to inputs only. Outputs are driven at CMOS levels.

| Mnemonic | Description             |

|----------|-------------------------|

| Analog   | Analog-level compatible |

| CMOS     | CMOS-level compatible   |

| Dcdr     | Decoder                 |

| Ext      | External                |

| G        | Ground                  |

| I        | Input                   |

| Int      | Internal                |

| I/O      | Input/Output            |

| Mux      | Multiplexer             |

| NIC      | No Internal Connection  |

| 0        | Output                  |

| OD       | Open drain              |

| Р        | Power                   |

| PD       | Pull-down resistor      |

| PU       | Pull-up resistor        |

| S        | Schmitt-trigger         |

| S/T/S    | Sustain Tristate        |

| TTL      | TTL-level compatible    |

Table 1. Signal Definitions Legend

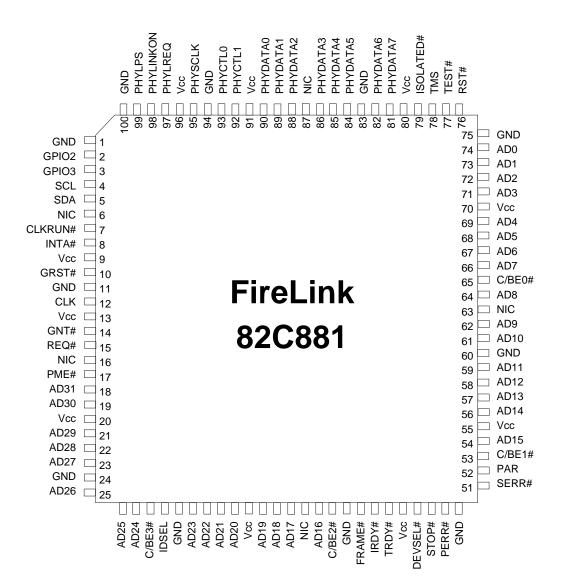

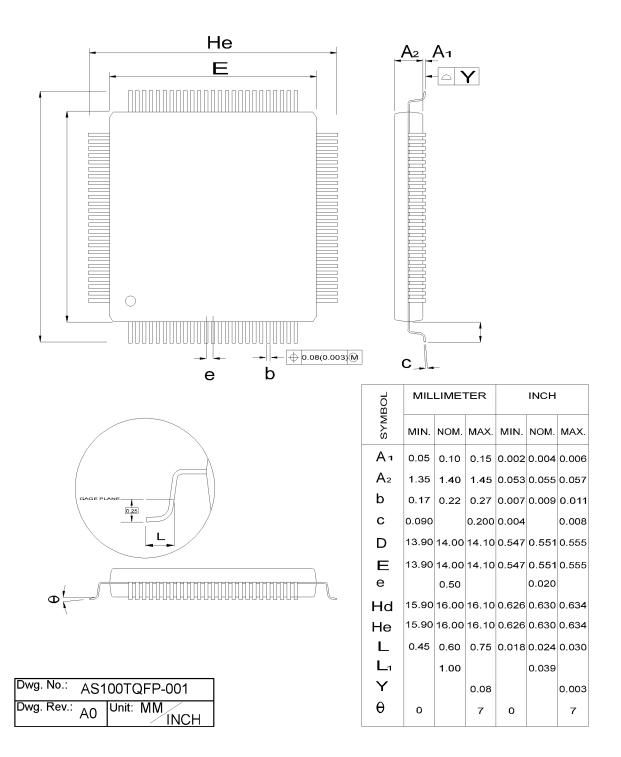

#### Figure 3-1 LQFP Pin Diagram (Note)

**Note:** Figure 3-1 shows a pin diagram of the 82C881 packaged in an LQFP (Low-profile Quad Flat Pack, square). The device is also available in a QFP (Quad Flat Pack, rectangular). The pin assignment remains the same.

Refer to Section 5, "Mechanical Package" for details regarding packaging.

#### 3.2 Numerical Pin Cross-Reference List

| Pin<br>No. | Signal Name | Power<br>Plane |

|------------|-------------|----------------|

|            |             |                |

| 1          | GND         | VccCORE        |

| 2          | GPIO2       |                |

| 3          | GPIO3       |                |

| 4          | SCL         |                |

| 5          | SDA         |                |

| 6          | NIC         |                |

| 7          | CLKRUN#     |                |

| 8          | INTA#       |                |

| 9          | Vcc         |                |

| 10         | GRST#       |                |

| 11         | GND         |                |

| 12         | CLK         |                |

| 13         | Vcc         |                |

| 14         | GNT#        |                |

| 15         | REQ#        |                |

| 16         | NIC         |                |

| 17         | PME#        |                |

| 18         | AD31        |                |

| 19         | AD30        |                |

| 20         | Vcc         |                |

| 21         | AD29        |                |

| 22         | AD28        |                |

| 23         | AD27        |                |

| 24         | GND         |                |

| 25         | AD26        |                |

| 26         | AD25        |                |

| 27         | AD24        |                |

| 28         | C/BE3#      |                |

| 29         | IDSEL       |                |

| 30         | GND         |                |

| 31         | AD23        |                |

| 32         | AD22        |                |

| 33         | AD21        |                |

| 34         | AD20        |                |

| Pin<br>No. | Signal Name | Power<br>Plane |

|------------|-------------|----------------|

| 35         | Vcc         | VccCORE        |

| 36         | AD19        |                |

| 37         | AD18        |                |

| 38         | AD17        |                |

| 39         | NIC         |                |

| 40         | AD16        |                |

| 41         | C/BE2#      |                |

| 42         | GND         |                |

| 43         | FRAME#      |                |

| 44         | IRDY#       |                |

| 45         | TRDY#       |                |

| 46         | Vcc         |                |

| 47         | DEVSEL#     |                |

| 48         | STOP#       |                |

| 49         | PERR#       |                |

| 50         | GND         |                |

| 51         | SERR#       |                |

| 52         | PAR         |                |

| 53         | C/BE1#      |                |

| 54         | AD15        |                |

| 55         | Vcc         |                |

| 56         | AD14        |                |

| 57         | AD13        |                |

| 58         | AD12        |                |

| 59         | AD11        |                |

| 60         | GND         |                |

| 61         | AD10        |                |

| 62         | AD9         |                |

| 63         | NIC         |                |

| 64         | AD8         |                |

| 65         | C/BE0#      |                |

| 66         | AD7         |                |

| 67         | AD6         |                |

| 68         | AD5         |                |

| Pin<br>No. | Signal Name | Power<br>Plane |  |

|------------|-------------|----------------|--|

| 69         | AD4 VccCOR  |                |  |

| 70         | Vcc         |                |  |

| 71         | AD3         |                |  |

| 72         | AD2         |                |  |

| 73         | AD1         |                |  |

| 74         | AD0         |                |  |

| 75         | GND         |                |  |

| 76         | RST#        |                |  |

| 77         | TEST#       |                |  |

| 78         | TMS#        |                |  |

| 79         | ISOLATED#   |                |  |

| 80         | Vcc         |                |  |

| 81         | PHYDATA7    |                |  |

| 82         | PHYDATA6    |                |  |

| 83         | GND         |                |  |

| 84         | PHYDATA5    |                |  |

| 85         | PHYDATA4    |                |  |

| 86         | PHYDATA3    |                |  |

| 87         | NIC         |                |  |

| 88         | PHYDATA2    |                |  |

| 89         | PHYDATA1    |                |  |

| 90         | PHYDATA0    |                |  |

| 91         | Vcc         |                |  |

| 92         | PHYCTL1     |                |  |

| 93         | PHYCTL0     |                |  |

| 94         | GND         |                |  |

| 95         | PHYSCLK     |                |  |

| 96         | Vcc         |                |  |

| 97         | PHYLREQ     |                |  |

| 98         | PHYLINKON   |                |  |

| 99         | PHYLPS      |                |  |

| 100        | GND         |                |  |

### 82C881

#### 3.3 Strapping Options

#### 3.3.1 Test Mode Selection (Pins 77, 78)

| Pin 78, TMS# | Pin 77, TEST# | Function             |

|--------------|---------------|----------------------|

| Pulled up    | Don't care    | Normal Operation     |

| Pulled down  | Pulled down   | Scan Chain Test mode |

| Pulled down  | Pulled up     | NAND Tree Test mode  |

#### 3.3.2 Serial EEPROM Presence Detect (Pin 5)

| Pin 5, SDA  | Serial EEPROM | Function                              |

|-------------|---------------|---------------------------------------|

| Pulled down | Not present   | Load default values on PCI registers. |

| Pulled up   | Present       | Load PCI values from EEPROM           |

#### 3.4 Signal Descriptions

| 3.4.1 | PCI Bus Inte | rface Signals |

|-------|--------------|---------------|

|-------|--------------|---------------|

| Signal Name | Pin<br>No.                 | Pin<br>Type    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | Refer to<br>Pin<br>Diagram | I/O            | Address and Data Lines 31 through 0: This bus carries the address and/or data during a PCI bus cycle. A PCI bus cycle has two phases - an address phase which is followed by one or more data phases. During the initial clock of the bus cycle, the AD bus contains a 32-bit physical byte address. AD[7:0] is the least significant byte (LSB) and AD[31:24] is the most significant byte (MSB). After the first clock of the cycle, the AD bus contains data. |

|             |                            |                | When the 82C881 is the target, AD[31:0] are inputs during the address phase.<br>For the data phase(s) that follow, the 82C881 may supply data on AD[31:0] in the case of a read or accept data in the case of a write.                                                                                                                                                                                                                                           |

|             |                            |                | When the 82C881 is the master, it drives a valid address on AD[31:2] during the address phase, and drives write or accepts read data on AD[31:0] during the data phase. As a master, the 82C881 always drives AD[1:0] low.                                                                                                                                                                                                                                       |

| C/BE[3:0]#  | 28, 41,<br>53, 65          | I/O            | <b>Bus Command and Byte Enables 3 through 0:</b> These signals provide the command type information during the address phase and carry the byte enable information during the data phase. C/BE0# corresponds to byte 0, C/BE1# to byte 1, C/BE2# to byte 2, and C/BE3# to byte 3.                                                                                                                                                                                |

|             |                            |                | If the 82C881 is the initiator of a PCI bus cycle, it drives C/BE[3:0]#. When it is the target, it samples C/BE[3:0]#.                                                                                                                                                                                                                                                                                                                                           |

| PAR         | 52                         | 0              | <b>Even Parity:</b> The 82C881 calculates PAR for both the address and data phases of PCI cycles. PAR is valid one PCI clock after the associated address or data phase, but may or may not be valid for subsequent clocks. It is calculated based on 36 bits - AD[31:0] plus C/BE[3:0]#. "Even" parity means that the sum of the 36 bit values plus PAR is always an even number, even if one or more bits of C/BE[3:0]# indicate invalid data.                 |

| FRAME#      | 43                         | I/O<br>(s/t/s) | <b>Cycle Frame:</b> This signal is driven by the current PCI bus master to indicate the beginning and duration of an access. The master asserts FRAME# at the beginning of a bus cycle, sustains the assertion during data transfers, and then negates FRAME# in the final data phase.                                                                                                                                                                           |

|             |                            |                | FRAME# is an input when the 82C881 is the target and an output when it is the initiator.                                                                                                                                                                                                                                                                                                                                                                         |

|             |                            |                | FRAME# is tristated from the leading edge of RESET# and remains tristated until driven as either a master or slave by the 82C881.                                                                                                                                                                                                                                                                                                                                |

## 82C881

| Signal Name | Pin<br>No. | Pin<br>Type    | Signal Description                                                                                                                                                                                                                                                                             |

|-------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRDY#       | 44         | I/O<br>(s/t/s) | <b>Initiator Ready:</b> IRDY#, along with TRDY#, indicates whether the 82C881 is able to complete the current data phase of the cycle. IRDY# and TRDY# are both asserted when a data phase is completed.                                                                                       |

|             |            |                | During a write, the 82C881 asserts IRDY# to indicate that it has valid data on AD[31:0]. During a read, the 82C881 asserts IRDY# to indicate that it is prepared to accept data.                                                                                                               |

|             |            |                | IRDY# is an input when the 82C881 is a target and an output when it is the initiator.                                                                                                                                                                                                          |

|             |            |                | IRDY# is tristated from the leading edge of RESET# and remains tristated until driven as either a master or a slave by the 82C881.                                                                                                                                                             |

| TRDY#       | 45         | I/O<br>(s/t/s) | <b>Target Ready:</b> TRDY#, along with IRDY#, indicates whether the 82C881 is able to complete the current data phase of the cycle. TRDY# and IRDY# are both asserted when a data phase is completed.                                                                                          |

|             |            |                | When the 82C881 is acting as the target during read and write cycles, it performs in the following manner:                                                                                                                                                                                     |

|             |            |                | 1. During a read, the 82C881 asserts TRDY# to indicate that it has placed valid data on AD[31:0].                                                                                                                                                                                              |

|             |            |                | 2. During a write, the 82C881 asserts TRDY# to indicate that is prepared to accept data.                                                                                                                                                                                                       |

|             |            |                | TRDY# is an input when the 82C881 is the initiator and an output when it is the target.                                                                                                                                                                                                        |

|             |            |                | TRDY# is tristated from the leading edge of RESET# and remains so until driven as either a master or a slave by the 82C881.                                                                                                                                                                    |

| STOP#       | 48         | I/O<br>(s/t/s) | <b>Stop:</b> STOP# is an output when the 82C881 is the target and an input when it is the initiator. As the target, the 82C881 asserts STOP# to request that the master stop the current cycle. As the master, the assertion of STOP# by a target forces the 82C881 to stop the current cycle. |

|             |            |                | STOP# is tristated from the leading edge of RESET# and remains so until driven by the 82C881 acting as a slave.                                                                                                                                                                                |

| DEVSEL#     | 47         | I/O<br>(s/t/s) | <b>Device Select:</b> The 82C881 claims a PCI cycle via positive decoding by asserting DEVSEL#. As an output, the 82C881 drives DEVSEL# for two different reasons:                                                                                                                             |

|             |            |                | 1. If the 82C881 samples IDSEL active in configuration cycles, DEVSEL# is asserted.                                                                                                                                                                                                            |

|             |            |                | 2. When the 82C881 decodes an internal address or when it subtractively decodes a cycle, DEVSEL# is asserted                                                                                                                                                                                   |

|             |            |                | When DEVSEL# is an input, it indicates the target's response to an 82C881 master-initiated cycle.                                                                                                                                                                                              |

|             |            |                | DEVSEL# is tristated from the leading edge of RESET# and remains so until driven by the 82C881 acting as a slave.                                                                                                                                                                              |

| Signal Name | Pin<br>No. | Pin<br>Type | Signal Description                                                                                                                                                                                                                                                                                                   |

|-------------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL       | 29         | I           | <b>Initialization Device Select:</b> This signal is the "chip select" during configuration read and write cycles. IDSEL is sampled by the 82C881 during the address phase of a cycle. If IDSEL is found to be active and the bus command is a configuration read or write, the 82C881 claims the cycle with DEVSEL#. |

| PERR#       | 49         | I/O         | <b>Parity Error:</b> The 82C8681 uses this line to report data parity errors during any PCI cycle except a Special Cycle.                                                                                                                                                                                            |

| SERR#       | 51         | I           | <b>System Error:</b> The 82C881 uses this line to report address parity errors and data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic.                                                                                                                 |

| REQ#        | 15         | 0           | <b>Bus Request:</b> REQ# is asserted by the 82C881 to request ownership of the PCI bus.                                                                                                                                                                                                                              |

| GNT#        | 14         | I           | <b>Bus Grant:</b> GNT# is sampled by the 82C881 for an active low assertion, which indicates that it has been granted use of the PCI bus.                                                                                                                                                                            |

| CLKRUN#     | 7          | I/O         | <b>Clock Run:</b> The CLKRUN# function is available on this pin and can be used to reduce chip power consumption during idle periods. It is an I/O sustained tristate signal and follows the PCI 2.1 defined protocol.                                                                                               |

| INTA#       | 8          | I/O         | <b>Interrupt:</b> The INTA# pin function is available on this pin and can be used to reduce chip power consumption during idle periods. It is an I/O sustained tristate signal and follows the PCI 2.1 defined protocol.                                                                                             |

#### 3.4.2 PHY-Link Interface Signal Set

| Signal Name      | Pin<br>No.                 | Pin<br>Type | Signal Description                                                                                                                                                                                |

|------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHYLREQ          | 97                         | 0           | <b>Link Request:</b> This signal is used by the 82C881 to request access to the serial bus and to read or write PHY registers.                                                                    |

| PHYCTL[1:0]      | 92, 93                     | I/O         | <b>Link-PHY Control Bus:</b> These two signals are used by both the Link and PHY devices to transfer control information to and from each other.                                                  |

| PHY<br>DATA[7:0] | Refer to<br>Pin<br>Diagram | I/O         | <b>Link-PHY Data Bus:</b> Data is transferred between the Link and PHY devices over DATA[7:0].                                                                                                    |

| PHYSCLK          | 95                         | I           | <b>System Clock:</b> This clock is generated by the PHY to the Link when PHYLPS is high, and is used to synchronize data transfer between the Link and PHY. Its specified frequency is 49.152MHz. |

| PHYLPS           | 99                         | 0           | Link Power Status: Indicates to the PHY whether or not link activity is required.                                                                                                                 |

| PHYLINKON        | 98                         | I/O         | Link On: Wakeup indication.                                                                                                                                                                       |

| ISOLATED#        | 79                         | I           | <b>"Isolated" Indicator from PHY:</b> The PHY sets this signal active to indicate that it has electrically isolated itself from the 82C881 Link Controller.                                       |

# 82C881

#### 3.4.3 Miscellaneous Signals

| Signal Name | Pin<br>No. | Pin<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                           |

|-------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS         | 78         | I           | <b>Test Mode Select:</b> The 82C881 logic can be strapped into Test Mode for two types of tests: NAND tree and Boundary Scan. Details are provided in the Test Modes section of this document.                                                                                                                                                                               |

|             |            |             | This pin must be strapped high for Normal Operation.                                                                                                                                                                                                                                                                                                                         |

| TEST#       | 77         | I           | <b>Test Scan Enable:</b> This pin is used solely for Test Mode operations and should be strapped either high or low for Normal Operation.                                                                                                                                                                                                                                    |

| RST#        | 76         | I           | <b>PCI Reset:</b> The PCI interface and standard register set of the 82C881 Link<br>Controller is reset to its default state by this line, which must be held active for at<br>least ????? PCI clocks to be effective. PCI Power Management registers and<br>Vendor ID / Subsystem ID registers are not reset. All PCI outputs are tri-stated<br>when this line is asserted. |

| G_RST#      | 10         | I           | <b>Global Reset:</b> The 82C881 Link Controller is completely reset to its default state by this line, which must be held active for at least <b>?????</b> PCI clocks to be effective.                                                                                                                                                                                       |

| SCL         | 4          | I/O         | <b>Serial Clock:</b> This clock signal synchronizes data from an industry-standard serial EEPROM.                                                                                                                                                                                                                                                                            |

| SDA         | 5          | I/O         | <b>Serial Data:</b> This data line is used to send commands to and read data from an industry-standard serial EEPROM. If no ROM is used, this line should be tied to ground.                                                                                                                                                                                                 |

| GPIO2-3     | 2, 3       | I/O         | <b>General Purpose I/O:</b> The GPIO pins can be used by software and hardware for any predefined purpose. They are controlled and monitored as inputs or outputs through PCICFG 4Ch.                                                                                                                                                                                        |

#### 4.0 Functional Description

The OPTi 82C881 1394 OHCI Link Controller sits between the PCI bus as host bus on one side, and the P1394-compliant PHY on the other side. On the host bus side, it interfaces to a 33MHz, 32-bit PCI bus.

The 82C881 can initiate read/write transactions on the PCI bus. It supports burst accesses for both read and write transactions with zero wait states.

The logic core supports three register spaces:

- PCI Configuration register set, mapped through standard PCI configuration cycles

- OHCI register set, mapped through either memory or I/O space

- FIFO Configuration register set, also mapped through either memory or I/O space.

When acting as a target of the PCI bus, the 82C881 supports byte aligned accesses for PCI Configuration Registers and quadlet (32-bit word) aligned accesses for the OHCI and FIFO Configuration registers.

Any packet coming from the 1394 serial bus is processed by the PHY, which then moves the data to the 82C881 per the 1394 packet format specification. According to the speed code received, data from data lines is read and converted to 32 bit quadlets. The received packet is passed through several checks such as header and data CRCs, packet type, and packet addressing with respect to physical and asynchronous request filters. The 82C881 converts the incoming packets in 1394 format to OHCI format and puts them on the PCI bus by through a write operation.

When a packet has to be transmitted, the 82C881 gets the required data from the host Memory through the PCI bus in OHCI format by a read operation through the host interface. The 82C881 converts the data to 1394 packet format and passes it on to the PHY, which in turn puts it out on the 1394 serial bus. For transmission, a specific packet is chosen based on its phase, isochronous or asynchronous, and priority among asynchronous packets as defined in 1394 OHCI specification1.0. Depending on the packet to be sent, the 82C881 sends different requests to the PHY through LReq patterns. It transmits the packet when the PHY wins the arbitration. Data will be transmitted on the data lines as appropriate for the PHY speed.

If the 82C881 is the root node, cycle start packets are formed and sent out at every cycle sync event. Bus reset packets are written into the Receive FIFO of the 82C881 whenever there is a bus reset indication.

Software has to program the necessary configuration registers to enable the software context. Once the context is active, the system is ready to receive and transmit packets.

The 82C881 has an interface to an external serial EEPROM. This memory device should contain the GUID of the 82C881 and may contain initialization information. The GUID is read only once after host power reset by an autonomous load operation from the EEPROM, if present, by the 82C881.

#### 4.1 Functional Block Description

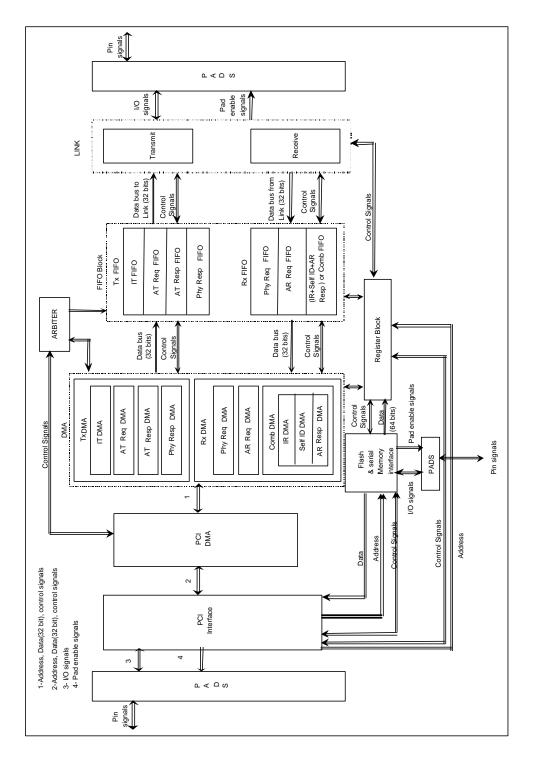

A logic block diagram is provided on the following page. The key sub elements shown in the diagram are described below.

#### 4.1.1 PCI Interface

The PCI Interface block is the interface to the PCI bus; it performs bus master functions and can act as a target as well. As a target, it responds to I/O and Memory transactions. Lock transactions are not supported.

Target and master aborts occurring during a transaction are reported to the DMA control block. The PCI interface can perform burst transfers both as a target and as a master.

Data Parity checking and reporting at the PCI bus interface is according to the PCI Local Bus Specifications 2.1. In case of a data parity error during a transaction initiated by the 82C881, the transaction is terminated normally and error is reported to the DMA control block. As a target, if an address parity error is detected, a target abort is generated.

PCI Power Management and PCI CLKRUN# functionality are supported as described elsewhere in this document.

### 82C881

Block Diagram

#### 4.1.1.1 PCI-DMA Block

The PCI-DMA block interfaces the DMA Control block to the PCI Interface block. This arrangement enables the functioning of the DMA blocks to be independent of the Host bus that it is interfaced to. A DMA transaction is a transfer of four or fewer bytes of data.

The PCI-DMA block translates transactions on the DMA interface to transactions on the PCI interface, aligns data to be written out on the PCI bus, merges data fetched, and restarts transactions in case of a disconnect. It also reports errors occurring on the PCI bus to the DMA Control block.

#### 4.1.2 DMA Control Block

The DMA control block supports seven types of DMA. All of the seven DMA controllers can be broadly classified as TxDMA and RxDMA.

#### 4.1.2.1 TxDMA

The TxDMA block is made up of four sub-blocks.

- Isochronous Transmit (IT)

- Asynchronous Transmit Response (AT Resp)

- Asynchronous Transmit Request (AT Req)

- Physical Response (Phy Resp)

Each of these blocks controls the transfer of packets from the host bus to the respective Tx FIFO. Host side software sets up the DMA "contexts," which are essentially programmed environments used by the respective DMA sub blocks for processing and managing movement of data. Each context consists of a programmed environment and a set of registers. The programmed environment directs the DMA controller in the assembly of packets for transmission.

#### 4.1.2.2 RxDMA

The RxDMA block is made up of three sub-blocks.

- Combined (Comb), consisting of:

- Isochronous Receive (IR)

- Self ID

- Asynchronous Receive Response (AR Resp)

- Asynchronous Receive (AR Req)

- Physical Receive Request (Phy Req)

This block picks out packets from the Rx FIFO, and puts them into the host memory. Host side software sets up contexts to enable logical storage of the received packets. The registers pertaining to these contexts are programmed to achieve this. On receiving a packet, the Rx FIFO gives an indication to the respective DMA context and the DMA context starts processing the packet.

#### 4.1.3 Serial EEPROM Interface

The Serial EEPROM interface is a two-wire industry-standard interface to the Serial EEPROM. This interface is capable of performing reads as well as writes to the Serial EEPROM. Information like GUID, Device ID, Vendor ID, Class Code, Revision ID, Subsystem ID, and Subsystem Vendor ID can be stored in the Serial PROM. These are then loaded from the Serial EEPROM to the corresponding PCICFG registers at each power-on reset.

### 82C881

#### 4.1.4 Arbiter

Since there are seven DMA controllers, the 82C881 prioritizes the DMA controllers. To enable this functionality, the bus request signals from all the DMA contexts are fed into the arbiter, which in turn, based on the priorities specified in 1394 OHCI specification, decides on which DMA controller should get the grant.

#### 4.1.5 Register Block

The Register block includes PCI bus management control and status registers (PCICFG), OHCI Registers as specified in 1394 OHCI specification, and FIFO Configuration registers. The OHCI Registers include control registers for both DMA and the Link, and individual DMA context registers.

All registers (OHCI, PCICFG, and FIFO Configuration) are implemented in the PCICLK domain except for the Isochronous Cycle Timer Register, which is implemented in the PHYSCLK clock domain.

Configuration of the various register blocks is described below.

#### 4.1.5.1 OHCI DMA and Link Registers

The OHCI registers provide the standard 1394-OHCI functionality as noted in the 1394a specification.

These registers should be programmed in the sequence specified in the specification. Programming the registers in a random order will lead to unspecified behavior.

#### 4.1.5.2 FIFO Configuration Registers

The FIFO Configuration registers allow sizing and control of the FIFOs and provide the ability to selectively disable features of the 1394a Link.

Programming of these registers is described elsewhere in this document and is detailed in Appendix B.

#### 4.1.5.3 PCI Interface Registers

The logic implements the required PCI register interface for 1394 OHCI Link controllers.

PCI configuration registers are configured per PCI Local Bus Specification Revision 2.1.

#### 4.1.6 FIFO Block

Primarily the FIFO block is used as a temporary storage place of data between DMA block on one side and the Link block on the other. This is required as data transfer rates on the host bus interface and Link sides are different. Therefore data available on one side, intended for transfer to the other side, is temporarily stored in the FIFO.

The DMA and Link blocks operate at two different frequencies. Therefore the FIFO block also acts as a synchronizer, synchronizing signals from one frequency domain to other.

#### 4.1.6.1 Tx FIFO Block

The Tx FIFO is used to store data for transmission from the transmit DMA block to the Link block, and is logically divided into sub-FIFOs in the following order.

- Isochronous Transmit (IT)

- Asynchronous Transmit Response (AT Resp)

- Asynchronous Transmit Request (AT Req)

- Physical Response (Phy Resp)

The sub-FIFOs are configurable. Software can modify their size, Read Watermark value and Write Watermark value.

Each sub-FIFO has separate controller logic. Handshaking signals are exchanged between the corresponding Transmit-DMAto-Tx FIFO and Tx FIFO-to-Link before the actual transaction starts.

#### 4.1.6.2 Rx FIFO Block

The Rx FIFO aids in transmitting data from the Link to the Rx DMA block. The Rx FIFO has been logically sub divided into sub-FIFOs in the following order:

- Combined (Comb)

- Isochronous Receive (IR)

- Self ID

- Asynchronous Receive Response (AR Resp)

- Asynchronous Receive (AR Req)

- Physical Receive Request (Phy Req)

Each sub-FIFO has separate controller logic. Handshaking signals are exchanged between the corresponding Receive-DMAto-Rx FIFO and Rx FIFO-to-Link before the actual transaction starts.

#### 4.1.7 Link Block

The Link block formats the final packets from OHCI to 1394 for transmission, and also checks the received packets from the PHY for errors and translates them back to OHCI format. While transmitting, the Link block reads the packets from different Tx FIFOs, reformats and appends CRC information, and then gives the packets to the PHY. While receiving, after checking the CRC information and format for errors, the Link block writes the received packets to the Rx FIFO.

The Link logic has two main blocks.

- Receive block

- Transmit block.

#### 4.1.7.1 Receive Block

The Receive block deals with the packets in 1394 format, coming from the PHY to the 82C881. It takes data from the serial data lines, converts it into parallel 32-bit data, performs required checks on the data, converts the data to OHCI format and puts it into the appropriate FIFO.

The Receive Block checks the following.

- The tcode, to determine the packet type.

- The destination ID, if the packet is asynchronous. The Receive block will receive the packet only if the destination ID matches with ID of this node.

- The request filter register to determine if this node can accept the request, if the packet is a request packet.

- The physical request filter bit to determine if this node should accept the physical request, if the packet offset address lies within the physical range.

- The retry code, to ensure that the packet is acceptable per the dual phase retry protocol.

- The header and data CRC.

- The data length of the packet, if the packet is a block request packet. If it is greater than the maximum accepted value, the packet is rejected.

The Receive block also generates the ack code to be sent in response to a packet and the event code in response to the packet sent.

#### 4.1.7.2 Transmit Block

The Transmit block deals with the packets intended for transfer from the 82C881 to the PHY. The Transmit block receives data quadlets in OHCI format, converts them to 1394 packet format, adds CRC information and converts the packets for transferring to the PHY.

Following is the list of main functions performed by this block.

- Chooses packet types for transmitting to the PHY, corresponding to whether the state of this period is isochronous or asynchronous.

- Adds header CRC and data CRC information to the packet to be transmitted. The CRC is calculated per clause 6.4, page 171 of IEEE 1394-1995.

- Converts 32-bit parallel data into two, four, or eight bits of serial data depending on the speed of transmission.

- Decodes the different fields of the status transfer from the PHY.

- Sends appropriate patterns to the PHY on the PHYLREQ line.

- Generates PHYLPS signal to the PHY.

- Implements the out-bound single-phase retry logic.

#### 4.2 Serial EEPROM Interface

This interface is capable of performing reads as well as writes onto a 256 byte two wire Serial EEPROM (AT24C01 or similar). Information like GUID, Subsystem ID, Subsystem Vendor ID, some PCI configuration register values and a few OHCI register values can be stored in the Serial PROM. These values will be loaded from the Serial EEPROM after a power on reset if the 82C881 detects its presence through a pull up on the SDA pin. If the EEPROM is not present (SDA sensed LOW after reset), default values are loaded instead.

PCICFG registers initialized from EEPROM data:

- 1. Subsystem ID

- 2. Subsystem vendor ID

- 3. PCI maximum latency, PCI minimum grant

OHCI registers initialized from EEPROM data:

- 1. Link enhancements control register

- 2. Host Control register

- 3. GUID

#### 4.2.1 Read Operations from the Serial EEPROM

Data from the serial EEPROM can be read through a PCI read cycle at any time other than in the power-on read phase. The sequence for reading data out of the EEPROM is as follows

- 1. Write the desired byte count (up to 8) of the READ operation in PCICFG 53h[6:3] and the eight bit start address on PCICFG 50h[7:0].

- 2. Set PCICFG 53h[0]=1 to start the EEPROM read state machine.

- 3. When PCICFG 53h[0] reads back 0, the operation is complete and and PCICFG 53h[2] contains the operation status: 0 for OK, 1 for ERROR.

- 4. If there is no error, data can be read from PCICFG 54h[31:0] (EEPROM\_DATA1), and also PCICFG 58h[31:0] (EEPROM\_DATA2) if the read byte count is greater than 4.

If an error occurs during a power-on reset EEPROM configuration read, the default values are loaded.

#### 4.2.2 Write operations to the Serial EEPROM

Data can be written to the serial EEPROM through PCI write cycles after the power-on read is completed.

- 1. Write the data in registers EEPROM\_DATA1 and EEPROM\_DATA2.

- 2. Write the byte count in PCICFG 53h[6:3].

- 3. Write the start address in PCICFG 50h[7:0].

- 4. Set PCICFG 53h[1]=1 to start the write operation.

- 5. When PCICFG 53h[1] reads back 0, the operation is complete and and PCICFG 53h[2] contains the operation status: 0 for OK, 1 for ERROR.

If an error occurs, the software should clear PCICFG 53h[2] before re-trying EEPROM operations.

#### 4.2.3 Related PCICFG Registers

| 7          | 6 | 5                                                                                                                             | 4             | 3       | 2                      | 1                  | 0                  |  |  |  |  |  |

|------------|---|-------------------------------------------------------------------------------------------------------------------------------|---------------|---------|------------------------|--------------------|--------------------|--|--|--|--|--|

| PCICFG 50h |   |                                                                                                                               | Default = 00h |         |                        |                    |                    |  |  |  |  |  |

| PCICFG 51h |   |                                                                                                                               | Res           | erved   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 52h |   | Reserved                                                                                                                      |               |         |                        |                    |                    |  |  |  |  |  |

| PCICFG 53h |   | EEPROM Control Register                                                                                                       |               |         |                        |                    |                    |  |  |  |  |  |

| Reserved   |   | Byte count - Must be loaded with value from 1 to 8 prior to issuing<br>read or write command U: operation<br>Successful Read: |               |         |                        |                    |                    |  |  |  |  |  |

|            |   |                                                                                                                               |               |         | successful<br>1: error | Read:<br>1: EEPROM | Read:<br>1: EEPROM |  |  |  |  |  |

|            |   | read in<br>progress                                                                                                           |               |         |                        |                    |                    |  |  |  |  |  |

|            |   | 0: Read<br>complete                                                                                                           |               |         |                        |                    |                    |  |  |  |  |  |

| PCICFG 54h |   |                                                                                                                               | EEPR          | OM Data |                        |                    | Default = 00h      |  |  |  |  |  |

|            |   |                                                                                                                               | Ву            | /te 0   |                        |                    |                    |  |  |  |  |  |

| PCICFG 55h |   |                                                                                                                               | Ву            | /te 1   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 56h |   |                                                                                                                               | Ву            | /te 2   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 57h |   |                                                                                                                               | Ву            | /te 3   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 58h |   |                                                                                                                               | Ву            | /te 4   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 59h |   |                                                                                                                               | By            | /te 5   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 5Ah |   |                                                                                                                               | Ву            | /te 6   |                        |                    | Default = 00h      |  |  |  |  |  |

| PCICFG 5Bh |   |                                                                                                                               | By            | /te 7   |                        |                    | Default = 00h      |  |  |  |  |  |

#### 4.2.4 Serial EEPROM MAP

| Byte Address | Bit 7 | Bit 6                      | Bit 5              | Bit 4                                       | Bit 3                                            | Bit 2                                        | Bit 1                                    | Bit 0 |  |  |

|--------------|-------|----------------------------|--------------------|---------------------------------------------|--------------------------------------------------|----------------------------------------------|------------------------------------------|-------|--|--|

| 00           |       | MIN GNT[7:0]               |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 01           |       | MAX LAT[7:0]               |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 02           |       | SUBYSTEM VENDOR ID [7:0]   |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 03           |       |                            | SI                 | JBSYSTEM VI                                 | ENDOR ID [15                                     | :8]                                          |                                          |       |  |  |

| 04           |       | SUBYSTEM ID [7:0]          |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 05           |       | SUBSYSTEM ID [15:8]        |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 06           | RSVD  | Program<br>Phy<br>1=Enable | ClkRun<br>1=Enable | Interface<br>Reset<br>Detection<br>1=Enable | Multi<br>Speed<br>Concate-<br>nation<br>1=Enable | Drive Idle<br>Before<br>Transmit<br>1=Enable | Accelera-<br>tion<br>Control<br>1=Enable | RSVD  |  |  |

| 07           |       | 1394 GUID HI [7:0]         |                    |                                             |                                                  |                                              |                                          |       |  |  |

| 08           |       |                            |                    | 1394 GUII                                   | D HI [15:8]                                      |                                              |                                          |       |  |  |

| 09           |       |                            |                    | 1394 GUIE                                   | ) HI [23:16]                                     |                                              |                                          |       |  |  |

| 0A           |       |                            |                    | 1394 GUIE                                   | ) HI [31:24]                                     |                                              |                                          |       |  |  |

| 0B           |       |                            |                    | 1394 GUII                                   | D LOI [7:0]                                      |                                              |                                          |       |  |  |

| 0C           |       |                            |                    | 1394 GUIE                                   | D LO [15:8]                                      |                                              |                                          |       |  |  |

| 0D           |       |                            |                    | 1394 GUID                                   | LO [23:16]                                       |                                              |                                          |       |  |  |

| 0E           |       |                            |                    | 1394 GUID                                   | LO [31:24]                                       |                                              |                                          |       |  |  |

#### 5.0 Register Descriptions

The 82C881 register set implements the OHCI registers, the FIFO Configuration registers, and the PCI bus configuration registers.

#### 5.1 OHCI and Bus Management Control and Status Registers

The OHCI Registers are memory mapped to Memory Base Address Register 1 (10h) and I/O mapped to I/O Base Address Register 1 (18h) of PCI Configuration space.

The OHCI Registers and bus management control and status registers are implemented per the 1394 OHCI Specification, Revision 1.0. For the register definitions, bit-mapping into the registers and access requirements for writing and reading the registers, refer to the 1394 OHCI Specification, Revision 1.0.

#### 5.2 FIFO Configuration Registers

As the FIFOs are configurable, the configuration can be changed by programming the FIFO Configuration registers. For each sub-FIFO, there is a 32 bit Register containing the configuration value.

The FIFO Configuration registers are accessed as offsets from a base address. The access can be either through memory or I/O space depending on the PCI base address configuration selected: a memory base address can be programmed in PCICFG 14h, while an I/O base address can be programmed in PCICFG 1Ch.

**Note**: After programming new FIFO Configuration register values, the FIFO Config Enable bit at OFST 1Ch[0] must be set to actually load the changed values.

There are eight registers in the FIFO Configuration register set:

- Isochronous Tx Configuration

- Asynchronous Tx Response Configuration

- Asynchronous Tx Request Configuration

- Physical Tx Configuration

- Miscellaneous Rx Configuration

- Asynchronous Rx Response Configuration

- Physical Rx Configuration

- Miscellaneous.

The first seven registers hold the FIFO Configuration values, while the Miscellaneous register is used to initiate loading of the values programmed into the first seven registers and to selectively enable/disable specific P1394a features.

### 82C881

#### 5.2.1 Tx FIFO-Related Registers

| 7                                                    | 6                                  | 5                                                        | 4                                                                                                                                       | 3                                                                                                                                          | 2                                                    | 1               | 0                                                                                                      |

|------------------------------------------------------|------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|

| OFST 00h                                             |                                    |                                                          | iguration data for                                                                                                                      | onfiguration Regi<br>Isochronous Trans<br>yte 0                                                                                            |                                                      |                 | Default = 40h                                                                                          |

|                                                      |                                    |                                                          |                                                                                                                                         | f empty quadlet sp<br>ntroller can start a                                                                                                 |                                                      |                 |                                                                                                        |

| OFST 01h                                             |                                    |                                                          | В                                                                                                                                       | yte 1                                                                                                                                      |                                                      |                 | Default = 80h                                                                                          |

|                                                      | Read Watermark leater than or equa |                                                          |                                                                                                                                         |                                                                                                                                            |                                                      | Write Water     | rmark bits [9:8]                                                                                       |

| OFST 02h                                             |                                    |                                                          | В                                                                                                                                       | yte 2                                                                                                                                      |                                                      |                 | Default = 00h                                                                                          |

|                                                      | Sub-FIFO S                         | ize bits [3:0]                                           |                                                                                                                                         |                                                                                                                                            | Read Watern                                          | nark bits [9:6] |                                                                                                        |

| OFST 03h                                             |                                    |                                                          | В                                                                                                                                       | yte 3                                                                                                                                      |                                                      |                 | Default = 10h                                                                                          |

| Rese                                                 | erved                              |                                                          |                                                                                                                                         | Sub-FIFO S                                                                                                                                 | ize bits [9:4]                                       |                 |                                                                                                        |

| OFST 04h                                             |                                    |                                                          | configuration data                                                                                                                      | onse Configuration<br>for AT Response<br>yte 0                                                                                             |                                                      |                 | Default = 40h                                                                                          |

|                                                      |                                    |                                                          | Write Waterr                                                                                                                            | nark bits [7:0]                                                                                                                            |                                                      |                 |                                                                                                        |

| OFST 05h                                             |                                    |                                                          | В                                                                                                                                       | yte 1                                                                                                                                      |                                                      |                 | Default = 00h                                                                                          |

|                                                      |                                    | Read Waterr                                              | nark bits [5:0]                                                                                                                         |                                                                                                                                            |                                                      | Write Water     | rmark bits [9:8]                                                                                       |

| OFST 06h                                             |                                    |                                                          | В                                                                                                                                       | yte 2                                                                                                                                      |                                                      |                 | Default = 02h                                                                                          |

|                                                      | Sub-FIFO S                         | ize bits [3:0]                                           |                                                                                                                                         |                                                                                                                                            | Read Watern                                          | nark bits [9:6] |                                                                                                        |

| OFST 07h                                             |                                    |                                                          | В                                                                                                                                       | yte 3                                                                                                                                      |                                                      |                 | Default = 10h                                                                                          |

| Reso                                                 | erved                              |                                                          |                                                                                                                                         | Sub-FIFO S                                                                                                                                 | ize bits [9:4]                                       |                 |                                                                                                        |

| OFST 08h                                             |                                    | Asyncl                                                   | nronous Tx Requ                                                                                                                         | est Configuration                                                                                                                          |                                                      |                 | Default = 40h                                                                                          |

|                                                      |                                    | Holds                                                    | configuration dat                                                                                                                       | a for AT Request s<br><b>yte 0</b>                                                                                                         |                                                      |                 |                                                                                                        |

|                                                      |                                    | Holds                                                    | В                                                                                                                                       |                                                                                                                                            |                                                      |                 |                                                                                                        |