### aSC7621 Hardware Monitor With Integrated Fan Control

#### Preliminary Specification

#### **Product Description**

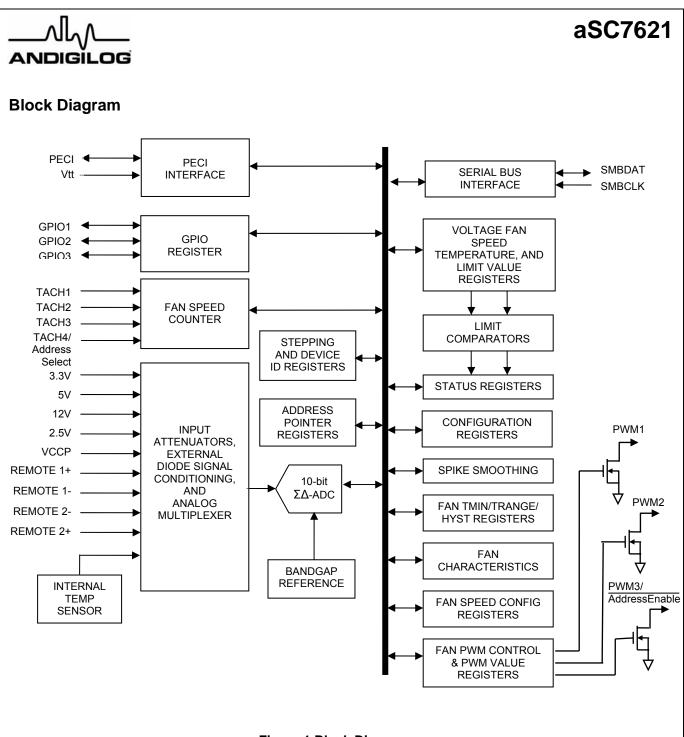

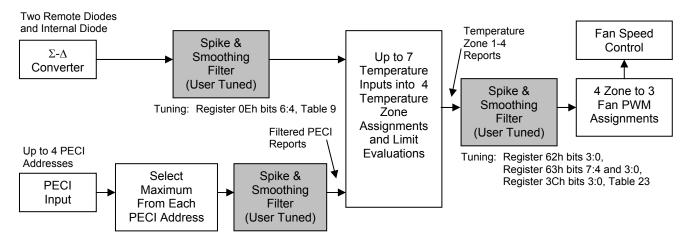

The aSC7621 has a two wire digital interface compatible with SMBus 2.0. Using a 10-bit  $\Sigma\Delta$ - ADC, the aSC7621 measures the temperature of two remote diode connected transistors as well as its own die. Support for Platform Environmental Control Interface (PECI) is included.

Using temperature information from these four zones, an automatic fan speed control algorithm is employed to minimize acoustic impact while achieving recommended CPU temperature under varying operational loads.

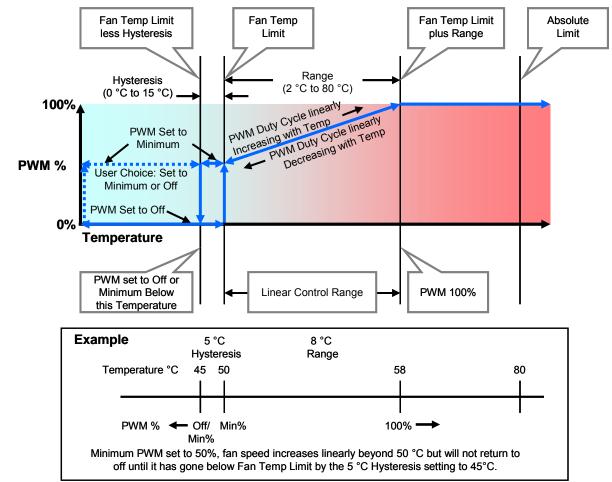

To set fan speed, the aSC7621 has three independent pulse width modulation (PWM) outputs that are controlled by one, or a combination of three, temperature zones. Both high- and low-frequency PWM ranges are supported. The aSC7621 also includes a digital filter that can be invoked to smooth temperature readings for better control of fan speed and minimum acoustic impact. The aSC7621 has tachometer inputs to measure fan speed on up to four fans. Limit and status registers for all measured values are included to alert the system host that any measurements are outside of programmed limits via status registers.

System voltages of VCCP, 2.5V, 3.3V, 5.0V, and 12V motherboard power are monitored efficiently with internal scaling resistors.

#### Features

Dreliminary Specification – Subject to change without notice

- Supports PECI interface and monitors internal and remote thermal diodes

- 2-wire, SMBus 2.0 compliant, serial interface

- 10-bit ΣΔ-ADC

- Monitors VCCP, 2.5V, 3.3V, 5.0V, and 12V motherboard/processor supplies

- Programmable autonomous fan control based on temperature readings

- Noise filtering of temperature reading for fan speed control

- 0.25°C digital temperature sensor resolution

- 3 PWM fan speed control outputs for 2-, 3- or 4wire fans and up to 4 fan tachometer inputs

- Enhanced measured temperature to Temperature Zone assignment.

- Provides high and low PWM frequency ranges

- 3 GPIO pins for custom use

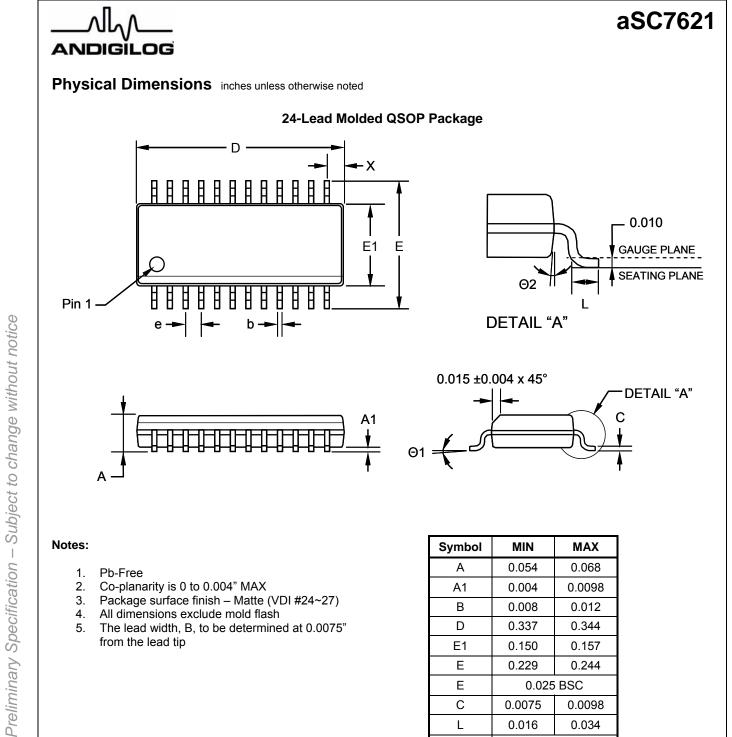

- 24-Lead QSOP package

#### **Measurement System**

#### Temperature:

- 0.25°C resolution, ±2°C accuracy on remote diode

- 0.25°C resolution, ±3°C accuracy on local sensor

- Temperature measurement range on remote sensor –55°C to +125°C using 2's complement coding.

#### Voltage:

• 10-bit Resolution, ±2% (TUE)

Fan Tachometer:

• 16-bit count of 90kHz clock periods

Limit alarms for all measured values

#### Applications

- Desktop Computers Motherboards and Graphics Cards

- Microprocessor based equipment (e.g. Basestations, Routers, ATMs, Point of Sales)

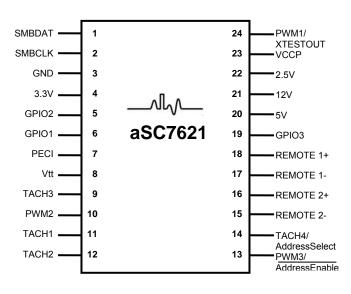

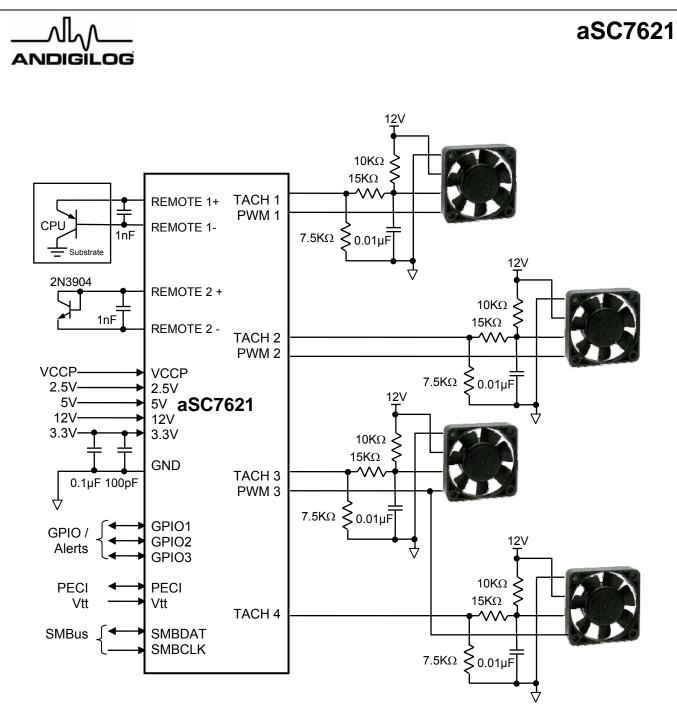

#### **Connection Diagram**

### **Ordering Information**

| Part Number | Package      | Temperature Range<br>and Operating Voltage | Marking         | How Supplied           |

|-------------|--------------|--------------------------------------------|-----------------|------------------------|

| aSC7621QS24 | 24-lead QSOP | 0°C to +120°C, 3.3V                        | aSC7621<br>Ayww | 2500 units Tape & Reel |

Ayww – Assembly site, year, workweek

Preliminary Specification – Subject to change without notice

#

#### **Pin Descriptions**

|                   | Symbol              | Pin | Туре                                       | Name and Function/Connection                                                                                                                                                                                                                                               |

|-------------------|---------------------|-----|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMBus             | SMBDAT              | 1   | Digital I/O<br>(Open-Drain)                | System Management Bus Data. Open-drain output. 5V tolerant, SMBus 2.0 compliant.                                                                                                                                                                                           |

| SME               | SMBCLK              | 2   | Digital Input                              | System Management Bus Clock. Tied to Open-drain output. 5V tolerant, SMBus 2.0 compliant.                                                                                                                                                                                  |

| PECI              | PECI                | 7   | Digital I/O                                | Platform Environmental Control Interface (PECI). PECI 1.0 compliant, CPU digital thermometer input                                                                                                                                                                         |

| _ ₽_              | Vtt                 | 8   | Analog Input                               | PECI reference voltage.                                                                                                                                                                                                                                                    |

| Power             | 3.3V                | 4   | POWER                                      | +3.3V pin. Can be powered by +3.3V Standby power if monitoring in low power states is required. This pin should be bypassed with a $0.1\mu$ F capacitor in parallel with 100pF. A bulk capacitance of approximately $10\mu$ F needs to be in near vicinity of the aSC7621. |

|                   | GND                 | 3   | GROUND                                     | Ground for all analog and digital circuitry.                                                                                                                                                                                                                               |

|                   | 5V                  | 20  | Analog Input                               | Analog Input for +5V monitoring.                                                                                                                                                                                                                                           |

| Voltage<br>Inputs | 12V                 | 21  | Analog Input                               | Analog Input for +12V monitoring.                                                                                                                                                                                                                                          |

| Voltage<br>Inputs | 2.5V                | 22  | Analog Input                               | Analog Input for +2.5V monitoring                                                                                                                                                                                                                                          |

|                   | VCCP                | 23  | Analog Input                               | Analog Input for VCCP (processor voltage) monitoring.                                                                                                                                                                                                                      |

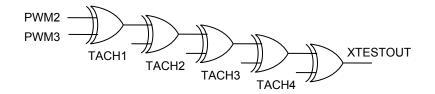

|                   | Remote 1+           | 18  | Remote Thermal<br>Diode Positive<br>Input  | Positive input (current source) from the first remote thermal diode Serves as the positive input into the A/D. Connected to THERMDA pin of Pentium processor.                                                                                                              |

| te                | Remote 1-           | 17  | Remote Thermal<br>Diode Negative<br>Input  | Negative input (current sink) from the first remote thermal diode Serves as the negative input into the A/D. Connected to THERMDC pin of Pentium processor.                                                                                                                |

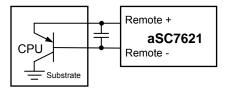

| Remote            | Remote 2+           | 16  | Remote Thermal<br>Diode Positive<br>Output | Positive input (current source) from the second remote<br>thermal diode Serves as the positive input into the A/D.<br>Connected to the base of a diode connected MMBT3904<br>NPN transistor.                                                                               |

|                   | Remote 2-           | 15  | Remote Thermal<br>Diode Negative<br>Input  | Negative input (current sink) from the second remote<br>thermal diode Serves as the negative input into the A/D.<br>Connected to the emitter of a diode connected MMBT3904<br>NPN transistor.                                                                              |

|                   | TACH1               | 11  | Digital Input                              | Input for monitoring tachometer output of fan 1.                                                                                                                                                                                                                           |

| eter              | TACH2               | 12  | Digital Input                              | Input for monitoring tachometer output of fan 2.                                                                                                                                                                                                                           |

| Tachome<br>Inputs | ТАСНЗ               | 9   | Digital Input                              | Input for monitoring tachometer output of fan 3. During power-up, if held low through a $10K\Omega$ resistor, SMBus address may be selected based on the state of TACH4 pin.                                                                                               |

| Fan               | TACH4/AddressSelect | 14  | Digital Input                              | Input for monitoring tachometer output of fan 4. If in Address Select Mode, determines the SMBus address of aSC7621.                                                                                                                                                       |

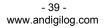

| 0                 | PWM1/XTESTOUT       | 24  | Digital Open-<br>Drain Output              | Fan speed control 1. When in XOR tree test mode, functions as XOR Tree output.                                                                                                                                                                                             |

| Fan Control       | PWM2                | 10  | Digital Open-<br>Drain Output              | Fan speed control 2.                                                                                                                                                                                                                                                       |

| Fan               | PWM3/Address Enable | 13  | Digital Open-<br>Drain Output              | Fan speed control 3. Pull to ground at power on to enable<br>Address Select Mode (Address Select pin controls SMBus<br>address of the device).                                                                                                                             |

Preliminary Specification – Subject to change without notice

|      | Symbol | Pin | Туре        | Name and Function/Connection                        |

|------|--------|-----|-------------|-----------------------------------------------------|

|      | GPIO1  | 6   | Digital I/O | Alert Out / Zone # THERM Out. Default is GPIO input |

| GPIO | GPIO2  | 5   | Digital I/O | Alert Out / Zone # THERM Out. Default is GPIO input |

|      | GPIO3  | 19  | Digital I/O | Alert Out / Zone # THERM Out. Default is GPIO input |

#### Absolute Maximum Ratings<sup>1</sup>

|         | Parameter                                             | Rating                             |  |  |

|---------|-------------------------------------------------------|------------------------------------|--|--|

| Supply  | Voltage, V <sub>DD</sub>                              | 3.6V                               |  |  |

|         | on Any Digital Input or<br>Pin other than PWM Outputs | -0.3V to V <sub>DD</sub> +0.3V     |  |  |

| Voltage | on PWM Outputs                                        | -0.3V to 5.5V                      |  |  |

| Voltage | on 12V Analog Input                                   | -0.5V to 16V                       |  |  |

| Voltage | on 5V Analog Input                                    | -0.5V to 6.5V                      |  |  |

| Voltage | on Remote 1 +, Remote 2 +                             | -0.5V to (V <sub>DD</sub> + 0.50V) |  |  |

| Voltage | on Other Analog Inputs                                | -0.5V to 6.0V                      |  |  |

| Current | on Remote 1 -, Remote 2 -                             | ±1mA                               |  |  |

| Input C | urrent on Any Pin <sup>2</sup>                        | ±5mA                               |  |  |

| Packag  | e Input Current <sup>2</sup>                          | ±20mA                              |  |  |

| Packag  | e Dissipation at T <sub>A</sub> = 25°C                | See (Note 3)                       |  |  |

| Storage | Temperature                                           | -65°C to +150°C                    |  |  |

|         | Human Body Model                                      | 4000 V                             |  |  |

| $ESD^4$ | Machine Model                                         | 250 V                              |  |  |

|         | Charged Device Model                                  | 2000V                              |  |  |

#### Notes:

- Absolute maximum ratings are limits beyond which operation may cause permanent damage to the device. These are stress ratings only; functional operation at or above these limits is not implied.

- 2. When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sub>DD</sub>), the current at that pin should be limited to 5mA. The 20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to four. Parasitic components and/or ESD protection circuitry are present on the aSC7621 pins. Care should be taken not to forward bias the parasitic diode present on pins D+ and D-. Doing so by more than 50mV may corrupt temperature measurements.

### **Operating Ratings**<sup>1</sup>

| Parameter                                                                                            | Rating                                 |

|------------------------------------------------------------------------------------------------------|----------------------------------------|

| aSC7621 Operating<br>Temperature Range, Ambient<br>Temperature, T <sub>MIN</sub> to T <sub>MAX</sub> | $0^{\circ}C \le T_A \le +120^{\circ}C$ |

| Remote Diode Temperature<br>Range                                                                    | -55°C ≤ T <sub>D</sub> ≤ +125°C        |

| Supply Voltage (3.3V nominal)                                                                        | +3.0V to +3.6V                         |

| V <sub>IN</sub> Voltage Range                                                                        |                                        |

| +12V V <sub>IN</sub>                                                                                 | -0.05V to 16V                          |

| +5V V <sub>IN</sub>                                                                                  | -0.05V to 6.5V                         |

| +3.3V V <sub>IN</sub>                                                                                | 3.0V to 4.4V                           |

| VCCP and All Other Inputs                                                                            | -0.05V to V <sub>DD</sub> + 0.05V      |

| Typical Supply Current                                                                               | 1.8mA                                  |

- 3. Thermal resistance junction-to-ambient when attached to a double-sided printed circuit board with 1oz. foil is 115°C/W

- 4. Human Body Model: 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Machine Model: 200pF capacitor discharged directly into each pin. Charged-Device Model is per JESD22-C101C.

### **DC Electrical Characteristics<sup>5</sup>**

The following specifications apply for  $V_{DD}$  = 3.0V to 3.6V, and all analog input source impedance  $R_s$  = 50 $\Omega$  unless otherwise specified in conditions. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> over T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. T<sub>A</sub> is the ambient temperature of the aSC7621; T<sub>J</sub> is the junction temperature of aSC7621; T<sub>D</sub> is the remote thermal diode junction temperature. Specifications subject to change without notice

| Parameter                                              |                   | Conditions                                                                                                                                          | Min | Тур        | Max | Units      |

|--------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|------------|

| POWER SUPPLY CHARACTERIS                               | STICS             |                                                                                                                                                     | •   |            |     |            |

| Supply Current                                         |                   | Converting, Interface and Fans<br>Inactive, Peak Current                                                                                            |     | 1.8        | 3.5 | mA(max)    |

| Supply Surrent                                         |                   | Converting, Interface and Fans inactive, Average Current                                                                                            |     | 0.5        |     | mA         |

| Power-On Reset Threshold<br>Voltage                    |                   |                                                                                                                                                     | 1.6 |            | 2.8 | V          |

| TEMPERATURE TO DIGITAL CO                              | NVERTE            | R CHARACTERISTICS                                                                                                                                   | I   |            |     |            |

| Resolution                                             |                   |                                                                                                                                                     |     | 0.25<br>10 |     | °C<br>Bits |

| Demote Concer Accurrent <sup>6</sup>                   |                   | $0^{\circ}C \le T_A \le +100^{\circ}C,$<br>$0^{\circ}C \le T_D \le +100^{\circ}C,$<br>$3V \le V_{DD} \le 3.6V$                                      |     |            | ±2  | °C         |

| Remote Sensor Accuracy <sup>6</sup>                    |                   | $\begin{array}{c} 0^{\circ}C \leq T_{A} \leq +120^{\circ}C, \\ -55^{\circ}C \leq T_{D} \leq +125^{\circ}C, \\ 3V \leq V_{DD} \leq 3.6V \end{array}$ |     |            | ±3  | °C         |

| Temperature Accuracy using Internal Diode <sup>7</sup> |                   | $0^{\circ}C \le T_A \le +120^{\circ}C, \ 3V \le V_{DD} \le 3.6V$                                                                                    |     | ±1         | ±3  | °C         |

|                                                        |                   | High Level                                                                                                                                          |     | 96         |     | µA(max)    |

| External Diode Current Source                          | I <sub>DS</sub>   | Low Level                                                                                                                                           |     | 6          |     | μA         |

| External Diode Current Ratio                           |                   |                                                                                                                                                     |     | 16         |     |            |

| ANALOG TO DIGITAL CONVERT                              | ER CHAF           | ACTERISTICS                                                                                                                                         | I   |            | I   |            |

| Total Unadjusted Error <sup>8</sup>                    | TUE               |                                                                                                                                                     |     |            | ±2  | %(max)     |

| Differential Non-linearity                             | DNL               |                                                                                                                                                     |     | 1          |     | LSB        |

| Power Supply Sensitivity                               |                   |                                                                                                                                                     |     | ±1         |     | %/V        |

| Total Monitoring Cycle Time9                           |                   | All Voltage and Temperature<br>readings                                                                                                             |     | 200        | 250 | ms (max)   |

| Input Resistance, all analog inputs                    |                   |                                                                                                                                                     | 140 | 210        | 400 | kΩ         |

| DIGITAL OUTPUT: PWM1, PWM2                             | 2, PWM3,          | XTESTOUT                                                                                                                                            | i   | -          | i   | i          |

| Logic Low Sink Current                                 | I <sub>OL</sub>   | V <sub>OL</sub> = 0.4V                                                                                                                              | 8   |            |     | mA (min)   |

| Logic Low Level                                        | V <sub>OL</sub>   | I <sub>OUT</sub> = +8mA                                                                                                                             |     |            | 0.4 | V (max)    |

| SMBUS OPEN-DRAIN OUTPUT:                               | SMBDAT            |                                                                                                                                                     | i   | -          | i   | i          |

| Logic Low Output Voltage                               | V <sub>OL</sub>   | I <sub>OUT</sub> = +4mA                                                                                                                             |     |            | 0.4 | V (max)    |

| High Level Output Current                              | I <sub>ОН</sub>   | V <sub>OUT</sub> = V+                                                                                                                               |     | 0.1        | 10  | µA(max)    |

| SMBUS INPUTS: SMBCLK, SMB                              | DAT               |                                                                                                                                                     | 1   |            |     |            |

| Logic Input High Voltage                               | VIH               |                                                                                                                                                     | 2.1 |            |     | V (min)    |

| Logic Input Low Voltage                                | VIL               |                                                                                                                                                     |     |            | 0.8 | V (max)    |

| Logic Input Hysteresis Voltage                         | V <sub>HYST</sub> |                                                                                                                                                     |     | 300        |     | mV         |

| DIGITAL INPUTS: ALL                                    |                   |                                                                                                                                                     |     |            |     |            |

| Logic Input High Voltage                               | VIH               |                                                                                                                                                     | 2.1 |            |     | V (min)    |

#

| Parameter                     |                 | Conditions            | Min | Тур    | Max | Units   |

|-------------------------------|-----------------|-----------------------|-----|--------|-----|---------|

| Logic Input Low Voltage       | VIL             |                       |     |        | 0.8 | V (max) |

| Logic Input Threshold Voltage | V <sub>TH</sub> |                       |     | 1.5    |     | V       |

| Logic High Input Current      | I <sub>IH</sub> | $V_{IN} = V+$         |     | 0.005  | 10  | µA(max) |

| Logic Low Input Current       | IIL             | V <sub>IN</sub> = GND |     | -0.005 | -10 | µA(max) |

| Digital Input Capacitance     | C <sub>IN</sub> |                       |     | 20     |     | pF      |

### **AC Electrical Characteristics**

The following specifications apply for  $V_{DD}$  = 3.0V to 3.6V unless otherwise specified in conditions. Boldface limits apply for  $T_A = T_J$  over  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Parameter                      | Conditions             | Min | Тур    | Max         | Units    |

|--------------------------------|------------------------|-----|--------|-------------|----------|

| TACHOMETER                     |                        | ·   |        |             | ·        |

| Fan Full-Scale Count           |                        |     |        | 65535       | (max)    |

| Fan Counter Clock Frequency    |                        |     | 90     |             | kHz      |

| Fan Count Conversion Time      |                        | 0.3 |        | 1.0         | sec(max) |

| FAN PWM OUTPUT                 |                        |     |        | -           | -        |

|                                |                        |     | 10     |             | Hz       |

| Frequency Range                | Low-Frequency Range    |     | 94     |             | Hz       |

|                                | Llink Franciscov Dance |     | 23     |             | kHz      |

|                                | High-Frequency Range   |     | 30     |             | kHz      |

| Duty-Cycle Range               |                        |     |        | 0 to<br>100 | %(max)   |

| Duty-Cycle Resolution (8-bits) |                        |     | 0.3906 |             | %/count  |

| Chin Lin Time Interval Dense   |                        |     | 0      |             | ms       |

| Spin-Up Time Interval Range    |                        |     | 4000   |             | ms       |

### Logic Electrical Characteristics

(T<sub>A</sub> = 25 °C,  $V_{DD}$  = 3.3V unless otherwise noted)

| Parameter                 | Symbol          | Conditions                                                  | Min | Тур | Max  | Units |

|---------------------------|-----------------|-------------------------------------------------------------|-----|-----|------|-------|

| Input Voltage Logic High  | V <sub>IH</sub> | $3V \le V_{DD} \le 3.6V$                                    | 2.1 |     |      | V     |

| Input Voltage Logic Low   | V <sub>IL</sub> | $3V \le V_{DD} \le 3.6V$                                    |     |     | 0.8  | V     |

| Input Leakage Current     | l <sub>iN</sub> | V <sub>IN</sub> = 0V or 5.5V,<br>0°C≤T <sub>A</sub> ≤+125°C |     |     | ±1.0 | μA    |

| SMBus Output Sink Current | I <sub>OL</sub> | T <sub>A</sub> = 25 °C, V <sub>OL</sub> = 0.6V              | 6   |     |      | mA    |

| SMBus Logic Input Current | lih, li∟        |                                                             | -1  |     | +1   | μA    |

| Output Leakage Current    | I <sub>OH</sub> | V <sub>OH</sub> = V <sub>DD</sub> = 5.5V                    |     | 0.1 | 1    | μA    |

| Output Transition Time    | t <sub>F</sub>  | C <sub>L</sub> = 400pF, I <sub>OL</sub> = -3mA              |     |     | 250  | ns    |

| Input Capacitance         | C <sub>IN</sub> | All Digital Inputs                                          |     |     | 5    | pF    |

Preliminary Specification – Subject to change without notice

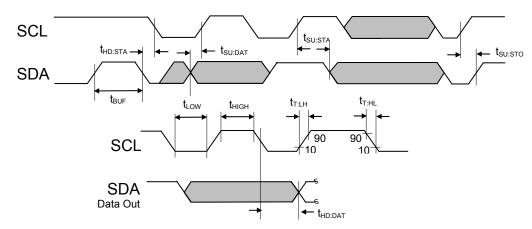

#### **Serial Port Timing**

ANDIGILOG

(T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3V unless otherwise noted, Guaranteed by design, not production tested)

| Parameter                                                                | Symbol                  | Min | Тур | Max | Units |

|--------------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| SCL Operating Frequency                                                  | f <sub>SCL</sub>        |     |     | 400 | kHz   |

| SCL Clock Transition Time                                                | $t_{T:LH}$ , $t_{T:HL}$ |     |     | 300 | ns    |

| SCL Clock Low Period                                                     | t <sub>LOW</sub>        | 1.3 |     |     | μS    |

| SCL Clock High Period                                                    | t <sub>ніGH</sub>       | 0.6 |     | 50  | μS    |

| Bus free time between a Stop and a new Start Condition                   | t <sub>BUF</sub>        | 1.3 |     |     | μS    |

| Data in Set-Up to SCL High                                               | t <sub>SU:DAT</sub>     | 100 |     |     | ns    |

| Data Out Stable after SCL Low                                            | t <sub>HD:DAT</sub>     | 300 |     |     | ns    |

| SCL Low Set-up to SDA Low (Repeated Start Condition)                     | t <sub>su:sta</sub>     | 600 |     |     | ns    |

| SCL High Hold after SDA Low (Start Condition)                            | t <sub>HD:STA</sub>     | 600 |     |     | ns    |

| SDA High after SCL High (Stop Condition)                                 | tsu:sto                 | 600 |     |     | ns    |

| Time in which aSC7621 must be operational after a power-on reset         | t <sub>POR</sub>        |     |     | 500 | ms    |

| SMBus Time-out before device communication interface reset <sup>10</sup> | t <sub>TIMEOUT</sub>    | 25  |     | 35  | ms    |

#### Notes (cont'd):

- 5. These specifications are guaranteed only for the test conditions listed.

- 6. The accuracy of the aSC7621 is guaranteed when using the thermal diode of Intel Pentium 4, 65nm processors or any thermal diode with a non-ideality of 1.009 and series resistance of 4.52Ω. When using a 2N3904 type transistor or an CPU with a different non-ideality the error band will be typically shifted depending on transistor diode or CPU characteristics. See applications section for details.

- 7. Accuracy (expressed in °C) = Difference between the aSC7621 reported output temperature and the temperature being measured. Local temperature accuracy does not include the effects of self-heating. The rise in temperature due to self-heating is the product of the internal power dissipation of the aSC7621 and the thermal resistance. See (Note 3) for the thermal resistance to be used in the self-heating calculation.

- 8. TUE, total unadjusted error, includes ADC gain, offset, linearity and reference errors. TUE is defined as the "actual  $V_{in}$ " to achieve a given code transition minus the "theoretical  $V_{in}$ " for the same code. Therefore, a positive error indicates that the input voltage is greater than the theoretical input voltage for a given code. If the theoretical input voltage was applied to an aSC7621 that has positive error, the aSC7621's reading would be less than the theoretical.

- 9. This specification is provided only to indicate how often temperature and voltage data is updated. The aSC7621 can be read at any time without regard to conversion state (and will yield last conversion result).

- 10. Holding the SMBCLK line low for a time interval greater than t<sub>TIMEOUT</sub> will reset the aSC7621's SMBus state machine, therefore setting the SMBDAT pin to a high impedance state.

© Andigilog, Inc. 2006

#### **Control Communication**

#### SMBus

The aSC7621 is compatible with devices that are compliant to the SMBus 2.0 specifications. More information on this bus can be found at <u>http://www.smbus.org/</u>. Compatibility of SMBus2.0 to other buses is discussed in the SMBus 2.0 specification.

#### **General Operation**

Writing to and reading from the aSC7621 registers is accomplished via the SMBus-compatible two-wire serial interface. SMBus protocol requires that one device on the bus initiate and control all read and write operations. This device is called the "master" device. The master device also generates the SCL signal that is the clock signal for all other devices on the bus. All other devices on the bus are called "slave" devices. The aSC7621 is a slave device. Both the master and slave devices can send and receive data on the bus.

During SMBus operations, one data bit is transmitted per clock cycle. All SMBus operations follow a repeating nine clock-cycle pattern that consists of eight bits (one byte) of transmitted data followed by an acknowledge (ACK) or not acknowledge (NACK) from the receiving device. Note that there are no unused clock cycles during any operation therefore there must be no breaks in the stream of data and ACKs / NACKs during data transfers.

For most operations, SMBus protocol requires the SDA line to remain stable (unmoving) whenever SCL is high — i.e. any transitions on the SDA line can only occur when SCL is low. The exceptions to this rule are when the master device issues a start or stop condition. Note that the slave device cannot issue a start or stop condition.

#### **SMBus Definitions**

Dreliminary Specification – Subject to change without notice

The following are definitions for some general SMBus terms:

**Start Condition:** This condition occurs when the SDA line transitions from high to low while SCL is high. The master device uses this condition to indicate that a data transfer is about to begin.

**Stop Condition:** This condition occurs when the SDA line transitions from low to high while SCL is high. The master device uses this condition to signal the end of a data transfer.

Acknowledge and Not Acknowledge: When data are transferred to the slave device it sends an "acknowledge" (ACK) after receiving each byte. The receiving device sends an ACK by pulling SDA low for one clock. Following the last byte, a master device sends a "not acknowledge" (NACK) followed by a stop condition. A NACK is indicated by forcing SDA high during the clock after the last byte.

#### **Slave Address**

aSC7621 is designed to be used primarily in desktop systems that require only one monitoring device. If only one aSC7621 is used on the motherboard, the designer should

be sure that the AddressEnable /PWM3 pin is High during the first SMBus communication addressing the aSC7621.

AddressEnable /PWM3 is an open drain I/O pin that at

power-on defaults to the input state of AddressEnable . A maximum of 10k pull-up resistance on

AddressEnable /PWM3 is required to assure that the SMBus address of the device will be locked at 010 1110b, which is the default address of the aSC7621.

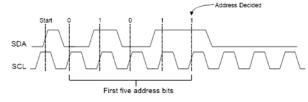

During the first SMBus communication TACH4 and PWM3 can be used to change the SMBus address of the aSC7621 to 0101101b or 0101100b. aSC7621 address selection procedure:

A  $10k\Omega$  pull-down resistor to ground on the

AddressEnable /PWM3 pin is required. Upon power up, the aSC7621 will be placed into

AddressEnable mode and assign itself on SMBus address according to the state of the Address Select input. The aSC7621 will latch the address during the first valid SMBus transaction in which the first five bits of the targeted address match those of the aSC7621 address, 0 1011b. This feature eliminates the possibility of a glitch on the SMBus interfering with

address selection. When the AddressEnable /PWM3 pin is not used to change the SMBus address of the aSC7621, it will remain in a high state until the first communication with the aSC7621. After the first SMBus transaction is completed PWM3 and TACH4 will return to normal operation.

| Address | Address<br>Select | Board Imple-<br>mentation                                                                                | SMB<br>Addre |     |

|---------|-------------------|----------------------------------------------------------------------------------------------------------|--------------|-----|

| Enable  | Select            | mentation                                                                                                | Binary       | Hex |

| 0       | 0                 | Both pins pulled<br>to ground<br>through a 10 kΩ<br>resistor                                             | 010<br>1100  | 2Ch |

| 0       | 1                 | Address Select<br>pulled to 3.3V<br>and<br>AddressEnable<br>pulled to GND<br>through a 10 kΩ<br>resistor | 010<br>1101  | 2Dh |

| 1       | Х                 | AddressEnable<br>pulled to 3.3V<br>through a 10 kΩ<br>resistor                                           | 010<br>1110  | 2Eh |

In this way, up to three aSC7621 devices can exist on a SMBus at any time. Multiple aSC7621 devices can be used to monitor additional processors in the temperature zones. When using the non-default addresses, additional circuitry will be required if Tach4 and PWM3 require to function correctly. Such circuitry could consist of GPIO pins from a micro-controller. During the first communication the micro-controller would drive the

AddressEnable and Address Select pins to the proper state for the required address. After the first SMBus communication the micro-controller would drive its pins into Tri-State allowing TACH4 and PWM3 to operate correctly.

#### Writing to and Reading from the aSC7621

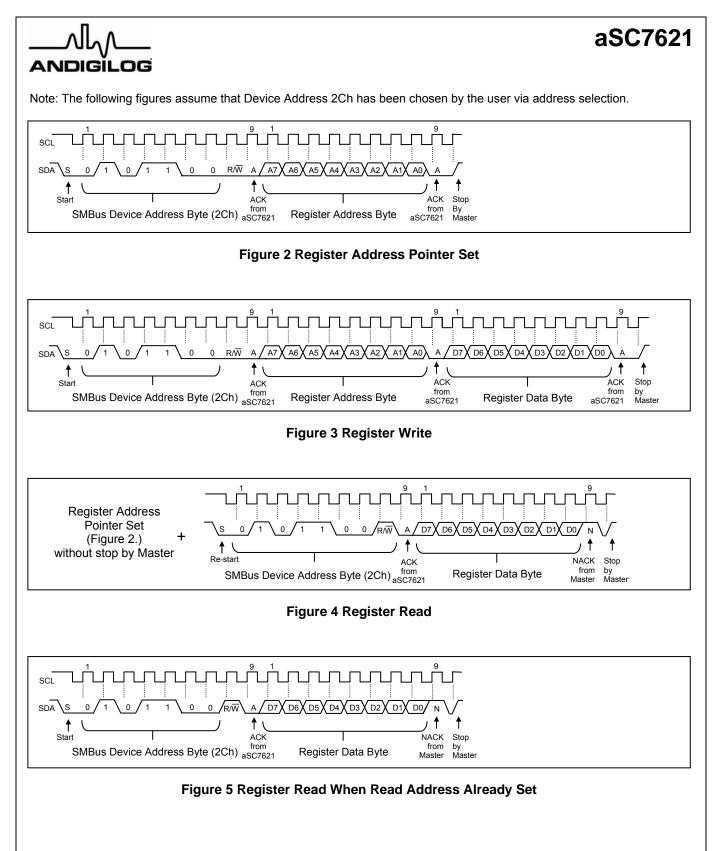

All read and write operations must begin with a start condition generated by the master device. After the start condition, the master device must immediately send a slave address (7-bits) followed by a  $R/\overline{W}$  bit. If the slave address matches the address of the aSC7621, it sends an ACK by pulling the SDA line low for one clock. Read or write operations may contain one- or two-bytes. See Figures 2 through 6 for timing diagrams for all aSC7621 operations.

#### Setting the Register Address Pointer

For all operations, the address pointer stored in the address pointer register must be pointing to the register address that is going to be written to or read from. This register's content is automatically set to the value of the first base following the D(M) bit bases got to 0

first byte following the R/W bit being set to 0.

After the aSC7621 sends an ACK in response to receiving the address and  $R/\overline{W}$  bit, the master device must transmit an appropriate 8-bit address pointer value as explained in the Registers section of this data sheet. The aSC7621 will send an ACK after receiving the new pointer data.

The register address pointer set operation is illustrated in Figure 2. If the address pointer is not a valid address the aSC7621 will internally terminate the operation. Also recall that the address register retains the current address pointer value between operations. Therefore, once a register is being pointed to, subsequent read operations do not require another Address Pointer set cycle.

#### Writing to Registers

All writes must start with a pointer set as described previously, even if the pointer is already pointing to the desired register. The sequence is described in Figure 2.

Immediately following the pointer set, the master must begin transmitting the data to be written. After transmitting each byte of data, the master must release the SDA line for one clock to allow the aSC7621 to acknowledge receiving the byte. The write operation should be terminated by a stop condition from the master.

#### **Reading from Registers**

To read from a register other than the one currently being pointed to by the address pointer register, a pointer set sequence to the desired register must be done as described previously. Immediately following the pointer set, the master must perform a repeat start condition that indicates to the aSC7621 that a read is about to occur. It is important to note that if the repeat start condition does not occur, the aSC7621 will assume that a write is taking place, and the selected register will be overwritten by the upcoming data on the data bus. The read sequence is described in Figure 4. After the start condition, the master must again send the device address and read/write bit.

This time the R/W bit must be set to 1 to indicate a read. The rest of the read cycle is the same as described in the previous paragraph for reading from a preset pointer location.

If the pointer is already pointing to the desired register, the

master can read from that register by setting the  $R/\overline{W}$  bit (following the slave address) to a 1. After sending an ACK, the aSC7621 will begin transmitting data during the following clock cycle. After receiving the 8 data bits, the master device should respond with a NACK followed by a stop condition.

If the master is reset while the aSC7621 is in the process of being read, the master should perform an SMBus reset. This is done by holding the clock low for more than 35ms, allowing all SMBus devices to be reset. This follows the SMBus 2.0 specification of 25-35ms.

When the aSC7621 detects an SMBus reset, it will prepare to accept a new start sequence and resume communication from a known state.

#

#### PECI

The aSC7621 is compatible with devices that are compliant with Intel's PECI 1.0 specifications. More information on this interface may be found in their PECI interface specifications.

Temperatures sent over the PECI interface from the CPU are in Celsius degrees relative to the Thermal Control Circuit (TCC) temperature stored internally in the CPU and accessed only through BIOS. This is the temperature limit where internal measures are taken to reduce power dissipation. Fan speed control settings sent by the BIOS over the SMBus to registers in the aSC7621 are made using this relative temperature rather than the absolute readings of remote or on-chip diodes.

As many as four CPU clients on the PECI bus are addressed in the range of 0x30 to 0x33. Currently, each address is a single-packaged device that may have up to two domains or CPU-measured digital temperatures.

#### **General Operation**

Preliminary Specification – Subject to change without notice

The PECI host in aSC7621 performs the following functions:

- Responds to SMBus configuration identifying the presence of PECI clients and the Thermal Zone associated with each client.

- Reads the PECI temperature of the domain(s) of each client processor addressed.

- Stores the highest result from each PECI address into Temperature Zone register associated to the measurement received from the client. (each address may be associated with any one Temperature Zone.)

- Flags an error if no valid PECI temperature can be read.

- Continuously monitors the state of the PECI interface for fault conditions.

#### **PECI Temperature Format and Range**

The PECI temperatures read from the processor will be in the range  $0^{\circ}$ C to  $-127^{\circ}$ C where  $0^{\circ}$ C is the hottest temperature and has the following format:

| Temperature | 2's Complement<br>Representation |

|-------------|----------------------------------|

| 0° C        | 0000 0000 00.00 0000             |

| -1° C       | 1111 1111 11.00 0000             |

| -5° C       | 1111 1110 11.00 0000             |

| -32° C      | 1111 1000 00.00 0000             |

| -127° C     | 1111 0000 01.00 0000             |

#### **Table 1 Raw PECI Temperature Format**

These readings are not accessible to the user but are filtered, re-formatted and assigned to a Temperature Zone. Filtered PECI Temperature readings are accessible by the user before they are assigned to a Temperature Zone by reading registers F6h through FDh. These readings follow the format described in Table 2. The PECI temperatures assigned to a Temperature Zone are reported over SMBus interface in Temperature Zone registers also will be in the range 0°C to -127°C. The format reported through Temperature Zone registers is re-aligned to agree with diode measurements. It is stored in two register locations in the following format with integer high byte and fractional low byte to be consistent with all other temperature reports:

| Temperature | 2's Complement<br>Representation |            |  |  |  |  |  |  |

|-------------|----------------------------------|------------|--|--|--|--|--|--|

|             | High Byte                        | Low Byte   |  |  |  |  |  |  |

| 0° C        | 0000 0000                        | .0000 0000 |  |  |  |  |  |  |

| -1° C       | 1111 1111                        | .0000 0000 |  |  |  |  |  |  |

| -5° C       | 1111 1011                        | .0000 0000 |  |  |  |  |  |  |

| -32° C      | 1110 0000                        | .0000 0000 |  |  |  |  |  |  |

| -127° C     | 1000 0001                        | .0000 0000 |  |  |  |  |  |  |

#### **Table 2 PECI Temperature Report Format**

#### PECI Errors

A specific set of temperature reading value encodings, well outside the operational range of 0°C to -127°C, are reserved to signal temperature sensor faults on the CPU to aSC7621 interface. These encodings are in the PECI temperature format as delivered by the CPU and are converted to the appropriate Interrupt Status Register 3 error bits described in the Interrupt Status register section below.

# aSC7621

**Register Set**

| Register<br>Address | R/W   | Register<br>Name                  | Bit 7<br>(MSB)           | Bit 6             | Bit 5            | Bit 4            | Bit 3            | Bit 2            | Bit 1              | Bit 0<br>(LSB)        | De-<br>fault<br>Value<br>(hex) | Lock     |

|---------------------|-------|-----------------------------------|--------------------------|-------------------|------------------|------------------|------------------|------------------|--------------------|-----------------------|--------------------------------|----------|

| 00h                 | R     | Fan Zone Status                   | Fan 3.                   | Zone #<br>0       | Fan 2<br>1       | Zone #<br>0      | Fan 1            | Zone #<br>0      | RES                | RES                   | N/A                            |          |

| 02h                 | R/W   | Zone 1 & 2<br>Assignment          | RES                      | Z                 | one 1 Sour       | ce               | RES              | Z                | Zone 2 Sourc       |                       | 00                             | x        |

|                     |       |                                   |                          | 2                 | 1                | 0                |                  | 2                |                    | 0                     |                                |          |

| 03h                 | R/W   | Zone 3 & 4<br>Assignment          | RES                      | 2                 | one 3 Sour<br>1  | ce<br>0          | RES              | 2                | Cone 4 Sourc       | e<br>0                | 00                             | х        |

| 04h                 | R/W   | Tach 1<br>Configuration           | 3-Wire<br>Enable1        | 3-Wire<br>Enable0 | Meas<br>Blank1   | Meas<br>Blank 0  | Meas<br>Dwell 1  | Meas<br>Dwell 0  | Meas<br>Duration 1 | Meas<br>Duration<br>0 | 36                             | x        |

| 05h                 | R/W   | Tach 2<br>Configuration           | 3-Wire<br>Enable1        | 3-Wire<br>Enable0 | Meas<br>Blank1   | Meas<br>Blank 0  | Meas<br>Dwell 1  | Meas<br>Dwell 0  | Meas<br>Duration 1 | Meas<br>Duration<br>0 | 36                             | x        |

| 06h                 | R/W   | Tach 3<br>Configuration           | 3-Wire<br>Enable1        | 3-Wire<br>Enable0 | Meas<br>Blank1   | Meas<br>Blank 0  | Meas<br>Dwell 1  | Meas<br>Dwell 0  | Meas<br>Duration 1 | Meas<br>Duration<br>0 | 36                             | x        |

| 07h                 | R/W   | Tach 4<br>Configuration           | 3-Wire<br>Enable1        | 3-Wire<br>Enable0 | Meas<br>Blank1   | Meas<br>Blank 0  | Meas<br>Dwell 1  | Meas<br>Dwell 0  | Meas<br>Duration 1 | Meas<br>Duration<br>0 | 36                             | х        |

| 0Eh                 | R/W   | PECI Extended<br>Configuration    | Four<br>Domain<br>Enable | Diode<br>Filter2  | Diode<br>Filter1 | Diode<br>Filter0 | Proc 3<br>Enable | Proc 2<br>Enable | Proc 1<br>Enable   | Proc 0<br>Enable      | 21                             | x        |

| 10h                 | R     | Zone 1 Temper-<br>ature (LS Byte) | 1                        | 0                 | х                | х                | х                | х                | х                  | х                     | N/A                            |          |

| 11h                 | R     | 3.3V (LS Byte)                    | 1                        | 0                 | Х                | Х                | Х                | Х                | Х                  | Х                     | N/A                            |          |

| 12h                 | R     | 5V (LS Byte)                      | 1                        | 0                 | Х                | Х                | Х                | Х                | Х                  | Х                     | N/A                            |          |

| 13h                 | R     | 2.5V (LS Byte)                    | 1                        | 0                 | х                | х                | Х                | Х                | Х                  | Х                     | N/A                            |          |

| 14h                 | R     | 12V (LS Byte)                     | 1                        | 0                 | х                | х                | Х                | Х                | Х                  | Х                     | N/A                            |          |

| 15h                 | R     | Zone 2 Temper-<br>ature (LS Byte) | 1                        | 0                 | х                | х                | х                | х                | х                  | х                     | N/A                            |          |

| 16h                 | R     | Zone 3 Temper-<br>ature (LS Byte) | 1                        | 0                 | х                | x                | х                | х                | x                  | х                     | N/A                            |          |

| 17h                 | R     | Zone 4 Temper-<br>ature (LS Byte) | 1                        | 0                 | х                | х                | х                | х                | х                  | х                     | N/A                            |          |

| 18h                 | R     | Vccp (LS Byte)                    | 1                        | 0                 | Х                | Х                | Х                | Х                | Х                  | Х                     | N/A                            |          |

| 19h                 | R/W   | GPIO 1                            | RES                      | RES               | Alert As         | signment         | GPIO 1           | G                | PIO 1 Functi       | on                    | 00                             | х        |

| 1311                | 17.44 | Configuration                     | NL0                      | NL0               | 1                | 0                | bit              | 2                | 1                  | 0                     | 00                             | ^        |

| 1Ah                 | R/W   | GPIO 2 & 3                        | GPIO 2                   | GF                | IO 2 Func        | tion             | GPIO 3           | G                | PIO 3 Functi       | on                    | 00                             | х        |

|                     |       | Configuration                     | bit                      | 2                 | 1                | 0                | bit              | 2                | 1                  | 0                     |                                |          |

| 1Ch                 | R/W   | Remote 1 offset                   | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | 00                             | Х        |

| 1Dh                 | R/W   | Remote 2 offset                   | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | 00                             | Х        |

| 20h                 | R     | 2.5V (MS Byte)                    | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | N/A                            |          |

| 21h                 | R     | Vccp (MS Byte)                    | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | N/A                            |          |

| 22h                 | R     | 3.3 V (MS Byte)                   | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | N/A                            |          |

| 23h                 | R     | 5V (MS Byte)                      | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | N/A                            |          |

| 24h                 | R     | 12V (MS Byte)                     | 7                        | 6                 | 5                | 4                | 3                | 2                | 1                  | 0                     | N/A                            |          |

| 25h                 | R     | Zone 1 Temper-<br>ature (MS Byte) | 9                        | 8                 | 7                | 6                | 5                | 4                | 3                  | 2                     | N/A                            | <b> </b> |

| 26h                 | R     | Zone 2 Temper-<br>ature (MS Byte) | 9                        | 8                 | 7                | 6                | 5                | 4                | 3                  | 2                     | N/A                            |          |

| 27h                 | R     | Zone 3 Temper-<br>ature (MS Byte) | 9                        | 8                 | 7                | 6                | 5                | 4                | 3                  | 2                     | N/A                            |          |

| Register<br>Address | R/W | Register<br>Name                    | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | De-<br>fault<br>Value<br>(hex) | Lock           |

|---------------------|-----|-------------------------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|--------------------------------|----------------|

| 28h                 | R   | Tach 1 LS Byte                      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 29h                 | R   | Tach 1 MS Byte                      | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |                |

| 2Ah                 | R   | Tach 2 LS Byte                      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 2Bh                 | R   | Tach 2 MS Byte                      | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |                |

| 2Ch                 | R   | Tach 3 LS Byte                      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 2Dh                 | R   | Tach 3 MS Byte                      | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |                |

| 2Eh                 | R   | Tach 4 LS Byte                      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 2Fh                 | R   | Tach 4 MS Byte                      | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |                |

| 30h                 | R/W | Fan 1 Current<br>PWM Duty           | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 31h                 | R/W | Fan 2 Current<br>PWM Duty           | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 32h                 | R/W | Fan 3 Current<br>PWM Duty           | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |                |

| 33h                 | R   | Zone 4<br>Temperature<br>(MS Byte)  | 9              | 8     | 7     | 6     | 5     | 4     | 3     | 2              | N/A                            |                |

| 34h                 | R/W | Zone 4 Low<br>Temp                  | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 81h                            |                |

| 35h                 | R/W | Zone 4 High<br>Temp                 | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 00h                            |                |

| 36h                 | R/W | PECI<br>Configuration               | RES            | RES   | RES   | LEG   | DOM   | AVG2  | AVG1  | AVG0           | 00h                            | х              |

| 38h                 | R/W | Fan 1 Max Duty<br>Cycle             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             | х              |

| 39h                 | R/W | Fan 2 Max Duty<br>Cycle             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             | х              |

| 3Ah                 | R/W | Fan 3 Max Duty<br>Cycle             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FF                             | х              |

| 3Bh                 | R/W | Zone 4 Fan<br>Temp Limit            | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | E0h                            | х              |

| 3Ch                 | R/W | Zone 4 Range,<br>Spike<br>Smoothing | RAN3           | RAN2  | RAN1  | RAN0  | ZN4E  | ZN4-2 | ZN4-1 | ZN4-0          | C3h                            | x              |

| 3Dh                 | R/W | Zone 4 Absolute<br>Temp Limit       | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 00h                            | х              |

| 3Eh                 | R   | Company ID                          | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 61                             |                |

| 3Fh                 | R   | Version/<br>Stepping                | VER3           | VER2  | VER1  | VER0  | 4WIRE | PECI  | STP1  | STP0           | 6C                             |                |

| 40h                 | R/W | Ready/Lock/<br>Start/Override       | RES            | RES   | SAFE  | PECI  | OVRID | READY | LOCK  | START          | 00                             | X <sup>2</sup> |

| 41h                 | R   | Interrupt Status<br>Register 1      | ERR            | ZN3   | ZN2   | ZN1   | 5V    | 3.3V  | VCCP  | 2.5V           | 00                             |                |

| 42h                 | R   | Interrupt Status<br>Register 2      | ERR2           | ERR1  | FAN4  | FAN3  | FAN2  | FAN1  | ERR   | 12V            | 00                             |                |

| 43h                 | R   | Interrupt Status<br>Register 3      | ERR            | RES   | RES   | RES   | ALOVR | СОММ  | DATA  | ZN4            | 00h                            |                |

aSC7621

| Register<br>Address | R/W | Register<br>Name                    | Bit 7<br>(MSB) | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | De-<br>fault<br>Value<br>(hex) | Lock |

|---------------------|-----|-------------------------------------|----------------|-----------------|-------|-------|-------|-------|-------|----------------|--------------------------------|------|

| 44h                 | R/W | 2.5V Low Limit                      | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 00                             |      |

| 45h                 | R/W | 2.5V High Limit                     | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 46h                 | R/W | Vccp Low Limit                      | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 00                             |      |

| 47h                 | R/W | Vccp High Limit                     | 7              | 7 6 5 4 3 2 1 0 |       | FF    |       |       |       |                |                                |      |

| 48h                 | R/W | 3.3V Low Limit                      | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 00                             |      |

| 49h                 | R/W | 3.3V High Limit                     | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 4Ah                 | R/W | 5V Low Limit                        | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 00                             |      |

| 4Bh                 | R/W | 5V High Limit                       | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 4Ch                 | R/W | 12V Low Limit                       | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 00                             |      |

| 4Dh                 | R/W | 12V High Limit                      | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 4Eh                 | R/W | Zone 1 Low<br>Temperature           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 81                             |      |

| 4Fh                 | R/W | Zone 1 High<br>Temperature          | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 7F                             |      |

| 50h                 | R/W | Zone 2 Low<br>Temperature           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 81                             |      |

| 51h                 | R/W | Zone 2 High<br>Temperature          | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 7F                             |      |

| 52h                 | R/W | Zone 3 Low<br>Temperature           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 81                             |      |

| 53h                 | R/W | Zone 3 High<br>Temperature          | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | 7F                             |      |

| 54h                 | R/W | Tach 1 Minimum<br>LS Byte           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 55h                 | R/W | Tach 1 Minimum<br>MS Byte           | 15             | 14              | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |      |

| 56h                 | R/W | Tach 2 Minimum<br>LS Byte           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 57h                 | R/W | Tach 2 Minimum<br>MS Byte           | 15             | 14              | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |      |

| 58h                 | R/W | Tach 3 Minimum<br>LS Byte           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 59h                 | R/W | Tach 3 Minimum<br>MS Byte           | 15             | 14              | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |      |

| 5Ah                 | R/W | Tach 4 Minimum<br>LS Byte           | 7              | 6               | 5     | 4     | 3     | 2     | 1     | 0              | FF                             |      |

| 5Bh                 | R/W | Tach 4 Minimum<br>MS Byte           | 15             | 14              | 13    | 12    | 11    | 10    | 9     | 8              | FF                             |      |

| 5Ch                 | R/W | Fan 1<br>Configuration              | ZON2           | ZON1            | ZON0  | INV   | ALT   | SPIN2 | SPIN1 | SPIN0          | 62                             | х    |

| 5Dh                 | R/W | Fan 2<br>Configuration              | ZON2           | ZON1            | ZON0  | INV   | ALT   | SPIN2 | SPIN1 | SPIN0          | 62                             | х    |

| 5Eh                 | R/W | Fan 3<br>Configuration              | ZON2           | ZON1            | ZON0  | INV   | ALT   | SPIN2 | SPIN1 | SPIN0          | 62                             | х    |

| 5Fh                 | R/W | Zone 1 Range/<br>Fan 1<br>Frequency | RAN3           | RAN2            | RAN1  | RAN0  | HLFRQ | FRQ2  | FRQ1  | FRQ0           | C3                             | x    |

aSC7621

| aSC7621 |  |

|---------|--|

|---------|--|

Preliminary Specification – Subject to change without notice

| Register<br>Address | R/W | Register<br>Name                      | Bit 7<br>(MSB)   | Bit 6              | Bit 5            | Bit 4            | Bit 3 | Bit 2  | Bit 1  | Bit 0<br>(LSB) | De-<br>fault<br>Value<br>(hex) | Lock |

|---------------------|-----|---------------------------------------|------------------|--------------------|------------------|------------------|-------|--------|--------|----------------|--------------------------------|------|

| 60h                 | R/W | Zone 2 Range/<br>Fan 2<br>Frequency   | RAN3             | RAN2               | RAN1             | RAN0             | HLFRQ | FRQ2   | FRQ1   | FRQ0           | C3                             | x    |

| 61h                 | R/W | Zone 3 Range/<br>Fan 3<br>Frequency   | RAN3             | RAN2               | RAN1             | RAN0             | HLFRQ | FRQ2   | FRQ1   | FRQ0           | C3                             | x    |

| 62h                 | R/W | Min/Off, Zone 1<br>Spike<br>Smoothing | OFF3             | OFF2               | OFF1             | RES              | ZN1E  | ZN1-2  | ZN1-1  | ZN1-0          | 00                             | x    |

| 63h                 | R/W | Zone 2 / Zone 3<br>Spike<br>Smoothing | ZN2E             | ZN2-2              | ZN2-1            | ZN2-0            | ZN3E  | ZN3-2  | ZN3-1  | ZN3-0          | 00                             | x    |

| 64h                 | R/W | Fan 1 PWM<br>Minimum                  | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 80                             | х    |

| 65h                 | R/W | Fan 2 PWM<br>Minimum                  | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 80                             | х    |

| 66h                 | R/W | Fan 3 PWM<br>Minimum                  | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 80                             | х    |

| 67h                 | R/W | Zone 1 Fan<br>Temp Limit              | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 5A                             | х    |

| 68h                 | R/W | Zone 2 Fan<br>Temp Limit              | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 5A                             | х    |

| 69h                 | R/W | Zone 3 Fan<br>Temp Limit              | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 5A                             | х    |

| 6Ah                 | R/W | Zone 1 Temp<br>Absolute Limit         | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 64                             | х    |

| 6Bh                 | R/W | Zone 2 Temp<br>Absolute Limit         | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 64                             | х    |

| 6Ch                 | R/W | Zone 3 Temp<br>Absolute Limit         | 7                | 6                  | 5                | 4                | 3     | 2      | 1      | 0              | 64                             | х    |

| 6Dh                 | R/W | Zone 1, Zone 2<br>Hysteresis          | H1-3             | H1-2               | H1-1             | H1-0             | H2-3  | H2-2   | H2-1   | H2-0           | 44                             | х    |

| 6Eh                 | R/W | Zone 3, Zone 4<br>Hysteresis          | H3-3             | H3-2               | H3-1             | H3-0             | H4-3  | H4-2   | H4-1   | H4-0           | 44                             | х    |

| 6Fh                 | R/W | XOR Tree<br>Enable                    | RES              | RES                | RES              | RES              | RES   | RES    | RES    | XEN            | 00                             | х    |

| 75h                 | R/W | Fan Spin-up<br>Mode                   | Tach4<br>Disable | Tach3/4<br>Disable | Tach2<br>Disable | Tach1<br>Disable | RES   | PWM3SU | PWM2SU | PWM1SU         | 00                             | х    |

#### Notes:

1. Reserved bits will always return 0 when read, X-bits in readings may be ignored.

When register 40h is locked, all bits are locked except 0 and 3 which remain user changeable.

Two-byte or extended resolution temperature, voltage and tachometer values are protected from changing when only one of the bytes is read. The implementation of a data word latch involves the register pairs in the table below. When one of the address pairs is read, the mating data is latched at the same time. The next SMBus access MUST be the mating address or the latch will be released. This implementation allows that the data may be read in the order of LS-MS or MS-LS and the pair will remain coherent.

Preliminary Specification – Subject to change without notice

#

| MS-Byte<br>Address<br>(hex) | LS-Byte<br>Address<br>(hex) | Data Field Name    |

|-----------------------------|-----------------------------|--------------------|

| 25                          | 10                          | Zone 1 Temperature |

| 26                          | 15                          | Zone 2 Temperature |

| 27                          | 16                          | Zone 3 Temperature |

| 33                          | 17                          | Zone 4 Temperature |

| 20                          | 13                          | 2.5V               |

| 21                          | 18                          | VCCP               |

| 22                          | 11                          | 3.3V               |

| 23                          | 12                          | 5V                 |

| 24                          | 14                          | 12V                |

| 29                          | 28                          | Tach 1             |

| 2B                          | 2A                          | Tach 2             |

| 2D                          | 2C                          | Tach 3             |

| 2F                          | 2E                          | Tach 4             |

#### **Temperature Measurement**

Diode temperatures are measured with a precision  $Delta-V_{BE}$  methodology converted to a digital temperature reading by a 10-bit sigma-delta converter. PECI interface to the CPU provide Digital Thermometer readings of substrate temperature. The measurement system provides a means for assigning any of the temperature inputs to a Temperature Zone. The user may set limits on these readings to be continuously monitored and alarm bits set when they are exceeded. Separately, the measurements are also delivered to the automatic fan control system to adjust fan speed. The following registers contain the readings from the internal and remote sensors.

| 5                   | -              | ,                                 | -              |       |       | 5     | • (•• =• |       |       |                |                  |

|---------------------|----------------|-----------------------------------|----------------|-------|-------|-------|----------|-------|-------|----------------|------------------|

| Register<br>Address | Read/<br>Write | Register Name                     | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

| 25h                 | R              | Zone 1 Temper-<br>ature (MS Byte) | 9              | 8     | 7     | 6     | 5        | 4     | 3     | 2              | N/A              |

| 10h                 | R              | Zone 1 Temper-<br>ature (LS Byte) | 1              | 0     | х     | х     | х        | х     | х     | х              | N/A              |

| 26h                 | R              | Zone 2 Temper-<br>ature (MS Byte) | 9              | 8     | 7     | 6     | 5        | 4     | 3     | 2              | N/A              |

| 15h                 | R              | Zone 2 Temper-<br>ature (LS Byte) | 1              | 0     | х     | х     | х        | х     | х     | х              | N/A              |

| 27h                 | R              | Zone 3 Temper-<br>ature (MS Byte) | 9              | 8     | 7     | 6     | 5        | 4     | 3     | 2              | N/A              |

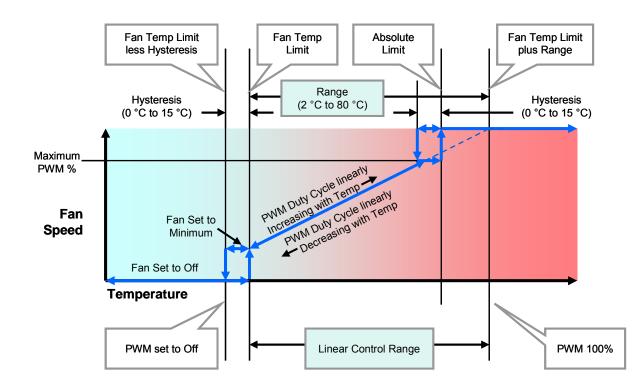

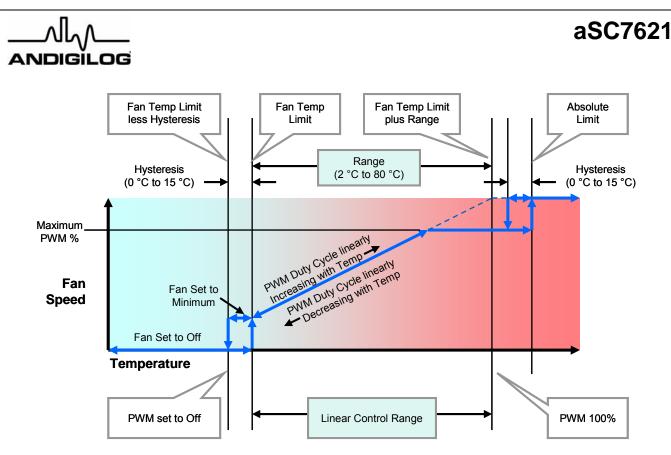

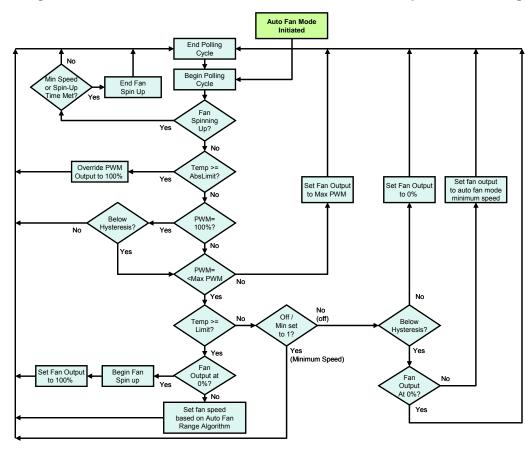

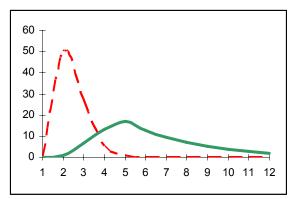

| 16h                 | R              | Zone 3 Temper-<br>ature (LS Byte) | 1              | 0     | х     | х     | х        | х     | х     | х              | N/A              |