# microelectronics group

# USS-720 *Instant USB*™ USB-to-*IEEE*\* 1284 Bridge

#### **Features**

#### **Device Features:**

- Full compliance with the Universal Serial Bus Specification Revision 1.0

- On-chip transceivers for USB

- Low power consumption allows part to be powered from USB connection

- Dual on-chip USB packet buffers for fast response

- Fully compatible USB host device drivers available

- Fully compliant with USB printer device class specification

- Implemented in Lucent Technologies Microelectronics Group's 0.35 μm, 3 V standard-cell library

- Complete single-chip solution in a 44-pin MQFP

#### IEEE 1284 (Parallel) Features:

- Transparent, fully automatic support for true bidirectional communication

- Hardware initiates and manages automatic negotiation for the fastest protocol available

- Supports standard PC parallel port register-based operation

- Support of multiple logical channels

- Maximum throughput: 1.216 Mbytes/s (ECP mode)

#### Software Features:

- The USS-720 software allows current Microsoft Windows<sup>†</sup> printer drivers to print seamlessly to USB

- Fully Plug & Play compatible

- Can print from any application running under Windows 95 OEM release including DOS applications

# Description

The USS-720 integrated circuit connects an *IEEE* 1284 parallel port peripheral to the universal serial bus (USB). It is designed to be a low-cost, single-chip embedded solution requiring minimal external components. It is suitable for a wide range of applications, from integrated applications where the IC is mounted on a printed-circuit board inside a product, to stand-alone applications where the chip provides a standard parallel port to a USB-capable computer. The USS-720 software will allow peripheral vendors to easily migrate parallel port devices to USB. This solution requires no firmware changes on the peripheral.

- \* IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

- † Microsoft and Windows are registered trademarks of Microsoft Corporation.

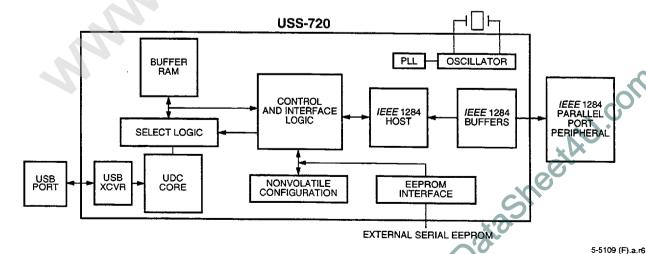

Figure 1. Block Diagram

Note: Advisories are issued as needed to update product information. When using this data sheet for design purposes, please contact your Lucent Technologies Microelectronics Group Account Manager to obtain the latest advisory on this product.

# **Table of Contents**

| Contents Page                               | Contents                        | Page |

|---------------------------------------------|---------------------------------|------|

| Features1                                   | Bidirectional Mode (001)        | 14   |

| Description 1                               | Compatibility Mode (010)        |      |

| Pin Information 3                           | ECP Mode (011)                  |      |

| Overview 5                                  | EPP Mode (100)                  | 14   |

| USB Port 5                                  | Registers                       |      |

| Device Descriptor, Configurations, and      | Data Register                   |      |

| Interfaces 5                                | Status Register                 |      |

| Supported Descriptors 5                     | Control Register                |      |

| Descriptor Locations 5                      | EPP Address Register            |      |

| Onboard Device Descriptor 6                 |                                 |      |

| Configuration Descriptor 7                  |                                 |      |

| Interface Descriptors 8                     |                                 |      |

| Interface 0, Alternate Setting 0 (I0:A0) 8  | USS-720 Control Register        |      |

| Interface 0, Alternate Setting 1 (I0:A1) 9  | USS-720 Setup Register          |      |

| Interface 0, Alternate Setting 2 (I0:A2) 10 | Interrupts                      |      |

| Pipes 11                                    | nAck Interrupt                  |      |

| Control Pipe 11                             | EPP Time-Out Interrupt          | 22   |

| Bulk In Pipe 11                             | nFault Interrupt                |      |

| Bulk Out Pipe11                             | Bulk In Interrupt               |      |

| Interrupt Pipe11                            | Bulk Out Interrupt              |      |

| Interpipe Synchronization11                 | Change Interrupt                |      |

| Requests 11                                 | Disconnect Interrupt            |      |

| Standard Requests11                         | External Circuitry Requirements | 23   |

| Printer Class-Specific Requests 12          | Filter Bypass Mode              | 24   |

| GET_DEVICE_ID12                             | High Drive Mode                 | 24   |

| GET_PORT_STATUS 12                          | Self-Powered Mode               | 24   |

| SOFT_RESET12                                | Absolute Maximum Ratings        |      |

| Vendor-Specific Requests 13                 | Electrical Characteristics      | 24   |

| GET_1284_REGISTER13                         | Timing Characteristics          |      |

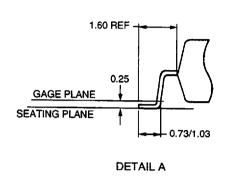

| SET_1284_REGISTER 13                        | Outline Diagram                 |      |

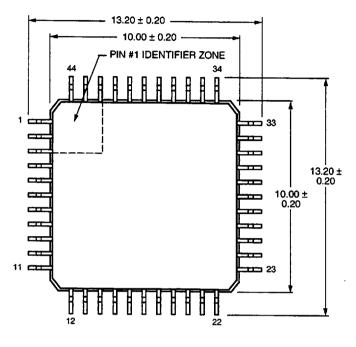

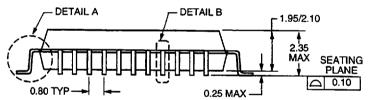

| EEE 1284 Port 14                            | 44-Pin MQFP                     | 27   |

| Register-Based Operation14                  | •                               |      |

| Standard Mode (000) 14                      |                                 |      |

# Pin Information

5-5429.r4

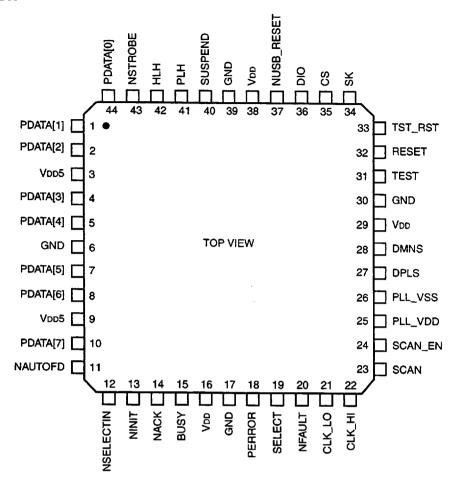

Note: An N before symbol names indicates active-low.

Figure 2. Pin Diagram

**Table 1. Pin Descriptions**

| Pin | Symbol*  | Туре | Name/Description                                |

|-----|----------|------|-------------------------------------------------|

| 1   | PDATA[1] | 1/0  | Parallel Port Data Signal Bit 1.                |

| 2   | PDATA[2] | 1/0  | Parallel Port Data Signal Bit 2.                |

| 3   | VDD5     | Р    | 5 V Power Supply for 5 V Parallel Port Signals. |

| 4   | PDATA[3] | 1/0  | Parallel Port Data Signal Bit 3.                |

| 5   | PDATA[4] | 1/0  | Parallel Port Data Signal Bit 4.                |

| 6   | GND      | Р    | Ground.                                         |

| 7   | PDATA[5] | 1/0  | Parallel Port Data Signal Bit 5.                |

| 8   | PDATA[6] | 1/0  | Parallel Port Data Signal Bit 6.                |

<sup>\*</sup> An N before symbol names indicates active-low.

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| 9 VDD5 P 5 V Power Supply for 5 V Parallel Port Signals.  10 PDATA[7] I/O Parallel Port Data Signal Bit 7.  11 NAUTOFD O Parallel Port nAutoFd Signal (Active-Low).  12 NSELECTIN O Parallel Port nSelectIn Signal (Active-Low).  13 NINIT O Parallel Port nAck Signal (Active-Low).  14 NACK I Parallel Port Roke Signal (Active-Low).  15 BUSY I Parallel Port Busy Signal.  16 VDD P 3.3 V Power Supply.  17 GND P Ground.  18 PERROR I Parallel Port Perror Signal.  19 SELECT I Parallel Port Select Signal.  20 NFAULT I Parallel Port Fault Signal (Active-Low).  21 CLK_LO I Clock Low. Crystal or CMOS input.  22 CLK_HI O Clock High. Crystal or no connection.  23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion.  24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing.  25 PLL_VDD P 3.3 V Analog Power Supply for PLL.  26 PLL_VSS P Analog Ground for PLL.  27 DPLS I/O USB DPLS Signal.  28 DMNS I/O USB DNS Signal.  29 VDD P 3.3 V Power Supply.  30 GND P Ground.  31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.                                                                                                                                                                                                                                                    | Pin | Symbol*    | Туре | Name/Description                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |            |      |                                                                                                                                                 |

| 11 NAUTOFD   O Parallel Port nAutoFd Signal (Active-Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  | PDATA[7]   | 1/0  |                                                                                                                                                 |

| 13 NINIT   O Parallel Port Initi Signal (Active-Low).     14 NACK   I Parallel Port nAck Signal (Active-Low).     15 BUSY   I Parallel Port Busy Signal.     16 Vob   P 3.3 V Power Supply.     17 GND   P Ground.     18 PERROR   I Parallel Port PError Signal.     19 SELECT   I Parallel Port Select Signal.     19 SELECT   I Parallel Port Select Signal.     20 NFAULT   I Parallel Port NFault Signal (Active-Low).     21 CLK_LO   I Clock Low. Crystal or CMOS input.     22 CLK_HI   O Clock High. Crystal or no connection.     23 SCAN   I Scan. This signal is only used for production testing. Tie to GND for normal operation.     24 SCAN_EN   I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation.     25 PLL_VDD   P 3.3 V Analog Power Supply for PLL.     26 PLL_VSS   P Analog Ground for PLL.     27 DPLS   I/O USB DMNS Signal.     29 VDD   P 3.3 V Power Supply.     30 GND   P Ground.     31 TEST   I Test. This signal is only used for production testing. Tie to GND for normal operation.     32 RESET   I Reset. This signal is only used for production testing. Tie to GND for normal operation.     33 TST_RST   I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.     34 SK   O Serial ROM Clock.     35 CS   O Serial ROM Clock.     36 DIO   I/O Serial ROM Clock.     37 NUSB_RESET   O USB Reset (Active-Low). Indicates USB reset condition.     38 VDD   P 3.3 V Power Supply. | 11  |            | 0    |                                                                                                                                                 |

| 14 NACK I Parallel Port nAck Signal (Active-Low). 15 BUSY I Parallel Port Busy Signal. 16 VDD P 3.3 V Power Supply. 17 GND P Ground. 18 PERROR I Parallel Port PError Signal. 19 SELECT I Parallel Port Select Signal. 20 NFAULT I Parallel Port nFault Signal (Active-Low). 21 CLK_LO I Clock Low. Crystal or CMOS input. 22 CLK_HI O Clock High. Crystal or no connection. 23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion. 24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation. 25 PLL_VDD P 3.3 V Analog Power Supply for PLL. 26 PLL_VSS P Analog Ground for PLL. 27 DPLS I/O USB DPLS Signal. 28 DMNS I/O USB DMNS Signal. 29 VDD P 3.3 V Power Supply. 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Clock. 36 DIO I/O Serial ROM Chip Select. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply.                                                                                                                                                                                                                        | 12  | NSELECTIN  | 0    | Parallel Port nSelectin Signal (Active-Low).                                                                                                    |

| 15 BUSY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13  | NINIT      | 0    | Parallel Port ninit Signal (Active-Low).                                                                                                        |

| 15 BUSY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14  | NACK       | 1    | Parallel Port nAck Signal (Active-Low).                                                                                                         |

| 17 GND P Ground. 18 PERROR I Parallel Port PError Signal. 19 SELECT I Parallel Port Select Signal. 20 NFAULT I Parallel Port Fault Signal (Active-Low). 21 CLK_LO I Clock Low. Crystal or CMOS input. 22 CLK_HI O Clock High. Crystal or no connection. 23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion. 24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation. 25 PLL_VDD P 3.3 V Analog Power Supply for PLL. 26 PLL_VSS P Analog Ground for PLL. 27 DPLS I/O USB DPLS Signal. 28 DMNS I/O USB DNS Signal. 29 VDD P 3.3 V Power Supply. 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Clock. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply.                                                                                                                                                                                                                                                                                                                                         | 15  | BUSY       | 1    |                                                                                                                                                 |

| 18 PERROR I Parallel Port PError Signal.  19 SELECT I Parallel Port Select Signal.  20 NFAULT I Parallel Port nFault Signal (Active-Low).  21 CLK_LO I Clock Low. Crystal or CMOS input.  22 CLK_HI O Clock High. Crystal or no connection.  23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion.  24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation.  25 PLL_VDD P 3.3 V Analog Power Supply for PLL.  26 PLL_VSS P Analog Ground for PLL.  27 DPLS I/O USB DPLS Signal.  28 DMNS I/O USB DMNS Signal.  29 VDD P 3.3 V Power Supply.  30 GND P Ground.  31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  34 SK O Serial ROM Clock.  35 CS O Serial ROM Clock.  36 DIO I/O Serial ROM Data Signal.  37 NUSS_RESET O USB Reset (Active-Low). Indicates USB reset condition.  38 VDD P 3.3 V Power Supply.                                                                                                                                                                                                                                                                                                                                    | .16 | VDD        | Р    | 3.3 V Power Supply.                                                                                                                             |

| 19 SELECT I Parallel Port Select Signal. 20 NFAULT I Parallel Port nFault Signal (Active-Low). 21 CLK_LO I Clock Low. Crystal or CMOS input. 22 CLK_HI O Clock High. Crystal or no connection. 23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion. 24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation. 25 PLL_VDD P 3.3 V Analog Power Supply for PLL. 26 PLL_VSS P Analog Ground for PLL. 27 DPLS I/O USB DPLS Signal. 28 DMNS I/O USB DMNS Signal. 29 VDD P 3.3 V Power Supply. 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Clock. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 Vod P 3.3 V Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                 | 17  | GND        | Р    | Ground.                                                                                                                                         |

| NFAULT   Parallel Port nFault Signal (Active-Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18  | PERROR     | - 1  | Parallel Port PError Signal.                                                                                                                    |

| 21       CLK_LO       I       Clock Low. Crystal or CMOS input.         22       CLK_HI       O       Clock High. Crystal or no connection.         23       SCAN       I       Scan. This signal is only used for production testing. Tie to GND for normal operation.         24       SCAN_EN       I       Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation.         25       PLL_VDD       P       3.3 V Analog Power Supply for PLL.         26       PLL_VSS       P       Analog Ground for PLL.         27       DPLS       I/O       USB DMS Signal.         28       DMNS       I/O       USB DMNS Signal.         29       VDD       P       3.3 V Power Supply.         30       GND       P       Ground.         31       TEST       I       Test. This signal is only used for production testing. Tie to GND for normal operation.         32       RESET       I       Reset. This signal is only used for production testing. Tie to GND for normal operation.         33       TST_RST       I       Test Reset. This signal is only used for production testing. Tie to GND for normal operation.         34       SK       O       Serial ROM Clock.         35       CS       O                                                                                                                                                                                                                                                                  | 19  | SELECT     | 1    | Parallel Port Select Signal.                                                                                                                    |

| 22 CLK_HI O Clock High. Crystal or no connection. 23 SCAN I Scan. This signal is only used for production testing. Tie to GND for normal operation. 24 SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation. 25 PLL_VDD P 3.3 V Analog Power Supply for PLL. 26 PLL_VSS P Analog Ground for PLL. 27 DPLS I/O USB DPLS Signal. 28 DMNS I/O USB DMNS Signal. 29 VDD P 3.3 V Power Supply. 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Chip Select. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20  | NFAULT     | ı    | Parallel Port nFault Signal (Active-Low).                                                                                                       |

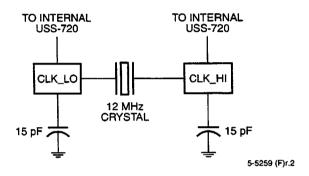

| SCAN I Scan. This signal is only used for production testing. Tie to GND for normal oper tion.  SCAN_EN I Scan Enable. When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation.  PLL_VDD P 3.3 V Analog Power Supply for PLL.  PLL_VSS P Analog Ground for PLL.  PLL_VSS P Analog Ground for PLL.  DPLS I/O USB DPLS Signal.  DMNS I/O USB DMNS Signal.  P Ground.  TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  TEST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  TEST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  TEST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  TEST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  SK O Serial ROM Clock.  SCS O Serial ROM Clock.  SCS O Serial ROM Data Signal.  NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  SK VDD P 3.3 V Power Supply.                                                                                                                                                                                                                                                                                                             | 21  | CLK_LO     |      | Clock Low. Crystal or CMOS input.                                                                                                               |

| tion.  24 SCAN_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22  | CLK_HI     | 0    | Clock High. Crystal or no connection.                                                                                                           |

| production testing. Tie to GND for normal operation.  25 PLL_VDD P 3.3 V Analog Power Supply for PLL.  26 PLL_VSS P Analog Ground for PLL.  27 DPLS I/O USB DPLS Signal.  28 DMNS I/O USB DMNS Signal.  29 VDD P 3.3 V Power Supply.  30 GND P Ground.  31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  34 SK O Serial ROM Clock.  35 CS O Serial ROM Clock.  36 DIO I/O Serial ROM Data Signal.  37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  38 VDD P 3.3 V Power Supply.  39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23  | SCAN       | 1    | <b>Scan.</b> This signal is only used for production testing. Tie to GND for normal operation.                                                  |

| 26 PLL_VSS P Analog Ground for PLL.  27 DPLS I/O USB DPLS Signal.  28 DMNS I/O USB DMNS Signal.  29 VDD P 3.3 V Power Supply.  30 GND P Ground.  31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  34 SK O Serial ROM Clock.  35 CS O Serial ROM Chip Select.  36 DIO I/O Serial ROM Data Signal.  37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  38 VDD P 3.3 V Power Supply.  39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24  | SCAN_EN    | ı    | <b>Scan Enable.</b> When high, internal chip scan is enabled. This signal is only used for production testing. Tie to GND for normal operation. |

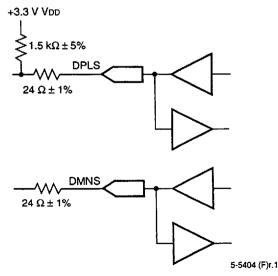

| DPLS I/O USB DPLS Signal.  DMNS I/O USB DMNS Signal.  TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  KK O Serial ROM Clock.  SCS O Serial ROM Chip Select.  MUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  NUSB_RESET O Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25  | PLL_VDD    | Р    | 3.3 V Analog Power Supply for PLL.                                                                                                              |

| DMNS I/O USB DMNS Signal.  P 3.3 V Power Supply.  GND P Ground.  TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  TEST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  Kest O Serial ROM Clock.  SCS O Serial ROM Clock.  CS O Serial ROM Chip Select.  NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  NUSB_RESET O Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26  | PLL_VSS    | Р    | Analog Ground for PLL.                                                                                                                          |

| 29 VDD P 3.3 V Power Supply. 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Clock. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply. 39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27  | DPLS       | 1/0  | USB DPLS Signal.                                                                                                                                |

| 30 GND P Ground. 31 TEST I Test. This signal is only used for production testing. Tie to GND for normal operation. 32 RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation. 33 TST_RST I Test Reset. This signal is only used for production testing. Tie to GND for normal operation. 34 SK O Serial ROM Clock. 35 CS O Serial ROM Clock. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply. 39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28  | DMNS       | 1/0  | USB DMNS Signal.                                                                                                                                |

| TEST I Test. This signal is only used for production testing. Tie to GND for normal operation.  RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  Kest Comparison.  Serial ROM Clock.  Comparison.  Serial ROM Clock.  Comparison.  Serial ROM Chip Select.  NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  NUSB_RESET O P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29  | VDD        | Р    | 3.3 V Power Supply.                                                                                                                             |

| tion.  RESET I Reset. This signal is only used for production testing. Tie to GND for normal operation.  Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  Keyper Supply.  SK O Serial ROM Clock.  Serial ROM Chip Select.  CS O Serial ROM Data Signal.  NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  NUSB_RESET O Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30  | GND        | Р    | Ground.                                                                                                                                         |

| tion.  Test Reset. This signal is only used for production testing. Tie to GND for normal operation.  Key Comparison operation.  Serial ROM Clock.  Comparison operation.  Serial ROM Clock.  Comparison operation.  Serial ROM Clock.  Serial ROM Chip Select.  Comparison operation.  Serial ROM Clock.  Serial ROM Chip Select.  NUSB_RESET of USB Reset (Active-Low). Indicates USB reset condition.  NUSB_RESET of Page 1.3.3 V Power Supply.  Comparison operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31  | TEST       | 1    | <b>Test.</b> This signal is only used for production testing. Tie to GND for normal operation.                                                  |

| operation.  34 SK O Serial ROM Clock.  35 CS O Serial ROM Chip Select.  36 DIO I/O Serial ROM Data Signal.  37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  38 VDD P 3.3 V Power Supply.  39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32  | RESET      | l    | <b>Reset.</b> This signal is only used for production testing. Tie to GND for normal operation.                                                 |

| 35 CS O Serial ROM Chip Select. 36 DIO I/O Serial ROM Data Signal. 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply. 39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33  | TST_RST    | I    | <b>Test Reset.</b> This signal is only used for production testing. Tie to GND for normal operation.                                            |

| 36 DIO I/O Serial ROM Data Signal.  37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition.  38 VDD P 3.3 V Power Supply.  39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34  | SK         | 0    | Serial ROM Clock.                                                                                                                               |

| 37 NUSB_RESET O USB Reset (Active-Low). Indicates USB reset condition. 38 VDD P 3.3 V Power Supply. 39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35  | CS         | 0    | Serial ROM Chip Select.                                                                                                                         |

| 38         VDD         P         3.3 V Power Supply.           39         GND         P         Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36  | DIO        | 1/0  | Serial ROM Data Signal.                                                                                                                         |

| 39 GND P Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37  | NUSB_RESET | 0    | USB Reset (Active-Low). Indicates USB reset condition.                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38  | VDD        | Р    | 3.3 V Power Supply.                                                                                                                             |

| 40 SUSPEND O Suspend. Indicates USB bus in suspend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39  | GND        | Р    | Ground.                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40  | SUSPEND    | 0    | Suspend. Indicates USB bus in suspend.                                                                                                          |

| 41 PLH ! Parallel Port Peripheral Logic High Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41  | PLH        | 1    | Parallel Port Peripheral Logic High Signal.                                                                                                     |

| 42 HLH O Parallel Port Host Logic High Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42  |            | 0    |                                                                                                                                                 |

| 43 NSTROBE O Parallel Port nStrobe Signal (Active-Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43  | NSTROBE    | 0    |                                                                                                                                                 |

| 44 PDATA[0] I/O Parallel Port Data Signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44  | PDATA[0]   | 1/0  | Parallel Port Data Signal.                                                                                                                      |

<sup>\*</sup> An N before symbol names indicates active-low.

#### Overview

The USS-720 creates a bridge between one USB port and one *IEEE* 1284 enhanced parallel port. Internally, the USS-720 contains an integrated USB transceiver, a USB device controller (UDC) core, an *IEEE* 1284 core, integrated *IEEE* 1284 buffers, storage for USB configuration data, data buffers, and control logic to tie the blocks together. The USS-720 also contains an onboard oscillator, PLL, and reset block for single-chip operation.

In use, the USB port of the USS-720 is connected via a USB cable to a host computer or the downstream port of a USB hub. Host software sends commands and data to the USS-720 and receives status and data from the USS-720 using the USB protocol.

The *IEEE* 1284 enhanced parallel port of the device is connected to a peripheral device. If the peripheral is *IEEE* 1284 compatible, then the associated features and communication modes can be used. The USS-720 provides both automatic and manual operation of the *IEEE* 1284 port.

#### **USB Port**

The USB port on the USS-720 is electrically and logically compliant with the USB Specification Revision 1.0.

# Device Descriptor, Configurations, and Interfaces

#### **Supported Descriptors**

- Device.

- Configuration.

- Interface. The USS-720 device supports one interface with three alternate settings.

- Interface 0, alternate settings 0 and 1 are compliant with the USB Device Class Definition for Printing Devices, Release Candidate 1.0.

- Interface 0, alternate setting 2 is a vendor-specific interface.

- Endpoint. The USS-720 supports the following endpoints:

- Control endpoint. Accessible as endpoint 0 in all three alternate interface settings.

- Bulk Out endpoint. Accessible as endpoint 1 in all three alternate interface settings.

- Bulk In endpoint. Accessible as endpoint 2 in alternate interface settings 1 and 2.

- Interrupt endpoint. Accessible as endpoint 3 in alternate interface setting 2.

- String.

#### **Descriptor Locations**

Descriptor data is supplied from an external ROM or other device. The USS-720 provides support for 93CS56 and 93CS66 EEPROM interfaces. The format for the externally supplied descriptor data requires that the descriptors loaded be preceded by the total length of the descriptor to be returned. In the case of the device descriptor, this value would be 0x12, which is redundant since the descriptor returned is always 0x12 bytes long; the first byte of the descriptor would also be 0x12. The length of the configuration descriptor, however, is not the same as the first byte of that descriptor, since the configuration descriptor and all associated interface and endpoint descriptors are returned as a whole.

The USS-720 also contains a set of device, configuration, interface, and endpoint descriptors that may be used in development and prototyping. Retrieval of the onboard descriptors will occur if no external descriptor data is supplied.

The format for the externally supplied data is as shown in Table 2. The addressing for the specified EEPROM device is word aligned, so the following restrictions are placed upon the starting locations for the configuration and string descriptors.

- The configuration descriptor must start at word address 0x13 (byte address 0x26).

- String descriptors must start at an address that is aligned on a double-word boundary.

**Table 2. Externally Supplied Data Format**

| Byte Address      | Word Address  | Value                                                                          |

|-------------------|---------------|--------------------------------------------------------------------------------|

| 0x00              | 0x00          | 0x12                                                                           |

| 0x010x12          | <del></del>   | Device descriptor as defined in USB Specification Revision 1.0.                |

| 0x26              | 0x13          | Total length of string to be returned in response to a                         |

| İ                 |               | GET_CONFIGURATION_DESCRIPTOR request.                                          |

| 0x27—0x2F         | <del>-</del>  | Configuration descriptor as defined in USB Specification Revision 1.0.         |

| 0x30???*          |               | Interface and endpoint descriptors to be returned in response to a             |

|                   |               | GET_CONFIGURATION_DESCRIPTOR request.                                          |

| Any even word a   | ddress beyond | Length of string to return in response to a GET_STRING_DESCRIPTOR              |

| the end of the co | nfiguration   | request. This address divided by two should be included in the low byte of the |

| descriptor return | string.       | windex field of the GET_DESCRIPTOR standard command.                           |

| Next address—e    | nd of string  | String descriptor as defined in USB Specification Revision 1.0.                |

| descriptor.       |               |                                                                                |

<sup>\*</sup> The question marks (???) indicate that this byte address value is determined for the user's application based on the above information. The number is going to vary depending on how the user formats their configuration information.

**Note:** Tables 3—14 describe the descriptor data contained in the USS-720's internal ROM. This information can be used as a guide in creating the externally supplied descriptor data.

#### **Onboard Device Descriptor**

There is only one device descriptor for each USB device. This descriptor contains the definitions of the device class and the device subclass, among other things.

**Table 3. Device Descriptor**

| Offset | Field              | Size | Value  | Description                                                       |

|--------|--------------------|------|--------|-------------------------------------------------------------------|

| 0      | bLength            | Byte | 0x12   | Size of this descriptor in bytes.                                 |

| 1      | bDescriptorType    | Byte | 0x01   | Device descriptor type.                                           |

| 2      | bcdUSB             | Word | 0x0100 | USB Specification release number in BCD.                          |

| 4      | bDeviceClass       | Byte | 0x00   | Interface specific. See Tables 6, 8, and 11.                      |

| 5      | bDeviceSubClass    | Byte | 0x00   | Interface specific. See Tables 6, 8, and 11.                      |

| 6      | bDeviceProtocol    | Byte | 0x00   | Interface specific. See Tables 6, 8, and 11.                      |

| 7      | wMaxPacketSize0    | Byte | 0x08   | Maximum packet size for endpoint 0.                               |

| 8      | idVendor           | Word | 0x047E | Vendor ID for Lucent Technologies.                                |

| 10     | idProduct          | Word | 0x1001 | Product ID.                                                       |

| 12     | bcdDevice          | Word | 0x0103 | Device release number in BCD.                                     |

| 14     | iManufacturer      | Byte | 0x00   | Index of string descriptor describing manufacturer.               |

| 15     | iProduct           | Byte | 0x00   | Index of string descriptor describing this product.               |

| 16     | iSerialNumber      | Byte | 0x00   | Index of string descriptor describing the device's serial number. |

| 17     | bNumConfigurations | Byte | 0x01   | Number of possible configurations.                                |

# **Configuration Descriptor**

The USS-720 has one default configuration descriptor. This descriptor has one interface, which has three alternate settings. The three alternate settings and the endpoints that they support are shown in Table 4.

Table 4. Alternate Settings and Supported Endpoints

| Endpoint       | Interface                     |                               |                               |  |  |  |  |  |  |

|----------------|-------------------------------|-------------------------------|-------------------------------|--|--|--|--|--|--|

|                | Alternate Setting 0           | Alternate Setting 1           | Alternate Setting 2           |  |  |  |  |  |  |

| Control Pipe   | Endpoint Number 0<br>8 bytes  | Endpoint Number 0<br>8 bytes  | Endpoint Number 0<br>8 bytes  |  |  |  |  |  |  |

| Bulk Out Pipe  | Endpoint Number 1<br>64 bytes | Endpoint Number 1<br>64 bytes | Endpoint Number 1<br>64 bytes |  |  |  |  |  |  |

| Bulk In Pipe   | *****                         | Endpoint Number 2<br>64 bytes | Endpoint Number 2<br>64 bytes |  |  |  |  |  |  |

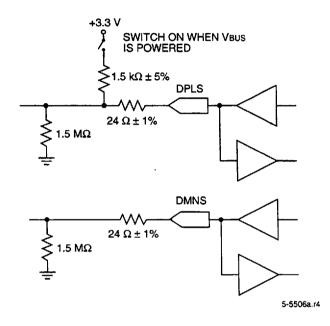

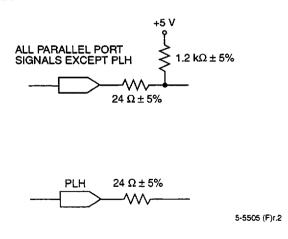

| Interrupt Pipe | _                             | _                             | Endpoint Number 3<br>4 bytes  |  |  |  |  |  |  |