February 1993

#### DESCRIPTION

The SSI 32R525R/525RM is an integrated read/write circuit designed for use with non-center tapped thin film heads in disk drive systems. Each chip controls four heads and has three modes of operation: read, write, and idle. The circuit contains four channels of read amplifiers and write drivers and also has an internal write current source. The 32R525RM provides the same device as the 32R525R in a mirror pinout.

A current monitor (IMF) output is provided that allows a multichip enable fault to be detected. An enabled chip's output will produce one unit of current. An open collector output, write select verify (WSV), will go low if the write current source transistor is forward biased. The circuit operates on +5 volt, and -5 volt power and is available in 20-lead and 24-lead SOL packages.

### **FEATURES**

High performance

Read Mode Gain = 125 V/V nominal

Input Noise = 0.8 nV/√Hz max

Input Capacitance = 35 pF max

Write Current Range = 25 mA to 40 mA

Write Current Rise Time = 10 nsec max

Head Voltage Swing = 3.8 Vpp min

- Write unsafe detection

- -5V, +5V power supplies

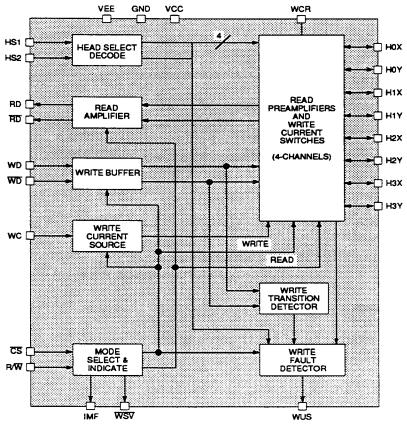

#### **BLOCK DIAGRAM**

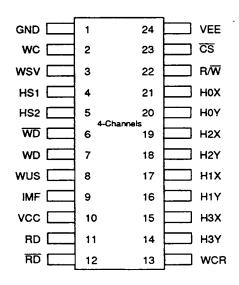

#### **PIN DIAGRAM**

24-Lead SOL

CAUTION: Use handling procedures necessary for a static sensitive component.

0293 - rev.

1

#### **FUNCTIONAL DESCRIPTION**

#### WRITE MODE

In Write Mode ( $R/\overline{W}$  and  $\overline{CS}$  low) the circuit functions as a differential current switch. The Head Select Inputs (HS1 and HS2) determine the selected head. The write current magnitude is adjusted by an external resistor Rex from WC to Vcc.

$$lw = \frac{80}{Rex} Adc$$

#### WRITE MODE FAULT DETECT CIRCUIT

Several circuits are dedicated to detecting fault conditions associated with the write mode. A logical high (off) level will be present at the Write Unsafe (WUS) terminal if any of the following write fault conditions are present:

- · Open head circuit

- · Head shorted to ground

- No write current

- Write current transition frequency too low

- Head select input(s) open circuit

- Write mode not logically selected

The Write Unsafe output is open-collector and is usually terminated by an external resistor connected to Vcc.

#### **READ MODE**

In Read Mode, (R/W high and  $\overline{CS}$  low), the circuit functions as a low noise differential amplifier. The read amplifier input terminals are determined by the Head Select inputs. The read amplifier outputs (RD,  $\overline{RD}$ ) are open collector, requiring external load resistors connected to Vcc. The amplifier gain polarity is non-inverting between HX, Y inputs and RD outputs.

#### **IDLE MODE**

Taking  $\overline{CS}$  high selects the idle mode which switches the RD and  $\overline{RD}$  outputs into a high impedance state and deactivates the internal write current source. This facilitates multi-device installations by allowing the read outputs to be wired OR'ed.

#### MODE SELECTION AND INDICATION CIRCUIT

Logical control inputs which select mode and head channel are TTL compatible. Their functions are described in Tables 1 and 2.

Selection of the write mode is indicated by a low (on) state of the Write Select Verify (WSV) terminal. The open collector output is usually terminated by an external resistor connected to Vcc.

The selection of either the write or read mode is indicated by the flow of a unit of current into the Current Monitor (IMF) terminal. By summing the currents from multiple circuits, the user can determine that one, and only one, circuit is active.

The mode select inputs have internal pull up circuits so that if an input is open it will rise to the upper logic level.

Table 1: Head Select Table

| Head Selected | HS2 | HS1 |

|---------------|-----|-----|

| 0             | 0   | 0   |

| 1             | 0   | 1   |

| 2             | 1   | 0   |

| 3             | 1   | 1   |

Table 2: Mode Select Table

|                                      | ode<br>lect |                  | Indicating & Fault Outputs |     |     |

|--------------------------------------|-------------|------------------|----------------------------|-----|-----|

| ĊS                                   | R/₩         | Selected<br>Mode | IMF                        | wsv | wus |

| 1                                    | X           | ldle             | off                        | off | off |

| 0                                    | 1           | Read             | on                         | off | off |

| 0                                    | 0           | Write            | on                         | on  | on* |

| *Provided that no fault is detected. |             |                  |                            |     |     |

## **PIN DESCRIPTION**

| NAME                   | TYPE       | DESCRIPTION                                                                                                                                                                                  |  |  |  |

|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CONTROL INP            | UT PINS    |                                                                                                                                                                                              |  |  |  |

| <u>cs</u>              | 1          | Chip Select input. A logical low level enables the circuit for a read or write operation. Has internal pull up.                                                                              |  |  |  |

| R/W                    | 1          | Read/Write select. A logical low level enables the Write mode (when $\overline{CS}$ is low). Has internal pull up.                                                                           |  |  |  |

| HS1,HS2                | 1          | Head Select inputs. Logical combinations (Table 1) select one of four heads.                                                                                                                 |  |  |  |

| HEAD TERMIN            | AL PINS    |                                                                                                                                                                                              |  |  |  |

| H0X - H3X<br>H0Y - H3Y | 1/0        | Connection to read/write magnetic head terminals.                                                                                                                                            |  |  |  |

| DATA INPUT/C           | UTPUT PINS |                                                                                                                                                                                              |  |  |  |

| WD, WD                 | J          | Differential Write Data inputs used to write data patterns on the disk.                                                                                                                      |  |  |  |

| RD, RD                 | ı          | Differential Read Data pattern output amplified playback from the disk. These outputs are normally terminated in $100\Omega$ resistors to Vcc.                                               |  |  |  |

| EXTERNAL CO            | MPONENT (  | CONNECTION PINS                                                                                                                                                                              |  |  |  |

| WC                     | 1          | Resistor connected to Vcc to provide desired value of write current.                                                                                                                         |  |  |  |

| CURRENT MO             | NITOR PINS |                                                                                                                                                                                              |  |  |  |

| ₩SV                    | 0          | Write Select Verify is an open collector output with the on state indicating that the circuit has been selected for a write operation. It is normally terminated to +Vcc through a resistor. |  |  |  |

| wus                    | 0          | Write Unsafe is an open collector output with the off state indicating that conditions are not proper for a write operation.                                                                 |  |  |  |

| IMF                    | 0          | High impedance output sinks a unit of monitor current when the chip is enabled.                                                                                                              |  |  |  |

| POWER, GROUND PINS     |            |                                                                                                                                                                                              |  |  |  |

| Vcc                    | I          | Positive power supply voltage for circuit functions.                                                                                                                                         |  |  |  |

| VEE                    | 1          | Negative power supply voltage.                                                                                                                                                               |  |  |  |

| GND                    | 1/0        | Power supply common.                                                                                                                                                                         |  |  |  |

| WCR                    | _          | Write Current Connection to power supply common.                                                                                                                                             |  |  |  |

## **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified,  $4.75 \le VCC \le 5.20$ ,  $-5.50 \le VEE \le -4.75V$ ,  $0^{\circ} \le T$  (junction)  $\le 125^{\circ}C$ .

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                            | RATING                         |  |  |

|--------------------------------------|--------------------------------|--|--|

| Positive Supply Voltage, Vcc         | 6 VDC                          |  |  |

| Negative Supply Voltage, VEE         | -6 VDC                         |  |  |

| Operating Junction Temperature       | -20 to +130°C                  |  |  |

| Storage Temperature                  | -65 to +150°C                  |  |  |

| Lead Temperature (Soldering, 10 sec) | 260°C                          |  |  |

| Input Voltages                       |                                |  |  |

| Head Select (HS)                     | -0.4 to Vcc + 0.3V             |  |  |

| Chip Enable (CS)                     | -0.4 to Vcc+ 0.3V              |  |  |

| Read Select (R/W)                    | -0.4V to Vcc + 0.3V            |  |  |

| Write Data (WD, <del>WD</del> )      | -VEE to 0.3V                   |  |  |

| Head Inputs (Read Mode)              | -0.6 to 0.4V                   |  |  |

| Outputs                              |                                |  |  |

| Read Data (RD, RD)                   | Vcc - 2.5 to Vcc + 0.3V        |  |  |

| Write Unsafe (WUS)                   | -0.4V to Vcc + 0.3 and 20 mA V |  |  |

| Write Select Verify (WSV)            | -0.4V to Vcc + 0.3 and 20 mA V |  |  |

| Current Monitor (IMF)                | -0.4 to Vcc + 0.3V             |  |  |

| Current Reference (WC)               | -1.0 mA to 5.0 mA              |  |  |

| Head Outputs (Write Mode)            | -100 mA to 1.0 mA              |  |  |

### **POWER SUPPLY**

| PARAMETER                     | CONDITIONS             | MIN | NOM | MAX      | UNIT |

|-------------------------------|------------------------|-----|-----|----------|------|

| Power Dissipation             | Idle Mode              |     |     | 100      | mW   |

|                               | Read Mode              |     |     | 350      | mW   |

|                               | Write Mode, Iw = 40 mA |     |     | 500      | mW   |

| Positive Supply Current (ICC) | Idle Mode              |     |     | 10       | mA   |

|                               | Read Mode              |     |     | 25       | mA   |

|                               | Write Mode             |     |     | 12       | mA   |

| Negative Supply Current (IEE) | Idle Mode              |     |     | -8       | mA   |

|                               | Read Mode              |     |     | -45      | mA   |

|                               | Write Mode             |     |     | -40 - Iw | mA   |

### **DC CHARACTERISTICS**

| PARAMETER                                          | CONDITIONS             | MIN  | NOM | MAX  | UNIT       |

|----------------------------------------------------|------------------------|------|-----|------|------------|

| High Level Input Voltage (VIH) (CS, R/W, HS1, HS2) |                        | 2.0  |     |      | V          |

| Low Level Input Voltage (VIL) (CS, R/W, HS1, HS2)  |                        |      |     | 0.8  | V          |

| High Level Input Current (IIH) (CS, R√W)           | (VIH=2.7V)             |      |     | 20   | μ <b>A</b> |

| Low Level Input Current (IIL) (CS, R/W)            | (VIL=0.4V)             |      |     | -400 | μА         |

| High Level Input Current (IIH) (HS1, HS2)          | (VIH=2.7V)             |      |     | 250  | μА         |

| Low Level Input Current (IIL)<br>(HS1, HS2)        | (VIL=0.4V)             |      |     | 250  | μА         |

| High Level Input Voltage (VIH) (WD, WD)            |                        | -1.0 |     | .6   | ٧          |

| Low Level Input Voltage (VIL) (WD, WD)             |                        | -2.0 |     | -1.5 | V          |

| High Level Input Current (IIH) (WD, WD)            | (VIH=-0.6V, VIL=-2.0V) |      |     | 150  | μΑ         |

| Low Level Input Current (IIL) (WD, WD)             | (VIL=-2.0V, VIH=-1.0V) | -20  |     |      | μА         |

| Output Off Leakage Curr. (IOFF)<br>(WUS,- WSV)     | (VOFF=5.0V)            |      |     | 100  | μА         |

| Low Level Output Voltage (VOL) (WUS, -WSV)         | (IOL=8.0 mA)           |      |     | 0.4  | ٧          |

| Output Leakage Current (IOFF) (IMF)                | (VOFF=5.0V)            |      |     | 20   | μА         |

| Output on Current (ION) (IMF)                      | (VON=0.5V to 5.0V)     | 2.4  |     | 3.5  | mA         |

| Data Input Voltage Range                           |                        | -2.0 |     | 0.6  | V          |

| Data Input Current (per side)                      | Chip Enabled           |      |     | 150  | μА         |

| Data Input Capacitance                             | per side to GND        |      |     | 10   | pF         |

## **ELECTRICAL SPECIFICATIONS** (Continued)

### **READ MODE**

Tests performed with  $100\Omega$  load resistors from RD and  $\overline{RD}$  through series isolation diodes to VCC.

| PARAMETER                       | CONDITIONS                                                                         | MIN          | NOM | MAX          | UNIT  |

|---------------------------------|------------------------------------------------------------------------------------|--------------|-----|--------------|-------|

| Differential Voltage Gain       | Vin = 1m Vpp, f = 300 kHz                                                          | 100 125      |     | 150          | V/V   |

| Voltage Bandwidth (-3dB)        | Zs < 5z, Vin = 1m Vpp<br>f midband = 300 kHz                                       | 55           |     | 100          | MHz   |

| Input Noise Voltage             | $Zs = 0\Omega$ , $Vin = 0V$ , Power Bandwidth = 30 MHz                             |              |     | 0.8          | nV√Hz |

| Differential Input Capacitance  | Vin = 0V, f = 5 MHz                                                                |              |     | 35           | pF    |

| Differential Input Resistance   | Vin = 0V, f = 5 MHz                                                                | 500          |     | 1800         | Ω     |

| Input Bias Current (per side)   | Vin = 0V                                                                           |              |     | 0.17         | mA    |

| Dynamic Range                   | DC input voltage where AC gain falls to 90% of the gain with 0.5m Vpp input signal | -3.0         |     | 3.0          | mV    |

| Common Mode Rejection Ratio     | Vin = 100m Vpp, 0V DC<br>1 MHz ≤ f ≤10 MHz                                         | 50           |     |              | dB    |

|                                 | f = 20 MHz                                                                         | 46           |     |              | ďΒ    |

| Power Supply Rejection Ratio    | VCC or VEE = 100m Vpp<br>1 MHz $\leq$ f $\leq$ 10 MHz                              | 65           | -   |              | dB    |

|                                 | f = 20 MHz                                                                         | 40           |     |              | dB    |

| Channel Separation              | The three unselected channels are driven with Vin = 20m Vpp 1 MHz ≤ f ≤ 10 MHz     | 46           |     |              | dB    |

|                                 | f = 20 MHz                                                                         | 40           |     |              | dΒ    |

| Output Offset Voltage           |                                                                                    | -360         |     | 360          | mV    |

| Output Leakage Current          | Idle Mode                                                                          |              |     | 0.01         | mA    |

| Output Common Mode Voltage      |                                                                                    | VCC<br>-0.75 |     | VCC<br>-0.45 | ٧     |

| Single Ended Output Resistance  |                                                                                    | 10           |     |              | ΚΩ    |

| Single Ended Output Capacitance |                                                                                    |              |     | 10           | pF    |

### WRITE MODE

| Current Tolerance               | Current set to nominal value by Rex = 1.6K to 3.6 k $\Omega$ , Tj = 50°C | -8  | <b></b> | %   |

|---------------------------------|--------------------------------------------------------------------------|-----|---------|-----|

| Differential Head voltage swing | lw = 40 mA                                                               | 3.8 |         | Vpp |

## WRITE MODE (continued)

| PARAMETER                             | CONDITIONS                         | MIN  | NOM | MAX  | UNIT |

|---------------------------------------|------------------------------------|------|-----|------|------|

| Current Range (lw)                    | Rwc = $3600\Omega$ to $1600\Omega$ | 25   |     | 45   | mA   |

| Differential Output<br>Resistance, Rd |                                    | 1700 |     | 2600 | Ω    |

| Differential Output Capacitance       |                                    |      |     | 10   | pF   |

| WD, WD Transition Frequency           | WUS = low                          | 1.0  |     |      | MHz  |

### **SWITCHING CHARACTERISTICS**

| Lette de Desertantina Tourista Esta                   |                                                                                                        | <u> </u> |      |    |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|------|----|

| Idle to Read/Write Transition Time                    |                                                                                                        |          | 0.5  | μς |

| Read/Write to Idle Transition Time                    |                                                                                                        |          | 0.5  | μs |

| Read to Write Transition Time                         | VLCS = 0.8V,<br>Delay to 90% of lw                                                                     |          | 0.5  | μs |

| Write to Read Transition Time                         | VLCS = 0.8V, Delay to 90% of<br>20 MHz Read Signal<br>envelope, lw decay to 10%                        |          | 0.5  | μs |

| Head Select Switching Delay                           | Read or Write Mode                                                                                     |          | 0.5  | μs |

| Head Current Transition Time 10% to 90%               | lw = 40 mA, Lh = 0.15 $\mu$ H, Rh = 20 $\Omega$                                                        |          | 12   | ns |

| Head Current Overshoot                                | lw = 40 mA, Lh = 0.15 μH,<br>Rh = 20 $\Omega$ , relative to total<br>current change                    |          | 50   | %  |

| Head Current Switching Time<br>Asymmetry              | Lh = 0, Rh = 0, WD / $\overline{WD}$<br>transitions 2 ns, switching time<br>asymmetry 0.2 ns           |          | 1.5  | ns |

| WSV Transition Time                                   | Delay from 50% of write<br>select swing to 90% of final<br>WSV voltage,<br>Load = $2 k\Omega // 20 pF$ |          | 0.25 | μѕ |

| Unsafe to Safe Delay After<br>Write Data Begins (WUS) | f(data) = 5 MHz                                                                                        |          | 0.5  | μs |

| Safe to Unsafe Delay, (WUS)                           | Head open or shorted to GND, no write current, head select input open                                  |          | 0.5  | μѕ |

| Safe to Unsafe Delay, (WUS)                           | Non-switching write data                                                                               | 0.5      | 2.0  | μs |

| IMF Switching Time                                    | Delay from 50% of CS to 90% of final IMF current                                                       |          | 0.25 | μs |

### **PACKAGE PIN DESIGNATIONS**

(Top View)

|                |                    | -           | <u>-</u> |               | _     |          |                     |         |

|----------------|--------------------|-------------|----------|---------------|-------|----------|---------------------|---------|

| GND            | 1 24               | VEE.        | wsv 🖂    | 1 20          | □ wc  | wc 🗀     | 1 20                | wsv     |

| wc $\square$   | 2 23               | cs          | HS1      | 2 19          | GND   | GND      | 2 19                | HS1     |

| wsv 🗀          | 3 22               | RAW         | HS2      | 3 18          | VEE   | VEE      | 3 18                | HS2     |

| HS1            | 4 21               | <u></u> нох | WD       | 4 17          | cs    | <u> </u> | 4 17                | wo wo   |

| HS2            | 5 20               | HOY         | WD 🖂     | 5 16          | □ R/W | R/₩ [    | 5 16                | ₩D      |

| WD -           | 4-Channels<br>6 19 | H2X         | wus 🗀    | 6 Channels 15 | нох   | нох 🗔    | 2-<br>6 Channels 15 | wus wus |

| w <sub>D</sub> |                    |             | IMF      | 7 14          | □ ноч | ноу 🗔    | 7 14                | IMF     |

|                |                    | H2Y         | vcc 🗀    | 8 13          |       | н1х 🗀    | 8 13                | ₩ vcc   |

| wus            | 8 17               | H1X         | RD 🗀     | 9 12          | H1Y   | H1Y 🗀    | 9 12                | RD      |

| IMF            | 9 16               | H1Y         | RD       | 10 11         | wcr   | WCR      | 10 11               | RD      |

| vcc 🖂          | 10 15              | — нзх       | L        |               | J     | į.       |                     | j       |

| RD 🗀           | 11 14              | □ НЗҮ       |          | 32R525R       |       |          | 32R525RM            |         |

| RD             | 12 13              | WCR         | ;        | 20-Lead SO    | L     |          | 20-Lead SOL         | -       |

| 32R            | 525R-4 Chan        | inel        |          |               |       |          |                     |         |

### **ORDERING INFORMATION**

24-Lead SOL

| PART DESCRIPTION | ORDERING NUMBER | PACKAGE MARK |

|------------------|-----------------|--------------|

| SSI 32R525R      |                 |              |

| 20-Lead SOL      | 32R525R-2CL     | 32R525R-2CL  |

| 24-Lead SOL      | 32R525R-4CL     | 32R525R-4CL  |

| SSI 32R525RM     |                 |              |

| 20-Lead SOL      | 32R525RM-2CL    | 32R525RM-2CL |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680, (714) 573-6000, FAX: (714) 573-6914

©1989 Silicon Systems, Inc.

0293 - rev.

озвэзэ ↓ \_ В